Novel Step Floating Islands VDMOS with Low Specific on-Resistance by TCAD Simulation

Abstract

:1. Introduction

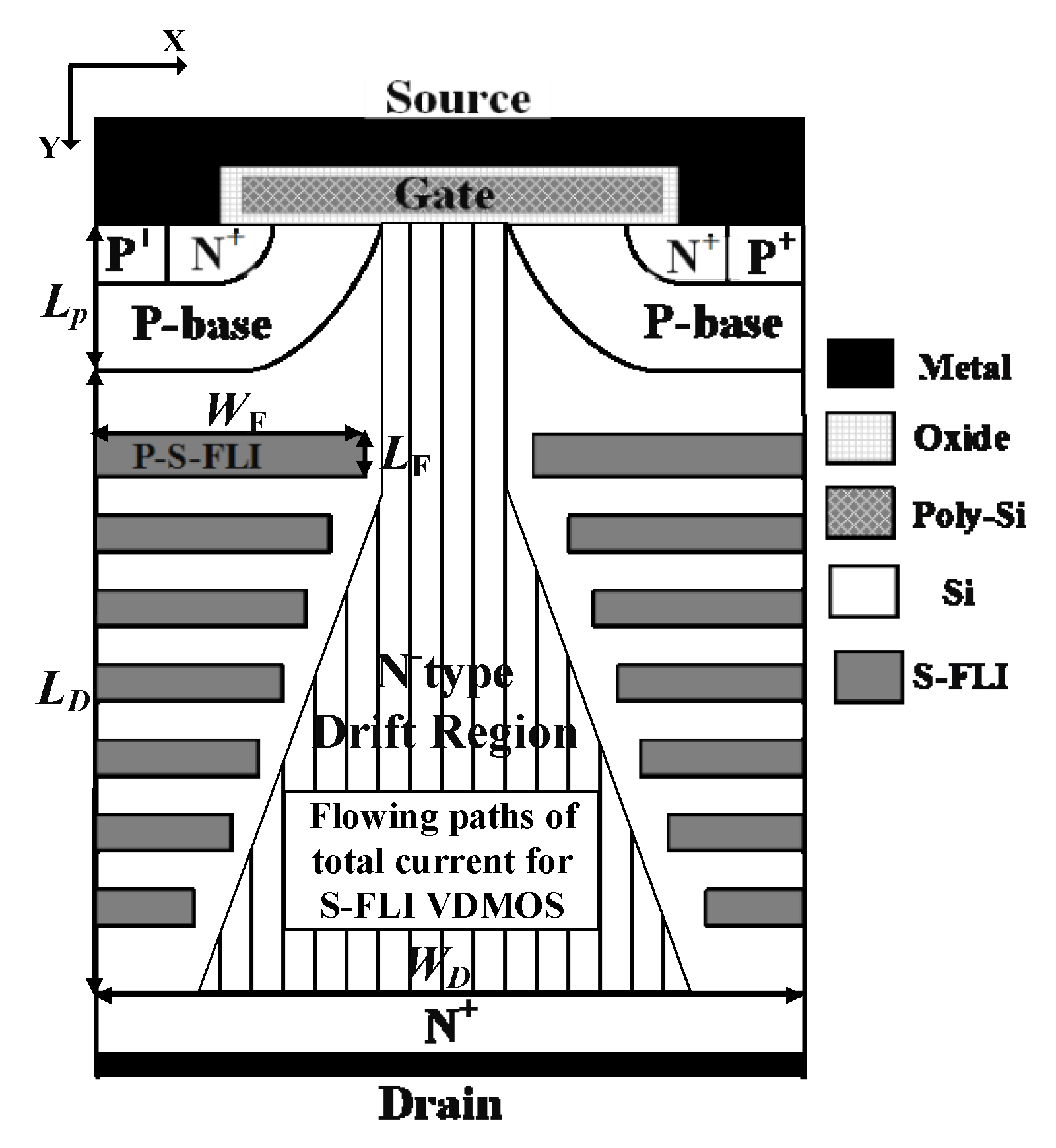

2. Device Structure and Description

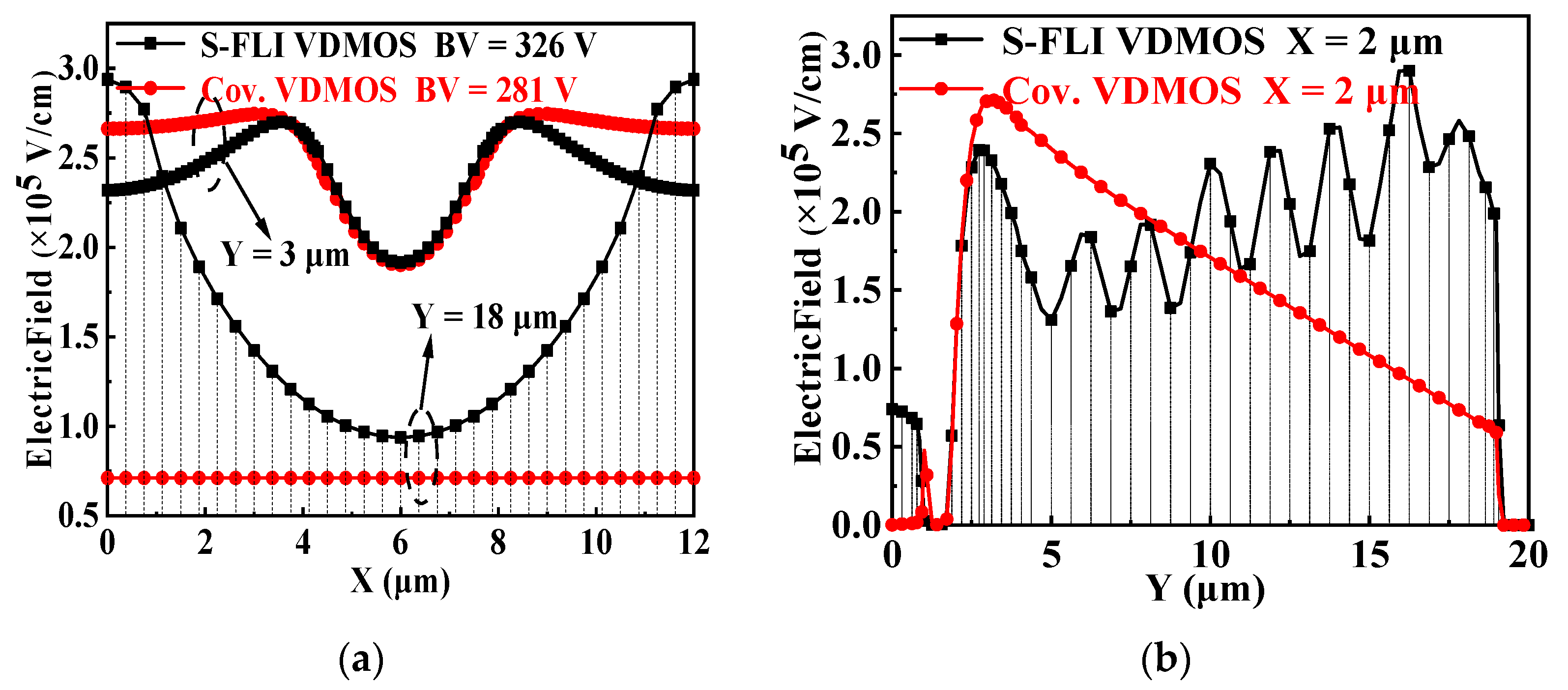

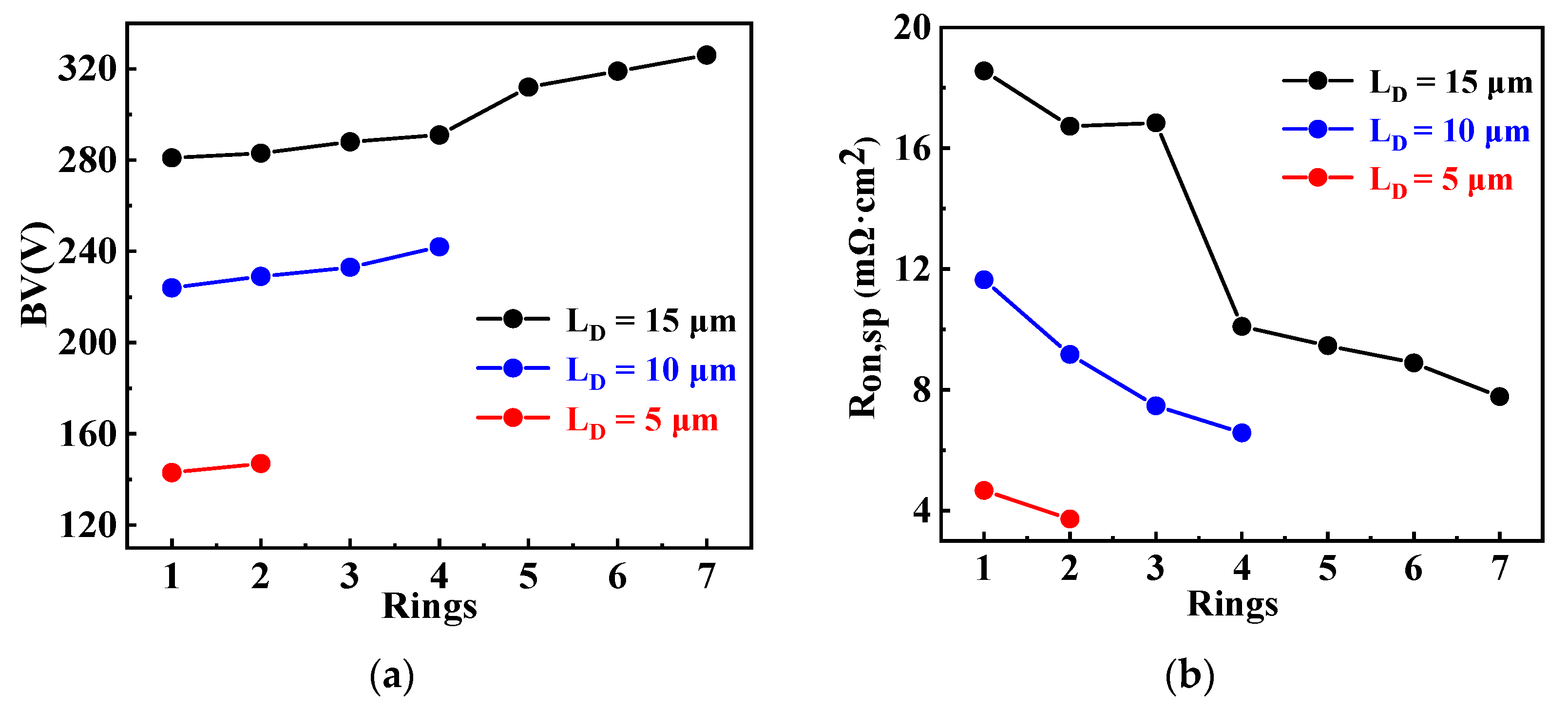

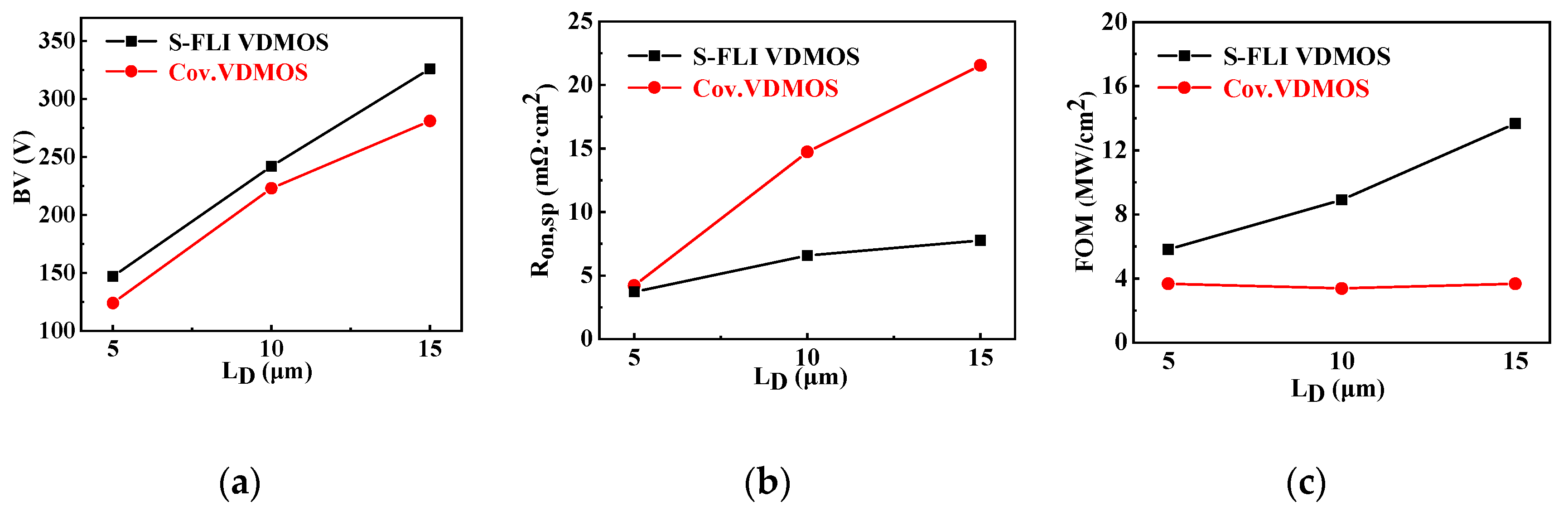

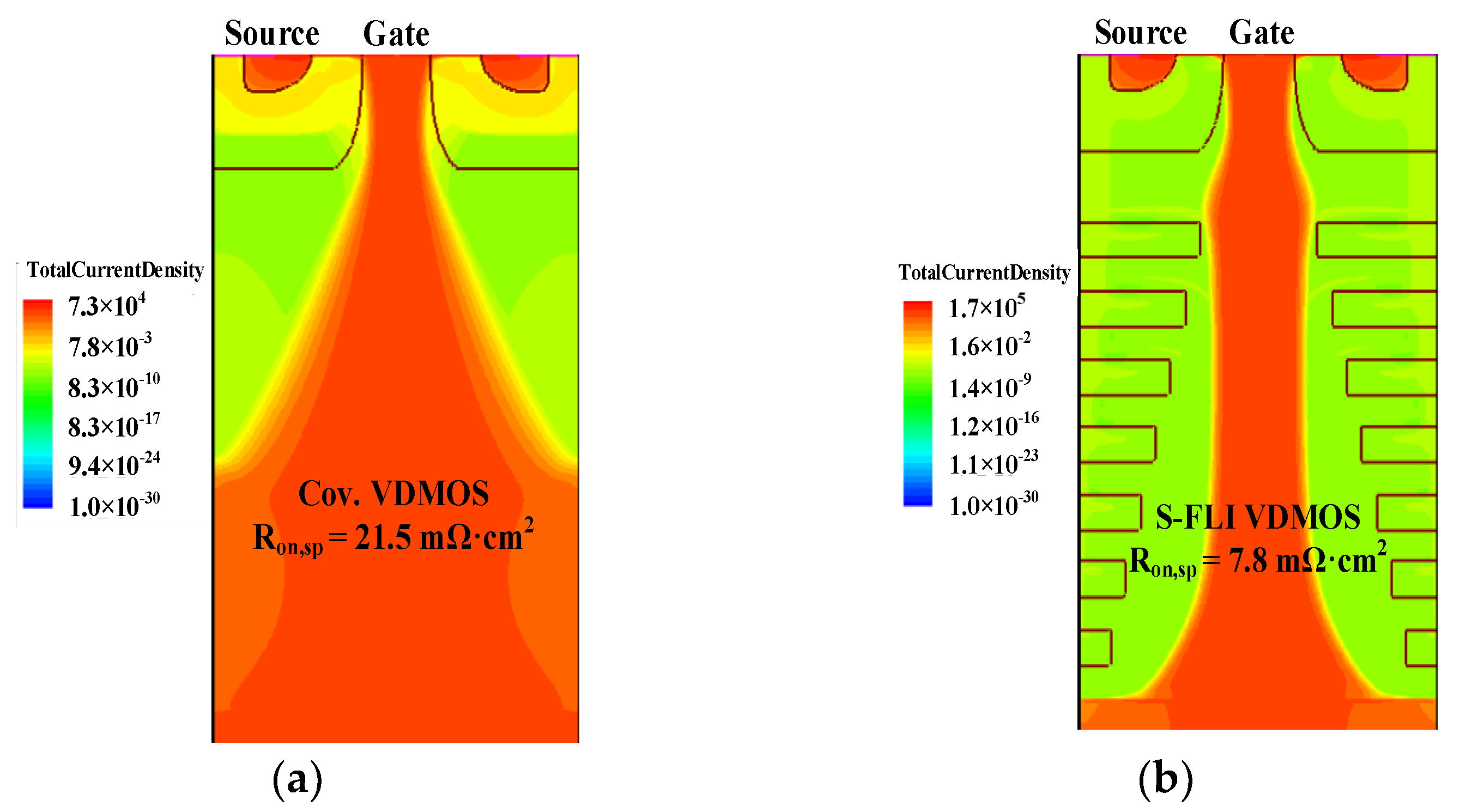

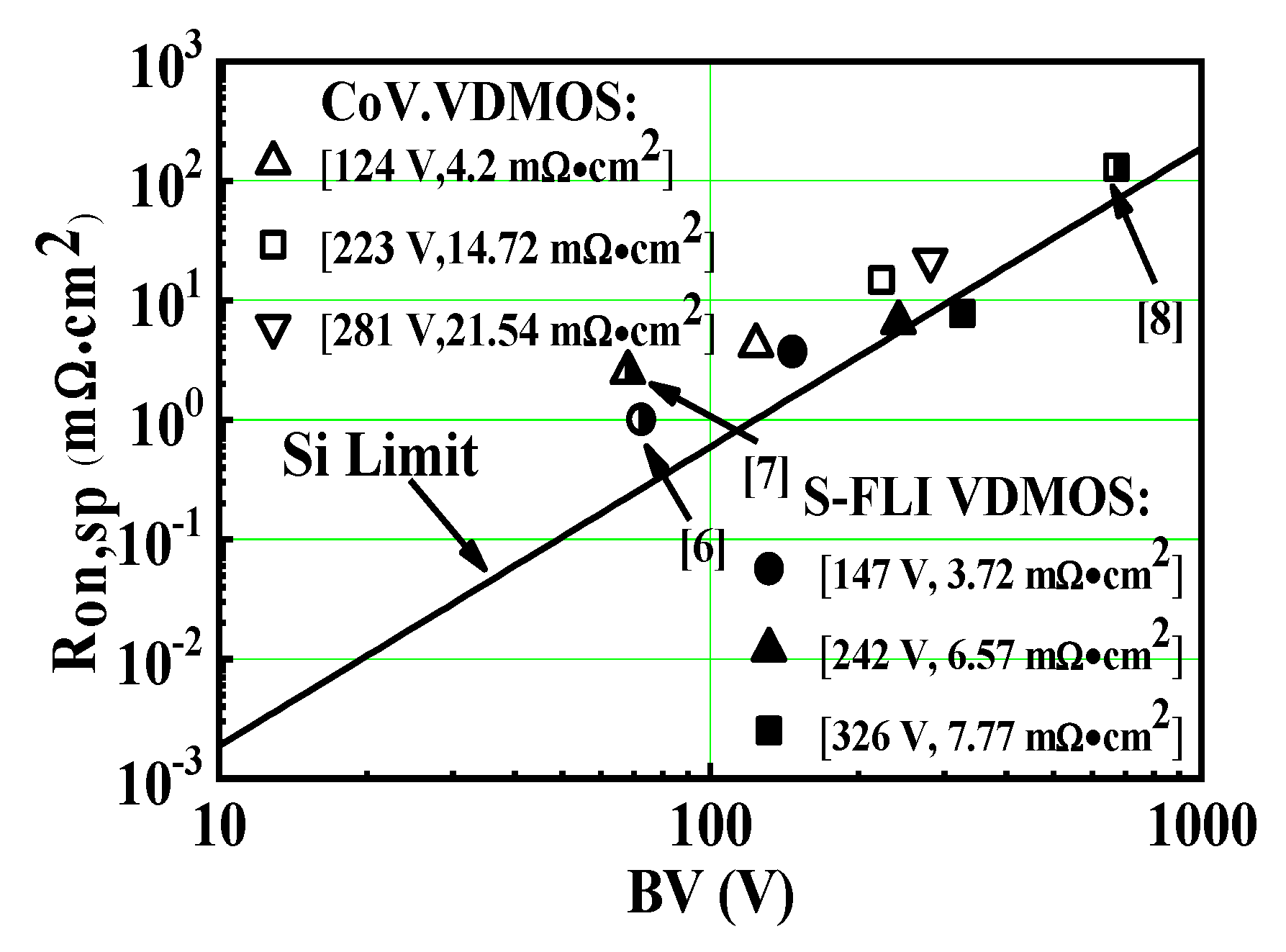

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Chen, W.Z.; Chen, J.J.; Lin, J.J. Simulation study on the high-k SJ-VDMOS with gradient side-wall. In Proceedings of the 41st International Convention on Information and Communication Technology, Electronics and Microelectronics (MIPRO), Opatija, Croatia, 21–25 May 2018. [Google Scholar]

- Williams, R.K.; Darwish, M.N.; Blanchard, R.A.; Siemieniec, R.; Rutter, P.; Kawaguchi, Y. The trench power MOSFET: Part II—Application Specific VDMOS, LDMOS, Packaging, and Reliability. IEEE Trans. Electron Devices 2017, 64, 692–712. [Google Scholar] [CrossRef]

- Williams, R.K.; Darwish, M.N.; Blanchard, R.A.; Siemieniec, R.; Rutter, P.; Kawaguchi, Y. The trench power MOSFET: Part I—History, technology, and prospects. IEEE Trans. Electron Devices 2017, 64, 674–691. [Google Scholar] [CrossRef]

- Udrea, F.; Deboy, G.; Fujihira, T. Superjunction Power Devices, History, Development, and Future Prospects. IEEE Trans. Electron Devices 2017, 64, 720–734. [Google Scholar] [CrossRef]

- Zhou, X.; Feng, Q.; Chen, X. The Study of P-pillar and Trench Technology in VDMOS. In Proceedings of the 2019 PhotonIcs & Electromagnetics Research Symposium-Spring (PIERS-Spring), Rome, Italy, 17–20 June 2019. [Google Scholar]

- Chen, Y.; Buddharaju, K.D.; Liang, Y.C.; Samudra, G.S. Superjunction Power LDMOS on Partial SOI Platform. In Proceedings of the 19th International Symposium on Power Semiconductor Devices and ICs, Jeju, Korea, 27–31 May 2007. [Google Scholar]

- Tam, W.; Siu, S.; Yang, B.; Kok, C.; Wong, H. Off-state drain breakdown mechanisms of VDMOS with anti-JFET implantation. Microelectron. Reliab. 2011, 51, 2064–2068. [Google Scholar] [CrossRef]

- Chen, X.; Feng, Q.; Jin, T. 600-V shielded trench split-gate VDMOS improving the figure of merit. Int. J. Electron. 2019, 107, 1083–1097. [Google Scholar] [CrossRef]

- Duan, B.; Wang, Y.; Wang, Y.; Dong, Z.; Yang, Y. Novel Vertical Power MOSFET with Step Hk Insulator Close to Super Junction Limit Relationship between Breakdown Voltage and Specific on-Resistance by Improving Electric Field Modulation. IEEE Trans. Electron Devices 2021, 68, 5048–5054. [Google Scholar] [CrossRef]

- Cao, Z.; Duan, B.; Shi, T.; Yuan, S.; Yang, Y. A superjunction U-MOSFET with SIPOS pillar breaking superjunction silicon limit by TCAD simulation study. IEEE Electron Device Lett. 2017, 38, 794–797. [Google Scholar] [CrossRef]

- Cezac, N.; Rossel, P.; Morancho, F.; Tranduc, H.; Peyre-Lavigne, A.; Pages, I. A new generation of power devices based on the concept of the “Floating Islands”. In Proceedings of the 22th International Conference on Microelectronics (Cat. No.00TH8400), Nis, Yugoslavia, 14–17 May 2000. [Google Scholar]

- Alves, S.; Morancho, F.; Reynes, J.-M.; Margheritta, J.; Deram, I.; Isoird, K.; Tranduc, H. Technological realization of low on-resistance FLYMOS/spl trade/transistors dedicated to automotive applications. In Proceedings of the European Conference on Power Electronics and Applications, Dresden, Germany, 11–14 September 2005. [Google Scholar]

- Vaid, R.; Padha, N. Factors Limiting the Device Performance in Power FLIMOSFET: 2-D Simulation Study. In Proceedings of the International Conference on Electrical Engineering, Lahore, Pakistan, 11–12 April 2007. [Google Scholar]

- Vaid, R.; Padha, N. Numerical Analysis of a Trench Gate FLIMOSFET with No Quasi-Saturation, Improved Specific on Resistance and Better Synchronous Rectifying Characteristics. In Proceedings of the 25th International Conference on Microelectronics, Belgrade, Serbia, 14–17 May 2006. [Google Scholar]

| Device | Cov. VDMOS | SJ VDMOS | S-FLI VDMOS |

|---|---|---|---|

| LD (μm) | 15 | 15 | 15 |

| Rings | / | / | 7 |

| ND (cm−3) | 0.7 × 1015 | 3.5 × 1015 | 3 × 1015 |

| Np (cm−3) | 5 × 1017 | 5 × 1017 | 5 × 1017 |

| NSUB (cm−3) | 1 × 1014 | 1 × 1014 | 1 × 1014 |

| Device | Cov. VDMOS | SJ VDMOS | S-FLI VDMOS |

|---|---|---|---|

| BV(V) | 281 | 326 | 326 |

| Ron,sp (mΩ·cm2) | 21.54 | 6.93 | 7.77 |

| FOM (MW/cm2) | 3.67 | 15.34 | 13.68 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhao, D.; Wang, Y.; Chen, Y.; Shao, J.; Fu, Z.; Duan, B.; Liu, F.; Li, X.; Li, T.; Yang, X.; et al. Novel Step Floating Islands VDMOS with Low Specific on-Resistance by TCAD Simulation. Micromachines 2022, 13, 573. https://doi.org/10.3390/mi13040573

Zhao D, Wang Y, Chen Y, Shao J, Fu Z, Duan B, Liu F, Li X, Li T, Yang X, et al. Novel Step Floating Islands VDMOS with Low Specific on-Resistance by TCAD Simulation. Micromachines. 2022; 13(4):573. https://doi.org/10.3390/mi13040573

Chicago/Turabian StyleZhao, Dongyan, Yubo Wang, Yanning Chen, Jin Shao, Zhen Fu, Baoxing Duan, Fang Liu, Xiuwei Li, Tenghao Li, Xin Yang, and et al. 2022. "Novel Step Floating Islands VDMOS with Low Specific on-Resistance by TCAD Simulation" Micromachines 13, no. 4: 573. https://doi.org/10.3390/mi13040573

APA StyleZhao, D., Wang, Y., Chen, Y., Shao, J., Fu, Z., Duan, B., Liu, F., Li, X., Li, T., Yang, X., Li, M., & Yang, Y. (2022). Novel Step Floating Islands VDMOS with Low Specific on-Resistance by TCAD Simulation. Micromachines, 13(4), 573. https://doi.org/10.3390/mi13040573