Abstract

Physical mechanisms underlying the multilevel resistive tuning over seven orders of magnitude in structures based on TiO2/Al2O3 bilayers, sandwiched between platinum electrodes, are responsible for the nonlinear dependence of the conductivity of intermediate resistance states on the writing voltage. To improve the linearity of the electric-field resistance tuning, we apply a contact engineering approach. For this purpose, platinum top electrodes were replaced with aluminum and copper ones to induce the oxygen-related electrochemical reactions at the interface with the Al2O3 switching layer of the structures. Based on experimental results, it was found that electrode material substitution provokes modification of the physical mechanism behind the resistive switching in TiO2/Al2O3 bilayers. In the case of aluminum electrodes, a memory window has been narrowed down to three orders of magnitude, while the linearity of resistance tuning was improved. For copper electrodes, a combination of effects related to metal ion diffusion with oxygen vacancies driven resistive switching was responsible for a rapid relaxation of intermediate resistance states in TiO2/Al2O3 bilayers.

1. Introduction

The fast growth of data that have to be processed by modern computing systems makes it necessary to search for effective solutions for increasing computing performance. A rapidly developing concept of memory-centric architectures, so-called in-memory and near-memory computing [1], promises to boost the performance of computing systems, overcoming memory bottlenecks of the von Neumann architectures. The goal of these computing design approaches is to minimize data movement as much as possible, performing the computations inside the memory (for in-memory computing) or bringing the memory close to logic chips as much as possible to maximize data bandwidth (for near-memory computing). The last approach requires the development of new processor-memory interfaces [2]. While for the first one, established memory technologies, such as SRAM, DRAM, ROM/RAM, or flash, could be used, or alternative memory types could be developed. For the established memory technologies, scaling remains the main issue for further computing transformation based on existing memory types. This circumstance gives rise to the development of the next-generation non-volatile memory technologies, such as ferroelectric field-effect transistor memory (FeFET), magnetoresistive random-access memory (MRAM), phase-change memory (PCV), and resistive random access memory (ReRAM). All of them are attractive combining the speed of SRAM and non-volatility of flash. Besides overcoming the von Neumann bottlenecks, memory-centric architectures substantially simplify the development of the modern non-traditional computation approach, or neuromorphic computing, which is based on mimicking the way that our brain uses for data processing [3]. In this approach, hardware-implemented neural networks perform computations on large amounts of data. It was demonstrated, that in-memory computing allows increasing application performance of machine learning algorithms in neuromorphic computing due to efficient implementation of fundamental operations of any typical neural network such as matrix-vector multiplication (MVM) [4,5]. For the moment, it is difficult to say which is the best memory type for in- and near-memory computing, but one of the most promising next-generation memory for neuromorphic computing is considered to be ReRAM [6,7]. Its integration into crossbar arrays offers highly-parallel and efficient hardware realization of MVM operations [8,9]. Among advantages of ReRAM devices are its extreme scaling, confirmed by fabricating devices with an electrode size in the range of 23 nm [10], low leakage, and potentially wide memory window (the experimentally demonstrated RON/ROFF ratio reaches 1011 [11]) with a possibility to obtain intermediate states between the RON and ROFF resistance. The high OFF/ON ratio provides a better sensing capability for operating in circuits and enables using large-scale crossbar arrays in hardware architecture. The intermediate resistance states offer the basis for multilevel logic, which is important for achieving high-density storage [12]. The main shortcomings of ReRAM are coming from relatively high write energy (2 nJ) and latency (100 ns), and, for some devices, their poor endurance [13]. In addition, one of the basic requirements for the successful implementation of ReRAM crossbars for MVM in neuromorphic computing systems is device linearity. Unfortunately, despite all the advantages, current ReRAM devices are highly nonlinear, which makes write operation and peripheral circuitry implementation in computing systems expensive.

Recently, we developed an approach to design thin-film TiO2/Al2O3 bilayer structures [14,15], exhibiting electric-field analog tuning of the nonvolatile resistance state in the range of seven orders of magnitude. Despite a wide memory window and the existence of multiple nonvolatile resistance states, TiO2/Al2O3 bilayer structures demonstrate nonlinear behavior originating from the initial difference in the resistive properties of TiO2 and Al2O3 layers. resulting in the nonlinear characteristics of the analog tuning [16]. Moreover, the presence of hydroxyl groups in functional oxide layers of our structures could not be eliminated due to the atomic layer deposition (ALD) technique, employed in the device fabrication. In combination with platinum electrodes, the development of oxygen-related electrochemical reactions involving OH-groups occurs at the interface with electrode regions owing to the catalytic activity of the platinum. The impact of oxygen-related electrochemical reactions on the oxygen vacancy density in the Al2O3 layer should also unpredictably contribute to the nonlinear behavior of TiO2/Al2O3 bilayer structures [17].

We assume that contact engineering could help to improve the linearity of the analog tuning of the resistance of our bilayer devices. Organization of the controlled electro-oxidation reactions between the metal electrode and the active (switching) oxide layer (in our case, Al2O3) of the bilayer structure may be considered as an additional capacity for oxygen-related ions, which could enhance the linearity of analog tuning. For this purpose, we replace the material of the top platinum electrode of TiO2/Al2O3 bilayers with chemically active materials, such as copper and aluminum. The choice of electrode materials was guided by their activity, based on the value of standard electrode potential. Aluminum is a good reducing agent with the negative value of the standard reduction potential (−1.66 V) and has a strong affinity to oxygen, while copper acts as an oxidizing agent with the positive value of standard electrode potential (+0.34 V) and is reduced to metal in aqueous electrolytes. Moreover, copper has been widely used as an electrode material in the metal-ion-based conductive bridge resistive random access memory (CBRAM), serving as a source of ions for conductive filament formation. This paper reports the results of the investigation of the effect of the electrode material on the resistive properties of TiO2/Al2O3 bilayer structures aiming to enhance the linearity of TiO2/Al2O3 bilayers while maintaining the wide memory window of the structures and keeping the possibility of analog tuning of the nonvolatile resistance state of the devices.

2. Materials and Methods

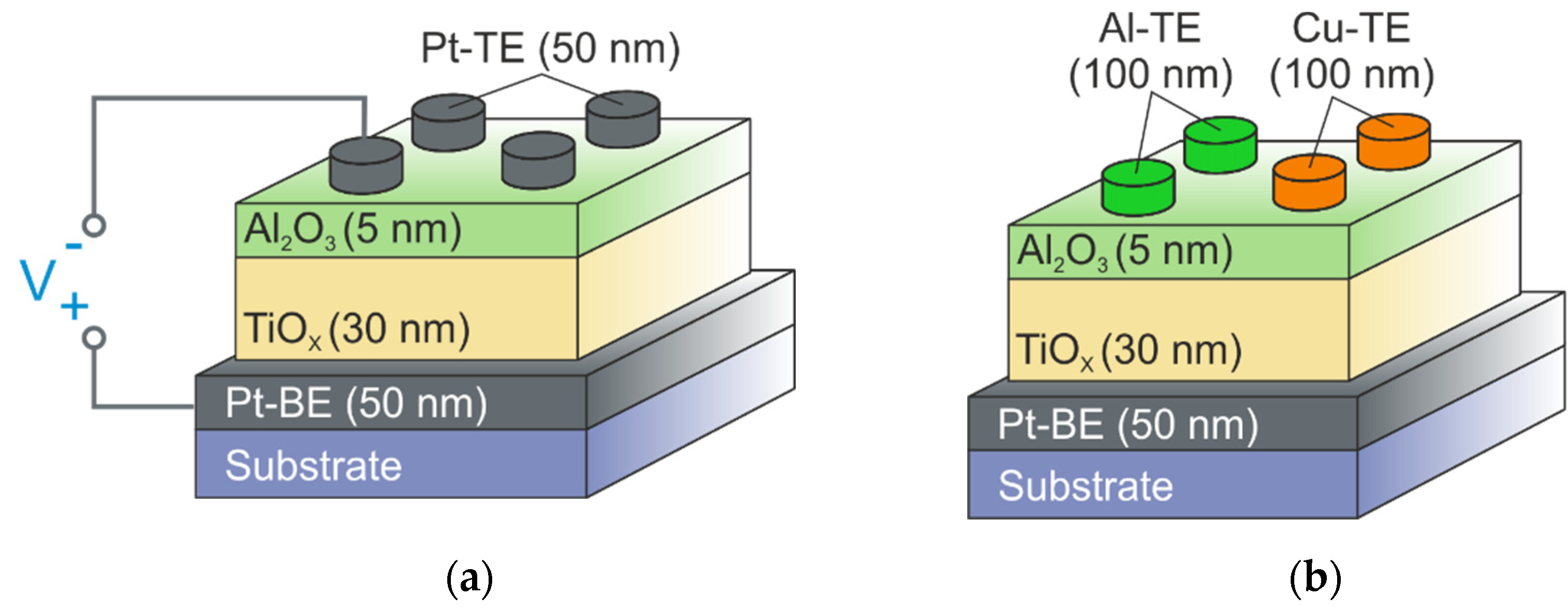

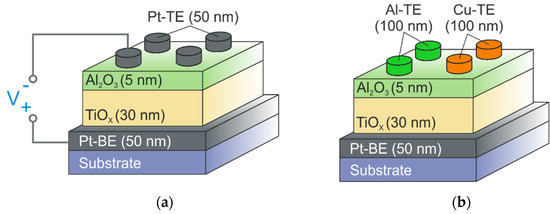

A 50 nm thick bottom platinum electrodes (Pt-BE) were deposited on a p-type Si/SiO2 substrate with a 10 nm thick titanium adhesive layer by DC magnetron sputtering at T = 150 °C. TiO2 (30 nm)/Al2O3 (5 nm) bilayers were grown via ALD on the mentioned substrate with TFS 200 system (Beneq, Espoo, Finland) at 150 °C using trimethylaluminum (Al(CH3)3) and titanium isopropoxide (Ti[OCH(CH3)2]4) as precursors and water vapor as an oxidizing agent. The thickness of the layers in Si/SiO2/Ti/Pt/TiO2/Al2O3 structures was controlled by scanning electron microscopy applied to a cross-section formed by focused ion beam (FEI, Helios NanoLab, Hillsboro, OR, USA). The surface topography of metal oxide layers was studied using atomic force microscopy (AFM) (Dimension 3100, Veeco, New York, NY, USA). In all fabricated metal-oxide bilayers, Al2O3 layers are amorphous. Post-deposition annealing was done at 200 °C for 30 s under ambient atmosphere. 50 nm thick Pt top electrodes (Pt-TE) and 100 nm thick Cu/Ni top electrodes (Cu-TE) were deposited by magnetron sputtering at T = 150 °C. 100 nm thick Al top electrodes (Al-TE) were deposited using electron beam evaporation at T = 150 °C. The top electrodes were patterned using a stencil mask, whose apertures were with the diameter of 350 μm for Pt-TE and Al-TE and 50 μm for Cu-TE (Figure 1).

Figure 1.

Schematic illustration of bilayer structures. (a) Si/SiO2/Ti/Pt-BE/TiO2/Al2O3 structures with platinum top electrodes; (b) Si/SiO2/Ti/Pt-BE/TiO2/Al2O3 structures with aluminum and copper top electrodes.

To verify the resistive properties and the role of every single metal-oxide layer in TiO2/Al2O3 bilayers, the Si/SiO2/Ti/Pt(50 nm)/TiO2(30 nm)/Pt(50 nm) and Si/SiO2/Ti/Pt(50 nm)/Al2O3(10 nm)/Pt(50 nm) structures were fabricated by the above-described method. To investigate resistive switching in the fabricated bilayer structures, I-V curves were measured using a Keithley 4200-SCS (Keithley Instruments Inc., Solon, OH, USA) semiconductor characterization system at ambient conditions using a two-probe configuration. For I-V measurements, tungsten needles were put in contact with the top and bottom electrodes of the structures. The operating voltage was applied to the top electrodes whereas the bottom electrodes were grounded. The resistance of structures was measured by using low (0.1 V) dc voltage.

3. Results and Discussions

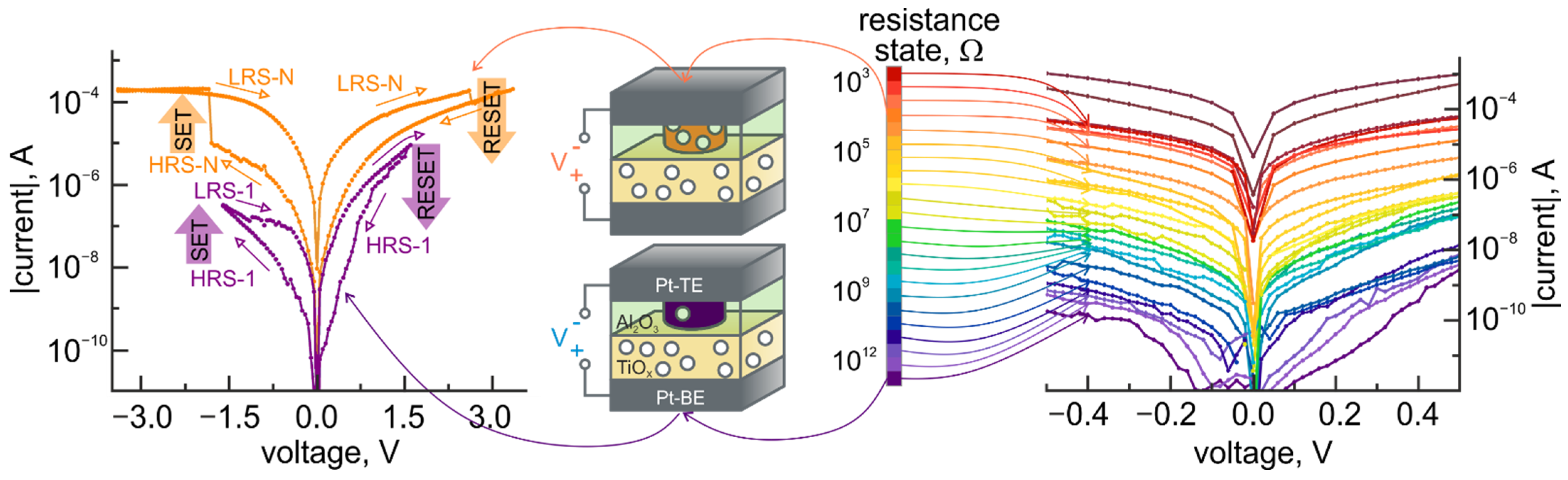

In Pt-BE/TiO2/Al2O3/Pt-TE bilayer structures, 5 nm thick Al2O3 layer plays a role of an active (or switching) layer, while 30 nm thick titanium oxide layer acts as a reservoir of oxygen vacancies (Figure 2).

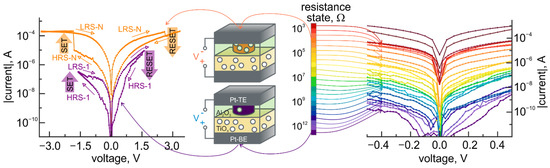

Figure 2.

Experimental I-V characteristics of Pt/TiO2/Al2O3/Pt structures with a combination of an electric-field analog tuning and a bipolar resistive switching and the schematic illustration of underlying physical mechanisms.

Under bias voltage application, oxygen vacancies drift in the Al2O3 layer, causing the reversible modification [18] of its properties and setting the resistance state of the structure. Relatively to a given resistance state determined by the value of bias voltage, a bipolar resistive switching takes place. An appearance of bipolar resistive switching is associated with electron-like processes related to the dominant transport mechanism in materials with high trap concentrations and accompanied by current pinching arising from the fluctuation instability in a direction perpendicular to the current [19]. The resistance of the TiO2/Al2O3 bilayer structures in the pristine state is 0.8 × 1012 Ω and is provided by the Al2O3 layer (the resistivity of Al2O3 is 1013–1015 Ω·cm as opposed to 104–107 Ω·cm for TiO2). In an analog tuning, the resistive properties of aluminum oxide are modified in a broad range (seven orders of magnitude) due to the variation of oxygen vacancy density [20]. The summary of resistive switching properties of TiO2/Al2O3 bilayer structures in comparison with the experimentally reported realization of multilevel memristors is presented in Table 1.

Table 1.

Comparison of the developed design of TiO2/Al2O3 bilayer structures with the performance of experimentally demonstrated multilevel memristors.

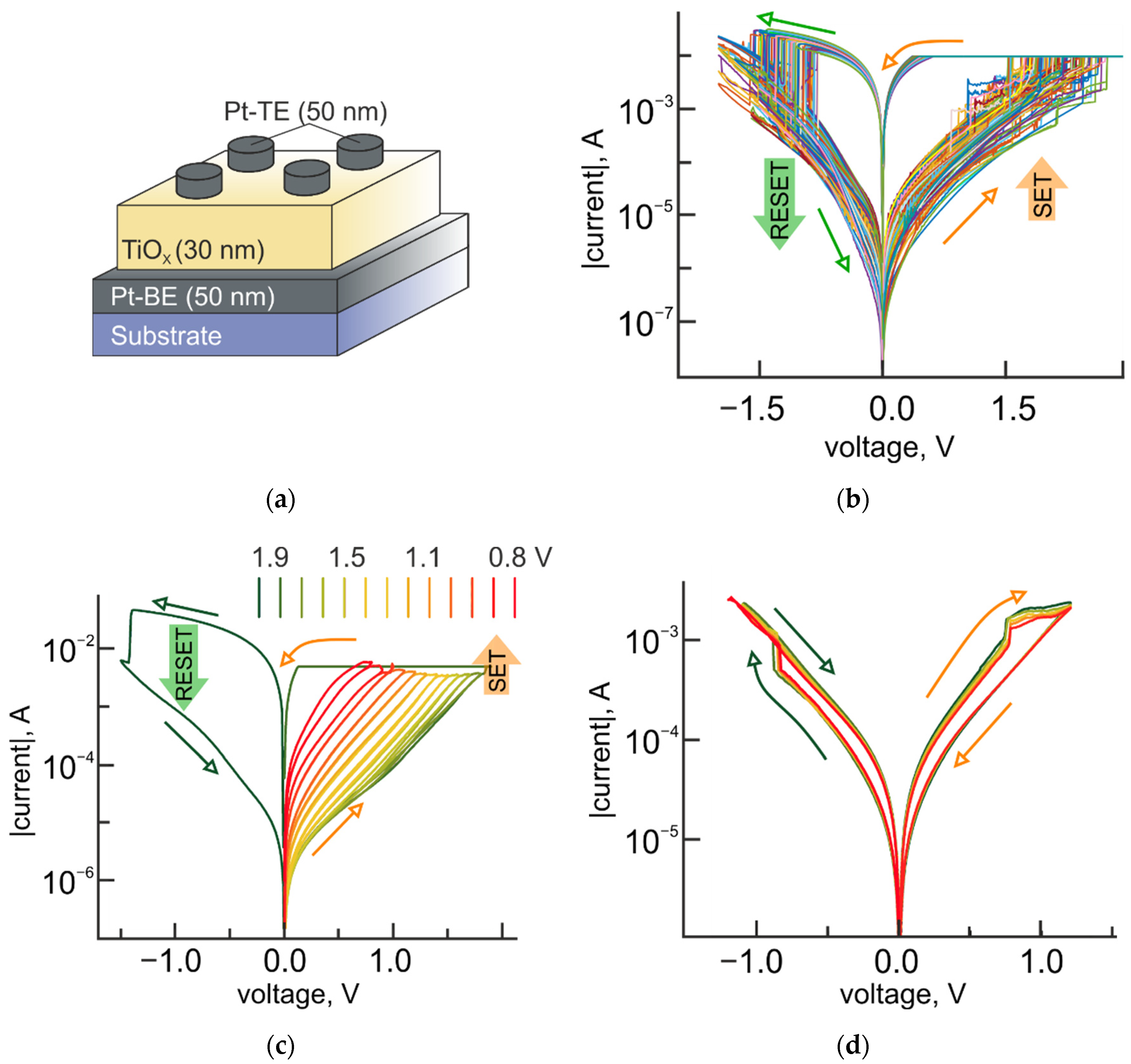

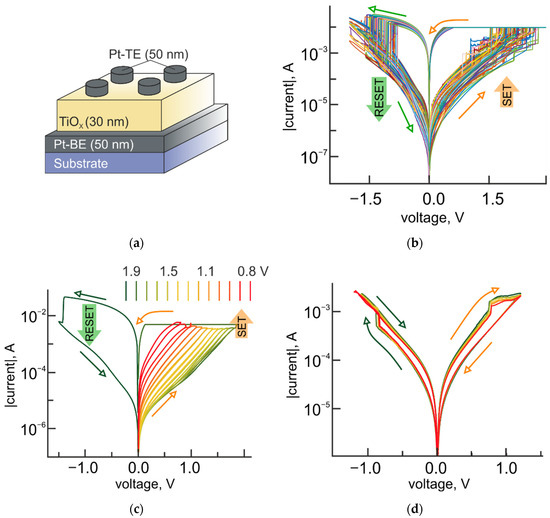

An appearance of the analog tuning regime in TiO2/Al2O3 bilayers is attributed to the properties of the TiO2 layer. In this case, it could be expected, that single-layer structures with a TiO2 switching layer (Figure 3a) should also be able to demonstrate an analog tuning behavior, coupled with the characteristic counterclockwise bipolar switching behavior (Figure 3b) and associated with the gradual decrease of the oxygen vacancy density [29]. Considering, that a bipolar resistive switching in Pt/TiO2(30 nm)/Pt structures are attributed to the formation of the conductive filamentary (CF) area, the gradual resistance tuning might be related to the variation of the oxygen vacancy concentration in the CF, formed during the SET process (switching from high resistance state (HRS) to low resistance state (LRS)). Indeed, the second nonvolatile resistive switching process with the switching direction of opposite polarity (i.e., clockwise) could be activated from the LRS of Pt/TiO2/Pt structures (Figure 3c) by applying a voltage to the Pt-TE less negative than the RESET value. The structure undergoes the transition into the intermediate resistance state, which could be tuned by applying a positive voltage to the Pt-TE less positive than the SET value. This additional clockwise bipolar resistive switching has a significantly lower value of ROFF/RON ratio (Figure 3d) and could be attributed to the oxide’s defects redistribution in the TiO2 layer, mainly in the CF/TE interface area, due to electrochemical reactions involving OH-groups [30,31]. This way, positively charged Pt-TE attracts negatively charged ions, such as OH−, O22−, triggering the electrochemical reaction (the value of standard electrode potential [32] is given in parentheses):

Figure 3.

Resistive switching modes in Pt/TiO2/Pt structures. (a) Schematic illustration of Pt/TiO2/Pt structure; (b) Experimental I-V curves for the counterclockwise filamentary-type bipolar resistive switching; (c) Experimental observation of the coexistence of the counterclockwise and the clockwise bipolar resistive switching modes; (d) Experimental I-V curves for the clockwise bipolar resistive switching for 5 consequent switching cycles.

The developed oxygen reduction reaction induces the oxidation of Ti in a TiO2 switching layer, and reduces the concentration of oxygen vacancies related to Ti3+ in the next possible way [33]:

This leads to the increase of the stoichiometry of TiO2–x in the CF area at the interface with the Pt-TE and results in increasing the structure resistance, i.e. switching to the HRS. The clockwise switching to the LRS takes place under the reverse polarity of the voltage bias and is accompanied by the electrochemical reactions with Ti4+ reduction to Ti3+ state.

When the conductivity of the HRS for a clockwise resistive switching reaches the value of HRS for the counterclockwise bipolar switching, the unipolar switching to the LRS of the counterclockwise switching mode occurs. Both the clockwise and the counterclockwise resistive switching modes do not obstruct each other. Moreover, the clockwise resistive switching leads to an appearance of intermediate resistance states in the range between the LRS and HRS of the counterclockwise bipolar switching.

It should be noted, that despite the existence of intermediate states in single-layer Pt/TiO2/Pt structures, the highest possible memory window of these systems is limited by the ROFF/RON ratio of the counterclockwise bipolar resistive switching and does not exceed two-three orders of magnitude.

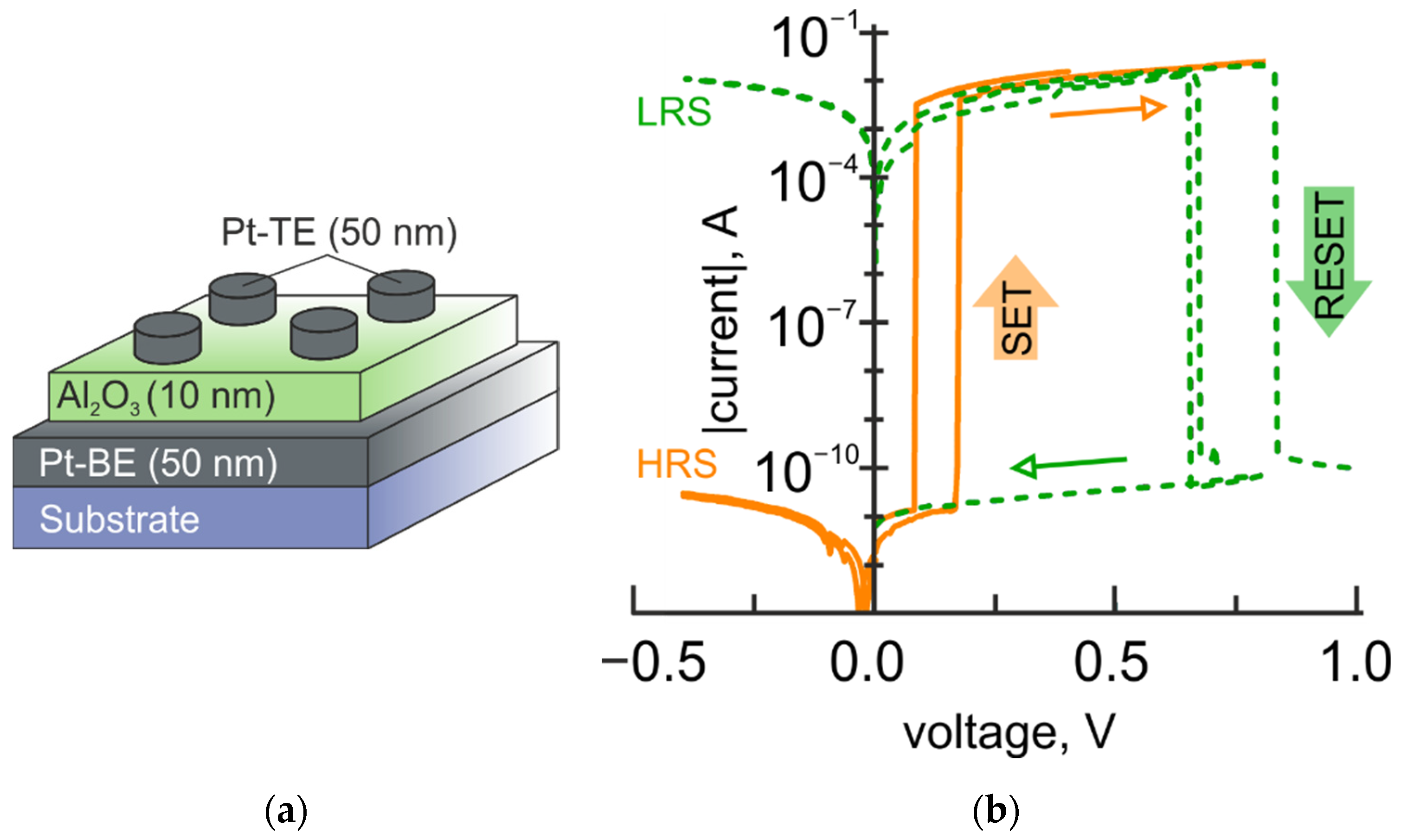

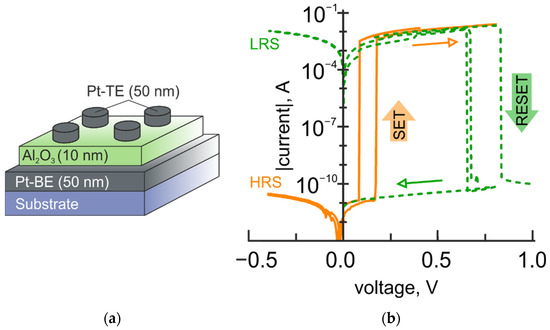

Adding the Al2O3 layer to the TiO2 layer allows extending the range of the nonvolatile tuning of the structural resistance to seven orders of magnitude. Thus, in Pt-BE/TiO2/Al2O3(10 nm)/Pt-TE bilayer structures, aluminum oxide plays the role of an active (switching) layer [15]. This statement is supported by experimental observation of the resistive switching in single-layer Pt/Al2O3/Pt structures with an ROFF/RON ratio of about seven orders of magnitude (Figure 4). More details of the resistive switching in single-layer Pt/Al2O3/Pt structures can be found elsewhere [17].

Figure 4.

Resistive switching in Pt/Al2O3/Pt structures. (a) Schematic illustration of Pt/Al2O3/Pt structures; (b) Experimental I-V curves for the resistive switching in Pt/Al2O3/Pt structures with a memory window of seven orders of magnitude.

The conductivity of Pt-BE/TiO2/Al2O3/Pt-TE bilayer structures is related to trap-assisted space-charge-limited currents (SCLC) in high-resistivity materials with low carrier mobility and long dielectric relaxation time. Traps or localized states within the Al2O3 bandgap are formed by the oxygen vacancies. The SCLC transport mechanism is manifested in power dependence of current on voltage with a changeable degree of power [15]. Both bipolar and multilevel resistive switching are clockwise for these structures. The first bipolar resistive switching, associated with the resistance state with the lowest conductivity (HRS-1 in Figure 2), is accompanied by the formation of the filamentary conductive area in the Al2O3 layer. SET process of this bipolar resistive switching happens at high injection levels, at which the traps are filled, reaching the trap-filled limit (TFL) [19]. Thus, the experimentally observed I-V curves for HRS are linearized in a double logarithmic scale with several characteristic parts, corresponding to linear, square, and power dependences (with n ≥ 3). While for LRS, the transition to the trap-free-square-law region takes place and experimental I-V curves exhibit only linear and square dependences. The limiting condition for the development of the conductive filament in the Al2O3 layer is a transition to the TFL regime, i.e., the trap filling process supplies positive feedback for the filament development [19].

An appearance of the next conductive state in the Pt-BE/TiO2/Al2O3/Pt-TE bilayer structures is related to an increase of the oxygen vacancy concentration in the filamentary conductive area of the Al2O3 due to the oxygen vacancies drift in from the TiO2 layer. In general terms, discretization of resistance states is defined by the statistically significant difference in the value of the resistivity (). For the hopping conductivity, the resistivity could be estimated based on percolation theory [34] and is given by: (where is Bohr radius and N is the oxygen vacancy concentration). Thus, the resistivity of the bilayer structure nonlinearly depends on the oxygen vacancy density in the CF area in the Al2O3 layer. The voltage drop across the Al2O3 layer in a bilayer structure is determined by the ratio of the resistance of TiO2 and Al2O3 layers (the resistivity of Al2O3 is 1013–1015 Ω cm as opposed to 104–107 Ω cm for TiO2), while the resistance of the Al2O3 layer is driven by the field-controlled oxygen vacancy drift and nonlinearly depends on the oxygen vacancy concentration in the Al2O3 layer. The combination of these factors results in the nonlinear characteristics of the tuning of the resistance state in Pt-BE/TiO2/Al2O3/Pt-TE bilayer structures.

In Pt-BE/TiO2/Al2O3/Al-TE bilayer structures, an impact from electrochemical reactions involving OH-groups at the interface with the top electrode is expected and can be defined in general as

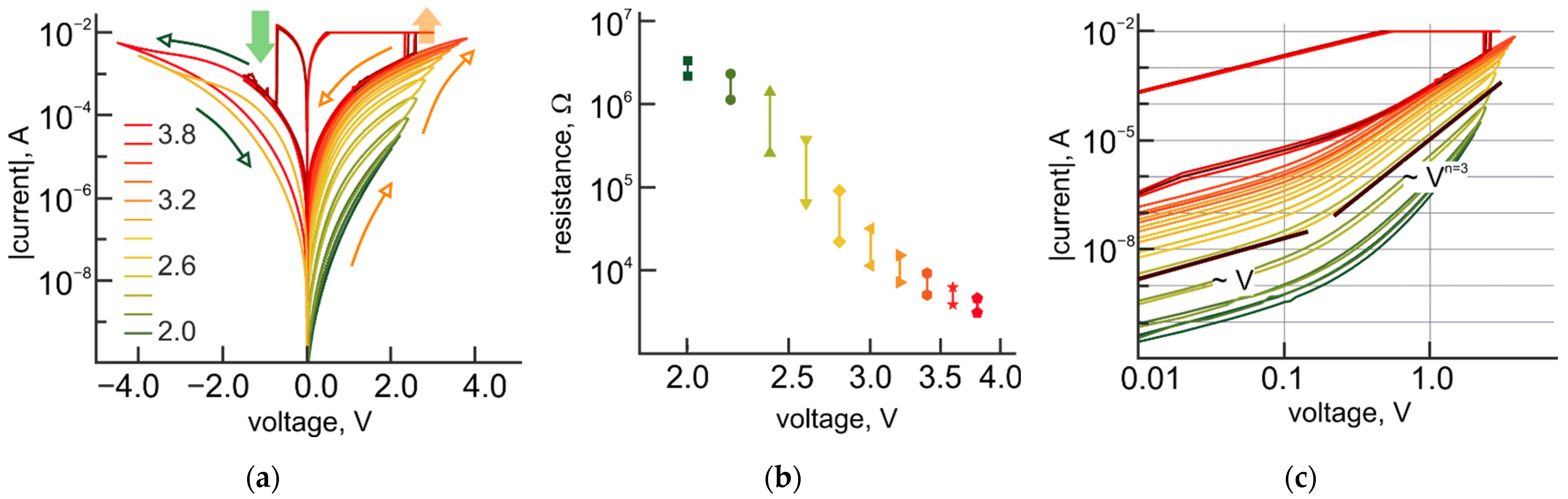

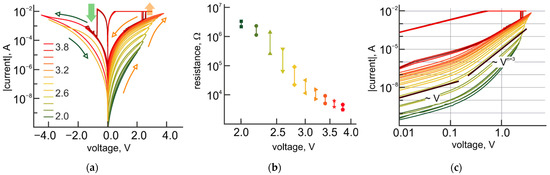

Indeed, the experimental I-V curves provide evidence of memristive behavior starting from the values of the applied voltage, which are approximately equal to the standard electrode potentials of reactions, mentioned above. The resistance state of the structures is gradually decreasing with increasing the value of the applied voltage above the standard electrode potentials (Figure 5a). Analog reversible tuning of the resistance is observed within the range of more than three orders of magnitude until the current through the bilayer structure exceeds the level of 10 mA. At this current, the switching to the LRS, associated with the characteristic counterclockwise bipolar switching behavior of the TiO2 layer, happens (Figure 5a).

Figure 5.

Resistive switching modes in Pt-BE/TiO2/Al2O3/Al-TE bilayer structures. (a) Experimental I-V curves for gradual resistance tuning as a function of voltage combined with a bipolar resistive switching in Pt-BE/TiO2/Al2O3/Al-TE structures; (b) Dependence of ROFF/RON ratio on the resistance state of Pt-BE/TiO2/Al2O3/Al-TE structures; (c) I-V curves from (a) in a double logarithmic scale.

Relatively to the given resistance state, tuned by applying a positive voltage to the Al-TE and determined by its value (2.3 to 4 V), a bipolar counterclockwise resistive switching takes place, accompanied by the next electrochemical reactions

The ROFF/RON ratio for this bipolar resistive switching varies with the resistance state of the structure from 1.5 to 5.5 (Figure 5b). The highest value of the ROFF/RON ratio corresponds to the intermediate range of the analog tuning, while at the edges of the tuning range the ROFF/RON ratio decreases to 1.5. I-V characteristics for both HRS and LRS are nonlinear, asymmetrical (regarding the polarity of applied bias), and could be linearized in a double logarithmic scale with several characteristic parts (), corresponding to linear and power dependences with n = 3. Compared to Pt-BE/TiO2/Al2O3/Pt-TE bilayer structures, for which the degree of power dependence of the corresponding part of I-V curves for HRS differs from those for LRS, Pt-BE/TiO2/Al2O3/Al-TE bilayer structures exhibit the same degree of power dependence for both HRS and LRS (Figure 5c). Previous experimental evidence [15,19] suggests the dominant role of electronic processes in the bipolar resistive switching in bilayer structures with platinum electrodes. The transition from the HRS to the LRS is associated with reaching the trap-filling limit (TFL) in the local conductive filamentary area at a high injection level. At reaching TFL, the transition to the trap-free-square law takes place and the I-V curves for LRS follow the square law, while for HRS the characteristic part for power dependence has a degree of power n ≥ 3. The same degree of power dependence for both HRS and LRS in Pt-BE/TiO2/Al2O3/Al-TE bilayer structures indicates changes in the mechanism of the bipolar resistive switching from electronic one to electrochemically driven. Reducing the ROFF/RON ratio from 1–2 orders of magnitude for structures with Pt-TE to less than 10 for Al-TE provides further evidence in support of this assumption. However, it should be noted, that dominance of electrochemically driven processes in the bipolar resistive switching of bilayer structures with Al-TE brings about linearity in the dependence of the resistance state on the voltage at the analog tuning of the resistance.

Copper is widely used as an electrode material in CBRAM devices due to its high metal diffusivity with low activation energy. At the same time, Al2O3 has advantages when used in conjunction with Cu electrodes, allowing to control the Cu migration and enhance the device endurance. The high energy gap of Al2O3 ensures the maintenance of the high ROFF/RON ratio, whereas its high thermal conductivity (15 W/mK) facilitates the formation of Cu ion conductive filament [35]. In addition, oxidation of Cu electrode at the Al2O3/Cu-TE interface provides a higher migration rate of Cu2+ ions due to the lower Cu-O bond energy compared with that of Cu-Cu metallic bond (1.5 eV vs. 2.0 eV [36]).

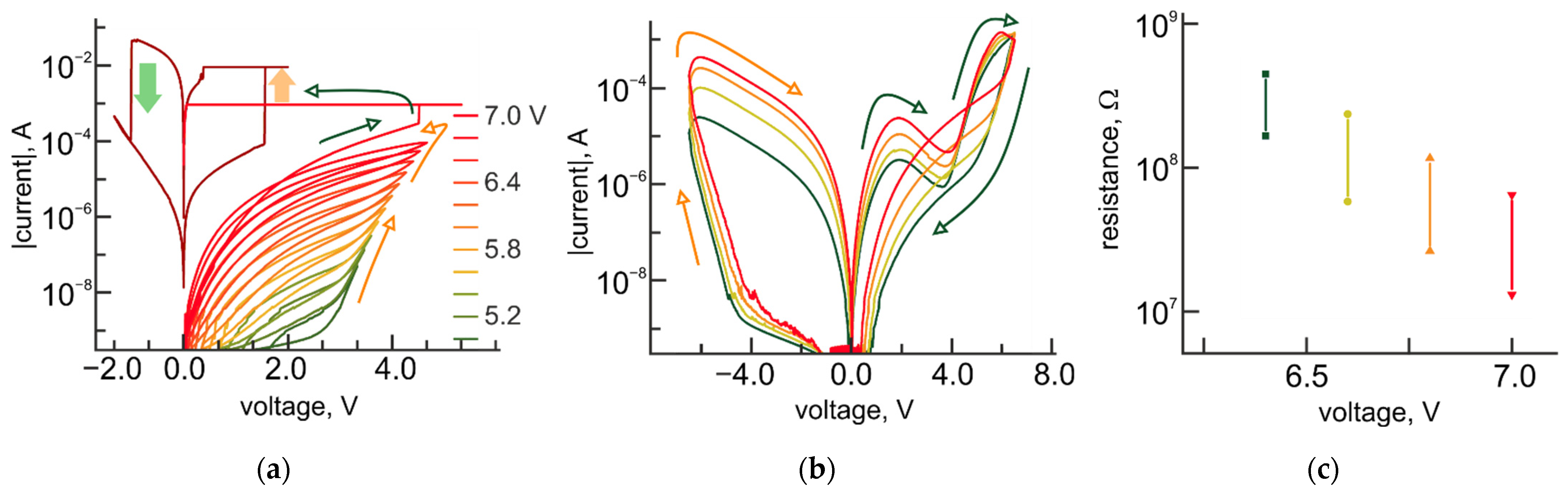

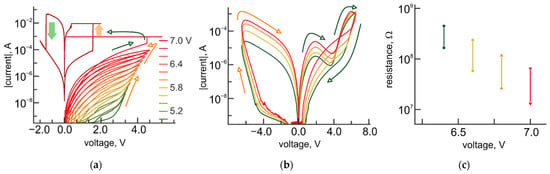

For TiO2/Al2O3 bilayer structures, contributions from the competition of oxygen vacancies and Cu ions to the formation of the conductive filamentary area in the Al2O3 layer are expected to take place. Indeed, if the thickness of the Al2O3 layer does not exceed 5 nm, the gradual resistance tuning is experimentally observed at negative bias applied to the Cu-TE and could be associated with the formation of oxygen vacancy CF. For bilayer structures with larger thicknesses, tuning of the resistance takes place at the positive polarity of applied bias and is related to the formation of Cu ion CF (Figure 6a).

Figure 6.

Resistive switching modes in Pt-BE/TiO2/Al2O3/Cu-TE bilayer structures. (a) Experimental I-V curves for a gradual resistance tuning as a function of voltage resistive switching in Pt-BE/TiO2/Al2O3/Cu-TE for structures with 7-nm thick Al2O3 layer; (b) Experimental I-V curves for the bipolar resistance switching in Pt-BE/TiO2/Al2O3/Cu-TE for structures with 5 nm-thick Al2O3 layer; (c) Dependence of ROFF/RON ratio on the resistance state of Pt-BE/TiO2/Al2O3/Cu-TE structures.

The development of pinched I-V hysteresis occurs starting with sufficiently high voltage bias (5 V), indicating the impact of thermal or thermochemical processes associated with ion diffusion.

Interestingly, at bipolar resistive switching in Pt-BE/TiO2/Al2O3/Cu-TE bilayer structures, relative to the given resistance state, an appearance of the characteristic part of I-V curves with negative differential resistance is experimentally observed on the LRS branch of I-V curves corresponding to the polarity of reset process (Figure 6b). We assume, that the region of the I-V curve with a negative slope (for 5 nm-thick Al2O3 layer) reflects the situation when the oxygen vacancy CF dissolves faster than Cu ion CF forms.

The switching to the LRS, associated with the characteristic counterclockwise bipolar switching behavior of the TiO2 layer, happens when the level of the current through the bilayer structure exceeds 1 mA and only at the positive polarity of applied bias. It should be noted, that the range of applied voltages for the resistance tuning of this type of structure is shifted toward higher values (from 5 to 7 V), in comparison with Pt-BE/TiO2/Al2O3/Al-TE bilayer structures. At the same time, the ROFF/RON ratio for bipolar resistive switching does not significantly vary with the resistance of the structure and is approximately equal to 5 (Figure 6c).

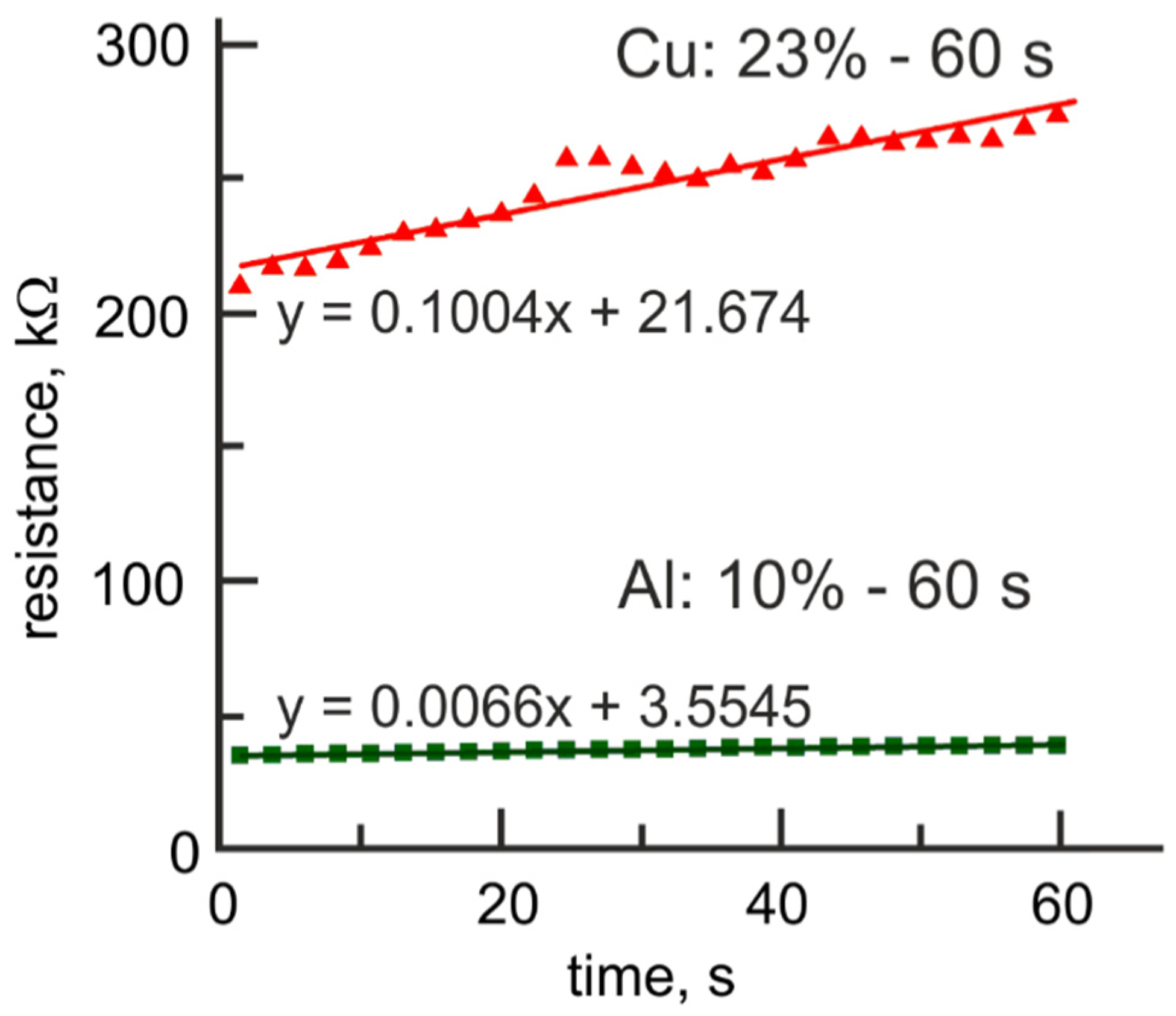

Despite the improved linearity of the resistance tuning, the major shortcoming of Pt-BE/TiO2/Al2O3/Cu-TE bilayer structures is a rapid degradation of intermediate resistance states with time (relaxation effect) (Figure 7), attributed to an impact from the electrochemical reactions at the Al2O3/Cu-TE interface:

Figure 7.

Time evolution of intermediate resistance state for Pt-BE/TiO2/Al2O3 bilayer structures with aluminum and copper top electrodes.

The values of standard electrode potential for these reactions suggest that in the presence of OH-groups in the Al2O3 layer copper oxidation/reduction processes strongly affect the original structure of conductive filament.

In summary, according to the experimental results, the material of the top electrode significantly influences the mechanism and operating parameters of nonvolatile resistive switching in TiO2/Al2O3-based bilayer structures. In the case of Al-TE, the prevalence of oxygen-related electrochemical reactions suppresses the development of the electronic mechanism of resistive switching, previously observed for Pt-BE/TiO2/Al2O3/Pt-TE structures. Switching to the electrochemical mechanism of resistive tuning results in the narrowing of a memory window down from seven to three orders of magnitude, while improving the linearity of the resistance tuning at the same range of operation voltages. The specificity of Cu-TE leads to an appearance of mixed effects, induced by Cu ion migration in the active Al2O3 layer of the structure on the one side, and oxygen vacancy-related formation of CF in the Al2O3 layer, on the other side. The combination of these competitive effects strongly deteriorates the performance of the TiO2/Al2O3 bilayer structures, shifting the operating voltages to higher values and causing the rapid relaxation of the intermediate resistance states in Pt-BE/TiO2/Al2O3/Cu-TE structures.

Comparison of the device performance between TiO2/Al2O3 bilayer structures with Al-TE and Cu-TE and those from recent reports (Table 1) shows that despite narrowing of the memory window when using Al as a top electrode material, the ROFF/RON ratio for those devices remains the highest among experimentally demonstrated multilevel memristors with analog tuning between the nonvolatile resistance states. According to the same Table 1, an attempt to combine the Cu ion migration together with oxygen-related electrochemical reactions at the top electrode interface in Pt-BE/TiO2/Al2O3/Cu-TE structures brings no benefits to the device performance.

4. Conclusions

Concluding, electrochemical reactions involving OH-groups could be experimentally observed in ALD deposited aluminum and titanium oxide layers in both single-layer and bilayer structures with resistive switching effects. In single-layer Pt/TiO2/Pt structures oxygen-related electrochemical reactions induce an analog tuning from LRS (50 Ω) to HRS (50 kΩ). Single-layer Pt/Al2O3/Pt structures show the abrupt transition from HRS (~1012 Ω) to LRS (~104–103 Ω) without controllable switching to intermediate resistance states. The resistance state of the combination of two oxide layers (TiO2 and Al2O3) in a bilayer structure, sandwiched between platinum electrodes, can be electrically tuned in an analog manner over seven orders of magnitude (from ~1012 Ω up to ~105 Ω). The resistance of intermediate states in bilayer structures is determined by the concentration of oxygen vacancies in the active layer of Al2O3. Unfortunately, the initial difference in the resistive properties of TiO2 and Al2O3 layers causes the nonlinear dependence of the state conductivity on the switching voltage in the analog regime. The contribution of the electrochemical reactions at the Al2O3/TE interface, induced by top electrode material substitution, may improve the linearity of analog nonvolatile tuning, but gives rise to the transformation of the resistive switching mechanism of bilayer structures. This, in turn, results in a separate observation of resistive switching effects, attributed to either Al2O3 or TiO2 layers of bilayer structures. Consequently, the range of the nonvolatile analog tuning of the resistance has narrowed down to three orders of magnitude (from ~106 Ω to ~103 Ω) in the case of Al-TE, together with the decreasing of the ROFF/RON ratio of the bipolar resistive switching (relatively to the given resistance state) from one-two orders of magnitude to 5. A combination of effects related to metal ion diffusion with oxygen vacancies driven resistive switching in TiO2/Al2O3 bilayers with Cu-TE, in addition to narrowing of the range of analog tuning (from ~108 Ω to ~107–106 Ω), provokes a rapid relaxation of intermediate resistance states, shifting switching voltages toward higher values (from 2–4 V for bilayers with Pt-TE and Al-TE to 6–7 V).

Author Contributions

Conceptualization, N.A. and A.R.; methodology, D.M., A.R., and D.C.; validation, N.A. and V.L.; formal analysis, M.G. and N.A.; investigation, N.A., M.G., and D.M.; data curation, N.A.; writing—original draft preparation, N.A.; writing—review and editing, N.A. and V.L.; visualization, M.G.; supervision, V.L. All authors have read and agreed to the published version of the manuscript.

Funding

This research was funded by the Ministry of Science and Higher Education of the Russian Federation, grant number FSEE-2020-0013.

Data Availability Statement

The data that support the findings of this study are available from the corresponding author, upon reasonable request.

Conflicts of Interest

The authors declare no conflict of interest. The funders had no role in the design of the study; in the collection, analyses, or interpretation of data; in the writing of the manuscript, or in the decision to publish the results.

References

- Karunaratne, G.; Le Gallo, M.; Cherubini, G.; Benini, L.; Rahimi, A.; Sebastian, A. In-memory hyperdimensional computing. Nat. Electron. 2020, 3, 327–337. [Google Scholar] [CrossRef]

- Handy, J.; Coughlin, T. The future of low-latency memory. Available online: Objective-analysis.com/white-papers-2 (accessed on 1 November 2021).

- Basheer, I.; Hajmeer, M. Artificial neural networks: Fundamentals, computing, design, and application. J. Microbiol. Methods 2000, 43, 3–31. [Google Scholar] [CrossRef]

- Gokmen, T.; Vlasov, Y. Acceleration of deep neural network training with resistive cross-point devices: Design considerations. Front. Neurosci. 2016, 10, 333. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Ankit, A.; Hajj, I.E.I.; Chalamalasetti, S.R.; Ndu, G.; Foltin, M.; Williams, R.S.; Faraboschi, P.; Hwu, W.M.; Strachan, J.P.; Roy, K. PUMA: A Programmable Ultra-efficient Memristor-based Accelerator for Machine Learning Inference. In Proceedings of the Twenty-Fourth International Conference on Architectural Support for Programming Languages and Operating Systems, Providence, RI, USA, 13–17 April 2019; pp. 715–731. [Google Scholar]

- Rehman, M.M.; Rehman, H.M.M.U.; Gul, J.Z.; Kim, W.Y.; Karimov, K.S.; Ahmed, N. Decade of 2D-materials-based RRAM devices: A review. Sci. Technol. Adv. Mater. 2020, 21, 147–186. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Rehman, M.M.; ur Rehman, H.M.M.; Kim, W.Y.; Sherazi, S.S.H.; Rao, M.W.; Khan, M.; Muhammad, Z. Biomaterial-based nonvolatile resistive memory devices toward ecofriendliness and biocompatibility. ACS Appl. Electron. Mater. 2021, 3, 2832–2861. [Google Scholar] [CrossRef]

- Shafiee, A.; Nag, A.; Muralimanohar, N.; Balasubramonian, R.; Strachan, J.P.; Hu, M.; Williams, R.S.; Srikumar, V. ISAAC: A convolutional neural network accelerator with in-situ analog arithmetic in crossbars. In Proceedings of the 43rd International Symposium on Computer Architecture, Seoul, Korea, 16–22 June 2016. [Google Scholar]

- Yao, P.; Wu, H.; Gao, B.; Tang, J.; Zhang, Q.; Zhang, W.; Yang, J.J.; Qian, H. Fully hardware-implemented memristor convolutional neural network. Nature 2020, 577, 641–646. [Google Scholar] [CrossRef]

- Pi, S.; Li, C.; Jiang, H.; Xia, W.; Xin, H.; Yang, J.J.; Xia, Q. Memristor crossbar arrays with 6-nm half-pitch and 2-nm critical dimension. Nat. Nanotechnol. 2019, 14, 35–39. [Google Scholar] [CrossRef] [PubMed]

- Chekol, S.A.; Cüppers, F.; Waser, R.; Hoffmann-Eifert, S. An Ag/HfO2/Pt Threshold Switching Device with an Ultra-Low Leakage (<10 fA), High On/Off Ratio (>1011), and Low Threshold Voltage (<0.2 V) for Energy-Efficient Neuromorphic Computing. In Proceedings of the 2021 IEEE International Memory Workshop (IMW), Dresden, Germany, 16–19 May 2021; pp. 1–4. [Google Scholar]

- Li, Y.; Wang, Z.; Midya, R.; Yang, J.J. Review of memristor devices in neuromorphic computing: Materials sciences and device challenges. J. Phys. D Appl. Phys. 2018, 51, 503002. [Google Scholar] [CrossRef]

- Zhao, M.; Gao, B.; Tang, J.; Qian, H.; Wu, H. Reliability of analog resistive switching memory for neuromorphic computing. Appl. Phys. Rev. 2019, 7, 011301. [Google Scholar] [CrossRef]

- Alekseeva, L.; Nabatame, T.; Chikyow, T.; Petrov, A. Resistive switching characteristics in memristors with Al2O3/TiO2 and TiO2/Al2O3 bilayer. Jpn. J. Appl. Phys. 2016, 55, 08PB02. [Google Scholar] [CrossRef]

- Andreeva, N.; Ivanov, A.; Petrov, A. Multilevel resistive switching in TiO2/Al2O3 bilayers at low temperature. AIP Adv. 2018, 8, 025208. [Google Scholar] [CrossRef] [Green Version]

- Sinev, A.E.; Andreeva, N.; Petrov, A.; Bobkov, A. Multilevel Resistive Switching in Heterogeneous Oxide System Based on TiO2/Al2O3 bilayers for ReRAM applications: Problems and prospects. In Proceedings of the IEEE International Conference on Electrical Engineering and Photonics (EExPolytech), St. Petersburg, Russia, 22–23 October 2018; pp. 189–191. [Google Scholar]

- Andreeva, N.; Romanov, A.; Mazing, D.; Chigirev, D.; Sevostyanov, E.; Gerasimova, M.; Trushlyakova, V.; Luchinin, V. Heterolayered memristive systems for multibit memory. The role of oxygen vacancy reservoir. Nanotechnol. Russ. 2021, 16, 825–832. [Google Scholar]

- Andreeva, N.V.; Chigirev, D.A.; Kunitsyn, A.S.; Petrov, A.A. Reversible modification of electrical properties at the nanoscale level in bilayer oxide systems. IOP Conf. Ser. Mater. Sci. Eng. 2018, 443, 012003. [Google Scholar] [CrossRef] [Green Version]

- Petrov, A.; Andreeva, N.; Ivanov, A. Mechanism of electron transport and bipolar resistive switching in lead oxide thin films. AIP Adv. 2018, 8, 105015. [Google Scholar] [CrossRef]

- Andreeva, N.; Luchinin, V.; Ryndin, E. Multimodal neuromorphic modules based on multilevel memristor logics. Electron. STB. 2020, 9, 72–82. [Google Scholar]

- Stathopoulos, S.; Khiat, A.; Trapatseli, M.; Cortese, S.; Serb, A.; Valov, I.; Prodromakis, T. Multibit memory operation of metal-oxide bi-layer memristors. Sci. Rep. 2017, 7, 17532. [Google Scholar] [CrossRef] [Green Version]

- Prezioso, M.; Merrikh-Bayat, F.; Hoskins, B.; Adam, G.C.; Likharev, K.K.; Strukov, D.B. Training and operation of an integrated neuromorphic network based on metal-oxide memristors. Nature 2015, 521, 61–64. [Google Scholar] [CrossRef] [Green Version]

- Bayat, F.M.; Prezioso, M.; Chakrabarti, B.; Nili, H.; Kataeva, I.; Strukov, D. Implementation of multilayer perceptron network with highly uniform passive memristive crossbar circuits. Nat. Commun. 2018, 9, 2331. [Google Scholar] [CrossRef]

- Sheridan, P.; Cai, F.; Du, C.; Ma, W.; Zhang, Z.; Lu, W.D. Sparse coding with memristor networks. Nat. Nanotech. 2017, 12, 784–789. [Google Scholar] [CrossRef] [PubMed]

- Du, C.; Cai, F.; Zidan, M.A.; Ma, W.; Lee, S.H.; Lu, W.D. Reservoir computing using dynamic memristors for temporal information processing. Nat. Commun. 2017, 8, 2204. [Google Scholar] [CrossRef]

- Park, J.; Biju, K.P.; Jung, S.; Lee, W.; Lee, J.; Kim, S.; Park, S.; Shin, J.; Hwang, H. Multibit operation of TiOx-based ReRAM by Schottky barrier height engineering. IEEE Electron Device Lett. 2011, 32, 476–478. [Google Scholar] [CrossRef]

- Prakash, A.; Deleruyelle, D.; Song, J.; Bocquet, M.; Hwang, H. Resistance controllability and variability improvement in a TaOx-based resistive memory for multilevel storage application. Appl. Phys. Lett. 2015, 106, 233104. [Google Scholar] [CrossRef] [Green Version]

- Kim, W.; Chattopadhyay, A.; Siemon, A.; Linn, E.; Waser, R.; Rana, V. Multistate Memristive Tantalum Oxide Devices for Ternary Arithmetic. Sci. Rep. 2016, 6, 36652. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Zhang, H.; Yoo, S.; Menzel, S.; Funck, C.; Cüppers, F.; Wouters, D.J.; Hwang, C.S.; Waser, R.; Hoffmann-Eifert, S. Understanding the coexistence of two bipolar resistive switching modes with opposite polarity in Pt/TiO2/Ti/Pt nanosized ReRAM devices. ACS Appl. Mater. Interfaces 2018, 10, 29766–29778. [Google Scholar] [CrossRef] [PubMed]

- Lübben, M.; Wiefels, S.; Waser, R.; Valov, I. Processes and effects of oxygen and moisture in resistively switching TaOx and HfOx. Adv. Electron. Mater. 2017, 4, 1700458. [Google Scholar] [CrossRef]

- Rückerl, A.; Zeisel, R.; Mandl, M.; Costina, I.; Schroeder, T.; Zoellner, M.H. Characterization and prevention of humidity related degradation of atomic layer deposited Al2O3. J. Appl. Phys. 2017, 121, 025306. [Google Scholar] [CrossRef]

- Mironov, I.V. Spravochnye Dannye Dlya Raschetov v Analiticheskoj Himii; RIC NGU: Novosibirsk, Russia, 2018; p. 152. [Google Scholar]

- Carta, D.; Salaoru, I.; Khiat, A.; Regoutz, A.; Mitterbauer, C.; Harrison, N.M.; Prodromakis, T. Investigation of the Switching Mechanism in TiO2-Based RRAM: A Two-Dimensional EDX Approach. ACS Appl. Mater. Interfaces 2016, 8, 19605–19611. [Google Scholar] [CrossRef] [Green Version]

- Gantmakher, V.F. Electrons and Disorder in Solids; Institute of Solid State Physics, Russian Academy of Sciences: Moscow, Rusia, 2003. [Google Scholar]

- Guy, J.; Molas, G.; Blaise, P. Experimental and theoretical understanding of forming, SET and RESET operations in conductive bridge RAM (CBRAM) for memory stack optimization. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 15–17 December 2014; pp. 152–155. [Google Scholar]

- Ginnaram, S.; Qiu, J.T.; Maikap, S. Controlling cu migration on resistive switching, artificial synapse, and glucose/saliva detection by using an optimized AlOx interfacial layer in a-COx-based conductive bridge random access memory. ACS Omega 2020, 5, 7032–7043. [Google Scholar] [CrossRef] [Green Version]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).