Dielectrophoresis-Based Positioning of Carbon Nanotubes for Wafer-Scale Fabrication of Carbon Nanotube Devices

Abstract

1. Introduction

2. Experimental Details

2.1. CNT-NMP Solution Preparation

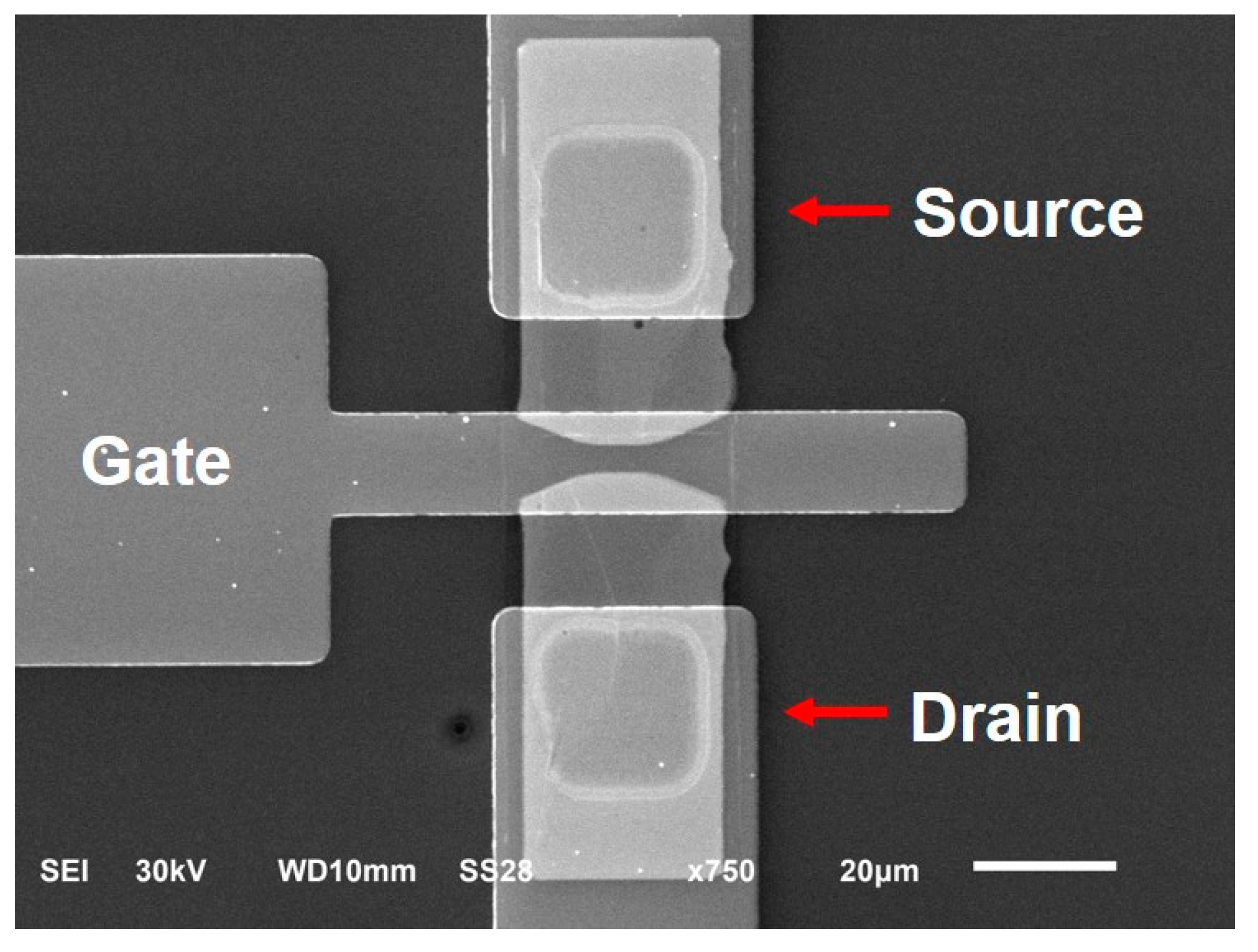

2.2. FET Device Fabrication

2.3. Electrical Measurements

2.4. Electrical Breakdown Process

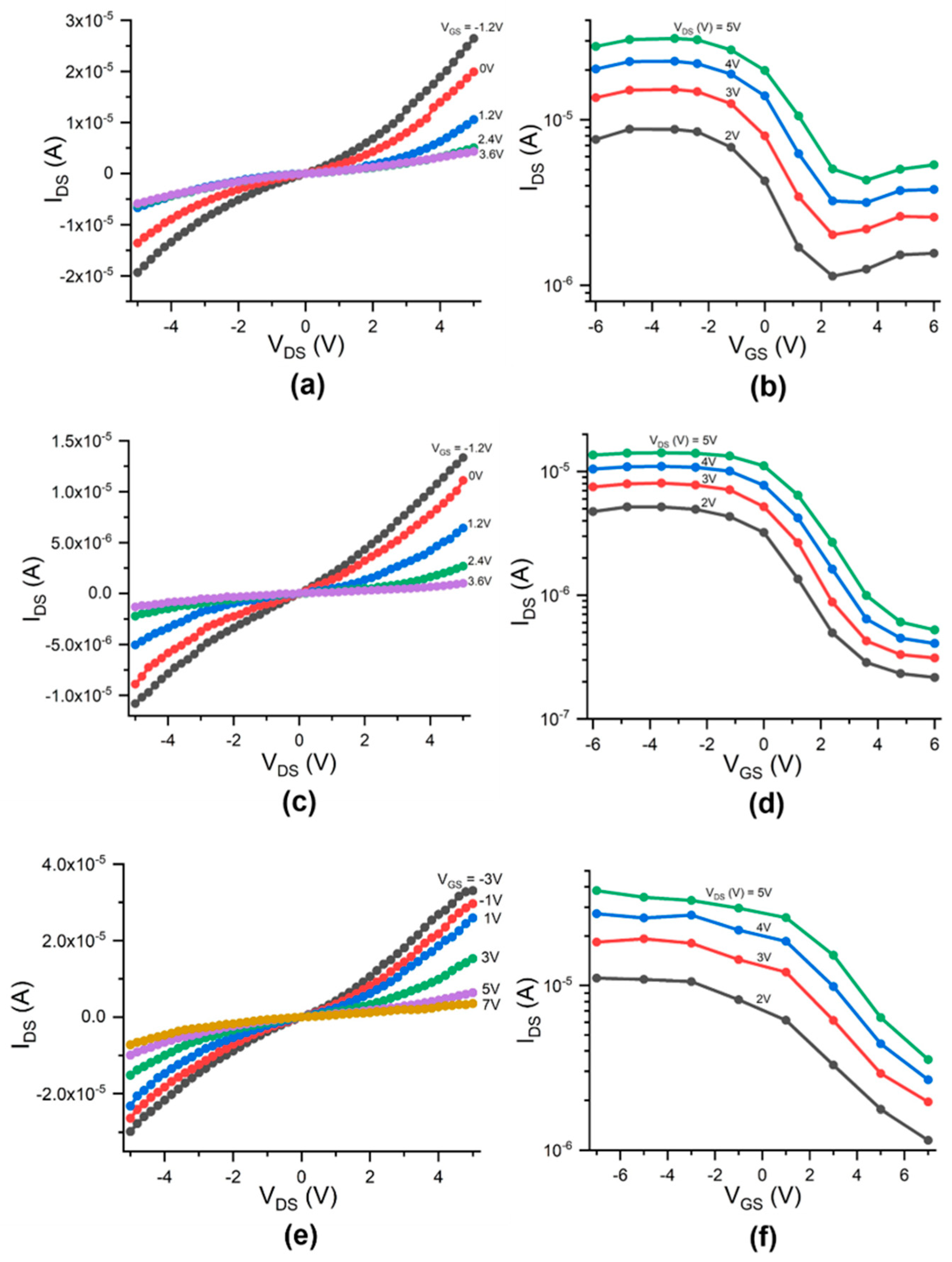

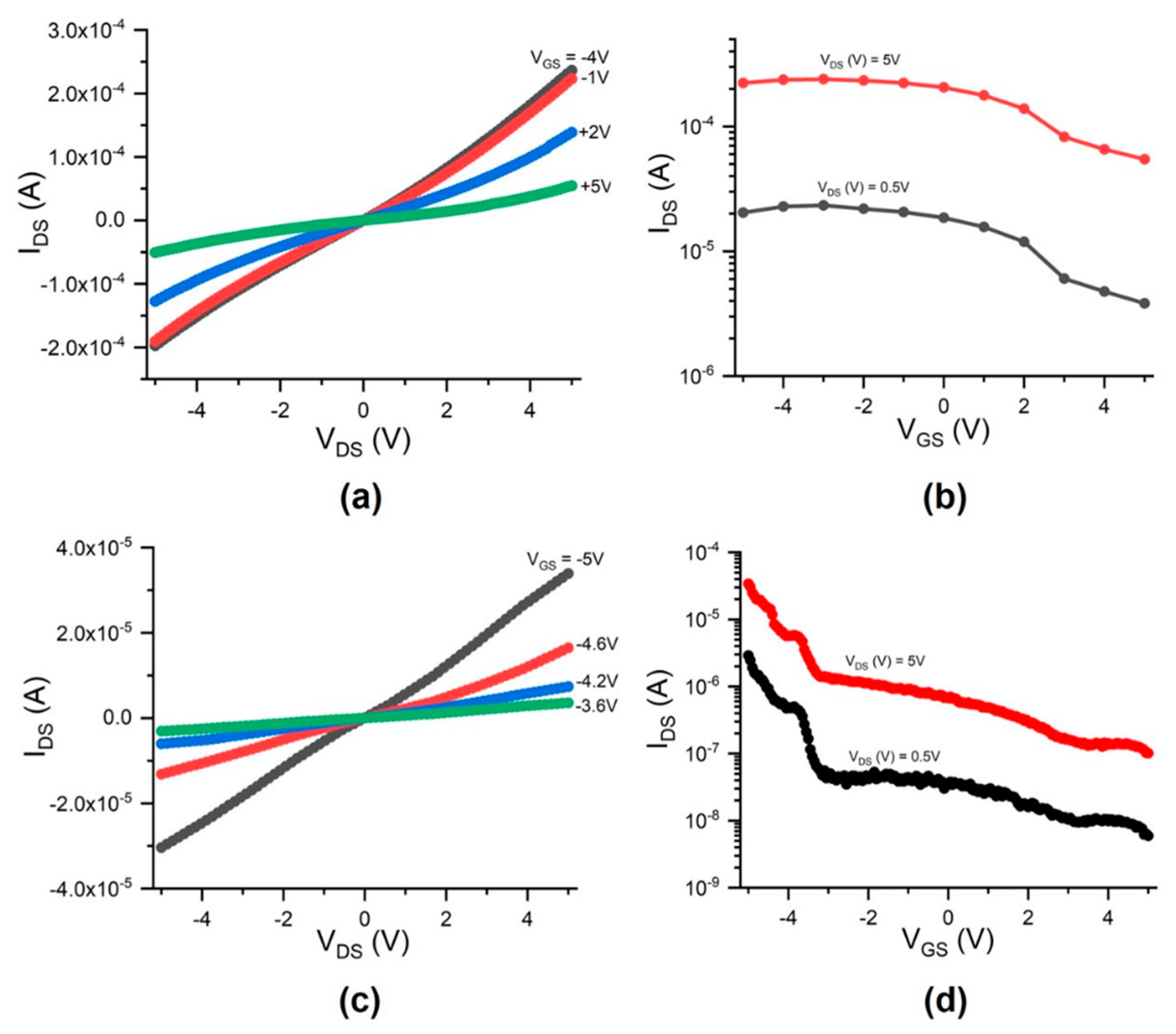

3. Results and Discussion

4. Summary

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Lemieux, M.C.; Roberts, M.; Barman, S.; Jin, Y.W.; Kim, J.M.; Bao, Z. Self-Sorted, Aligned Nanotube Networks for Thin-Film Transistors. Science 2008, 321, 101–104. [Google Scholar] [CrossRef]

- Javey, A.; Guo, J.; Farmer, D.B.; Wang, Q.; Wang, D.; Gordon, R.G.; Lundstrom, A.M.; Dai, H. Carbon Nanotube Field-Effect Transistors with Integrated Ohmic Contacts and High-κ Gate Dielectrics. Nano Lett. 2004, 4, 447–450. [Google Scholar] [CrossRef]

- Seidel, R.V.; Graham, A.P.; Kretz, J.; Rajasekharan, B.; Duesberg, G.S.; Liebau, M.; Unger, E.; Kreupl, F.; Hoenlein, W. Sub-20 nm Short Channel Carbon Nanotube Transistors. Nano Lett. 2005, 5, 147–150. [Google Scholar] [CrossRef]

- Wang, H.; Cobb, B.; Van Breemen, A.; Gelinck, G.G.; Bao, Z. Highly Stable Carbon Nanotube Top-Gate Transistors with Tunable Threshold Voltage. Adv. Mater. 2014, 26, 4588–4593. [Google Scholar] [CrossRef]

- Qiu, C.; Zhang, Z.; Zhong, D.; Si, J.; Yang, Y.; Peng, L.-M. Carbon Nanotube Feedback-Gate Field-Effect Transistor: Suppressing Current Leakage and Increasing On/Off Ratio. ACS Nano 2015, 9, 969–977. [Google Scholar] [CrossRef] [PubMed]

- Wanga, H.; Weib, P.; Lic, Y.; Hanb, J.; Leec, H.; Naabd, B.; Liub, N.; Wange, C.; Adijantob, E.; Teec, B.; et al. Tuning the threshold voltage of carbon nanotube transistors by n-type molecular doping for robust and flexible complementary circuits. Proc. Natl. Acad. Sci. USA 2014, 111, 4776. [Google Scholar] [CrossRef] [PubMed]

- Sun, D.-M.; Timmermans, M.Y.; Tian, Y.; Nasibulin, A.G.; Kauppinen, E.I.; Kishimoto, S.; Mizutani, T.; Ohno, Y. Flexible high-performance carbon nanotube integrated circuits. Nat. Nanotechnol. 2011, 6, 156–161. [Google Scholar] [CrossRef] [PubMed]

- Ding, L.; Zhang, Z.; Liang, S.; Pei, T.; Wang, S.; Li, Y.; Zhou, W.; Liu, J.; Peng, L.-M. CMOS-based carbon nanotube pass-transistor logic integrated circuits. Nat. Commun. 2012, 3, 677. [Google Scholar] [CrossRef]

- Kim, B.; Jang, S.; Geier, M.L.; Prabhumirashi, P.L.; Hersam, M.C.; Dodabalapur, A. High-Speed, Inkjet-Printed Carbon Nanotube/Zinc Tin Oxide Hybrid Complementary Ring Oscillators. Nano Lett. 2014, 14, 3683–3687. [Google Scholar] [CrossRef]

- Zaumseil, J. Single-walled carbon nanotube networks for flexible and printed electronics. Semicond. Sci. Technol. 2015, 30. [Google Scholar] [CrossRef]

- Chen, H.; Cao, Y.; Zhang, J.; Zhou, C. Large-scale complementary macroelectronics using hybrid integration of carbon nanotubes and IGZO thin-film transistors. Nat. Commun. 2014, 5, 4097. [Google Scholar] [CrossRef] [PubMed]

- Park, S.; Vosguerichian, M.; Bao, Z. A review of fabrication and applications of carbon nanotube film-based flexible electronics. Nanoscale 2013, 5, 1727. [Google Scholar] [CrossRef] [PubMed]

- Zhang, Z.; Liang, X.; Wang, S.; Yao, K.; Hu, Y.; Zhu, Y.; Chen, Q.; Zhou, W.; Li, Y.; Yao, Y.; et al. Doping-Free Fabrication of Carbon Nanotube Based Ballistic CMOS Devices and Circuits. Nano Lett. 2007, 7, 3603–3607. [Google Scholar] [CrossRef]

- Geier, M.L.; Prabhumirashi, P.L.; McMorrow, J.J.; Xu, W.; Seo, J.-W.T.; Everaerts, K.; Kim, C.H.; Marks, T.J.; Hersam, M.C. Subnanowatt Carbon Nanotube Complementary Logic Enabled by Threshold Voltage Control. Nano Lett. 2013, 13, 4810–4814. [Google Scholar] [CrossRef]

- Chen, Z.; Appenzeller, J.; Lin, Y.-M.; Sippel-Oakley, J.; Rinzler, A.G.; Tang, J.; Wind, S.J.; Solomon, P.M.; Avouris, P. An Integrated Logic Circuit Assembled on a Single Carbon Nanotube. Science 2006, 311, 1735. [Google Scholar] [CrossRef]

- Wei, B.Q.; Vajtai, R.; Ajayan, P.M. Reliability and current carrying capacity of carbon nanotubes. Appl. Phys. Lett. 2001, 79, 1172–1174. [Google Scholar] [CrossRef]

- White, C.T.; Todorov, T.N. Quantum electronics: Nanotubes go ballistic. Nature 2001, 411, 649. [Google Scholar] [CrossRef]

- Datta, S. Electronic Transport Properties in Mesoscopic Systems; Cambridge University Press: Cambridge, UK, 1995. [Google Scholar]

- Shulaker, M.M.; Hills, G.; Patil, N.; Wei, H.; Chen, H.-Y.; Wong, H.-S.P.; Mitra, S. Carbon nanotube computer. Nat. Cell Biol. 2013, 501, 526–530. [Google Scholar] [CrossRef]

- Xiao, Z.; Elike, J.; Reynolds, A.; Moten, R.; Zhao, X. The fabrication of carbon nanotube electronic circuits with dielectrophoresis. Microelectron. Eng. 2016, 164, 123–127. [Google Scholar] [CrossRef]

- Jariwala, D.; Sangwan, V.K.; Lauhon, L.J.; Marks, T.J.; Hersam, M.C. Carbon nanomaterials for electronics, optoelectronics, photovoltaics, and sensing. Chem. Soc. Rev. 2013, 42, 2824–2860. [Google Scholar] [CrossRef]

- Peng, L.-M.; Zhang, Z.; Wang, S. Carbon nanotube electronics: Recent advances. Mater. Today 2014, 17, 433–442. [Google Scholar] [CrossRef]

- Shulaker, M.M.; Van Rethy, J.; Wu, T.F.; Liyanage, L.S.; Wei, H.; Li, Z.; Pop, E.; Gielen, G.; Wong, H.-S.P.; Mitra, S. Carbon Nanotube Circuit Integration up to Sub-20 nm Channel Lengths. ACS Nano 2014, 8, 3434–3443. [Google Scholar] [CrossRef] [PubMed]

- Benedict, L.X.; Louie, S.G.; Cohen, M.L. Static polarizabilities of single-wall carbon nanotubes. Phys. Rev. B 1995, 52, 8541–8549. [Google Scholar] [CrossRef] [PubMed]

- Zhang, Z.-B.; Liu, X.; Campbell, E.E.B.; Zhang, S.-L. Alternating current dielectrophoresis of carbon nanotubes. J. Appl. Phys. 2005, 98, 56103. [Google Scholar] [CrossRef]

- Li, P.; Xue, W. Selective Deposition and Alignment of Single-Walled Carbon Nanotubes Assisted by Dielectrophoresis: From Thin Films to Individual Nanotubes. Nanoscale Res. Lett. 2010, 5, 1072–1078. [Google Scholar] [CrossRef] [PubMed]

- Yang, B.; Yang, Z.; Zhao, Z.; Hu, Y.; Li, J. The assembly of carbon nanotubes by dielectrophoresis: Insights into the dielectrophoretic nanotube–nanotube interactions. Phys. E Low-Dimens. Syst. Nanostruct. 2014, 56, 117–122. [Google Scholar] [CrossRef]

- Naieni, A.K.; Nojeh, A. Effect of solution conductivity and electrode shape on the deposition of carbon nanotubes from solution using dielectrophoresis. Nanotechnology 2012, 23, 495606. [Google Scholar] [CrossRef]

- Xiao, Z.; Sharma, H.; Zhu, M.Y.; Pearson, T. Dielectrophoresis-assisted deposition and alignment of single-walled carbon nanotubes for electronic-device fabrication. J. Vac. Sci. Technol. A 2010, 28, 750–754. [Google Scholar] [CrossRef]

- Krisnadi, F.; Nguyen, L.L.; Ankit; Ma, J.; Kulkarni, M.R.; Mathews, N.; Dickey, M.D. Directed Assembly of Liquid Metal–Elastomer Conductors for Stretchable and Self-Healing Electronics. Adv. Mater. 2020, 32, 2001642. [Google Scholar] [CrossRef]

- Naieni, A.K.; Nojeh, A. Dielectrophoretic deposition of carbon nanotubes: The role of field frequency and its dependence on solution conductivity. Microelectron. Eng. 2014, 114, 26–30. [Google Scholar] [CrossRef]

- Shekhar, S.; Stokes, P.; Khondaker, S.I. Ultrahigh Density Alignment of Carbon Nanotube Arrays by Dielectrophoresis. ACS Nano 2011, 5, 1739–1746. [Google Scholar] [CrossRef] [PubMed]

- Sarker, B.K.; Shekhar, S.; Khondaker, S.I. Semiconducting Enriched Carbon Nanotube Aligned Arrays of Tunable Density and Their Electrical Transport Properties. ACS Nano 2011, 5, 6297–6305. [Google Scholar] [CrossRef] [PubMed]

- Tittmann-Otto, J.; Hermann, S.; Kalbacova, J.; Hartmann, M.; Toader, M.; Rodriguez, R.D.; Schulz, S.; Zahn, D.R.T.; Gessner, T. Effect of cleaning procedures on the electrical properties of carbon nanotube transistors—A statistical study. J. Appl. Phys. 2016, 119, 124509. [Google Scholar] [CrossRef]

- Liu, B.; Liu, J.; Li, H.-B.; Bhola, R.; Jackson, E.A.; Scott, L.T.; Page, A.J.; Irle, S.; Morokuma, K.; Zhou, C. Nearly Exclusive Growth of Small Diameter Semiconducting Single-Wall Carbon Nanotubes from Organic Chemistry Synthetic End-Cap Molecules. Nano Lett. 2015, 15, 586. [Google Scholar] [CrossRef]

- Xiao, Z.; Williams, L.; Kisslinger, K.; Sadowski, J.T.; Camino, F. Fabrication of field-effect transistors with transfer-free nanostructured carbon as semiconducting channel material. Nanotechnology 2020, 31, 485203. [Google Scholar] [CrossRef]

- Xiao, Z.; Kisslinger, K.; Chance, S.; Banks, S. Comparison of Hafnium Dioxide and Zirconium Dioxide Grown by Plasma-Enhanced Atomic Layer Deposition for the Application of Electronic Materials. Crystals 2020, 10, 136. [Google Scholar] [CrossRef]

- Collins, P.G.; Arnold, M.S.; Avouris, P. Engineering Carbon Nanotubes and Nanotube Circuits Using Electrical Breakdown. Science 2001, 292, 706–709. [Google Scholar] [CrossRef]

- Otsuka, K.; Inoue, T.; Chiashi, S.; Maruyama, S. Selective removal of metallic single-walled carbon nanotubes in full length by organic film-assisted electrical breakdown. Nanoscale 2014, 6, 8831–8835. [Google Scholar] [CrossRef]

- Xiao, Z.; Camino, F.E. The fabrication of carbon nanotube field-effect transistors with semiconductors as the source and drain contact materials. Nanotechnol. 2009, 20, 135205. [Google Scholar] [CrossRef]

- Xiao, Z.; Camino, F.E. An Effective Switching-Off Mechanism for High-Performance Carbon Nanotube Field-Effect Transistors. J. Nanoelectron. Optoelectron. 2010, 5, 26–29. [Google Scholar] [CrossRef]

- Avouris, P. Carbon nanotube electronics. Chem. Phys. 2002, 281, 429. [Google Scholar] [CrossRef]

- Avouris, P.; Martel, R.; DeRycke, V.; Appenzeller, J. Carbon nanotube transistors and logic circuits. Phys. B Condens. Matter 2002, 323, 6–14. [Google Scholar] [CrossRef]

- Martel, R.; DeRycke, V.; Appenzeller, J.; Wind, S.; Avouris, P. Carbon nanotube field-effect transistors and logic circuits. In Proceedings of the ACM/IEEE Design Automation Conference, New Orleans, LA, USA, 10–14 June 2002; pp. 94–98. [Google Scholar]

- Xiao, Z.; Kisslinger, K. Electron-beam-evaporated thin films of hafnium dioxide for fabricating electronic devices. J. Vac. Sci. Technol. B 2015, 33, 042001. [Google Scholar] [CrossRef]

- Schroter, M.; Claus, M.; Sakalas, P.; Haferlach, M.; Wang, D. Carbon Nanotube FET Technology for Radio-Frequency Electronics: State-of-the-Art Overview. IEEE J. Electron Devices Soc. 2013, 1, 9–20. [Google Scholar] [CrossRef]

- Franklin, A.D.; Koswatta, S.O.; Farmer, D.B.; Smith, J.T.; Gignac, L.; Breslin, C.M.; Han, S.-J.; Tulevski, G.S.; Miyazoe, H.; Haensch, W.; et al. Carbon Nanotube Complementary Wrap-Gate Transistors. Nano Lett. 2013, 13, 2490–2495. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kimbrough, J.; Williams, L.; Yuan, Q.; Xiao, Z. Dielectrophoresis-Based Positioning of Carbon Nanotubes for Wafer-Scale Fabrication of Carbon Nanotube Devices. Micromachines 2021, 12, 12. https://doi.org/10.3390/mi12010012

Kimbrough J, Williams L, Yuan Q, Xiao Z. Dielectrophoresis-Based Positioning of Carbon Nanotubes for Wafer-Scale Fabrication of Carbon Nanotube Devices. Micromachines. 2021; 12(1):12. https://doi.org/10.3390/mi12010012

Chicago/Turabian StyleKimbrough, Joevonte, Lauren Williams, Qunying Yuan, and Zhigang Xiao. 2021. "Dielectrophoresis-Based Positioning of Carbon Nanotubes for Wafer-Scale Fabrication of Carbon Nanotube Devices" Micromachines 12, no. 1: 12. https://doi.org/10.3390/mi12010012

APA StyleKimbrough, J., Williams, L., Yuan, Q., & Xiao, Z. (2021). Dielectrophoresis-Based Positioning of Carbon Nanotubes for Wafer-Scale Fabrication of Carbon Nanotube Devices. Micromachines, 12(1), 12. https://doi.org/10.3390/mi12010012