2 kW Dual-Output Isolated DC/DC Converter Based on Current Doubler and Step-Down Chopper

Abstract

1. Introduction

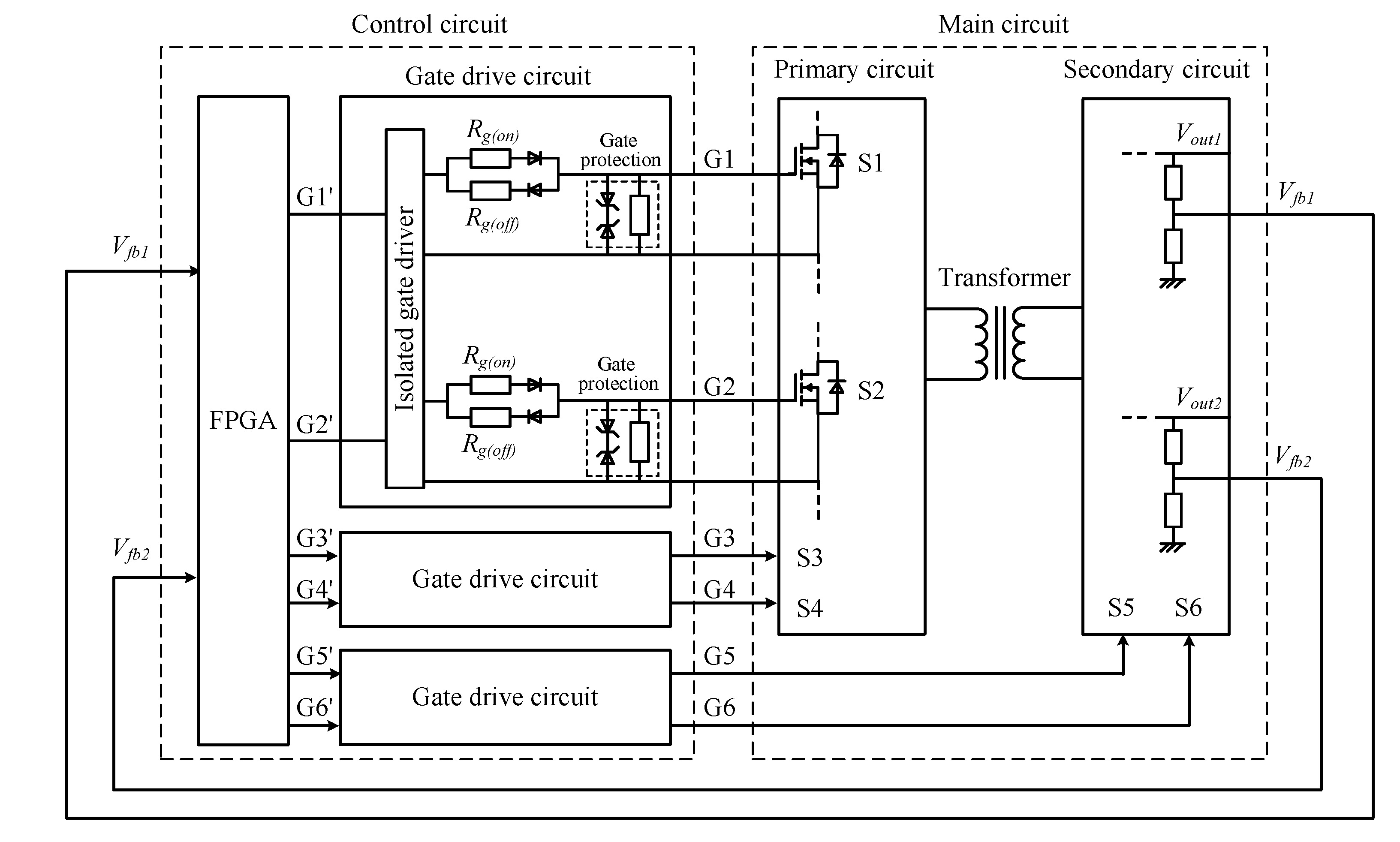

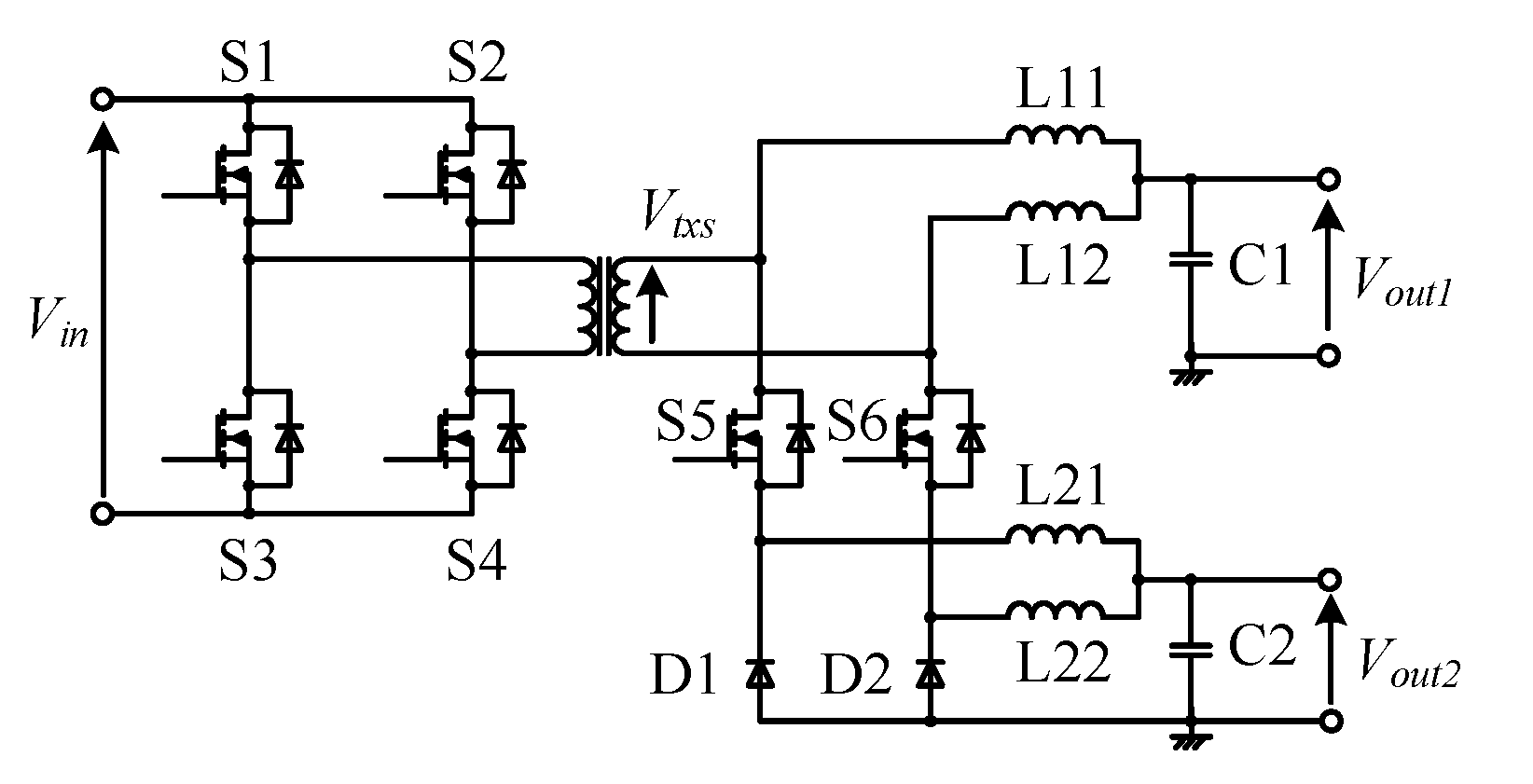

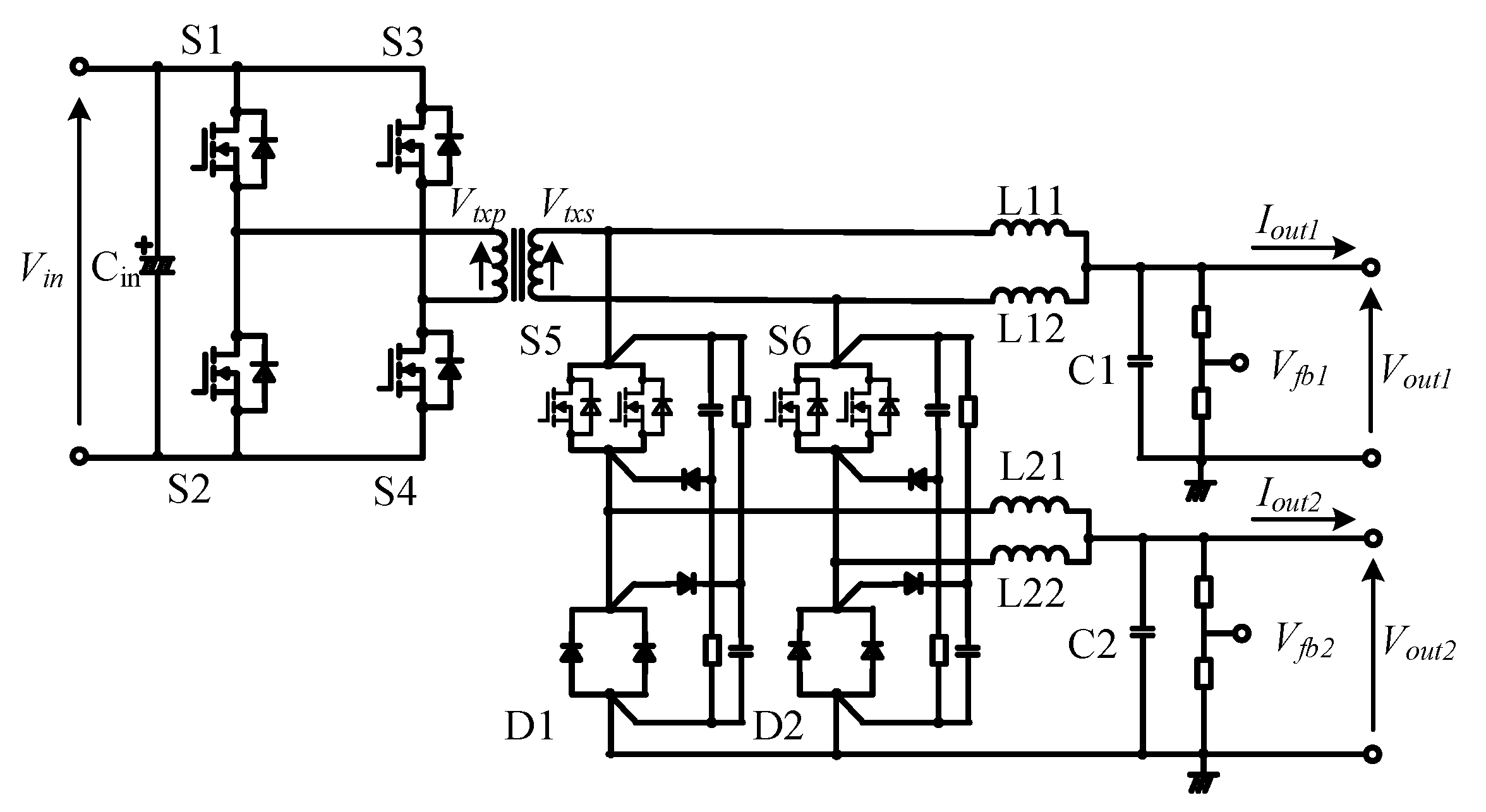

2. Circuit Configuration and Operation Principle

2.1. Circuit Configuration

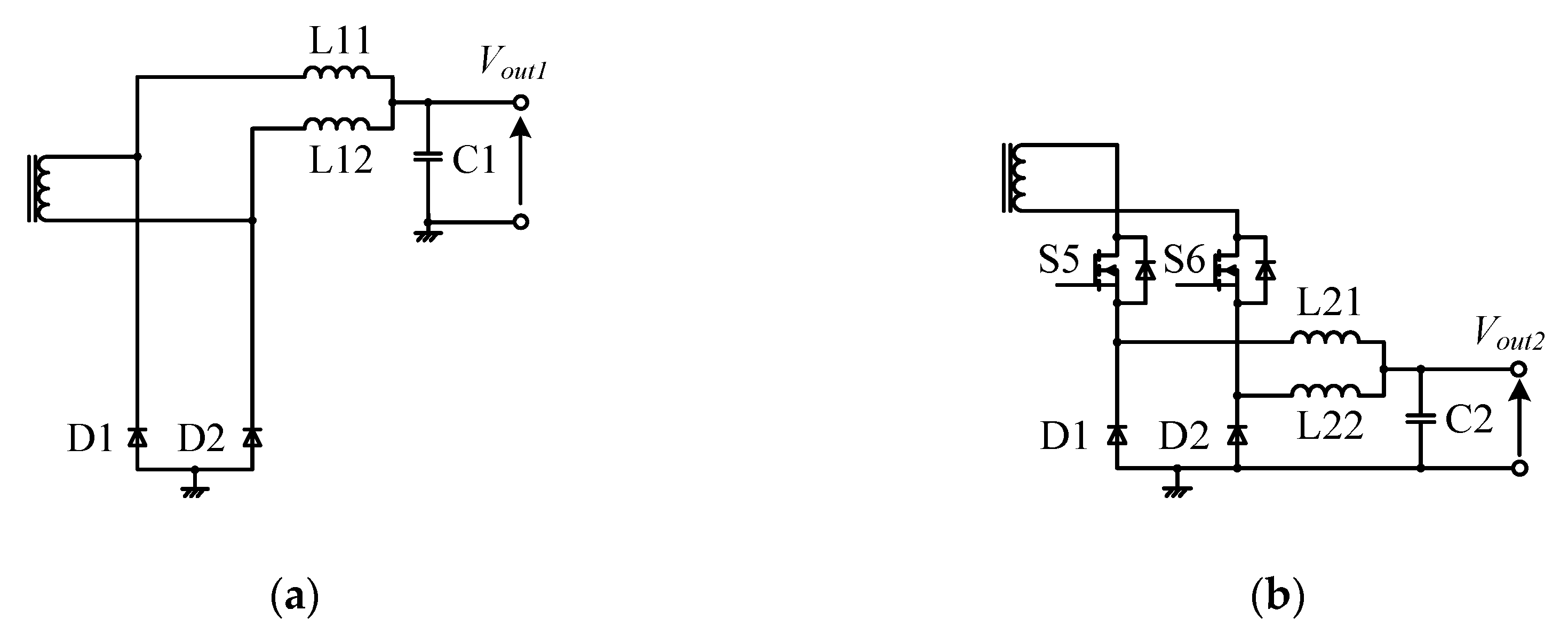

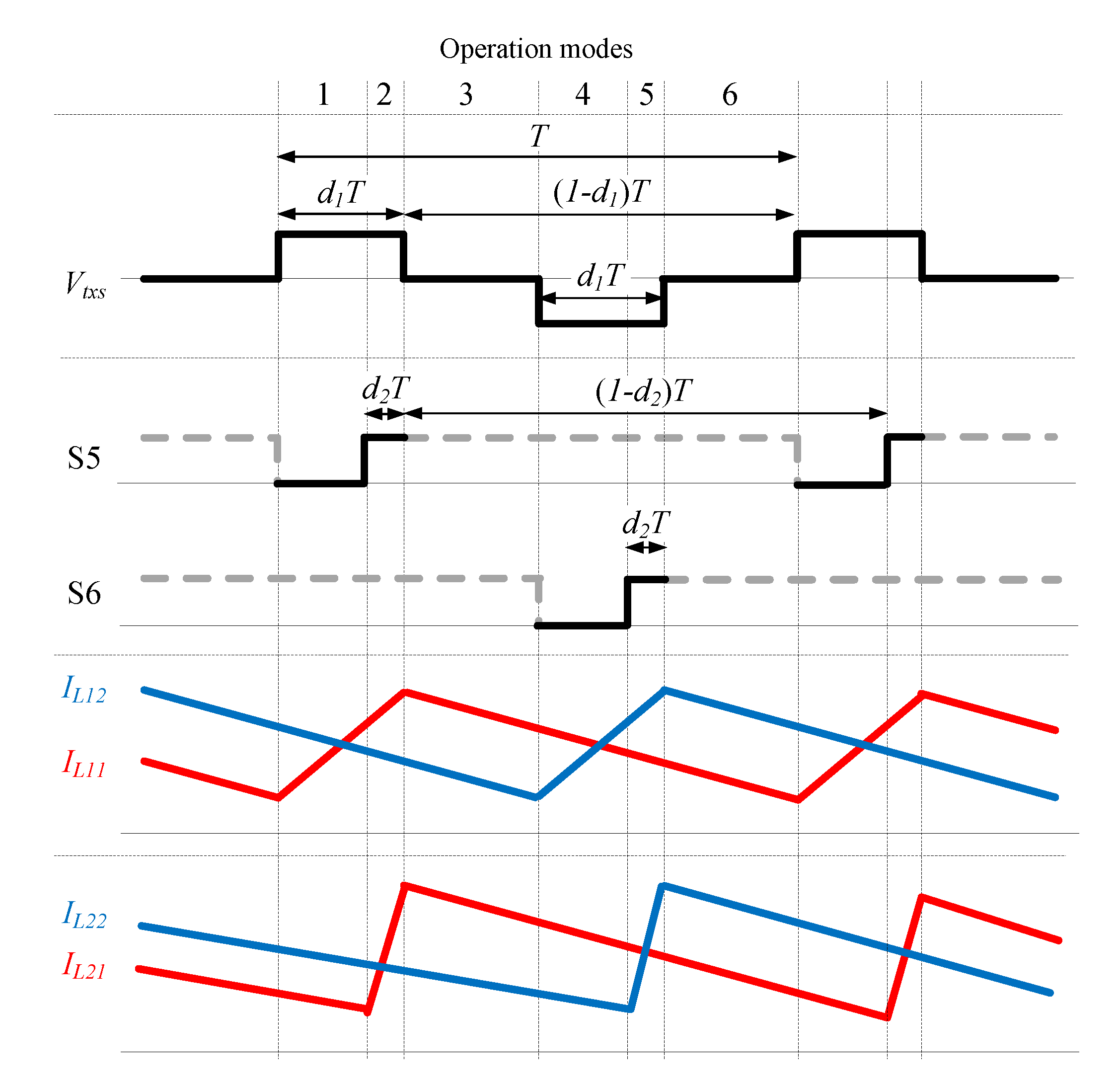

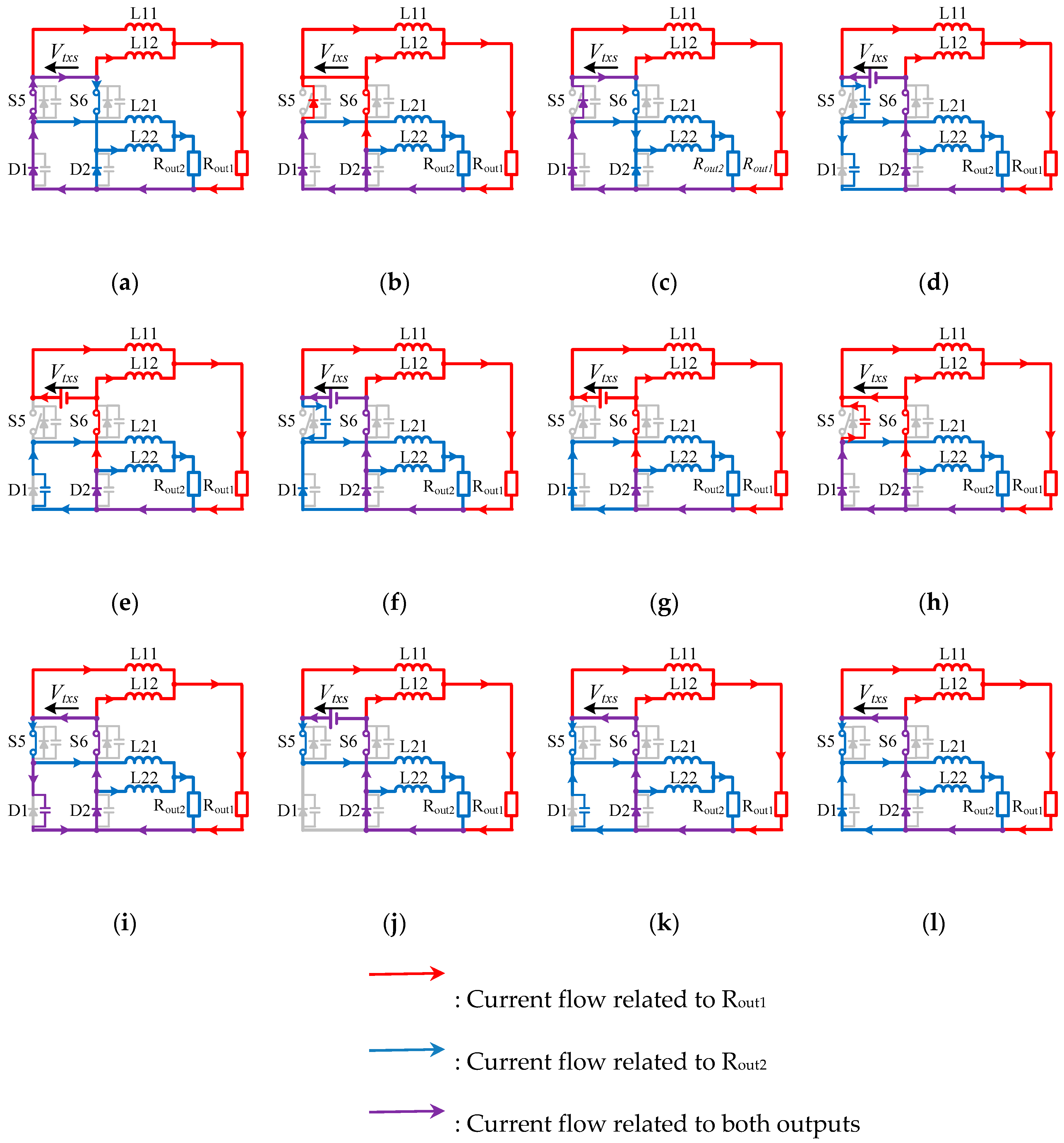

2.2. Operation Principle

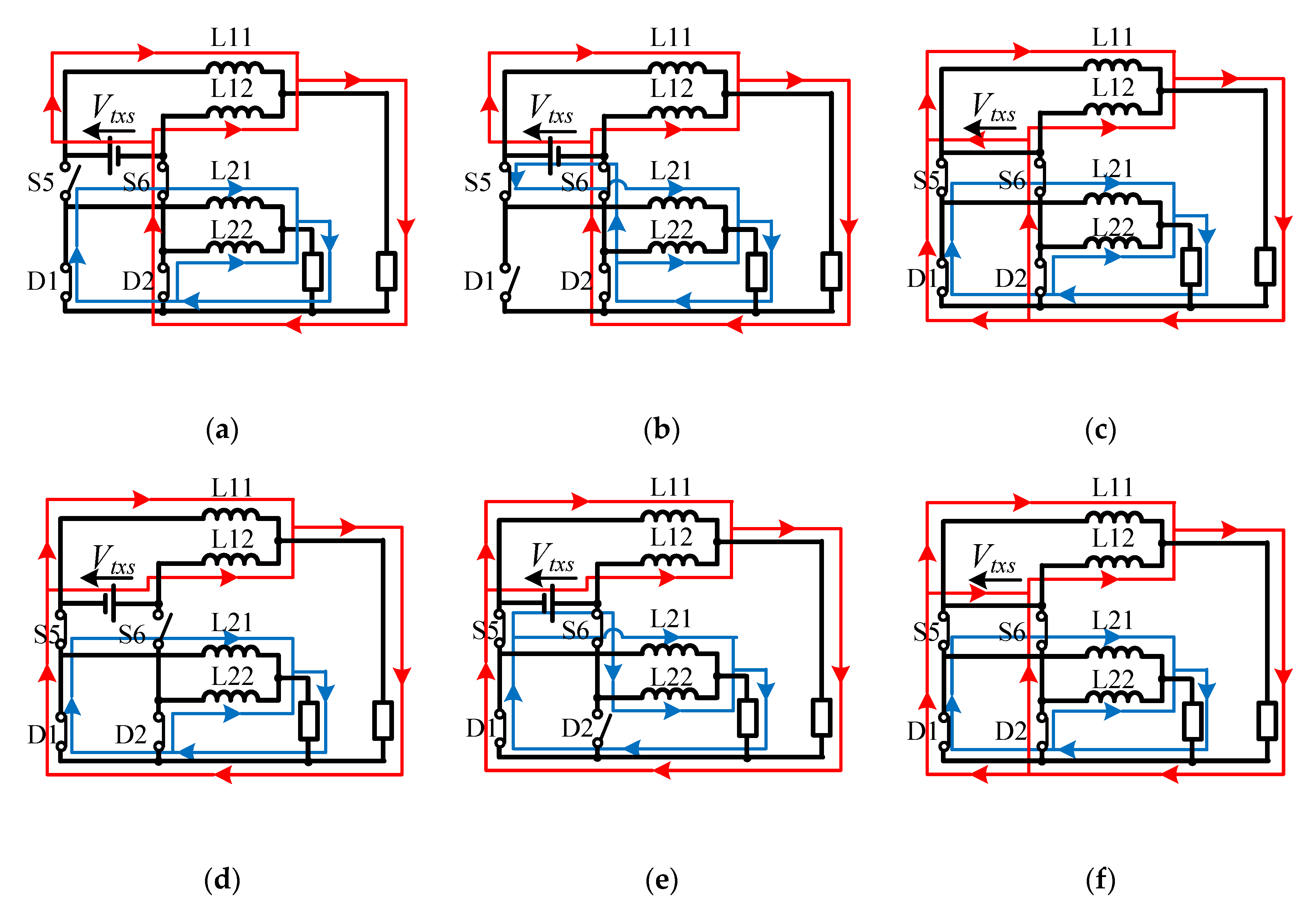

- The operation of the secondary side circuit in each mode is described below.

- Mode 1: Vtxs is positive and S5 is off (Figure 4a).

- L11 is charged by Vtxs and L12, L21, and L22 discharge.

- Mode 2: Vtxs is positive and S5 is on (Figure 4b).

- As S5 is turned on, both L11 and L21 are charged by Vtxs, whereas L12 and L22 still discharge.

- Mode 3: Vtxs is 0 (Figure 4c).

- When Vtxs is 0, there is no power, and therefore, L11, L12, L21, and L22 all discharge.

- Mode 4: Vtxs is negative and S6 is off (Figure 4d).

- L12 is charged by Vtxs and L11, L21, and L22 discharge.

- Mode 5: Vtxs is negative and S6 is on (Figure 4e).

- As S6 is turned on, L12 as well as L22 are charged. L11 and L21 still discharge.

- Mode 6: Vtxs is 0 (Figure 4f).

- As in Mode 3, as Vtxs is 0, L11, L12, L21, and L22 discharge.

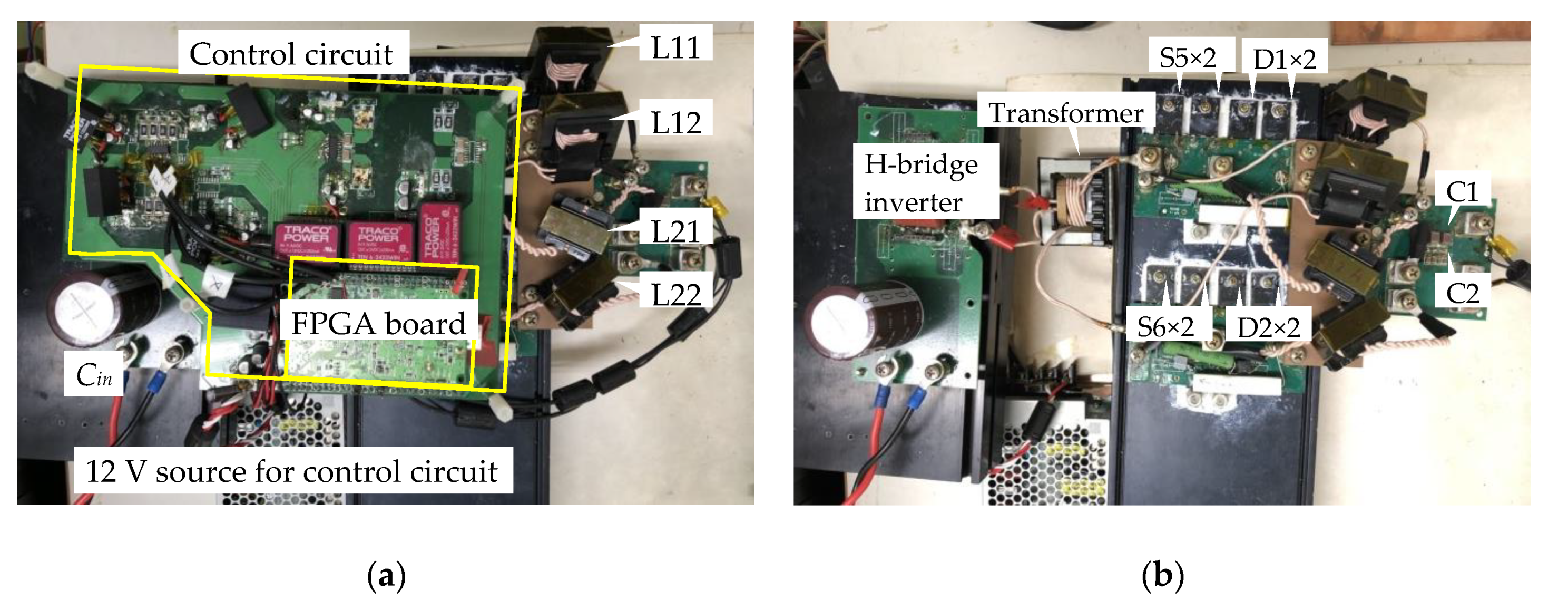

3. Actual Device Testing

3.1. Main Circuit Configuration

3.2. Control Circuit Configuration

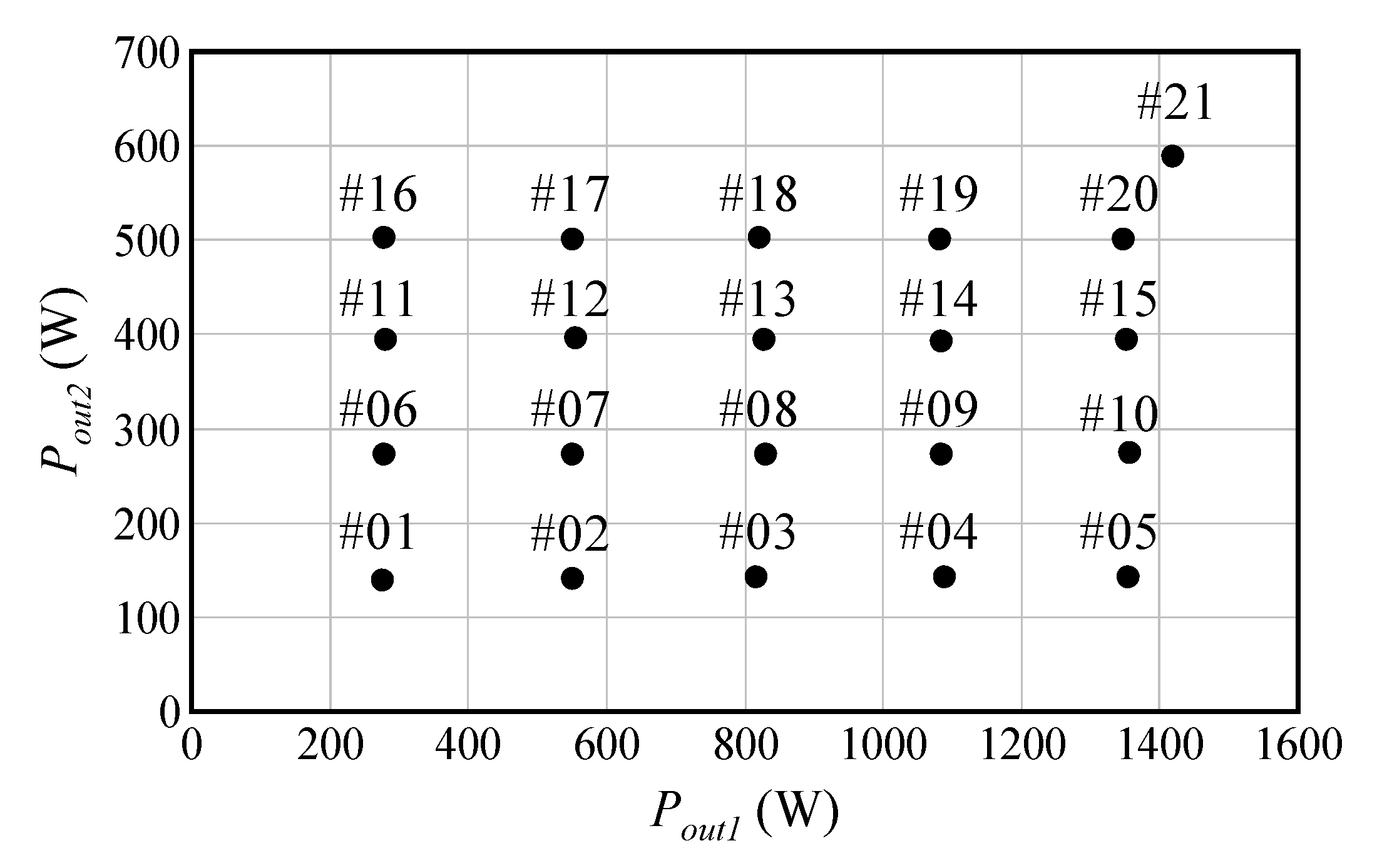

3.3. Operation Points

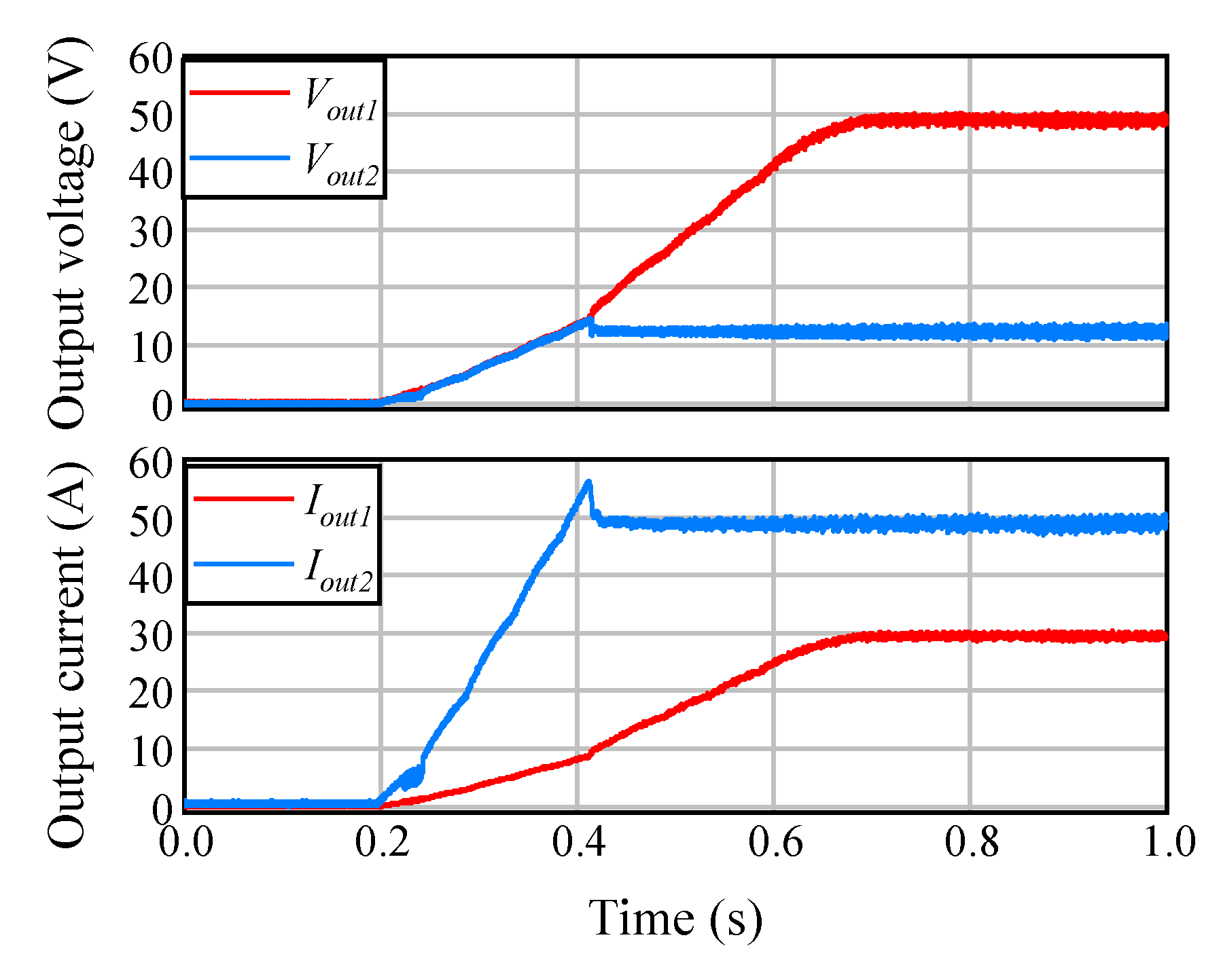

3.4. Voltage Target Value Response Characteristics

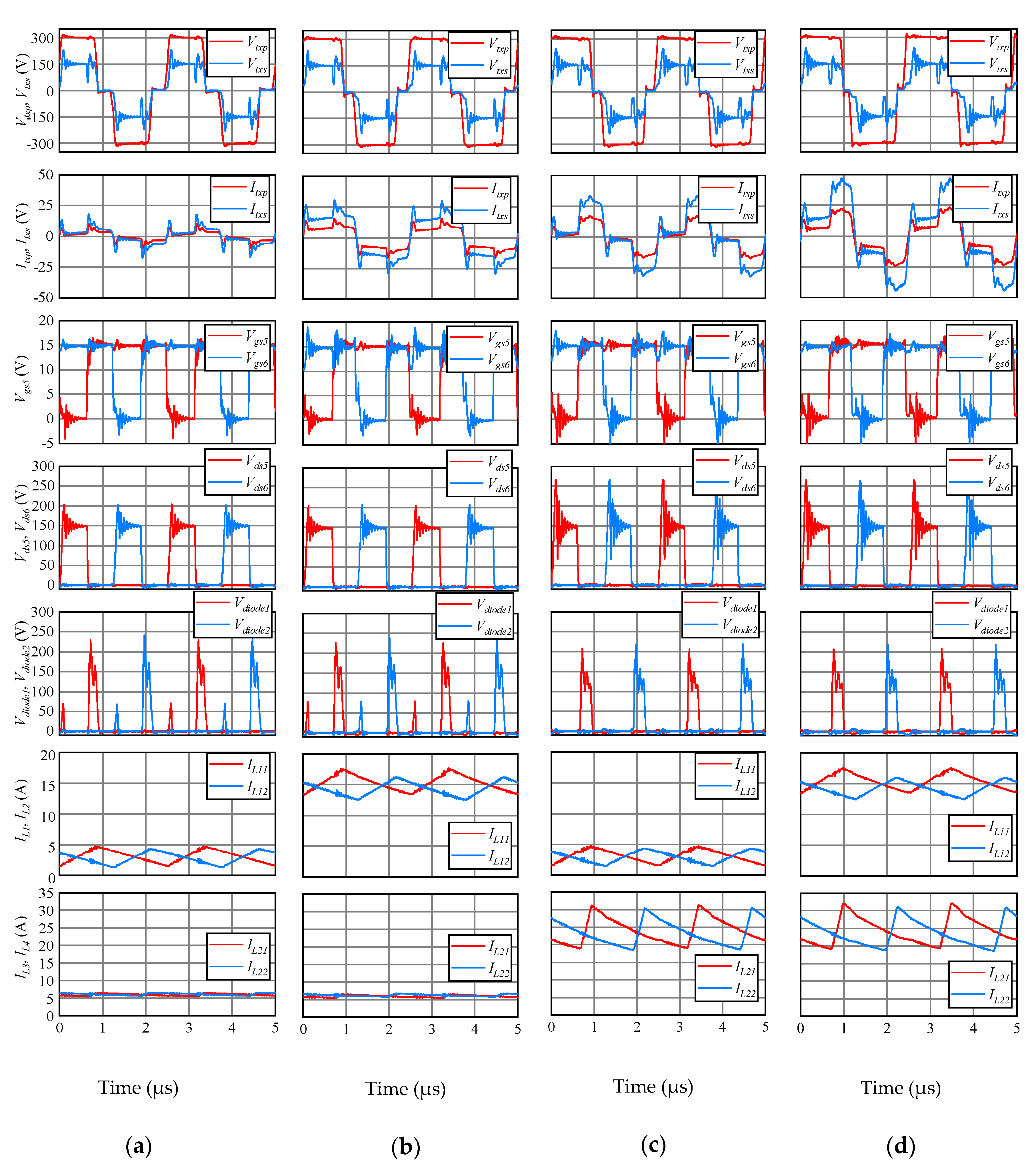

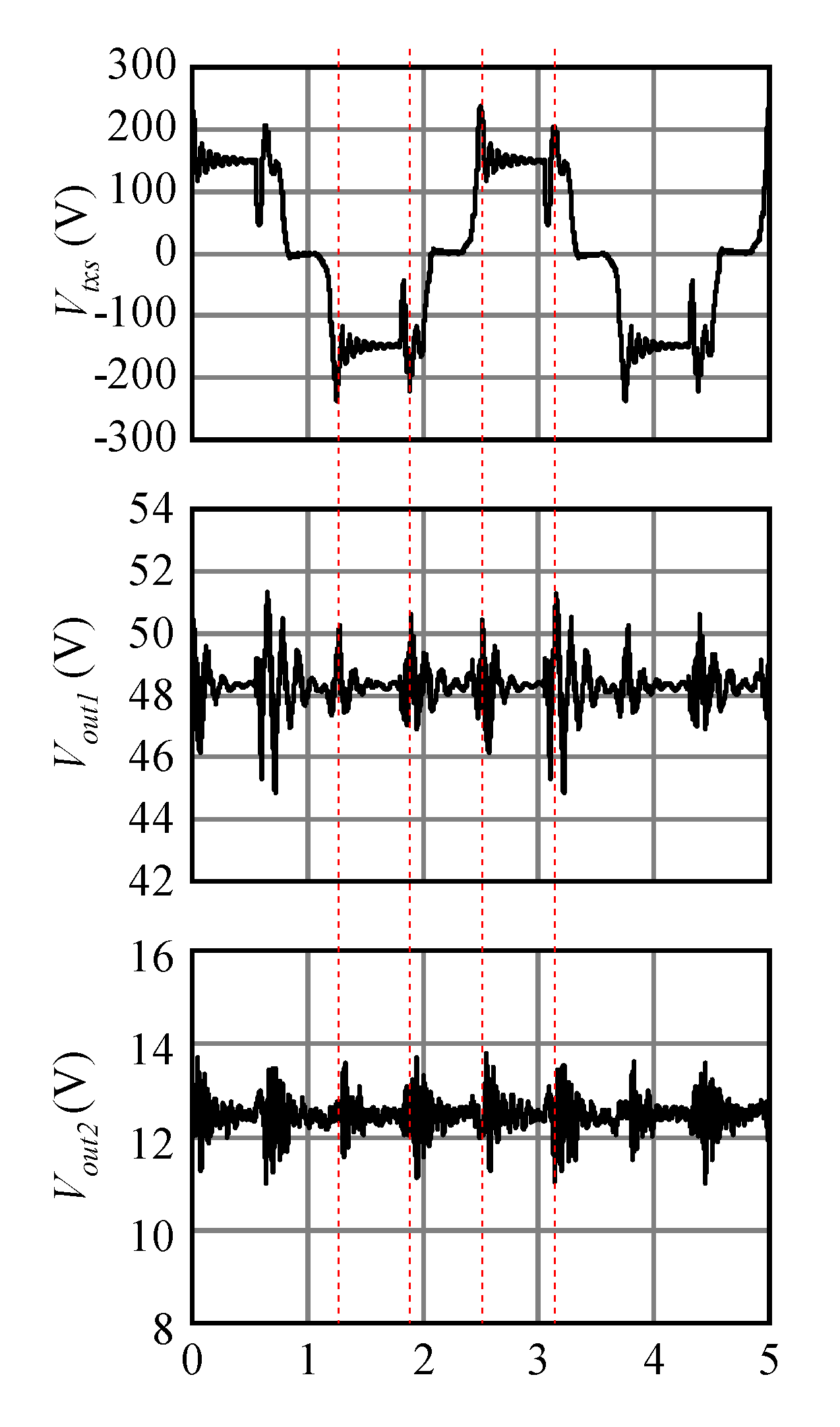

3.5. Operating Waveforms

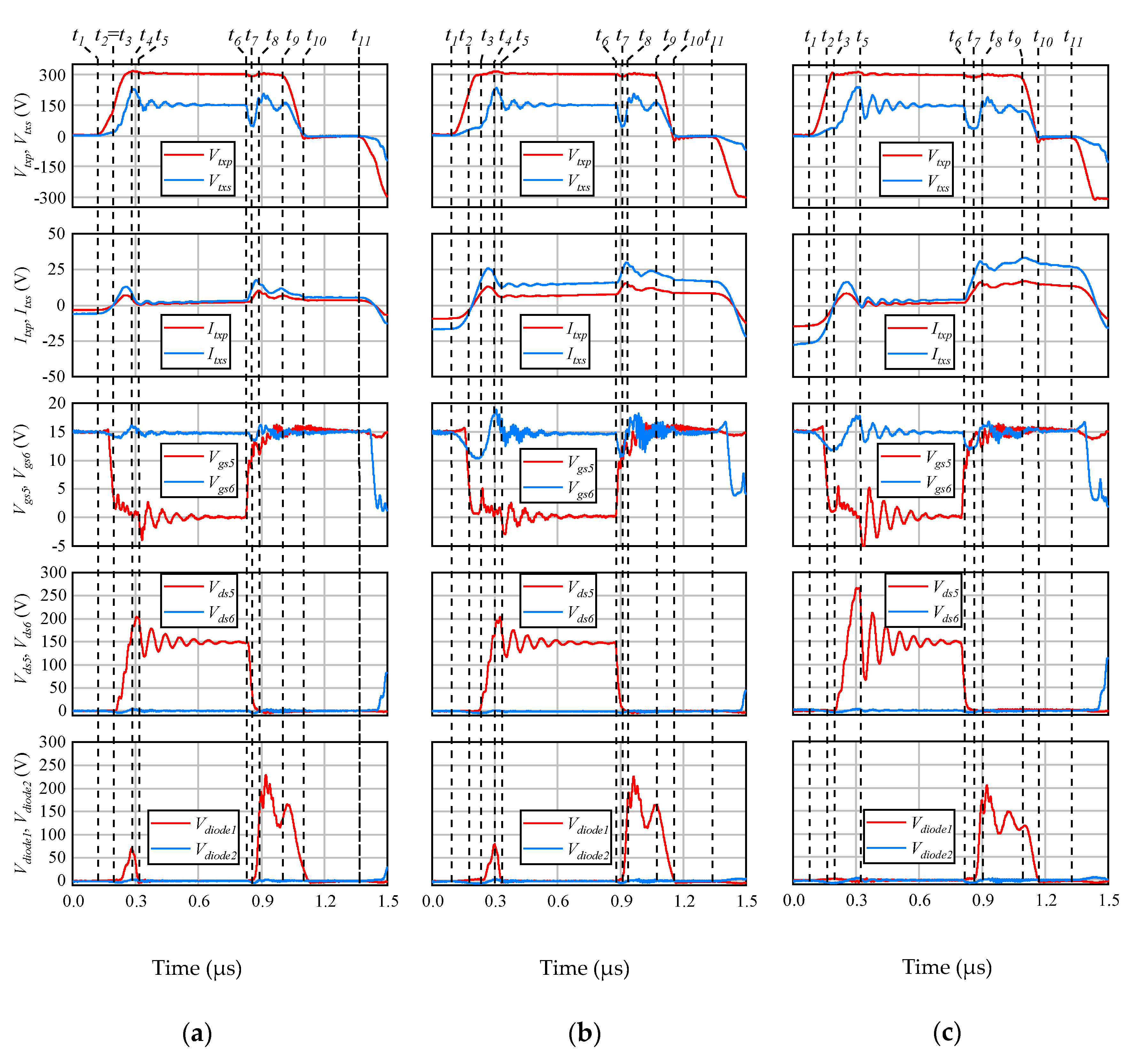

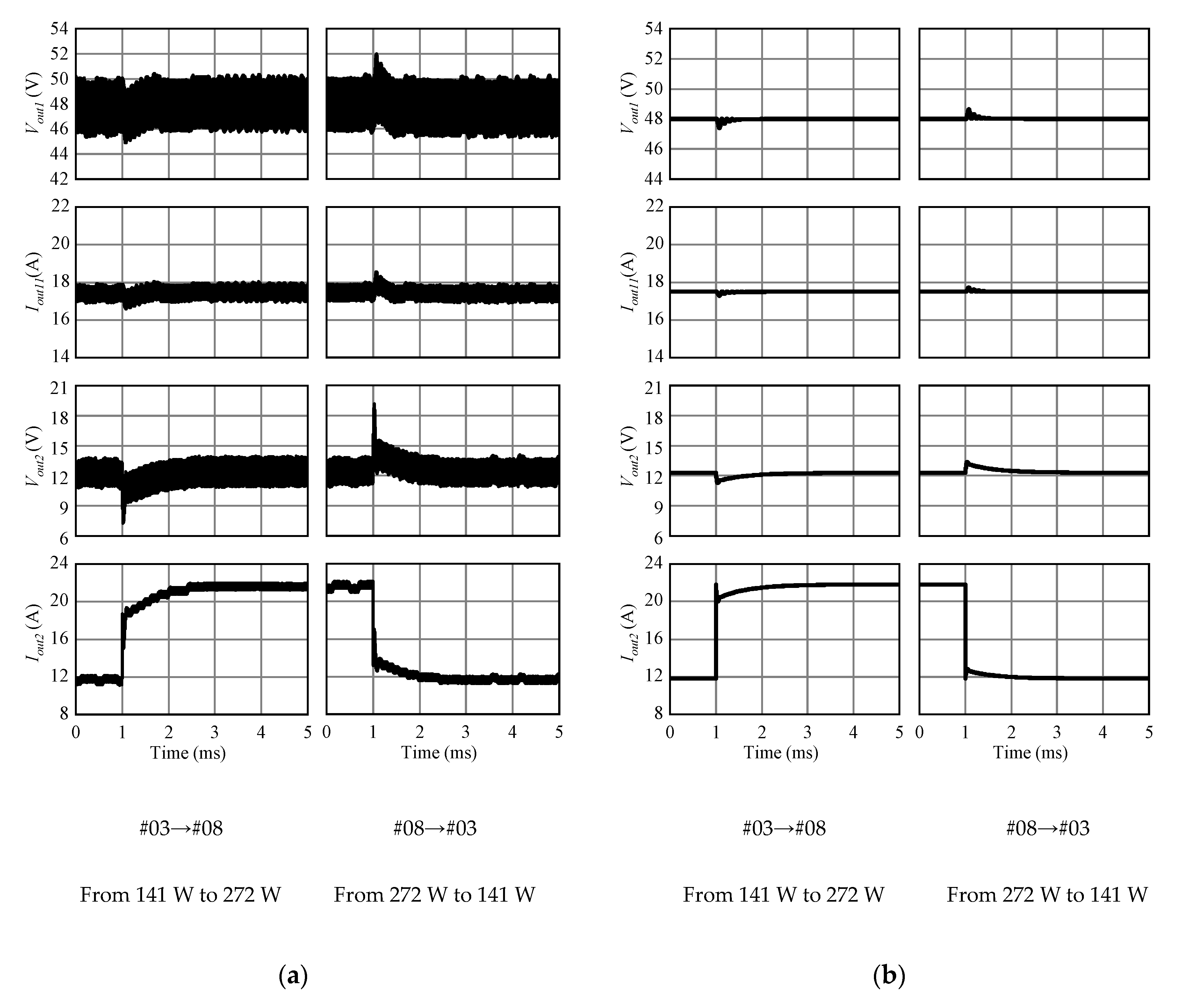

3.6. Detailed Operation Modes

- 2.

- 3.

- 4.

- 5.

- 6.

- 7.

- 8.

- 9.

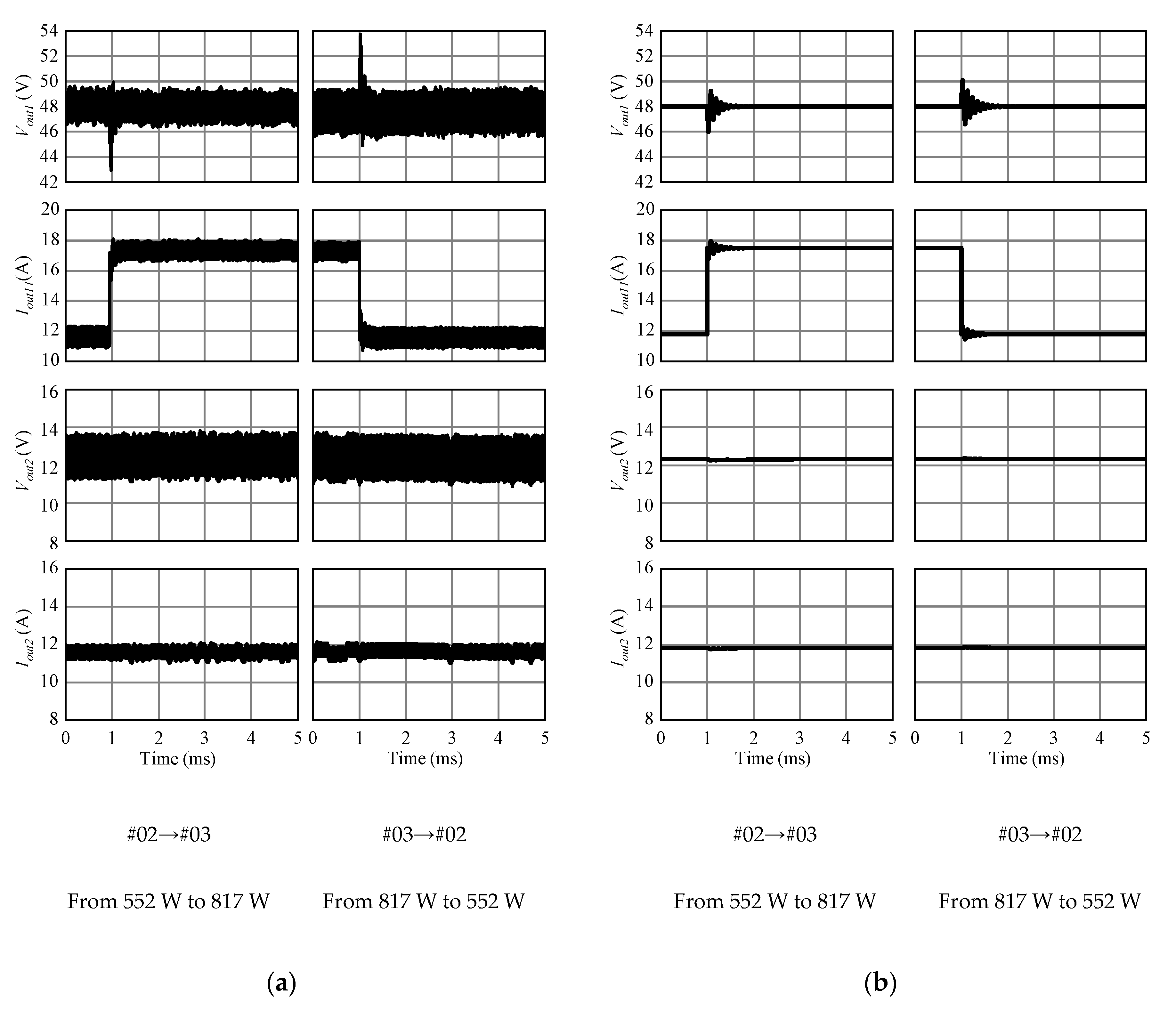

3.7. Load Disturbance Response Characteristics

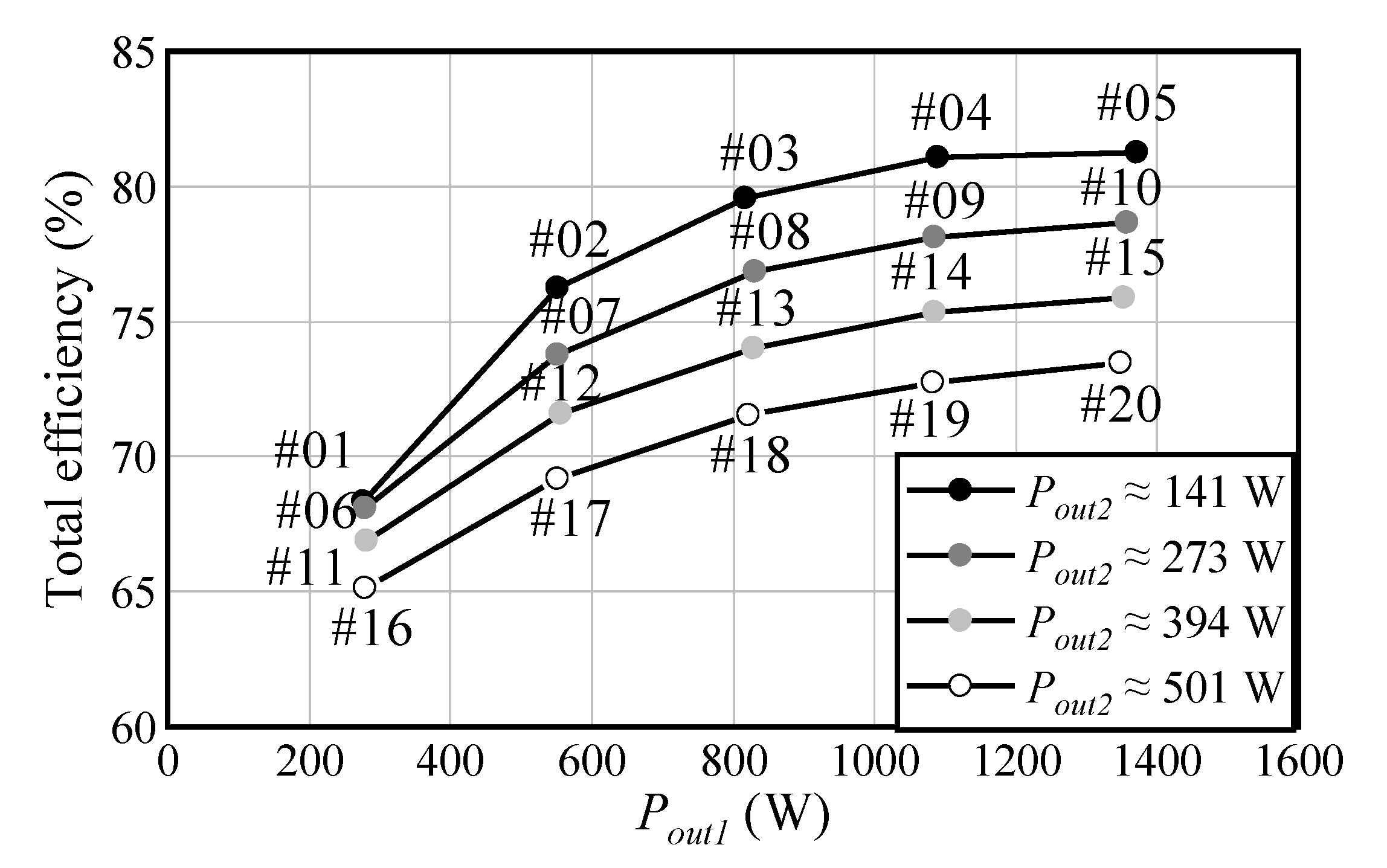

4. Efficiency and Loss Evaluation

4.1. Efficiency Characteristics

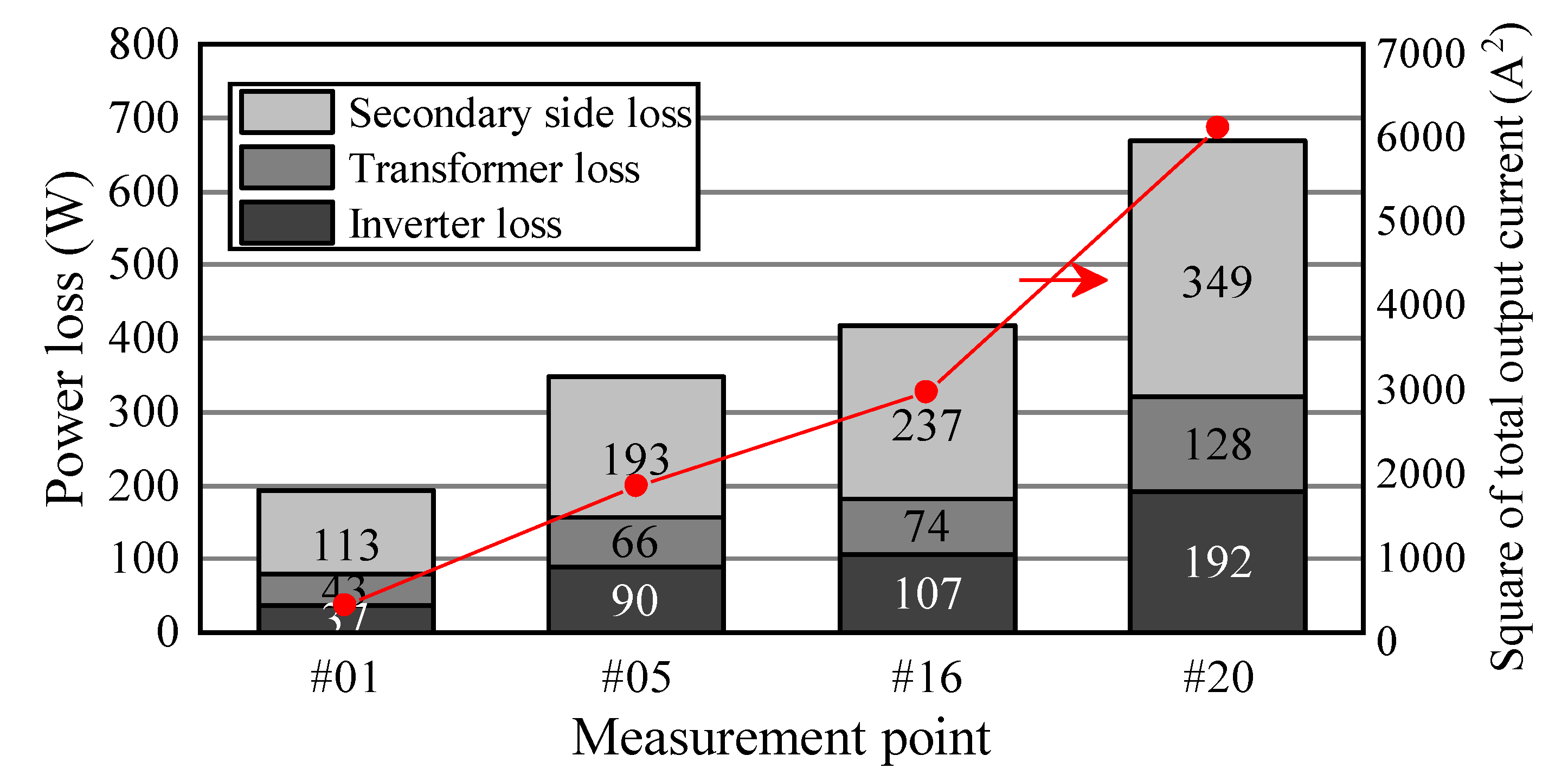

4.2. Loss Characteristics

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

Appendix A

References

- IEA–International Energy Agency, CO2 Emissions from Fuel Combustion: Overview. Available online: https://www.iea.org/reports/co2-emissions-from-fuel-combustion-overview (accessed on 2 November 2020).

- IEA–International Energy Agency, Global EV Outlook 2020. Available online: https://www.iea.org/reports/global-ev-outlook-2020 (accessed on 2 November 2020).

- Krismer, F.; Kolar, J.W. Efficiency-Optimized High-Current Dual Active Bridge Converter for Automotive Applications. IEEE Trans. Ind. Electron. 2012, 59, 2745–2760. [Google Scholar] [CrossRef]

- Hou, R.; Magne, P.; Bilgin, B.; Emadi, A. A topological evaluation of isolated DC/DC converters for Auxiliary Power Modules in Electrified Vehicle applications. In Proceedings of the 2015 IEEE Applied Power Electronics Conference and Exposition (APEC), Charlotte, NC, USA, 15–19 March 2015. [Google Scholar]

- Rhodes, K.; Kok, D.; Sohoni, P.; Perry, E.; Kraska, M.; Wallace, M. Estimation of the Effects of Auxiliary Electrical Loads on Hybrid Electric Vehicle Fuel Economy. SAE Tech. Pap. 2017, 1, 1155. [Google Scholar]

- Adriano, S.; Chiara, F.; Fabrizio, Z.; Alessandro, D.; Fabio, O.; Annalisa, D. Experimental Analysis of the Auxiliaries Consumption in the Energy Balance of a Pre-series Plug-in Hybrid-electric Vehicle. Energy Procedia 2014, 45, 779–788. [Google Scholar] [CrossRef]

- Teratani, T. Impact of DC48V on Automotive Power Supply Systems—Comparison with DC42V and Future View under DC60V—. IEEJ Trans. Ind. Appl. 2015, 135, 892–897. [Google Scholar] [CrossRef]

- Hayslett, S.; Maanen, K.V.; Wenzel, W.; Husain, T. The 48-V Mild Hybrid: Benefits, Motivation, and the Future Outlook. IEEE Electrif. Mag. 2020, 8, 11–17. [Google Scholar] [CrossRef]

- Chen, G.; Deng, Y.; Dong, J.; Hu, Y.; Jiang, L.; He, X. Integrated Multiple-Output Synchronous Buck Converter for Electric Vehicle Power Supply. IEEE Trans. Veh. Technol. 2017, 66, 5752–5761. [Google Scholar] [CrossRef]

- Matsushita, Y.; Noguchi, T.; Kimura, O.; Sunayama, T. Current-doubler based multiport DC/DC converter with galvanic isolation. In Proceedings of the 2017 IEEE 12th International Conference on Power Electronics and Drive Systems (PEDS), Honolulu, HI, USA, 12–15 December 2017. [Google Scholar]

- Jones, E.A.; de Rooij, M.; Biswas, S. GaN Based DC-DC Converter for 48 V Automotive Applications. In Proceedings of the 2019 IEEE Workshop on Wide Bandgap Power Devices and Applications in Asia (WiPDA Asia), Taipei, Taiwan, 23–25 May 2019. [Google Scholar]

- Martinez-heredia, J., M.; Colodro, F.; Mora-Jiménez, J.L.; Remujo, A.; Soriano, J.; Esteban, S. Development of GaN Technology-Based DC/DC Converter for Hybrid UAV. IEEE Access 2020, 8, 88014–88025. [Google Scholar] [CrossRef]

- Mitova, R.; Ghosh, R.; Mhaskar, U.; Klikic, D.; Wang, M.; Dentella, A. Investigations of 600-V GaN HEMT and GaN Diode for Power Converter Applications. IEEE Trans. Power Electron. 2014, 29, 2441–2452. [Google Scholar] [CrossRef]

- Huang, X.; Lee, F.C.; Li, Q.; Du, W. High-Efficiency GaN-Based Interleaved CRM Bidirectional Buck/Boost Converter with Inverse Coupled Inductor. IEEE Trans. Power Electron. 2016, 31, 4343–4352. [Google Scholar] [CrossRef]

- Imaoka, J.; Okamoto, K.; Kimura, S.; Noah, M.; Martinez, W.; Yamamoto, M.; Shoyama, M. A Magnetic Design Method Considering DC-Biased Magnetization for Integrated Magnetic Components Used in Multiphase Boost Converters. IEEE Trans. Power Electron. 2018, 33, 3346–3362. [Google Scholar] [CrossRef]

- Sugimura, K.; Yabu, N.; Sonehara, M.; Sato, T. Novel Method for Making Surface Insulation Layer on Fe-Based Amorphous Alloy Powder by Surface-Modification Using Two-Step Acid Solution Processing. IEEE Trans. Magn. 2018, 54, 2801805. [Google Scholar] [CrossRef]

- Liang, W.; Raymond, L.; Rivas, J. 3-D-Printed Air-Core Inductors for High-Frequency Power Converters. IEEE Trans. Power Electron. 2016, 31, 52–64. [Google Scholar] [CrossRef]

- Inoue, S.; Itoh, K.; Ishigaki, M.; Sugiyama, T. Magnetically integrated isolated bidirectional three-port DC-DC converter. In Proceedings of the 2017 19th European Conference on Power Electronics and Applications (EPE’17 ECCE Europe), Warsaw, Poland, 11–14 September 2017. [Google Scholar]

- Dao, N.D.; Lee, D.; Phan, Q.D. High-Efficiency SiC-Based Isolated Three-Port DC/DC Converters for Hybrid Charging Stations. IEEE Trans. Power Electron. 2020, 35, 10455–10465. [Google Scholar] [CrossRef]

- Tang, Y.; Lu, J.; Wu, B.; Zou, S.; Ding, W.; Khaligh, A. An Integrated Dual-Output Isolated Converter for Plug-in Electric Vehicles. IEEE Trans. Veh. Technol. 2018, 67, 966–976. [Google Scholar] [CrossRef]

| Operation Mode | 1 | 2 | 3 | 4 | 5 | 6 |

|---|---|---|---|---|---|---|

| Vtxs | 1 | 1 | 0 | −1 | −1 | 0 |

| S5 | off | on | - | - | - | - |

| S6 | - | - | - | off | on | - |

| Symbol | Value | Symbol | Value |

|---|---|---|---|

| Vout1 | Vout2 | ||

| Iout1 | Iout2 | ||

| γL11 γL12 | γL21 γL22 | ||

| Δic1 | Δic2 |

| Parameter | Value |

|---|---|

| Vin | 300 V |

| Cin | 330 μF |

| Vout1 (current doubler side) | 48 V |

| Vout2 (step-down chopper side) | 12 V |

| Switching frequency | 400 kHz (T = 2.5 μs) |

| FPGA | XC7K70T-1FBG484C (Xilinx) |

| Clock frequency of FPGA | 200 MHz |

| S1, S2, S3, S4, S5, S6 | SCT3030AL (ROHM) |

| D1, D2 | FFSH4065A (ON Semiconductor) |

| Transformer turns ratio | N1:N2 = 4:2 |

| L11 and L12 | 15 μH |

| L21 and L22 | 5 μH |

| C1 | 44 μF |

| C2 | 188 μF |

| Instrument | Model Number |

|---|---|

| Oscilloscope | HDO6104A-MS (TELEDYNE) |

| Voltage differential probe | 700924 (YOKOGAWA) |

| Current probe (<30 A) | TCP312A (Tektronix) |

| Current probe (>30 A) | TCP303 (Tektronix) |

| Deskew calibration source | DCS025 (TELEDYNE) |

| Operation Point | Operation Mode | |||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | 2-1 | 2-2 | 3-1a | 3-1b | 3-2 | 4 | 5 | 6 | 7 | 8 | 9 | |

| t1~t2 | t2~t3 | t3~t5 | t5~t6 | t6~t7 | t7~t8 | t8~t9 | t9~t10 | t10~t11 | ||||

| #01 | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | |||

| #05 | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ||

| #16 | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | |||

| Part | Symbol | Equation |

|---|---|---|

| Total loss | Wtotal | Pin − (Pout1 + Pout2) |

| Inverter loss | Winv | Pin − Ptxp |

| Transformer loss | Wtx | Ptxp − Ptxs |

| Secondary side loss | Wsec | Wtotal − (Winv + Wtx) |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Matsushita, Y.; Noguchi, T.; Taguchi, N.; Ishii, M. 2 kW Dual-Output Isolated DC/DC Converter Based on Current Doubler and Step-Down Chopper. World Electr. Veh. J. 2020, 11, 78. https://doi.org/10.3390/wevj11040078

Matsushita Y, Noguchi T, Taguchi N, Ishii M. 2 kW Dual-Output Isolated DC/DC Converter Based on Current Doubler and Step-Down Chopper. World Electric Vehicle Journal. 2020; 11(4):78. https://doi.org/10.3390/wevj11040078

Chicago/Turabian StyleMatsushita, Yoshinori, Toshihiko Noguchi, Noritaka Taguchi, and Makoto Ishii. 2020. "2 kW Dual-Output Isolated DC/DC Converter Based on Current Doubler and Step-Down Chopper" World Electric Vehicle Journal 11, no. 4: 78. https://doi.org/10.3390/wevj11040078

APA StyleMatsushita, Y., Noguchi, T., Taguchi, N., & Ishii, M. (2020). 2 kW Dual-Output Isolated DC/DC Converter Based on Current Doubler and Step-Down Chopper. World Electric Vehicle Journal, 11(4), 78. https://doi.org/10.3390/wevj11040078