1. Introduction

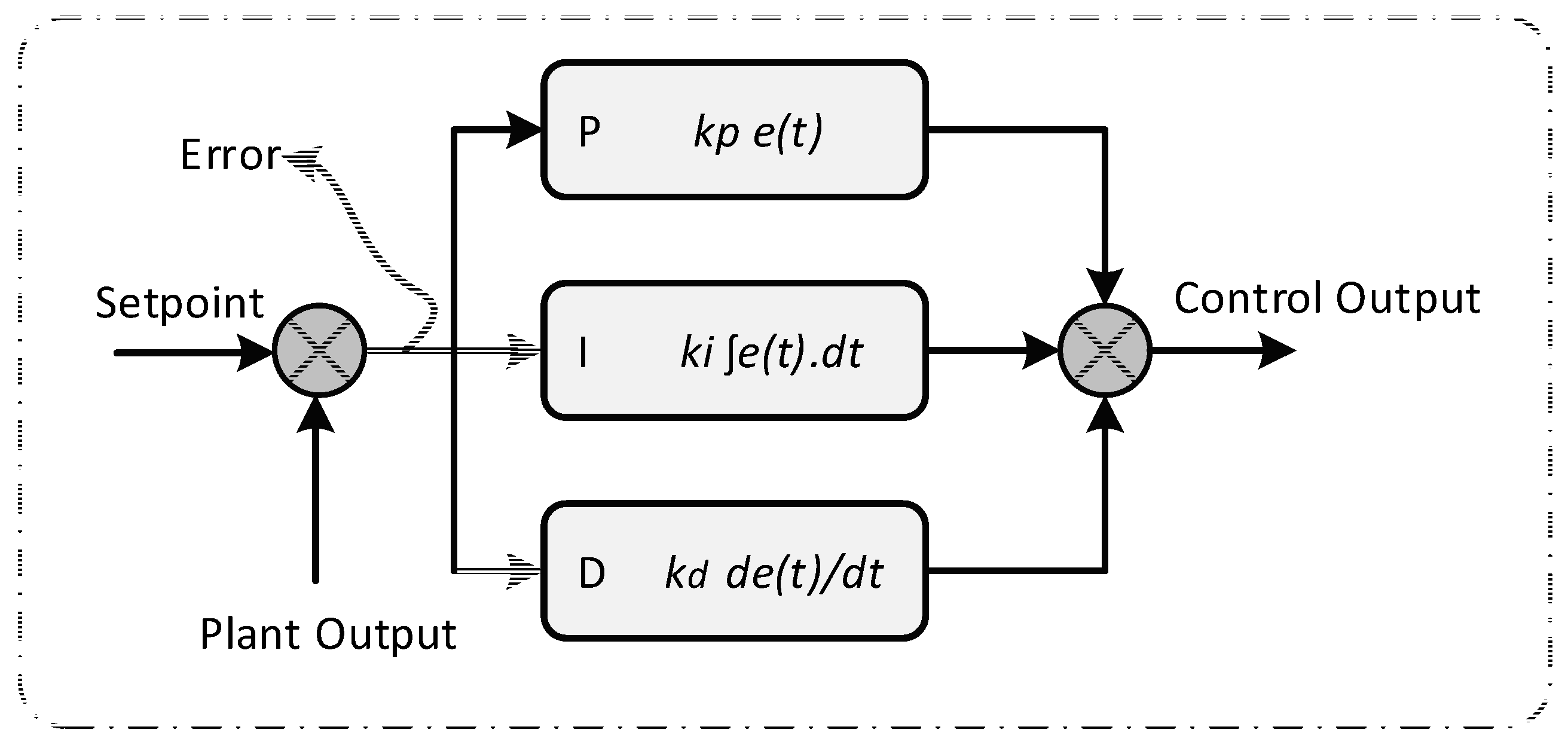

Although novel and effective theories and design methodologies are being continually developed in the digital control field, proportional–integral–derivative (PID) controllers are still the most widely adopted solution for control problems in both academic and industry sectors. The tuning of the parameters of the PID controllers has been proved a hard task and several approaches have been investigated in the past [

1,

2] using analytical methods, heuristic methods, such as Ziegler–Nichols (Z–N) rule, frequency response methods, artificial intelligence such as fuzzy logic [

3], and iterative learning approaches [

4]. Evolutionary algorithms (EA), such as genetic algorithms (GA) [

5] and particle swarm optimization (PSO) [

6], used in intelligent control applications, have been also proposed as an efficient solution for tuning the PID parameters. The simplicity and speed convenience of evolutionary algorithms force the controller quickly seek out the optimal output value.

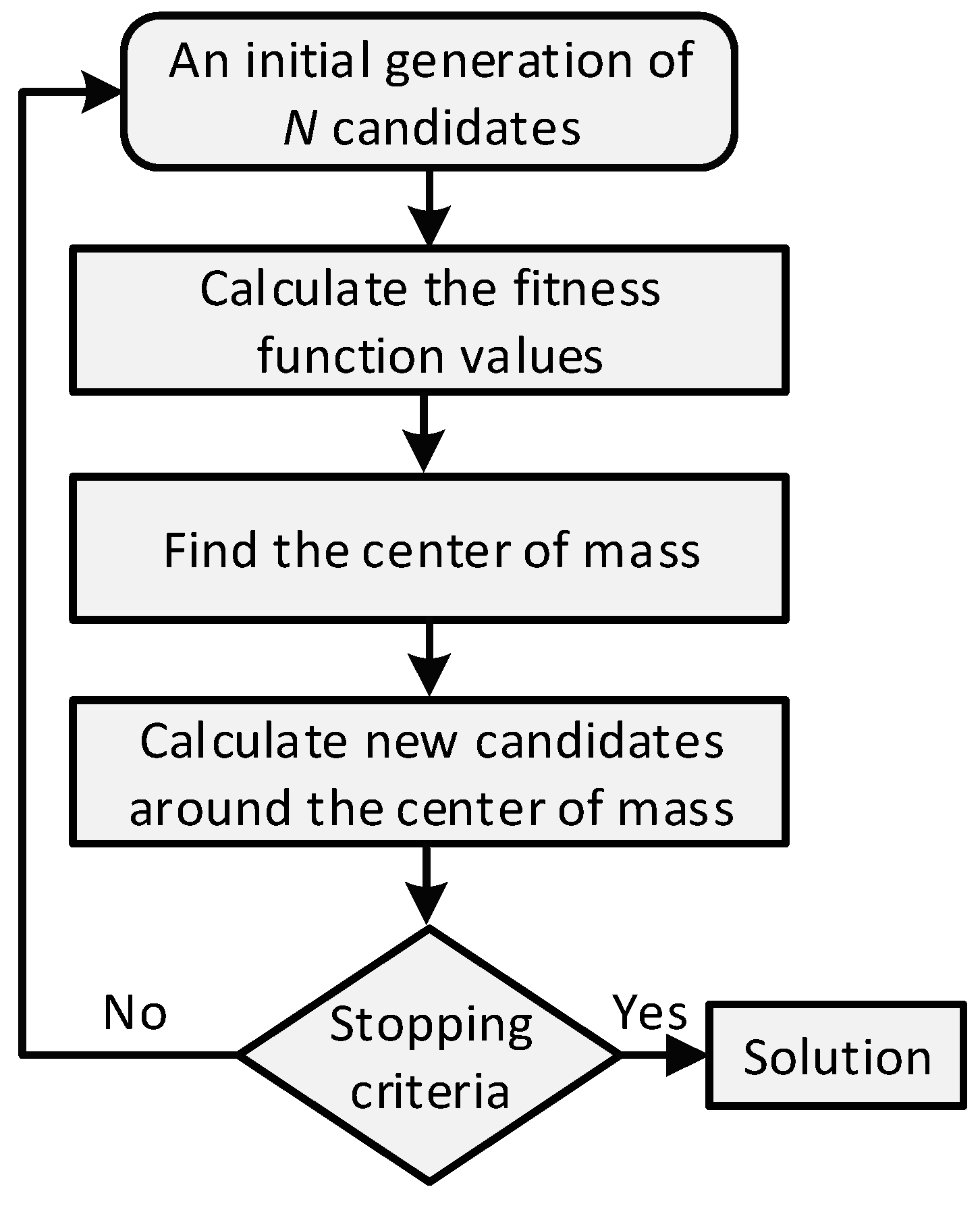

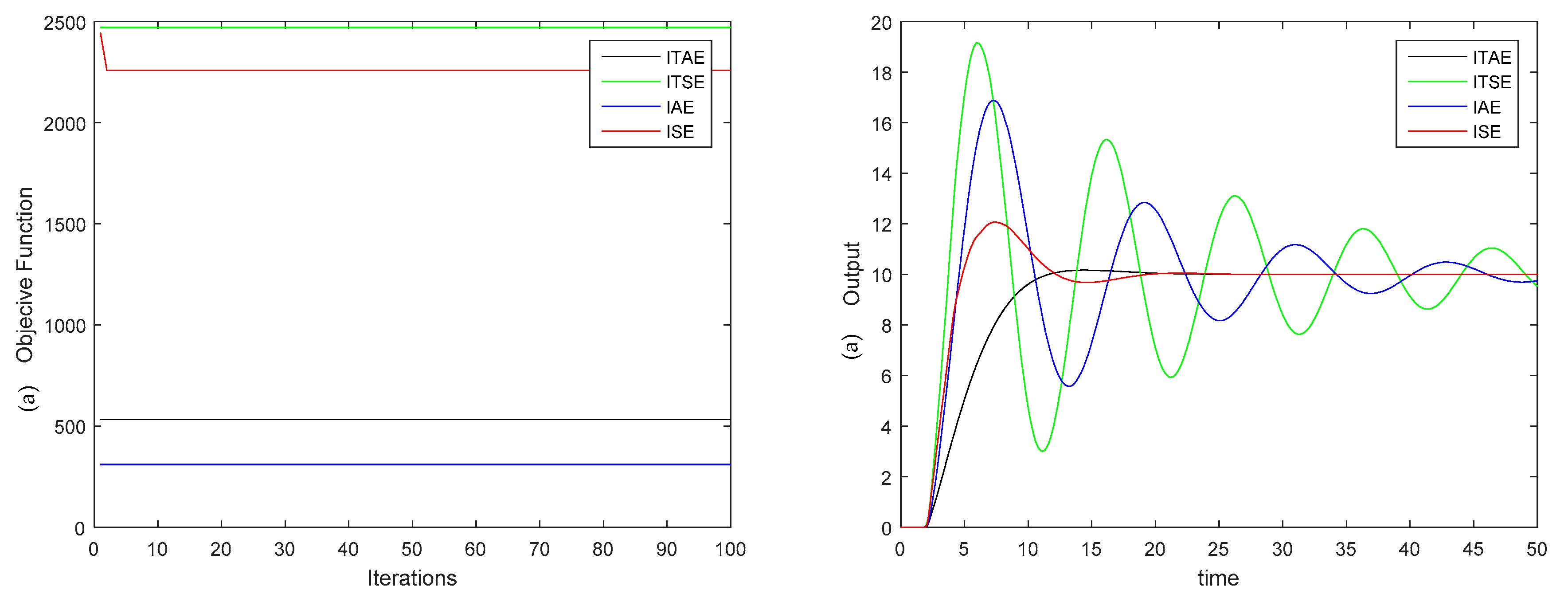

In this paper, we study the use of an evolutionary algorithm, named Big Bang–Big Crunch (BB–BC) [

7], to optimize PID controller gains. BB–BC optimization algorithm is used to minimize performance control measures, integral absolute error (IAE), integral time absolute error (ITAE), integral square error (ISE), and integral time square error (ITSE) while minimizing the system overshoot. The key idea of using BB–BC here can be explained as the transformation of a convergent solution to a chaotic state and then back to a single tentative solution point. BB–BC algorithm has been implemented in various engineering applications, especially where the computational time and convergence time are important factors [

8]. Some representative optimization problems, where the efficiency of BB–BC has been demonstrated, are the following: optimal design of truss structures [

9], Schwedler and ribbed domes [

10], concrete retaining walls [

11], fuzzy inverse controllers [

12], and fuzzy PID controllers [

13]. Moreover, BB–BC algorithm has been adopted in real-time applications where the optimization task is adaptive or must be solved in relatively small sampling intervals. Besides its low computational time and high global convergence speed, another advantage of BB–BC, especially important for auto-tuning processes, is that it does not need gradient information and therefore can operate to minimize naturally defined cost functions without complex mathematical operations.

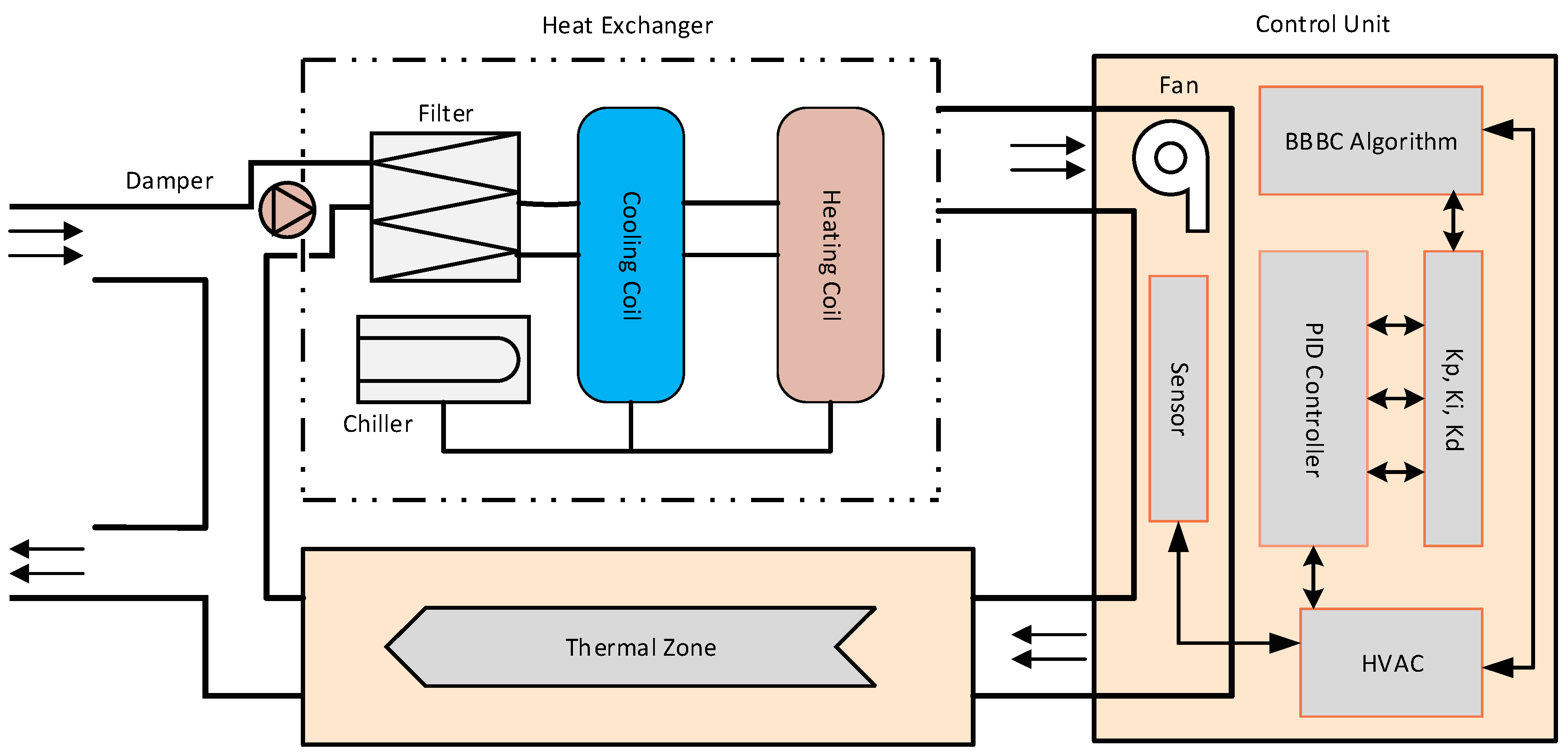

We evaluate the efficiency of BB–BC to tune the parameters of a PID controller used in a second-order heat, ventilation, and air conditioning (HVAC) system. In the HVAC system, the supply air pressure is regulated by the speed of a supply air fan. Increasing the fan speed will increase supply air pressure, and vice versa. The dynamics from the fan variable speed drive to the supply air pressure can be modeled as a second order plus dead time. This process is well established by Bi and Cai [

14]. In real applications, however, where both fans and dampers exhibit non-linear properties for different working points, even a well-tuned PID controller may not be able to achieve a desired performance for all set points and process variations. Thus, we investigate how fast and accurate the BB–BC algorithm can tune the PID controller parameters in this HVAC system.

To further reduce the optimization latency of the control system, the BB–BC algorithm along with the PID controller, are accelerated using FPGA technology. Up to now, embedded computers, built around programmable microcontrollers, were the dominant computing platform for implementing PID controllers in industrial environments. The last decades, the field programmable hardware technology, also known as field programmable gate arrays (FPGAs), has emerged as an alternative solution for controlling industrial applications. The main advantages of the FPGA technology are reduced engineering cost, reduced time-to-market, high performance due to the exploitation of fine-grained hardware parallelism, and adaptation to control system requirements. Especially for control systems that use demanding computational intelligence techniques, the advanced performance of FPGAs combined with their low-cost and high adaptability render them an attractive computing platform. Taking also into consideration the real-time requirements of our HVAC system, we propose the FPGA-based acceleration of the BB–BC optimization algorithm and the PID controller to speed up the parameters tuning process, and consequently, improve system performance.

The BB–BC, PID controller and register transfer level (RTL) models have been described using the VHDL language and implemented in the Xilinx Zybo (Zynq) development board from Xilinx Corporation (San Jose, CA, USA). Built around the Xilinx Zynq XC7Z010 FPGA device. Moreover, the FPGA-in-the-loop (FIL) technique has been used to enable the emulation of the plant (HVAC) in MATLAB/Simulink environment in conjunction with the execution of the PID controller and the optimization process in the real hardware; this way, the FIL technique facilitates the evaluation of the entire system in higher abstraction layers [

15].

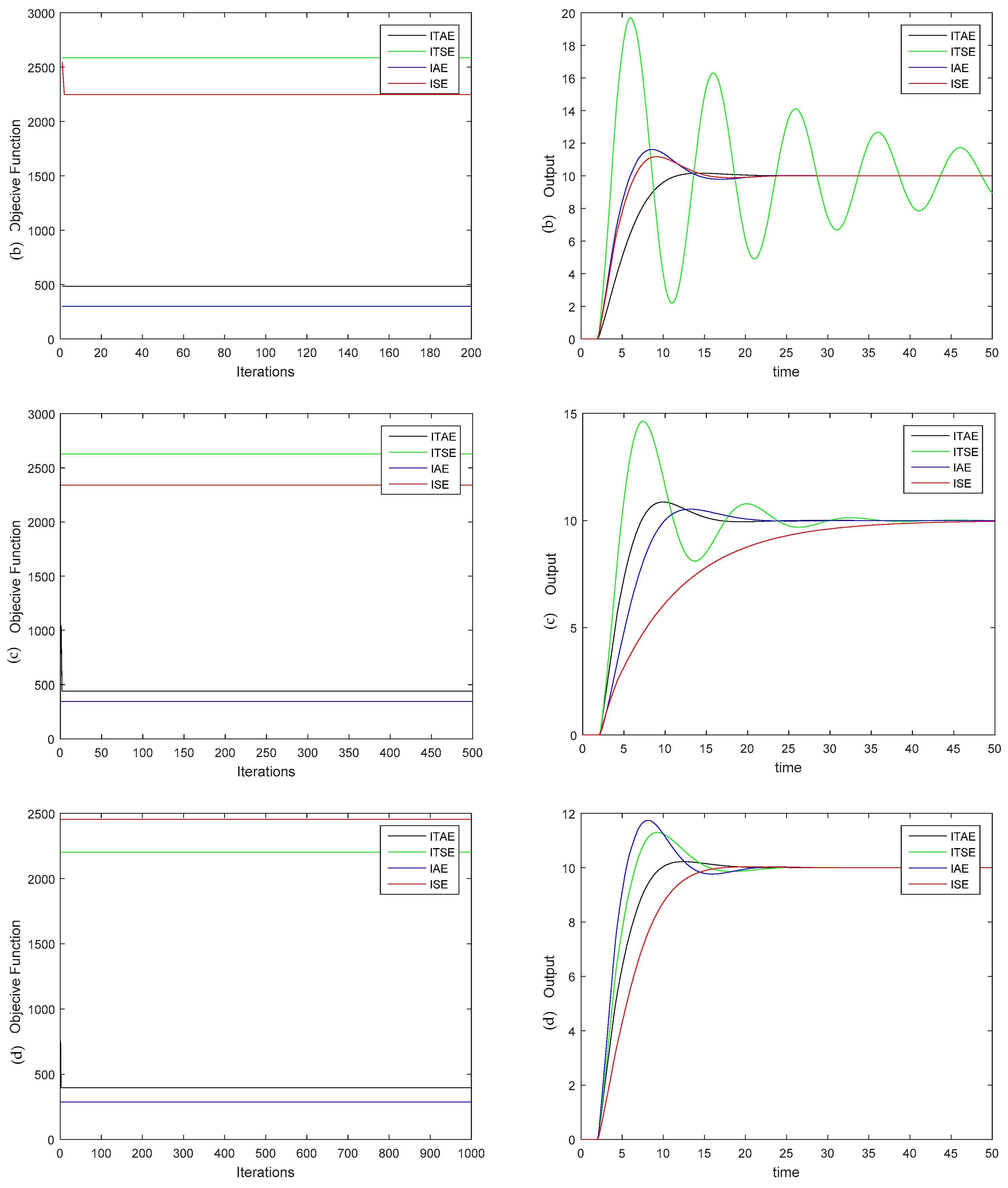

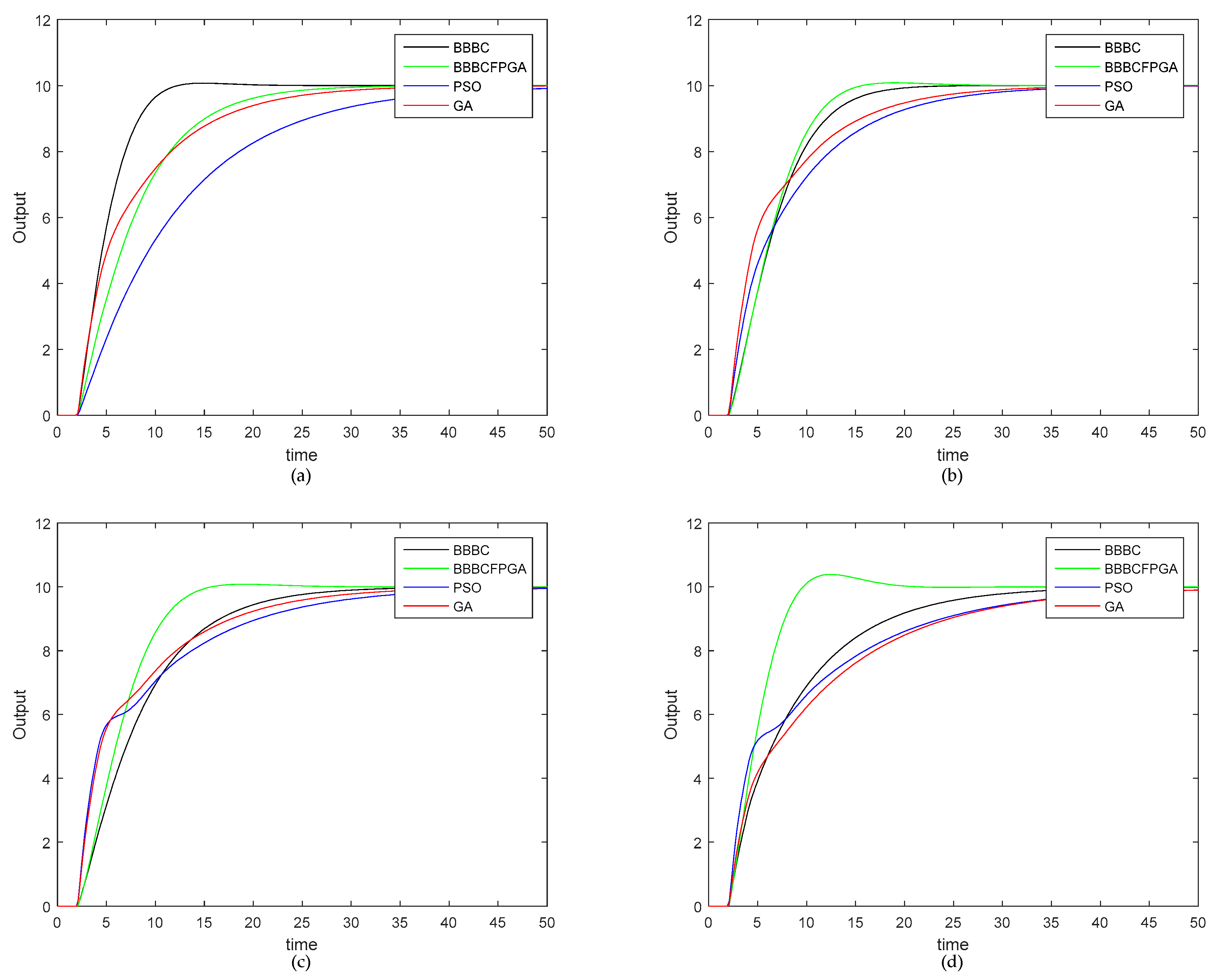

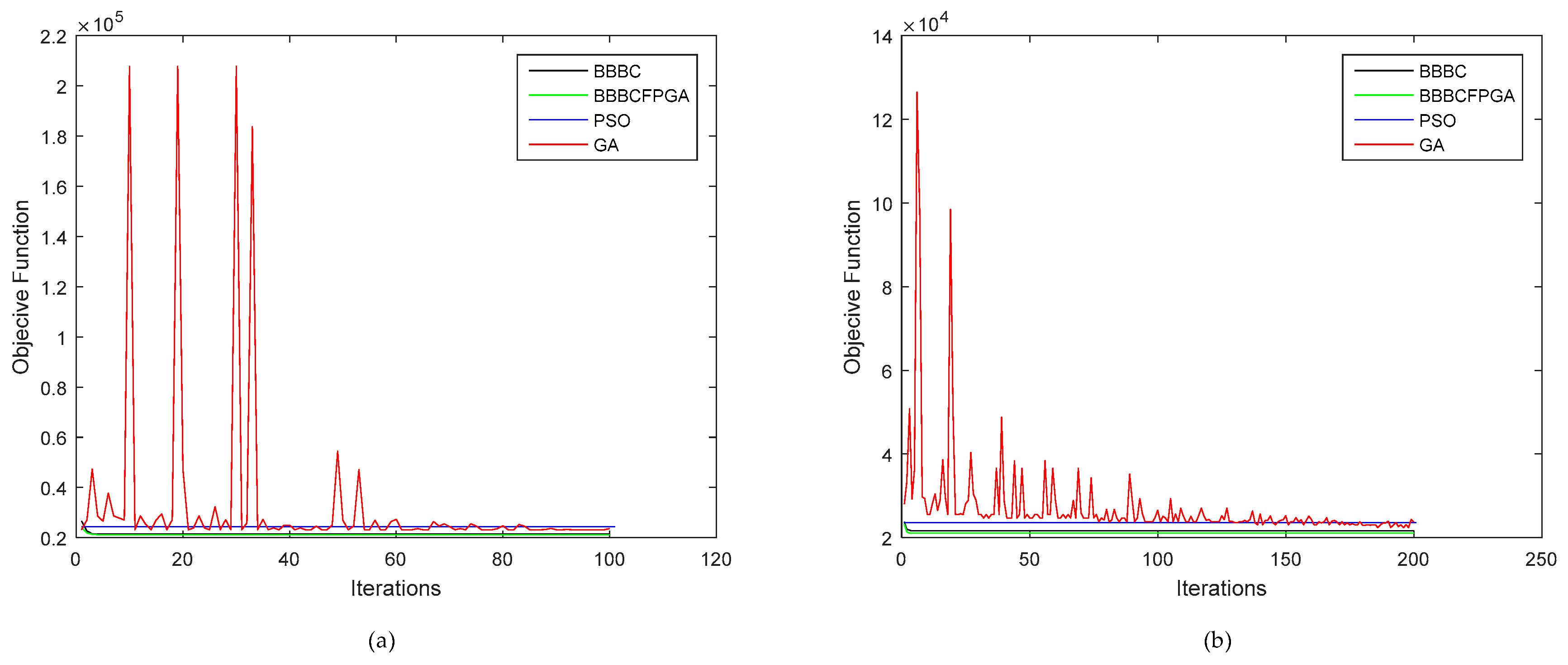

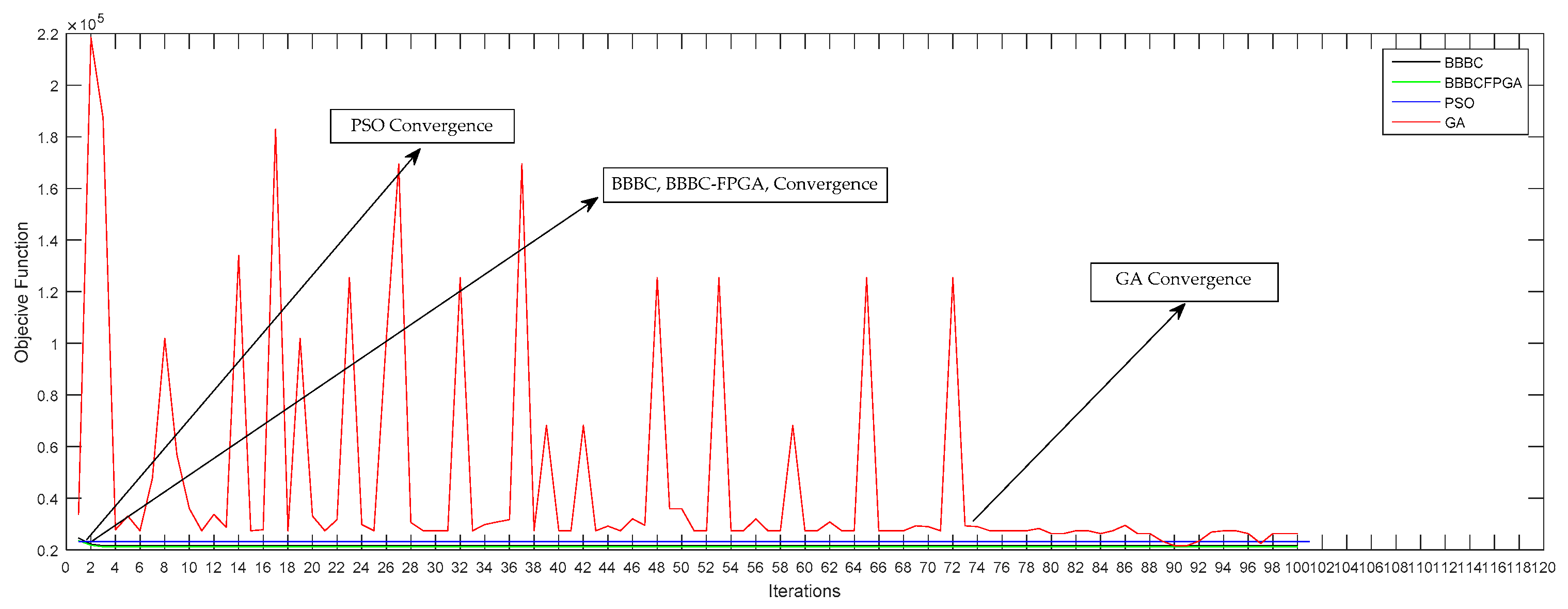

In order to demonstrate the efficiency of the proposed approach, we run various experiments in a second order system with two sec time delay and compared it with GA and PSO optimization algorithms in terms of PID tuning speed and convergence speed. The experimental results showed that the FPGA–BB–BC algorithm tunes the PID controller parameters ~430X faster than the software version of GA algorithm, ~539X faster than the software version of PSO algorithm, and ~270X faster than the software version of BB–BC algorithm. Furthermore, the proposed approach was tested under various fitness functions (error) for different number of iterations, and the integral time absolute error (ITAE) was chosen.

The organization of this paper is given as follows.

Section 2 shortly describes the basics of PID controllers and BB–BC optimization algorithm.

Section 3 presents the HVAC optimization problem and the proposed BB–BC-based tuning process of the PID parameters.

Section 4 describes the FPGA implementation of the PID and BB–BC subsystems and the FIL approach.

Section 5 presents the experimental results and demonstrates the efficiency of the proposed approach, while

Section 6 concludes the paper.

4. FPGA Implementation of PID Controller and BB–BC

The FPGA technology provides an effective solution in several industrial control applications due to its low development cost, high flexibility, and limited power consumption, while it has been proved an ideal processing platform for industrial applications with real-time constraints due to the acceleration achieved by the hardware parallelism. In this paper, we propose the use of FPGA technology to implement the BB–BC algorithm that calculates and optimizes the PID control parameters, (kp, ki, kd) in order to accelerate the control system process, which can be very effective for latency-sensitive applications.

4.1. PID Controller in FPGA

In the past, several approaches have proposed the use of FPGA technology to implement PID controllers [

20,

21] and/or optimize the PID controller parameters in real-time industrial applications, such as DC motor speed control system [

22]. In [

23], a fuzzy logic controller has been implemented on an FPGA platform and validated on a real-time application, namely a truck backer-upper control system. In [

24], the authors presented a runtime reconfigurable PID controller that can dynamically switch between the different controller variants, e.g., PI, PD, PI-PD, etc., as the control requirements change.

Figure 5 shows the block diagram of a typical PID controller FPGA architecture based on the differential Equation (6) and the parameters of

Table 1.

The PID controller architecture consists of five registers blocks, for storing the current and previous error values, i.e.,

e(

n),

e(

n − 1),

e(

n − 2),

u(

n − 1), and

u(

n − 2). Notice that the PID controller has a five-stage pipeline structure in order to increase clock frequency. Five arithmetic multipliers are used to multiply the proportional part, derivative part integral part with the corresponding parameters (

,

, and

, respectively) and the output signal with (

and

) as described in

Table 1, while the adder finally sums all factors. Embedded DSP slices of the FPGA device are used for the implementation of arithmetic multipliers and adders in order to improve the design area and speed.

4.2. BB–BC Algorithm in FPGA

Several FPGA-based implementations of evolutionary algorithms have been presented in the literature to accelerate the optimization process. Most of these approaches focus on the optimal design of hardware accelerators to achieve high performance and flexibility [

25,

26] and satisfy other genetic algorithm features, such as multi-objective optimization [

27]. In our approach, we adopted the BB–BC optimization algorithm due to its low computational time and high global convergence speed. These features of the BB–BC algorithm mainly motivated our work, since an FPGA-based BB–BC accelerator can greatly reduce the computational time providing an ideal platform for large-scale adaptive or latency-sensitive optimization problems [

28].

In this subsection, we describe the FPGA design architecture of the BB–BC algorithm.

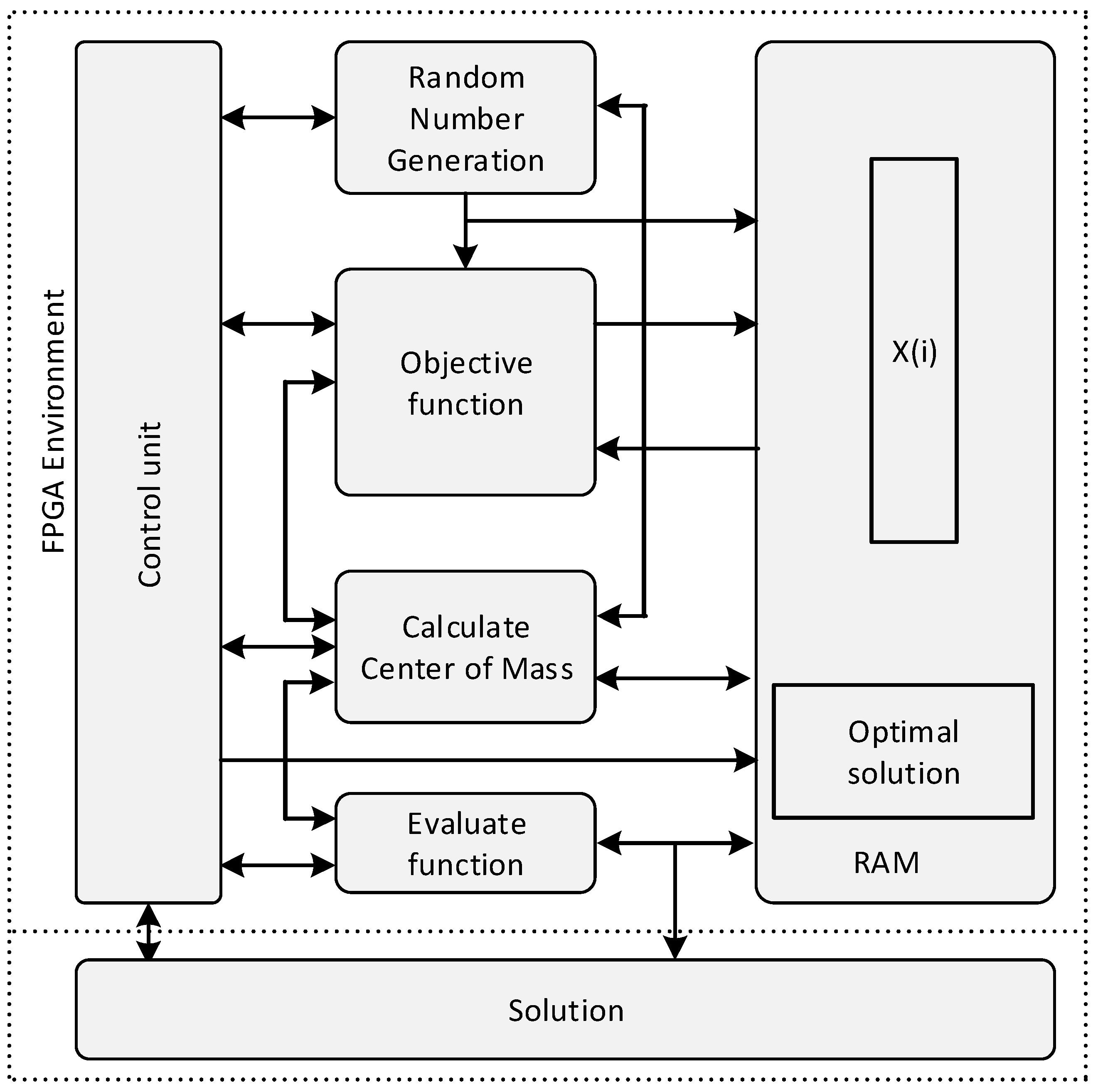

Figure 6 depicts the top-level design diagram of the FPGA BB–BC architecture consisting of the following blocks:

Random Number Generation: It generates the random numbers (), either to form an initial population (iteration 0) or to form new candidates around the CoM (iteration > 0). A typical linear feedback shift register (LFSR) is used to generate random numbers based on a configurable seed. Note that the boundaries of the random numbers are determined by the upper and lower values of the optimization function variables. In each iteration, the module generates N candidates sequentially, where N is the population size, with each one consisting of L random numbers, where L is the number of features of each candidate. The generated random numbers of each iteration are stored in a RAM in order to be processed later for the calculation of center of mass.

Objective Function: After the random number generation, this module calculates the objective function (

) for each candidate (

) using the ITAE equation, which is also stored in the RAM. Both the random number generation and objective function modules have been implemented following a simple, serial processing model, where a single element is processed in each clock cycle, providing a low-cost FPGA circuit. Note that both modules can be parallelized (i.e., to generate the random numbers and calculate the objective functions concurrently using many processing elements working in parallel) and pipelined in order to improve performance, as proposed in [

28].

Calculate Center of Mass: It reads the candidates and their objective function values from the RAM and calculates the center of mass which is forwarded in the random number generation module to generate the population in the next iteration cycle.

Evaluate Function: It reads the objective function values of the candidates from the RAM in order to select the best fitness candidate which is store in RAM too, and from output signal when the FPGA-BBBC control the HVAC model.

Control Unit: It orchestrates the operation of the other modules and repeats the BB–BC steps until the stopping criteria are met.

Solution: It includes a register that stores the outcome of the BB–BC algorithm.

Note that a high-performance FPGA architecture of BB–BC algorithm has been presented in [

28] which incorporates parallel pipelined engines to accelerate the execution of BB–BC. This FPGA BB–BC architecture has been optimized in terms of execution latency and is very suitable for control applications with strict real-time requirements. However, this performance optimization has been achieved at the expense of extra hardware area and power consumption. Thus, the optimized FPGA architecture of [

28] is suggested only for time sensitive control applications.

Table 3 presents the device utilization summary on a Xilinx Zynq XC7Z010 FPGA device.

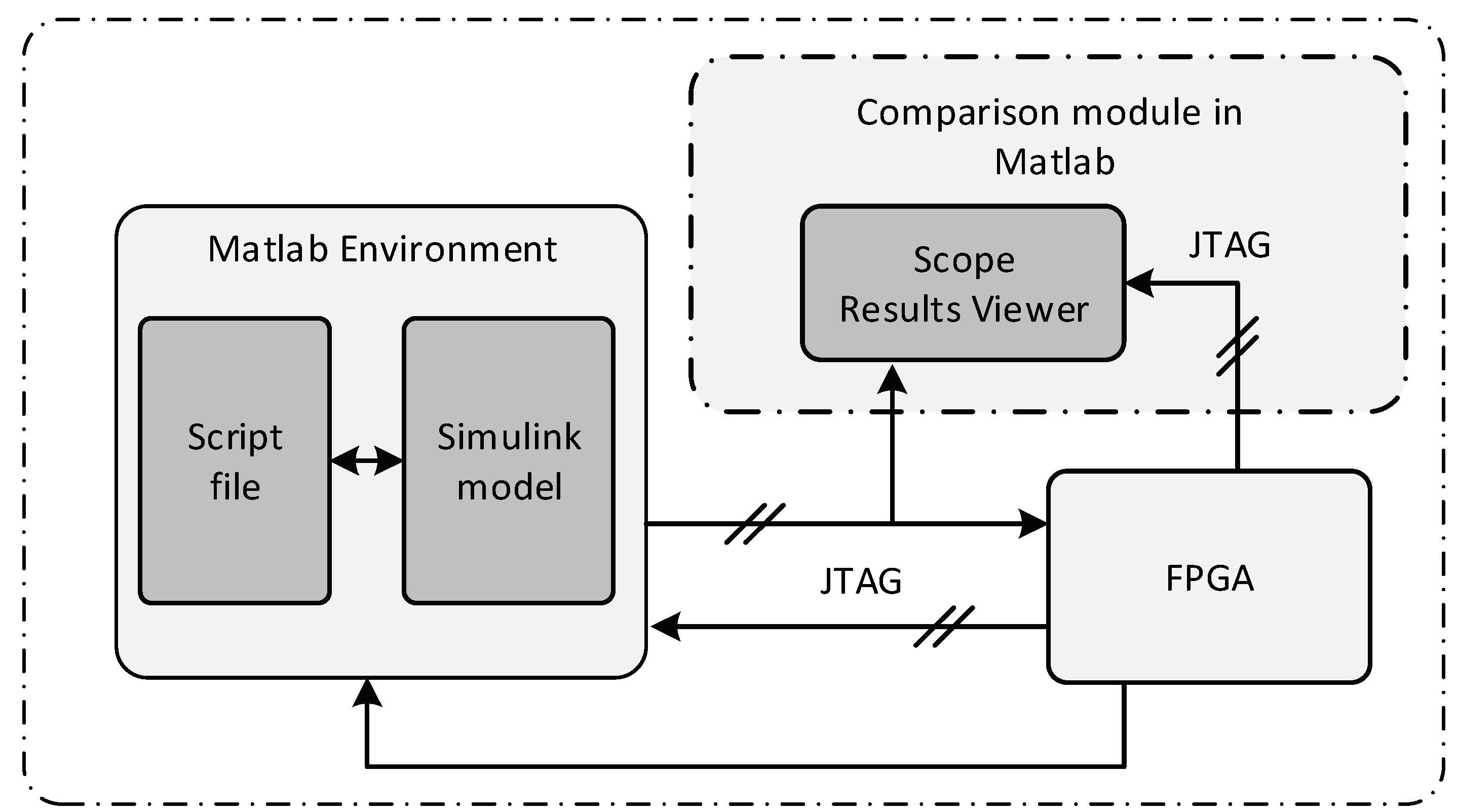

4.3. FPGA-In-The-Loop (FIL)

MATLAB/Simulink is a high-level language and interactive environment highly popular among system and algorithm designers for many different real-world applications and research topics. To accommodate developers to interface with real hardware (e.g., components implemented in FPGA devices), MathWorks

® presented the FPGA-in-the-loop (FIL) concept. Based on this idea, data can be exchanged between the MATLAB/Simulink modules and the FPGA device. FIL scheme can be used for multiple tasks while designing, evaluating, and verifying designs. For example, it can be used to configure and tune FPGA design parameters at runtime, such as tuning data pipe gains and modifying filter parameters [

29], or to monitor hardware components by reading specific status registers at runtime. Another powerful capability of the FIL approach is that allows the generation of complex stimulus datasets on the host PC and rapid download to the FPGA target in real time [

29]. By using the FIL approach and connecting the hardware target via some common protocol interface (e.g., Ethernet or JTAG), one can obtain significant improvements in simulation runtime compared to cycle-accurate host simulation.

As shown in

Section 5, the proposed approach in conjunction with the FIL technique achieves a speedup of around 253X compared to the MATLAB 2015b software simulation. Moreover, when design complexity increases, the advantages of the FIL methodology over software simulation at runtime will be more evident.

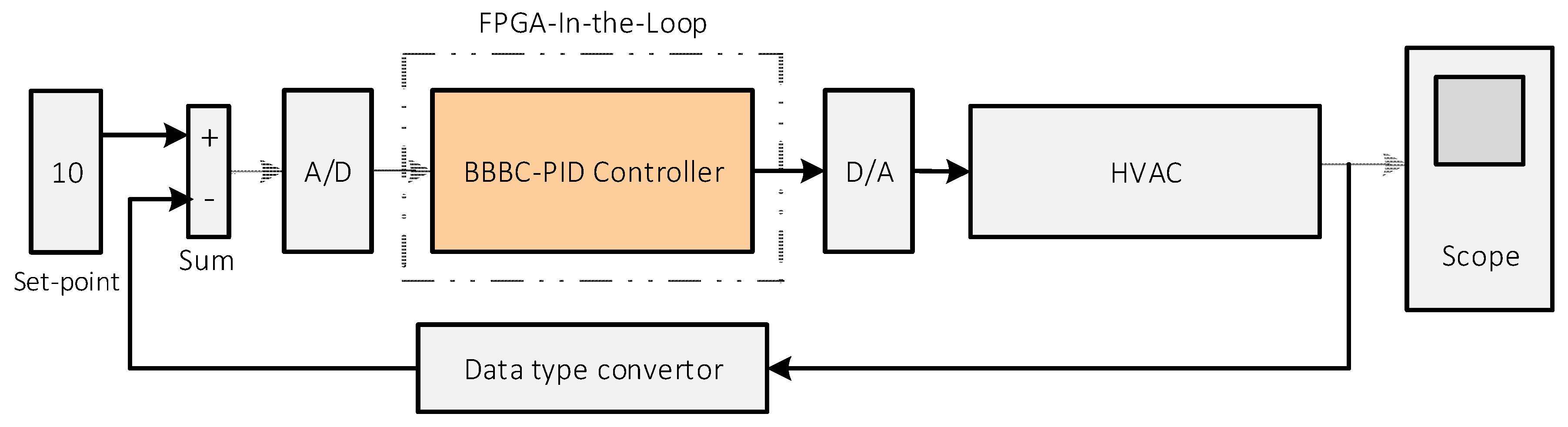

Figure 7 presents the structure of the FIL acceleration scheme used in our system, where MATLAB/Simulink provides the user with a working environment.

4.4. System Architecture

The FPGA design consisting of the PID controller and the BB–BC algorithm is written in VHDL hardware description language and implemented in a Xilinx development platform, Zybo–7010 board, using the Xilinx ISE Design Suite 14.7 and Vivado Design Suite.

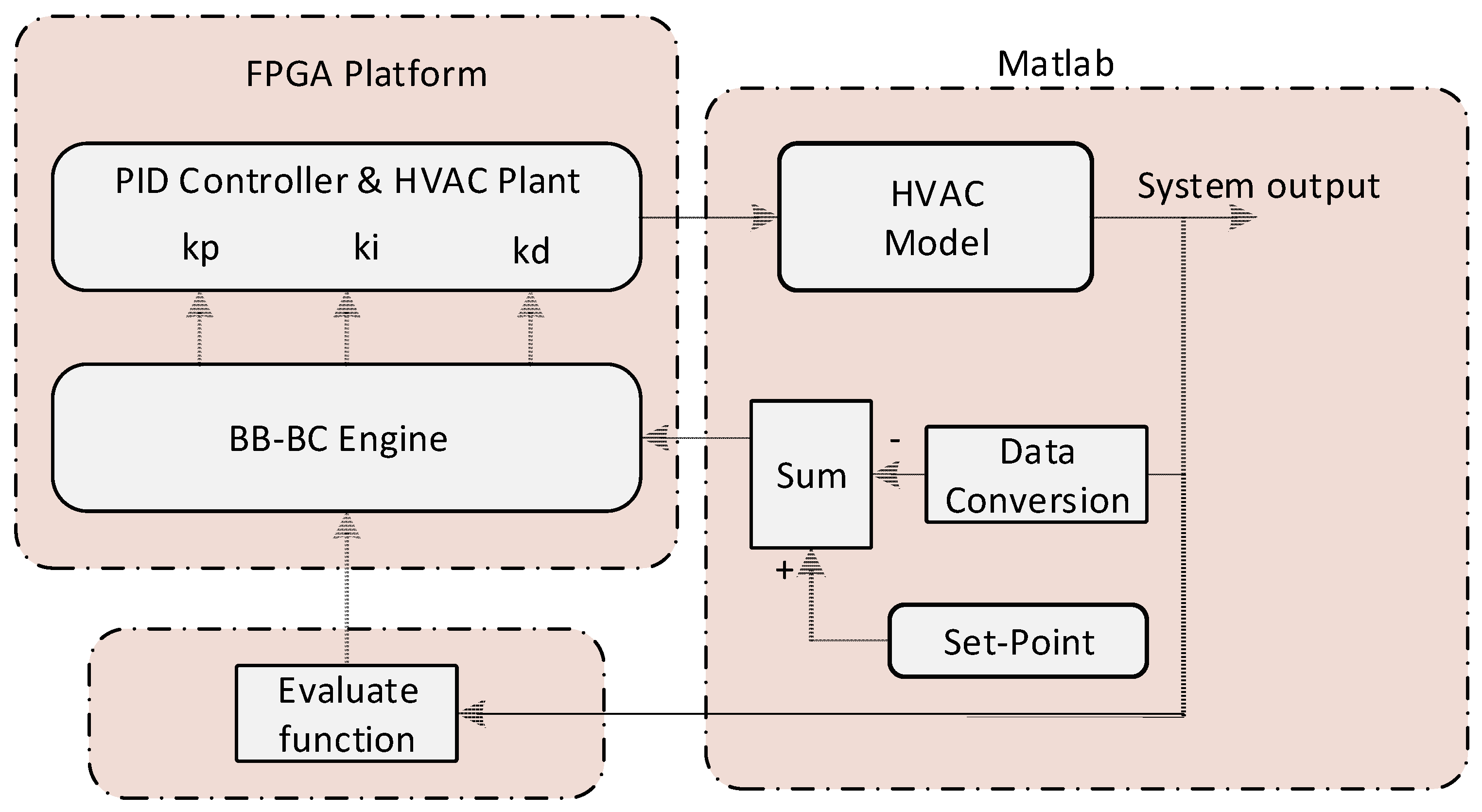

Figure 8 depicts the entire system architecture including the FPGA device and the HVAC model implemented in MATLAB environment. The processing steps of the proposed architecture are shortly described below.

- (1)

The FPGA BB–BC module generates a set of random PID parameters (kp, ki, kd), either to form the initial candidate or the new candidate around the center of mass in the next iteration cycles.

- (2)

The FPGA PID controller module receives the values of the parameters and controls the HVAC plant.

- (3)

The FPGA BB–BC module calculates the fitness functions for this candidate (i.e., PID parameters) using the ITAE equation and then calculates the new center of mass.

- (4)

The HVAC model runs for a short period.

- (5)

The evaluate function checks the system output and decides whether the BB–BC module must re-run to improve system performance, i.e., when the system has been affected by external disturbances that cause the output to exceed some predefined thresholds. Note that we use the HVAC plant as a part of the FPGA BBBC module to produce the first optimization parameters (kp, ki, kd) of the PID controller for the HVAC model in the first run.

Given that the evolutionary algorithms consume enough time to reach the optimal solution, even when the number of iterations is small, they are not suitable for latency-sensitive applications in real time. However, accelerating the evolutionary algorithm using an FPGA-based platform, as in the case of FPGA-in-the-loop (FIL) paradigm, can reduce the execution time and achieve the convergence into the optimal solution under specific timing constraints. Therefore, the FPGA-based BB–BC algorithm can be executed much faster, fact that improves confidence that the target optimization algorithm can finally satisfy the real-time requirements of an industrial application.

The total execution time of the MATLAB/Simulink model (

) incorporates the MATLAB processing time, the FPGA execution time and the time required for the data exchange between the host PC and the FPGA board and is given by the equation

where

is total execution time of the MATLAB/Simulink model,

is the MATLAB processing time,

is the time required for transferring data from MATLAB to FPGA platform,

is the FPGA processing time, and

is the time required for copying data from FPGA platform to the MATLAB/Simulink environment.

Assuming population size

N and number of iterations

M, the total execution time (

) of the proposed FPGA BB–BC circuit is given by the equation

where

are the latencies of the FPGA BB–BC stages, i.e., candidate generation, fitness function calculation, and center of mass calculation, respectively and

is the latency of FPGA PID controller and the plant.

Figure 9 shows the top-level diagram of our MATLAB/Simulink model, which includes the FPGA BB–BC/PID module (using the FIL concept), the HVAC module, an analog-to-digital converter to feed the digital error value into the FPGA BB–BC module, an digital-to-analog converter to provide the PID controller output to the HVAC model, an adder to calculate the error and the set point.

6. Conclusions

In this paper, we presented a novel technique for the fast tuning of the parameters of the PID controller of a second-order heat, ventilation, and air conditioning (HVAC) system using a low-cost, fast-convergent optimization algorithm, called Big Bang–Big Crunch (BB–BC). To further accelerate the optimization process, we proposed the implementation of both the BB–BC algorithm and the PID controller using FPGA technology. In order to emulate and evaluate the entire system we adopted the FPGA-in-the-loop (FIL) technique, according to which, the plant (i.e., MATLAB/Simulink model of HVAC) is connected to the FPGA board (i.e., the PID and BB–BC modules). To demonstrate the efficiency of the proposed approach, we run an extensive set of experiments in a second-order HVAC model using different optimization methods (BB–BC in FPGA, BB–BC in sw, GA, and PSO in sw). The experimental results proved the benefits of the proposed approach against the other methods in terms of convergence speed and computation time.