4.2. Result and Discusion

First, we compare the NBTI and leakage reduction results of different IVC methods. We define

Pleak and

Pdyn as the average leakage power and average dynamic power during the overall lifetime of the circuit, respectively. In the first step, three kinds of ILP formulations are constructed and their corresponding optimal input vectors are found. Then, the corresponding delay degradation Δ

D and leakage power

Pleak for these input vectors in ten years is calculated, and the result is shown in

Table 4.

The delay degradation Δ

D that corresponds to the input vector obtained by the IVC

#1, IVC

#2, and IVC

#3 methods is shown in column two to four, respectively. The corresponding leakage power

Pleak of these three IVC methods is shown in column five to seven, respectively. From

Table 4, we can obtain the following conclusions: first, IVC

#1 and IVC

#2 can find the optimal Δ

D or

Pleak minimization result, respectively. However, because only one issue is considered in generating the co-optimization ILP formulation, the reduction result for the other issue is not satisfactory. The proposed ILP formulation considers both effects, and can reduce Δ

D and

Pleak at the same time. For instance, compared with IVC

#1, our proposed IVC #3 method can achieve a 13.15% improvement in

Pleak reduction at the cost of a 0.69% Δ

D increase on average. On the other hand, compared with IVC

#2, our proposed method can decrease Δ

D by 8.32% on average, at the cost of a 2.01% increase in leakage power.

As shown in

Table 4, the results of the three ILP formulations are different tradeoffs between NBTI and leakage. In the following section, we combine these different IVC methods with the supply voltage assignment, which is a subsequent method after the input vector is determined. In most modern systems, the devices will periodically switch between the active and standby mode, and the circuit’s delay degradation is dependent on the ratio between the active and standby modes (

RAS) according to Equations (1)–(6). In some industrial applications, the circuit works under a predefined routine, and the

RAS is a fixed value during its lifetime. However, the

RAS value in some other applications will change randomly. In order to simplify the experimental setting, we assume that the

RAS is fixed, and analyze the NBTI and power reduction results of the combination method when

RAS is set to different values. In our future work, we will further analyze the results of our proposed method when the

RAS changes randomly.

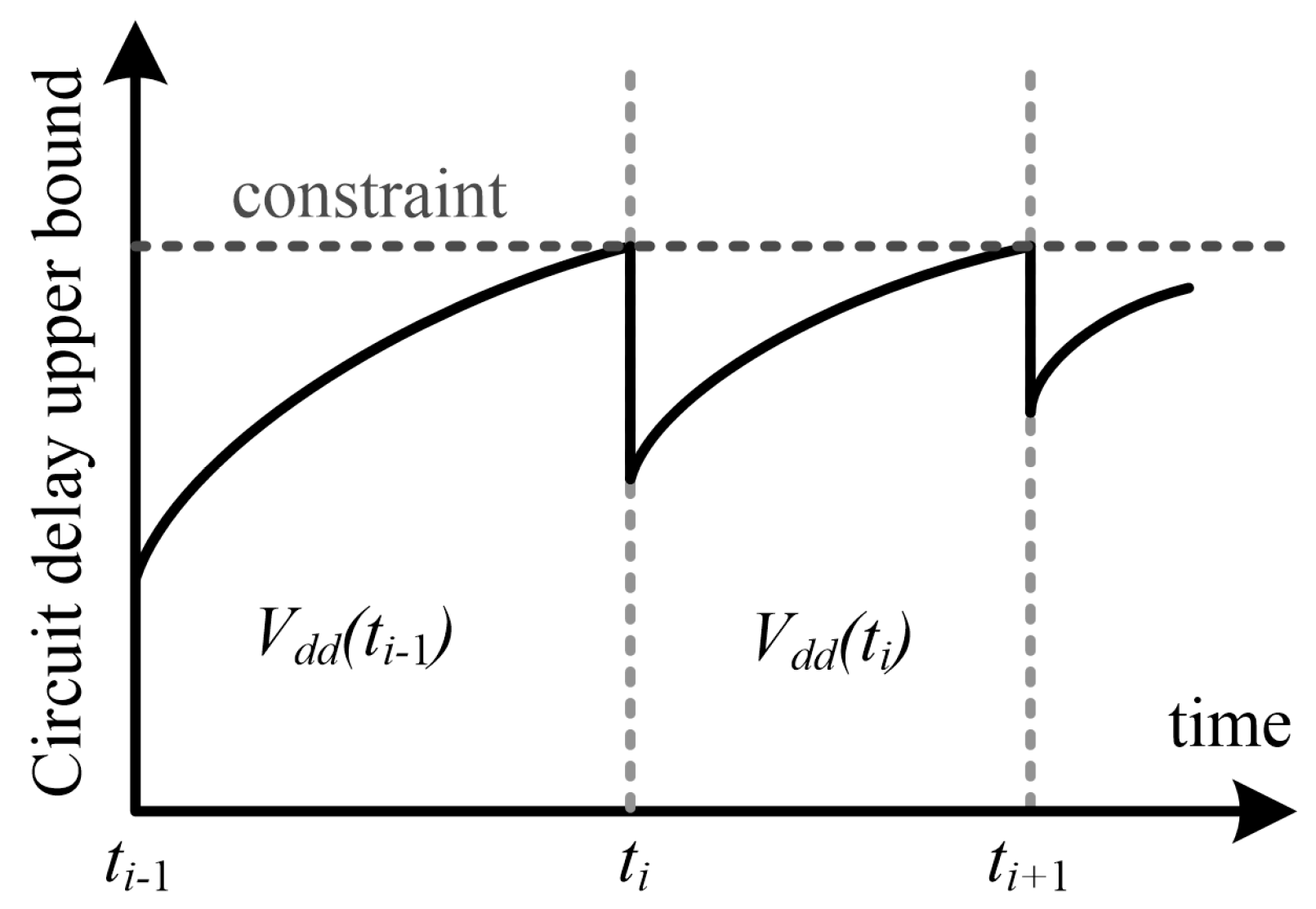

First, we use three kinds of ILP formulation IVC #1, IVC #2, and IVC #3 to determine the input vector that satisfies the NBTI minimization, leakage minimization, and co-optimization requirements, respectively. Then, the input vector is used in standby mode and the ratio between the active mode and the standby mode is assumed to be 0.1. Afterwards, an SVA method that uses the input vector obtained by IVC #1, IVC #2, and IVC #3, respectively, is applied to compensate for the NBTI-induced performance degradation. The

Vdd update cycle for the SVA method is five days, and the resolution for

Vdd adjustment is 20 mV. The above process is repeated until the end of the circuit’s lifetime. Then, the average leakage and dynamic power of the circuit in ten years is calculated. The results are shown in

Table 5.

In

Table 5, the

Pleak of SVA combined with IVC #1, IVC #2, and IVC #3 is shown in column two, four, and six, respectively. The

Pdyn of SVA combined with these three IVC methods is shown in column three, five, and seven, respectively.

Table 5 illustrates that, first, the

Pdyn of the SVA + IVC #1 method is the lowest because its aging rate is less severe than that for the SVA + IVC #2 and SVA + IVC #3 methods, and the

Vdd increase is the slowest. However, for most circuits, the

Pleak of SVA is the highest when the input vector found by IVC #1 is used. This is because the

Pleak that corresponds to the input vector obtained by IVC #1 is far higher than that corresponding to the other two ILP formulations when the circuit is in the initial state. Although the leakage power increase is the slowest for SVA + IVC #1, its total leakage power is still the highest at the end of the lifetime. Second, the

Pdyn of SVA + IVC #2 is the highest because its corresponding input vector will bring in the most severe NBTI-induced aging, and in turn the frequency of

Vdd adjustment is the highest. Third, our proposed co-optimization ILP formulation has considered both NBTI and leakage, and it can find the input vectors that help SVA save 13.82% and 2.49% more leakage power on average than IVC #1 and IVC #2, respectively. In addition, because the NBTI-induced delay degradation that corresponds to our proposed ILP formulation is near optimal, its corresponding

Pdyn is close to the

Pdyn of SVA + IVC #1 and is lower than the

Pdyn when the input vector found by IVC #2 is used. Fourth, different from dynamic power, the analysis for the

Pleak of the SVA method is a complex process when using different input vectors. For instance, in the c432 circuit, the input vector obtained by IVC #2 can help SVA save more leakage power than the input vector found by IVC #1. In contrast, the situation is the opposite for c7552 circuit.

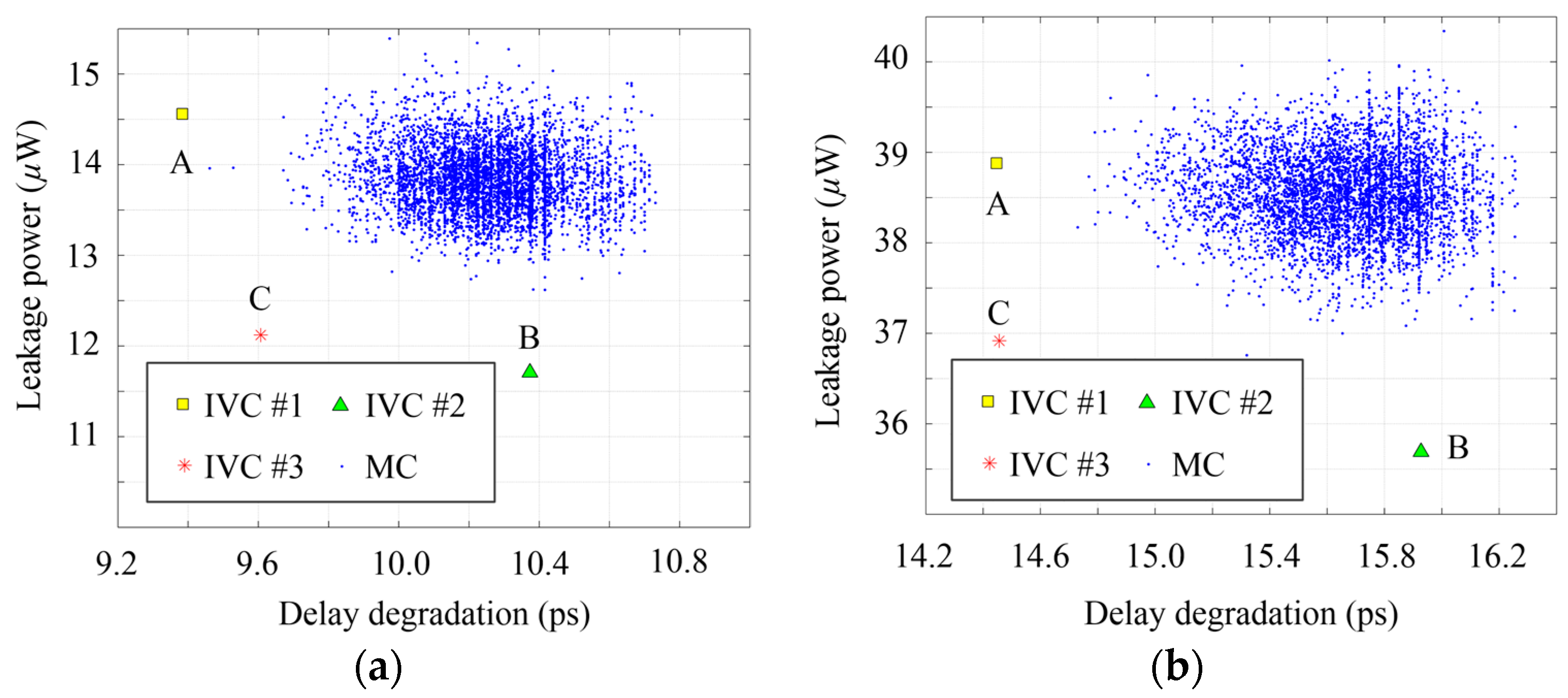

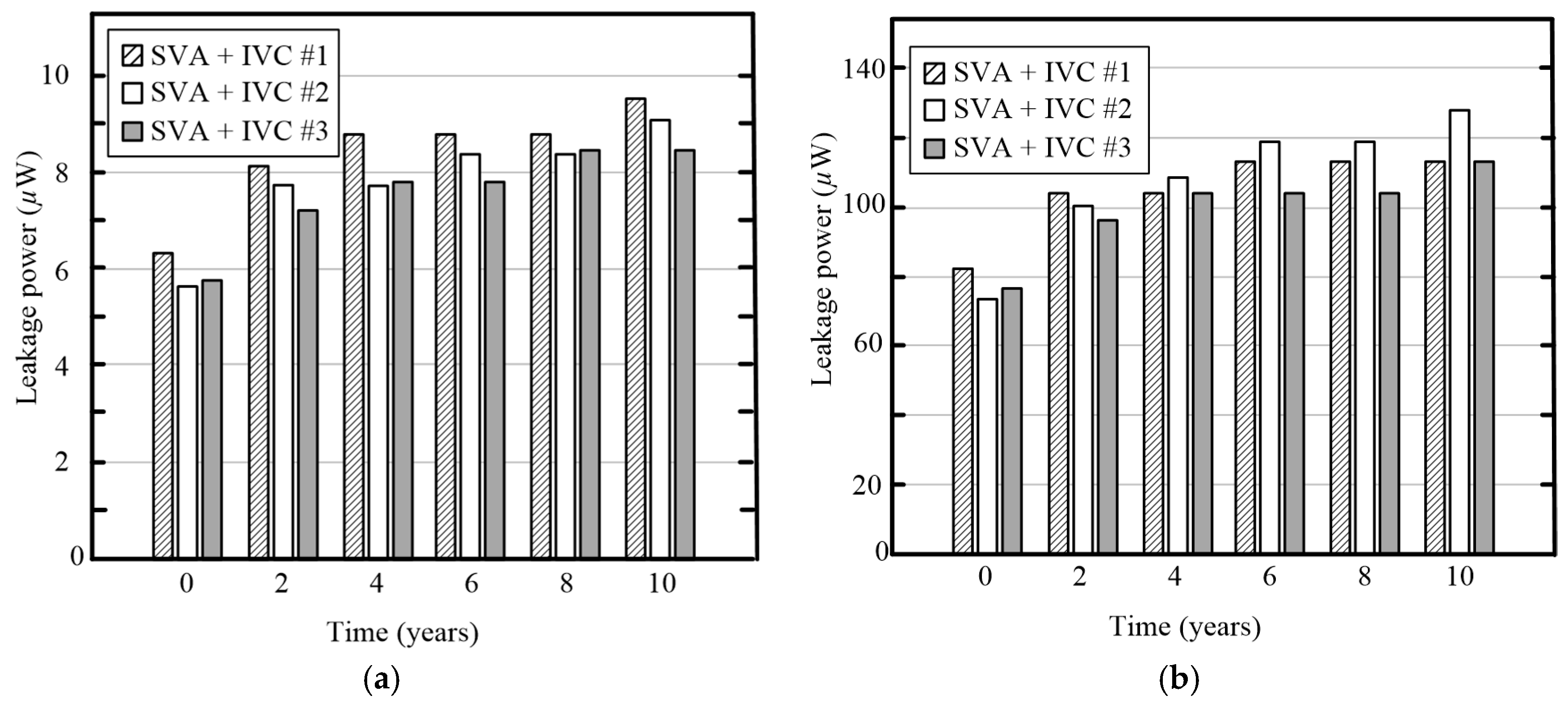

Figure 7 illustrates the change of the leakage power for the c432 and c7552 circuits at each 2-year time interval during the lifetime.

The histograms in

Figure 7 show that, for both circuits, the

Pleak of SVA + IVC #2 and SVA + IVC #3 increase faster than that of SVA + IVC #1. However, for the c432 circuit, the leakage power in standby mode that corresponds to IVC #1 is much higher than that corresponding to the other two ILP formulations at the starting time (0 year), which makes it still the highest after some iterations of

Vdd adjustment. Therefore, the

Pleak of SVA + IVC #1 is higher than that of SVA combined with IVC #2 and IVC #3, as shown in

Table 5. In contrast, although the initial leakage power that corresponds to the input vector found by IVC #2 is also the lowest for the c7552 circuit, the

Pleak of SVA

+ IVC #2 is the highest for the c7552 circuit. The reason for this phenomenon is that the frequency of

Vdd adjustment for SVA

+ IVC #2 is much faster than for SVA

+ IVC #1 and IVC #3 because of the severe delay degradation in standby mode, and makes its corresponding leakage power also increase fast as shown in

Figure 7b. Finally, we can see that the input vector obtained by our proposed co-optimization ILP formulation can provide a balanced tradeoff between NBTI and leakage, so that both specifications are near optimal, and it can help the SVA save more leakage power than the ILP formulation for a single effect.

Moreover, we have analyzed the power dissipation of the SVA method when

RAS is 0.01 and 1.0, and the results are shown in

Table 6 and

Table 7, respectively.

Table 5,

Table 6 and

Table 7 show that the power reduction result of the SVA method is dependent on both the input vector in standby mode and the

RAS value. First, compared with the SVA + IVC #1 method, our proposed SVA + IVC #3 method can save more leakage power, at the cost of a small increase of dynamic power. Second, when

RAS decreases, the advantage of our proposed SVA + IVC #3 method over the SVA + IVC #2 method on power reduction becomes high. For example, when

RAS is 0.01, the SVA + IVC #3 method can save 4.28% more leakage power on average than that of SVA + IVC #2. However, when the

RAS is 1.0, our proposed method can only save 0.03% more leakage power. The reason for this phenomenon is that when the

RAS is small, the ratio of standby mode in the whole lifetime becomes high; the advantage of the input vector found by IVC #1 and IVC #3 on NBTI mitigation becomes more distinct over the input vector obtained by IVC #2. Therefore, the frequency of

Vdd adjustment for the SVA method when using the input vector found by IVC #3 is much slower than that of IVC #2, which in turn helps the SVA + IVC #3 method save more leakage and dynamic power than that of the SVA + IVC #2 method.

In Ref. [

27], Firouzi et al. have proposed a kind of co-optimization method for NBTI and leakage reduction. This co-optimization ILP formulation is named IVC #4 in the following section. Their method constructed an ILP formulation to find the minimum NBTI-induced delay degradation with different power constraints. In this paper, we also use IVC #4 to find the input vector and analyze the power reduction result of the SVA method when using these input vectors. First, the ILP formulation for leakage minimization and the modified version of ILP formulation for leakage maximization are generated as per the design flow in Ref. [

27]. Then, we find the potential best and worst leakage power for the circuit by solving these formulations. Second, a set of power constrains can be built with 10% steps of the leakage power compared to the potential minimum value. With each constrain, an ILP formulation for NBTI mitigation is generated, and the result of these ILP formulations are input vectors, which can obtain the minimum NBTI-induced aging and satisfy the leakage power constrain. Finally, we use each of these ten input vectors in standby mode and apply an SVA to compensate for the performance aging. At the end of the circuit’s lifetime, we calculate the average leakage and dynamic power of an SVA when using each input vector. Suppose

Pleak,i and

Pdyn,i is the leakage and dynamic power of an SVA corresponding to input vector

i.

Pleak,min and

Pdyn,min is the potential minimum leakage and dynamic power for all of the ten input vectors. Then we define

Ei =

Pleak,i/

Pleak,min +

Pdyn,i/

Pdyn,min for each input vector

i, and the minimum

Ei is considered as the optimal result on power reduction for each circuit when using IVC #4. The leakage and dynamic power of the SVA method when using the input vector found by IVC #4 and our proposed IVC #3 method is shown in

Table 8.

From

Table 8, we can see that compared with the IVC #4 method, our proposed method can save more leakage power dissipation during a circuit’s lifetime, at the cost of a slight increase in dynamic power. Moreover, the design procedure of our proposed method is much simpler than that in Ref. [

27], which demonstrates the advantage of our method.

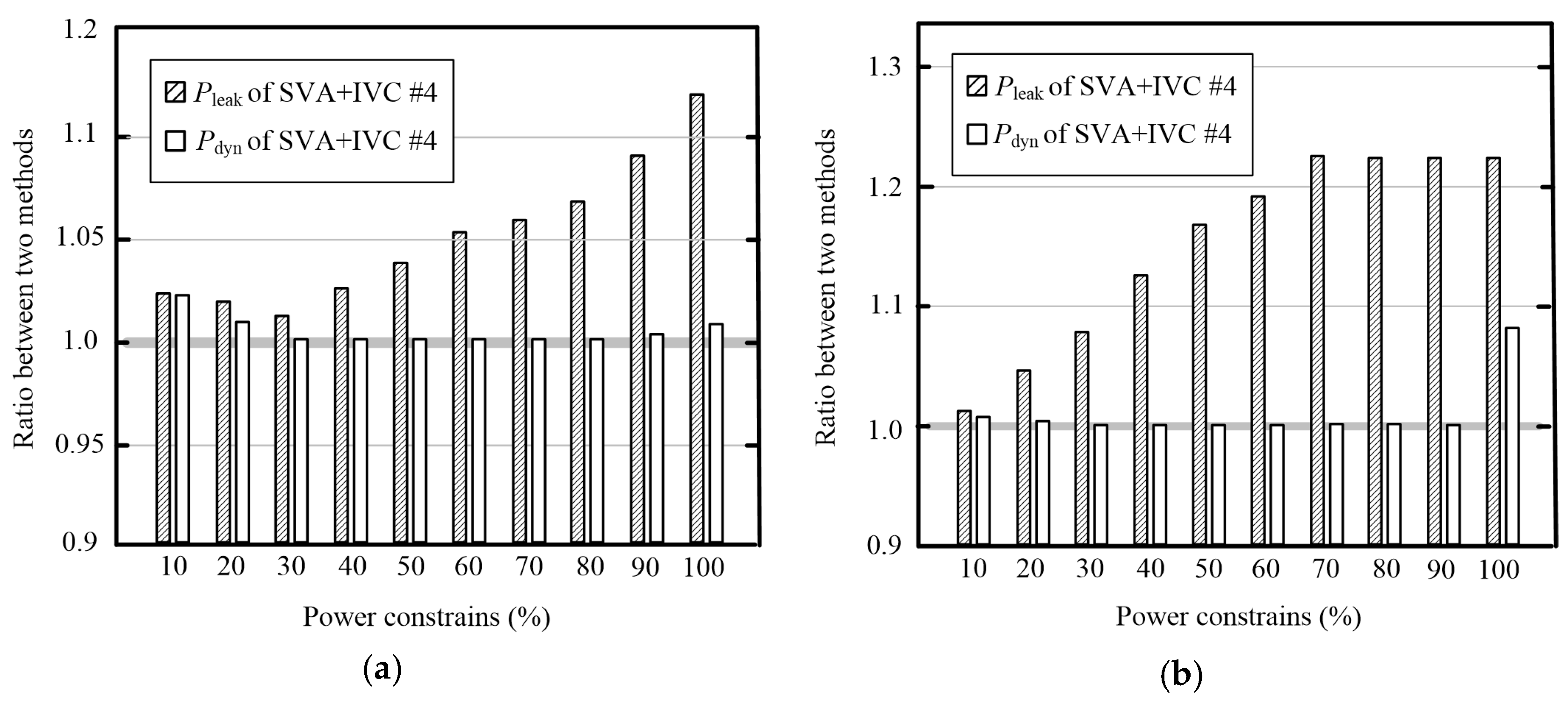

In addition, we implement a simulation on c880 and c3540 circuits to investigate the leakage and dynamic power change of the SVA method when using the input vector obtained by IVC #4 under different power constrains in detail. In order to observe the change more precisely, the leakage and dynamic power results of SVA + IVC #4 are normalized to the power results obtained by the proposed SVA + IVC #3 method. The results are shown in

Figure 8.

In

Figure 8, the x-axis represents the different power constrains for the ILP formulation in Ref. [

27], and the y-axis is the ratio of

Pdyn and

Pleak between the SVA + IVC #3 method and the SVA + IVC #4 method.

Figure 8 shows that, for the different circuits, the co-optimization ILP formulations with different power constrains can obtain the optimal leakage and dynamic power reduction result. For example, the power reduction result is optimal for an c880 circuit when the constrain is 30%. However, for the c3540 circuit, the optimal result can be obtained when the constrain is set to 10%. Therefore, it is inconvenient to find the best parameter for the co-optimization ILP formulation in Ref. [

27]. In comparison, our proposed ILP formulation can obtain the only optimal input vector that can help the SVA method save power dissipation conveniently.

Finally, we implement a 5000 times Monte Carlo simulation to find input vectors for the circuit. We calculate the

Pleak and

Pdyn of the SVA in ten years when these randomly selected input vectors are used in standby mode. The simulation setting is the same as the above section. We compare the power dissipation of SVA + MC with our proposed SVA + IVC #3 method. The result is shown in

Table 9.

Table 9 shows that the proposed IVC #3 method can find the optimal input vector and help the SVA save more leakage power than the input vector obtained by MC simulation. Since the dynamic power is strongly dependent on the circuit’s supply voltage in the active mode, the impact of NBTI-induced

Vdd change on power dissipation is great. As shown in

Figure 6, the result of NBTI mitigation by MC simulation is close or even better than the result by the proposed IVC #3 method, so the best result of the dynamic power for SVA + MC is close to the dynamic power of the SVA + IVC #3 method. Finally, the

Pdyn and

Pleak of the SVA method for the c880 and c3540 circuits when using the input vector obtained by MC and the three IVC methods are illustrated in

Figure 9, respectively.

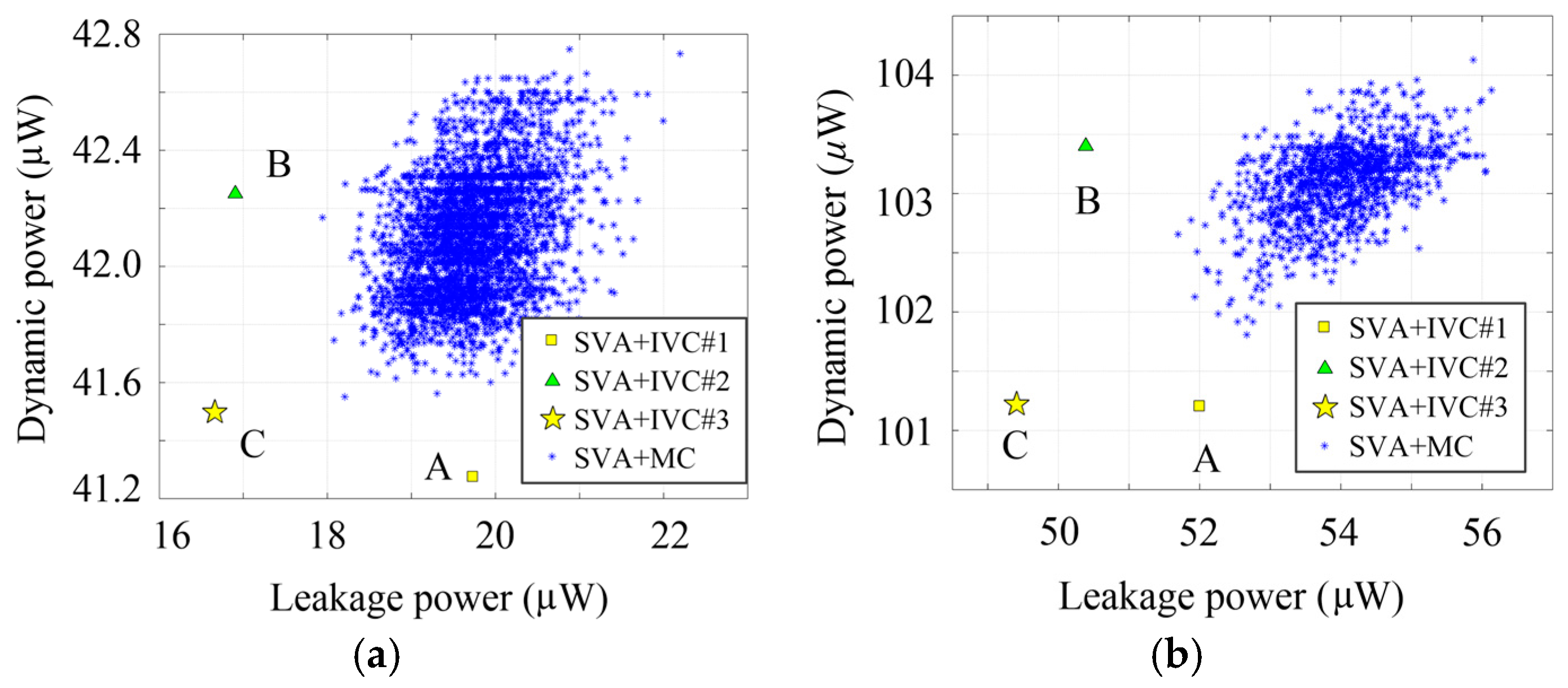

In

Figure 9, the x-axis and y-axis represent the leakage and dynamic power of the SVA method, respectively. Point A (the rectangular point) and B (the triangle point) correspond to the result of SVA + IVC #1 and SVA + IVC #2, respectively. Point C (the star point) represents the result of our proposed SVA + IVC #3 method. The small asterisk point represents the leakage and dynamic power of the SVA method using the input vector obtained by MC simulations. The iteration number for MC simulation is 100,000. From

Figure 9, we can get the following conclusions: first, the dynamic power of SVA when using the input vector obtained by IVC #1 is the lowest, because the ILP formulation for NBTI reduction can find the minimum degradation vector (MDV), and the frequency of V

dd adjustment for SVA + IVC #1 is the slowest. However, because the initial leakage power that corresponds to IVC #1 is the highest, the total leakage power dissipation for SVA + IVC #1 is the highest among the three ILP formulations. Second, although the leakage power dissipation for SVA + IVC #2 is low, its dynamic power is relatively high because of the high

Vdd adjustment frequency. Finally, the

Pdyn and

Pleak of our proposed SVA + IVC #3 method are all near the optimal result, which demonstrates its advantage over MC simulation and ILP formulations for a single effect.