Exploring Light Stability and Trapping Mechanisms in Organic Thin-Film Transistors for High-Brightness MicroLED Integration

Highlights

Abstract

1. Introduction

2. Experiment and Fabrication Process

2.1. Monolithic MicroLED Integration

2.2. Organic TFTs’ Process and Fabrication

2.3. Methods and Test Equipment

3. Results and Discussion

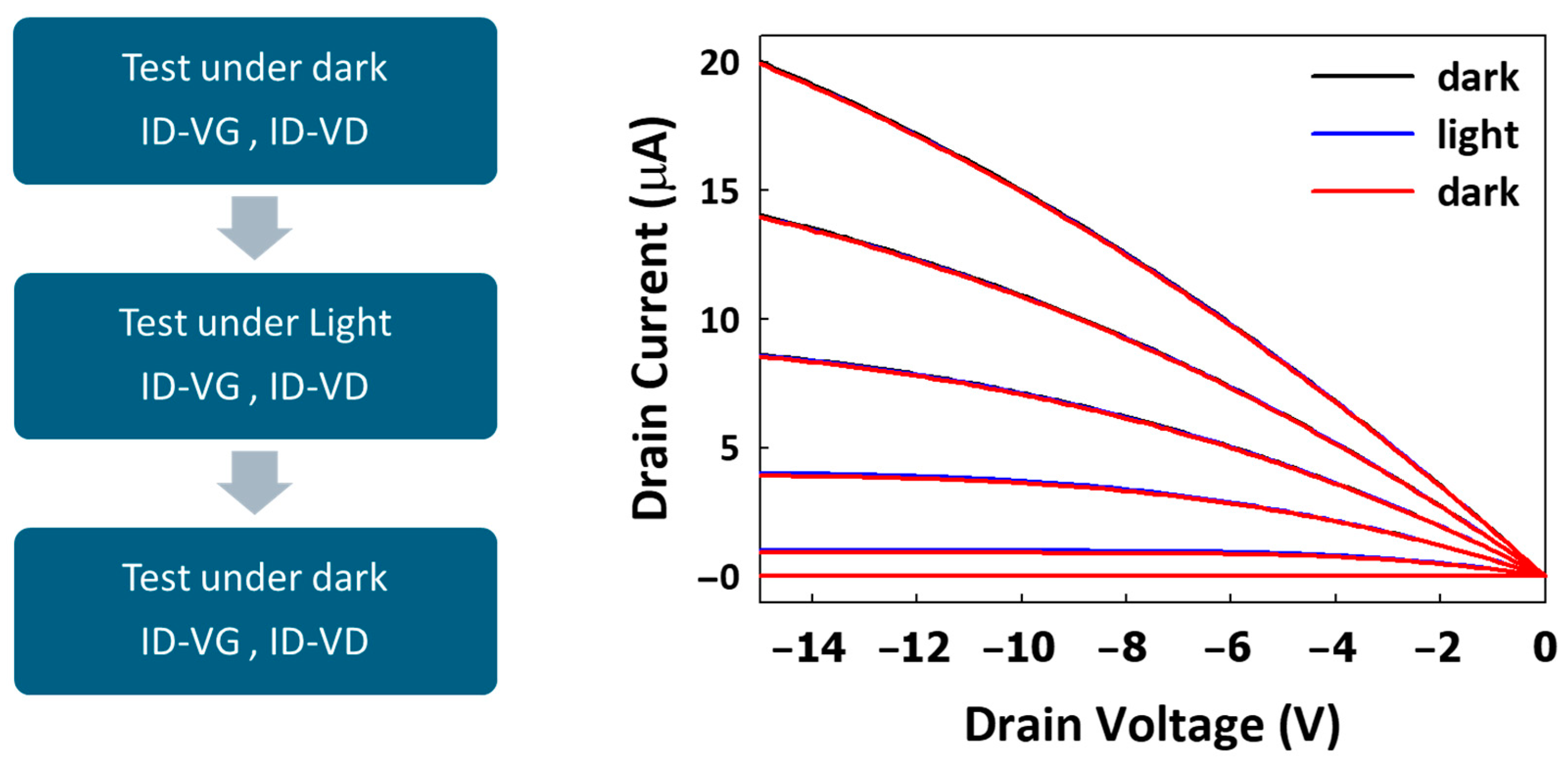

3.1. Experiment Flow and OTFTs’ Device Characteristics

3.2. Discussion of Photo-Induced Charge-Trapping Mechanism

- Shallow traps (1): These are energy states located close to the conduction or valence band edges, leading to minor Vth shifts as these charges are easily captured and released.

- Deep traps (2): These are energy states situated deeper within the bandgap, causing more significant Vth shifts, as these charges are more likely to remain trapped for longer periods.

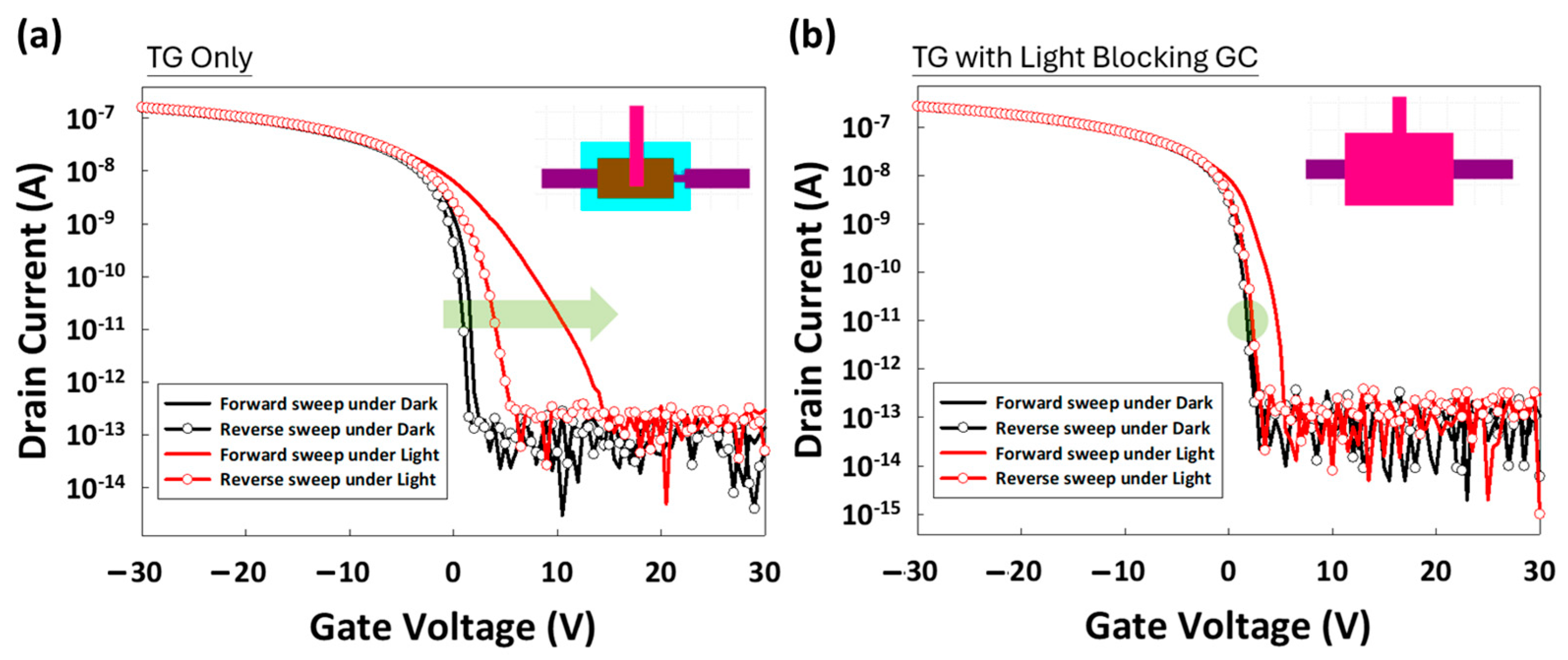

3.3. Optimization of TFT Design to Suppress Light-Induced Degradation

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

Correction Statement

References

- Zheng, Y.-Z.; Chen, Y.-A.; Chen, P.-H.; Chang, T.-C.; Hung, Y.-H.; Zhou, K.-J.; Tu, Y.-F.; Wang, Y.-X.; Chen, J.-J.; Wu, C.-C.; et al. Physical Mechanism of the Mechanical Bending of High-Performance Organic TFTs and the Effect of Atmospheric Factors. ACS Appl. Electron. Mater. 2022, 4, 3000–3009. [Google Scholar] [CrossRef]

- Chen, F.-C.; Chen, T.-D.; Zeng, B.-R.; Chung, Y.-W. Influence of mechanical strain on the electrical properties of flexible organic thin-film transistors. Semicond. Sci. Technol. 2011, 26, 034005. [Google Scholar] [CrossRef]

- Minamiki, T.; Minami, T.; Chen, Y.-P.; Mano, T.; Takeda, Y.; Fukuda, K.; Tokito, S. Flexible organic thin-film transistor immunosensor printed on a one-micron-thick film. Commun. Mater. 2021, 2, 8. [Google Scholar] [CrossRef]

- Song, J.; Liu, H.; Zhao, Z.; Lin, P.; Yan, F. Flexible Organic Transistors for Biosensing: Devices and Applications. Adv. Mater. 2024, 36, 2300034. [Google Scholar] [CrossRef]

- Ma, L.-Y.; Soin, N.; Aidit, S.N.; Md Rezali, F.A.; Wan Muhamad Hatta, S.F. Recent advances in flexible solution-processed thin-film transistors for wearable electronics. Mater. Sci. Semicond. Process. 2023, 165, 107658. [Google Scholar] [CrossRef]

- Tu, Y.F.; Huang, J.W.; Chang, T.C.; Hung, Y.H.; Lu, I.N.; Zhou, K.J.; Sun, L.C.; Chen, Y.A.; Wu, C.C.; Hung, W.C.; et al. Asymmetric Electrode Structure Induces Dual-Channel Phenomenon Under Hot-Carrier Stress in Organic Thin-Film Transistors. IEEE Electron Device Lett. 2023, 44, 1496–1499. [Google Scholar] [CrossRef]

- Han, L.; Ogier, S.; Li, J.; Sharkey, D.; Yin, X.; Baker, A.; Carreras, A.; Chang, F.; Cheng, K.; Guo, X. Wafer-scale organic-on-III-V monolithic heterogeneous integration for active-matrix micro-LED displays. Nat. Commun. 2023, 14, 6985. [Google Scholar] [CrossRef]

- Lee, T.-Y.; Chen, L.-Y.; Lo, Y.-Y.; Swayamprabha, S.S.; Kumar, A.; Huang, Y.-M.; Chen, S.-C.; Zan, H.-W.; Chen, F.-C.; Horng, R.-H.; et al. Technology and Applications of Micro-LEDs: Their Characteristics, Fabrication, Advancement, and Challenges. ACS Photonics 2022, 9, 2905–2930. [Google Scholar] [CrossRef]

- Lee, T.-Y.; Huang, Y.-M.; Chiang, H.; Chao, C.-L.; Hung, C.-Y.; Kuo, W.-H.; Fang, Y.-H.; Chu, M.-T.; Wu, C.-I.; Lin, C.-c.; et al. Increase in the efficiency of III-nitride micro LEDs by atomic layer deposition. Opt. Express 2022, 30, 18552–18561. [Google Scholar] [CrossRef]

- Miao, W.-C.; Hsiao, F.-H.; Sheng, Y.; Lee, T.-Y.; Hong, Y.-H.; Tsai, C.-W.; Chen, H.-L.; Liu, Z.; Lin, C.-L.; Chung, R.-J.; et al. Microdisplays: Mini-LED, Micro-OLED, and Micro-LED. Adv. Opt. Mater. 2024, 12, 2300112. [Google Scholar] [CrossRef]

- Wu, T.; Sher, C.-W.; Lin, Y.; Lee, C.-F.; Liang, S.; Lu, Y.; Huang Chen, S.-W.; Guo, W.; Kuo, H.-C.; Chen, Z. Mini-LED and Micro-LED: Promising Candidates for the Next Generation Display Technology. Appl. Sci. 2018, 8, 1557. [Google Scholar] [CrossRef]

- Hung, Y.H.; Chang, T.C.; Zheng, Y.Z.; Su, W.C.; Tu, Y.F.; Chen, J.J.; Kuo, C.W.; Lu, I.N.; Chen, Y.A.; Tsai, C.H.; et al. Investigation of Thermal Behavior on High-Performance Organic TFTs Using Phase Separated Organic Semiconductors. IEEE Electron Device Lett. 2021, 42, 859–862. [Google Scholar] [CrossRef]

- Hung, Y.H.; Chang, T.C.; Tu, Y.F.; Lu, I.N.; Zheng, Y.Z.; Chiang, C.L.; Chen, J.J.; Kuo, C.W.; Sun, L.C.; Zhou, K.J. Improving Drain-Induced Barrier Lowering Effect and Hot Carrier Reliability With Terminal via Structure on Half-Corbino Organic Thin-Film Transistors. IEEE Electron Device Lett. 2022, 43, 569–572. [Google Scholar] [CrossRef]

- Yin, X.; Li, J.; Han, L.; Tang, W.; Huang, Y.; Ogier, S.; Liu, Z.; Su, Y.; Guo, X. Three-Dimensional Integration of Switching and Light-Sensitive Organic Transistors in Solution Processes for Flexible High-Resolution Active-Matrix Optical Imager. IEEE Electron Device Lett. 2023, 44, 1504–1507. [Google Scholar] [CrossRef]

- Jiang, S.; Yang, L.; Huang, C.; Chen, Q.; Zeng, W.; She, X. Understanding Illumination Effect on Saturation Behavior of Thin Film Transistor. Photonics 2023, 10, 309. [Google Scholar] [CrossRef]

- Za’aba, N.K.; Taylor, D.M. Photo-induced effects in organic thin film transistors based on dinaphtho [2,3-b:2′,3′-f] Thieno[3,2-b′] thiophene (DNTT). Org. Electron. 2019, 65, 39–48. [Google Scholar] [CrossRef]

- Chen, Q.; Sanchez, J.E.; Lin, D.; Lei, Y.; Zhu, G. Analytical model for donor like Gaussian traps in organic thin-film transistor. Org. Electron. 2022, 103, 106464. [Google Scholar] [CrossRef]

- Janasz, L.; Borkowski, M.; Blom, P.W.M.; Marszalek, T.; Pisula, W. Organic Semiconductor/Insulator Blends for Elastic Field-Effect Transistors and Sensors. Adv. Funct. Mater. 2022, 32, 2105456. [Google Scholar] [CrossRef]

- Smith, J.; Zhang, W.; Sougrat, R.; Zhao, K.; Li, R.; Cha, D.; Amassian, A.; Heeney, M.; McCulloch, I.; Anthopoulos, T.D. Solution-Processed Small Molecule-Polymer Blend Organic Thin-Film Transistors with Hole Mobility Greater than 5 cm2/Vs. Adv. Mater. 2012, 24, 2441–2446. [Google Scholar] [CrossRef]

- McCall, K.L.; Rutter, S.R.; Bone, E.L.; Forrest, N.D.; Bissett, J.S.; Jones, J.D.E.; Simms, M.J.; Page, A.J.; Fisher, R.; Brown, B.A.; et al. High Performance Organic Transistors Using Small Molecule Semiconductors and High Permittivity Semiconducting Polymers. Adv. Funct. Mater. 2014, 24, 3067–3074. [Google Scholar] [CrossRef]

- Chuang, C.-S.; Chen, F.-C.; Shieh, H.-P.D. Organic thin-film transistors with reduced photosensitivity. Org. Electron. 2007, 8, 767–772. [Google Scholar] [CrossRef]

- Chuang, C.-S.; Tsai, S.-T.; Lin, Y.-S.; Chen, F.-C.; Shieh, H.-P.D. Photocurrent Suppression of Transparent Organic Thin Film Transistors. Jpn. J. Appl. Phys. 2007, 46, L1197. [Google Scholar] [CrossRef]

- Lin, P.; Yan, F. Organic Thin-Film Transistors for Chemical and Biological Sensing. Adv. Mater. 2012, 24, 34–51. [Google Scholar] [CrossRef] [PubMed]

- Zhuang, X.; Huang, W.; Han, S.; Jiang, Y.; Zheng, H.; Yu, J. Interfacial modifying layer-driven high-performance organic thin-film transistors and their nitrogen dioxide gas sensors. Org. Electron. 2017, 49, 334–339. [Google Scholar] [CrossRef]

- Rapisarda, M.; Fortunato, G.; Valletta, A.; Jacob, S.; Benwadih, M.; Coppard, R.; Chartier, I.; Mariucci, L. Self-heating effects on the electrical instability of fully printed p-type organic thin film transistors. Appl. Phys. Lett. 2012, 101, 233304. [Google Scholar] [CrossRef]

- Hung, W.C.; Lin, J.H.; Chang, T.C.; Zheng, Y.Z.; Hung, Y.H.; Chen, Y.A.; Wang, L.W.; Tsai, C.H.; Ogier, S. Improving Hot Carrier Reliability of Organic-TFTs by Extended Electrode. IEEE Electron Device Lett. 2023, 44, 626–629. [Google Scholar] [CrossRef]

- Chen, Y.A.; Zheng, Y.Z.; Chang, T.C.; Zhou, K.J.; Sun, P.J.; Hung, Y.H.; Lee, Y.H.; Tsai, T.M.; Chen, J.W.; Kuo, C.W.; et al. Investigation of the Self-Heating Effect in High Performance Organic TFTs with Multi-Finger Structure. IEEE Electron Device Lett. 2022, 43, 1243–1246. [Google Scholar] [CrossRef]

- Chen, H.C.; Zhou, K.J.; Chen, P.H.; Chen, G.F.; Huang, S.P.; Chen, J.J.; Kuo, C.W.; Tsao, Y.C.; Tai, M.C.; Chu, A.K.; et al. Abnormal Unsaturated Output Characteristics In a-InGaZnO TFTs with Light Shielding Layer. IEEE Electron Device Lett. 2019, 40, 1281–1284. [Google Scholar] [CrossRef]

- Chen, H.C.; Chen, G.F.; Huang, S.P.; Chang, T.C.; Chen, P.H.; Chen, J.J.; Kuo, C.W.; Zhou, K.J.; Hung, Y.H.; Tsao, Y.C.; et al. Formation of Hump Effect Due to Top-Gate Bias Stress in Organic Thin-Film Transistors. IEEE Electron Device Lett. 2019, 40, 1941–1944. [Google Scholar] [CrossRef]

- Kimura, M.; Kamada, Y.; Fujita, S.; Hiramatsu, T.; Matsuda, T.; Furuta, M.; Hirao, T. Mechanism analysis of photoleakage current in ZnO thin-film transistors using device simulation. Appl. Phys. Lett. 2010, 97, 075108. [Google Scholar] [CrossRef]

- Park, J.H.; Lee, H.S.; Park, S.; Min, S.-W.; Yi, Y.; Cho, C.-G.; Han, J.; Kim, T.W.; Im, S. Photo-Stable Organic Thin-Film Transistor Utilizing a New Indolocarbazole Derivative for Image Pixel and Logic Applications. Adv. Funct. Mater. 2014, 24, 1109–1116. [Google Scholar] [CrossRef]

- Aerts, W.F.; Verlaak, S.; Heremans, P. Design of an organic pixel addressing circuit for an active-matrix OLED display. IEEE Trans. Electron Devices 2002, 49, 2124–2130. [Google Scholar] [CrossRef]

- Xu, X.; Huang, B.; Fan, J.; Zhao, J.; Guo, X. Employing Drain-Bias Dependent Electrical Characteristics of Poly-Si TFTs to Improve Gray Level Control in Low Power AMOLED Displays. IEEE J. Electron Devices Soc. 2019, 7, 489–494. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Tsai, C.-H.; Wu, Y.-E.; Kuo, C.-W.; Chang, T.-C.; Chen, L.-Y.; Chen, F.-C.; Kuo, H.-C. Exploring Light Stability and Trapping Mechanisms in Organic Thin-Film Transistors for High-Brightness MicroLED Integration. Materials 2024, 17, 5643. https://doi.org/10.3390/ma17225643

Tsai C-H, Wu Y-E, Kuo C-W, Chang T-C, Chen L-Y, Chen F-C, Kuo H-C. Exploring Light Stability and Trapping Mechanisms in Organic Thin-Film Transistors for High-Brightness MicroLED Integration. Materials. 2024; 17(22):5643. https://doi.org/10.3390/ma17225643

Chicago/Turabian StyleTsai, Chia-Hung, Yang-En Wu, Chuan-Wei Kuo, Ting-Chang Chang, Li-Yin Chen, Fang-Chung Chen, and Hao-Chung Kuo. 2024. "Exploring Light Stability and Trapping Mechanisms in Organic Thin-Film Transistors for High-Brightness MicroLED Integration" Materials 17, no. 22: 5643. https://doi.org/10.3390/ma17225643

APA StyleTsai, C.-H., Wu, Y.-E., Kuo, C.-W., Chang, T.-C., Chen, L.-Y., Chen, F.-C., & Kuo, H.-C. (2024). Exploring Light Stability and Trapping Mechanisms in Organic Thin-Film Transistors for High-Brightness MicroLED Integration. Materials, 17(22), 5643. https://doi.org/10.3390/ma17225643