Conformally Gated Surface Conducting Behaviors of Single-Walled Carbon Nanotube Thin-Film-Transistors

Abstract

1. Introduction

2. Materials and Methods

2.1. Preparation of High Purity s-SWCNT Solution

2.2. Preparation of Gate Dielectric Solutions (CYTOP and Ion-Gel)

2.3. Fabrication of s-SWCNT FETs on Al2O3 Gate Dielectric

2.4. Fabrication of a Side Gate High-Purity SWCNT FETs Using Ion-Gel Gate Dielectric

2.5. Characterization

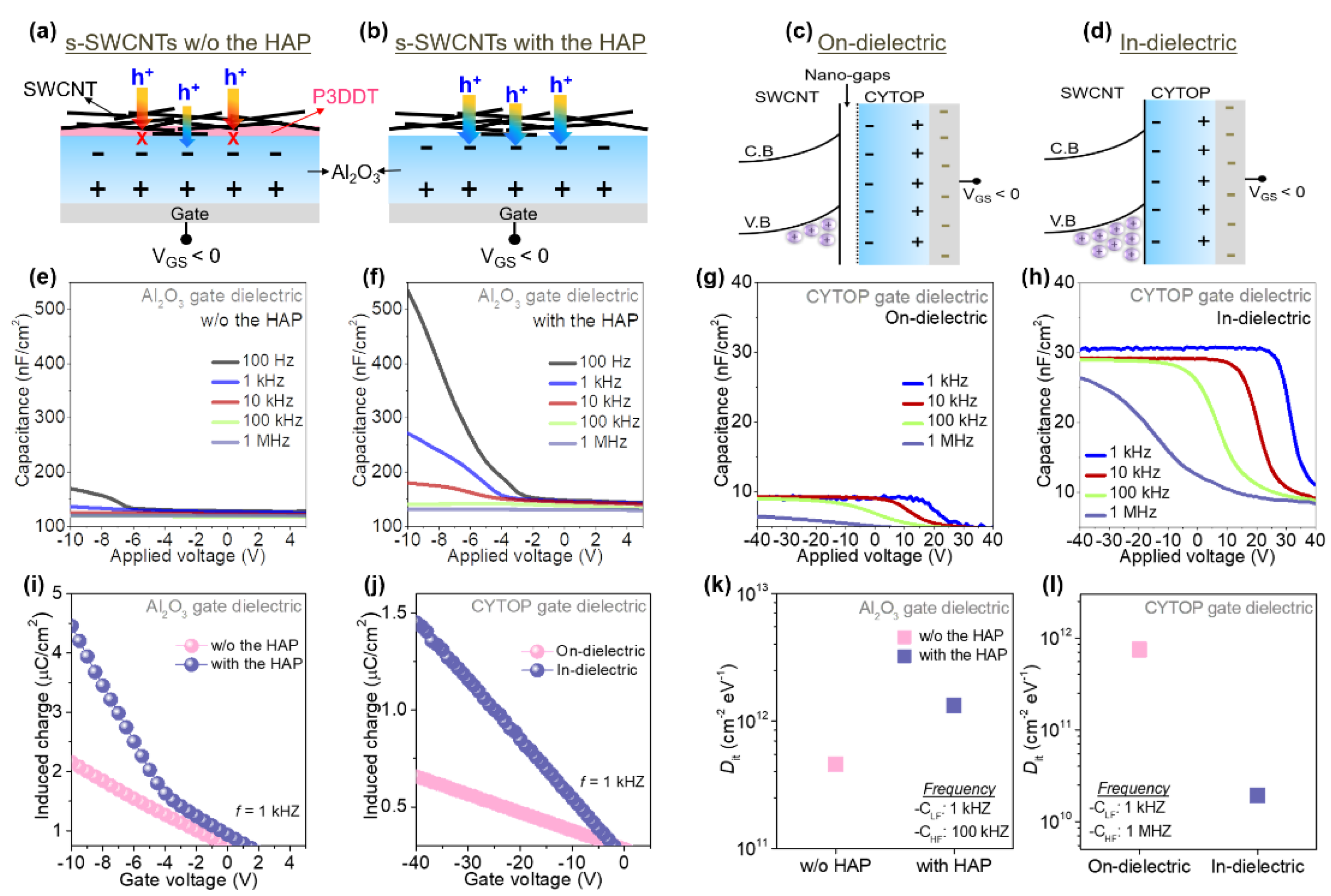

3. Results and Discussion

4. Conclusions

Supplementary Materials

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Cai, L.; Li, J.; Luan, P.; Dong, H.; Zhao, D.; Zhang, Q.; Zhang, X.; Tu, M.; Zeng, Q.; Zhou, W.; et al. Highly Transparent and Conductive Stretchable Conductors Based on Hierarchical Reticulate Single-Walled Carbon Nanotube Architecture. Adv. Funct. Mater. 2012, 22, 5238–5244. [Google Scholar] [CrossRef]

- Wang, S.; Xu, J.; Wang, W.; Wang, G.-J.N.; Rastak, R.; Molina-Lopez, F.; Chung, J.W.; Niu, S.; Feig, V.R.; Lopez, J.; et al. Skin electronics from scalable fabrication of an intrinsically stretchable transistor array. Nat. Cell Biol. 2018, 555, 83–88. [Google Scholar] [CrossRef]

- Zhu, C.; Chortos, A.; Wang, Y.; Pfattner, R.; Lei, T.; Hinckley, A.C.; Pochorovski, I.; Yan, X.; To, J.W.-F.; Oh, J.Y.; et al. Stretchable temperature-sensing circuits with strain suppression based on carbon nanotube transistors. Nat. Electron. 2018, 1, 183–190. [Google Scholar] [CrossRef]

- Heo, J.S.; Kim, T.; Ban, S.-G.; Kim, D.; Lee, J.H.; Jur, J.S.; Kim, M.-G.; Kim, Y.-H.; Hong, Y.; Park, S.K. Thread-Like CMOS Logic Circuits Enabled by Reel-Processed Single-Walled Carbon Nanotube Transistors via Selective Doping. Adv. Mater. 2017, 29, 1–8. [Google Scholar] [CrossRef] [PubMed]

- Lei, T.; Shao, L.-L.; Zheng, Y.-Q.; Pitner, G.; Fang, G.; Zhu, C.; Li, S.; Beausoleil, R.; Wong, H.-S.P.; Huang, T.-C.; et al. Low-voltage high-performance flexible digital and analog circuits based on ultrahigh-purity semiconducting carbon nanotubes. Nat. Commun. 2019, 10, 1–10. [Google Scholar] [CrossRef]

- Tang, J.; Cao, Q.; Tulevski, G.; Jenkins, K.A.; Nela, L.; Farmer, D.B.; Han, S.-J. Flexible CMOS integrated circuits based on carbon nanotubes with sub-10 ns stage delays. Nat. Electron. 2018, 1, 191–196. [Google Scholar] [CrossRef]

- Park, S.; Pitner, G.; Giri, G.; Koo, J.H.; Park, J.; Kim, K.; Wang, H.; Sinclair, R.; Wong, H.-S.P.; Bao, Z. Large-Area Assembly of Densely Aligned Single-Walled Carbon Nanotubes Using Solution Shearing and Their Application to Field-Effect Transistors. Adv. Mater. 2015, 27, 2656–2662. [Google Scholar] [CrossRef]

- Tenent, R.C.; Barnes, T.M.; Bergeson, J.D.; Ferguson, A.J.; To, B.; Gedvilas, L.M.; Heben, M.J.; Blackburn, J.L. Ultrasmooth, Large-Area, High-Uniformity, Conductive Transparent Single-Walled-Carbon-Nanotube Films for Photovoltaics Produced by Ultrasonic Spraying. Adv. Mater. 2009, 21, 3210–3216. [Google Scholar] [CrossRef]

- Krupke, R.; Hennrich, F.; Löhneysen, H.V.; Kappes, M.M. Separation of Metallic from Semiconducting Single-Walled Carbon Nanotubes. Science 2003, 301, 344–347. [Google Scholar] [CrossRef] [PubMed]

- Dyke, C.A.; Stewart, M.P.; Tour, J.M. Separation of Single-Walled Carbon Nanotubes on Silica Gel. Materials Morphology and Raman Excitation Wavelength Affect Data Interpretation. J. Am. Chem. Soc. 2005, 127, 4497–4509. [Google Scholar] [CrossRef]

- Arnold, M.S.; Green, A.; Hulvat, J.F.; Stupp, S.I.; Hersam, M.C. Sorting carbon nanotubes by electronic structure using density differentiation. Nat. Nanotechnol. 2006, 1, 60–65. [Google Scholar] [CrossRef] [PubMed]

- Kang, Y.K.; Lee, O.-S.; Deria, P.; Kim, S.H.; Park, T.-H.; Bonnell, D.A.; Saven, J.G.; Therien, M.J. Helical Wrapping of Single-Walled Carbon Nanotubes by Water Soluble Poly(p-phenyleneethynylene). Nano Lett. 2009, 9, 1414–1418. [Google Scholar] [CrossRef] [PubMed]

- Giulianini, M.; Waclawik, E.R.; Bell, J.M.; De Crescenzi, M.; Castrucci, P.; Scarselli, M.; Motta, N. Regioregular poly(3-hexyl-thiophene) helical self-organization on carbon nanotubes. Appl. Phys. Lett. 2009, 95, 13304. [Google Scholar] [CrossRef]

- Lee, H.W.; Yoon, Y.; Park, S.; Oh, J.H.; Hong, S.; Liyanage, L.S.; Wang, H.; Morishita, S.; Patil, N.; Park, Y.J.; et al. Selective dispersion of high purity semiconducting single-walled carbon nanotubes with regioregular poly(3-alkylthiophene) s. Nat. Commun. 2011, 2, 541. [Google Scholar] [CrossRef]

- Wang, W.Z.; Li, W.F.; Pan, X.Y.; Li, C.M.; Li, L.-J.; Mu, Y.G.; Rogers, J.; Chan-Park, M.B. Degradable Conjugated Polymers: Synthesis and Applications in Enrichment of Semiconducting Single-Walled Carbon Nanotubes. Adv. Funct. Mater. 2011, 21, 1643–1651. [Google Scholar] [CrossRef]

- Pochorovski, I.; Wang, H.; Feldblyum, J.I.; Zhang, X.; Antaris, A.L.; Bao, Z. H-Bonded Supramolecular Polymer for the Selective Dispersion and Subsequent Release of Large-Diameter Semiconducting Single-Walled Carbon Nanotubes. J. Am. Chem. Soc. 2015, 137, 4328–4331. [Google Scholar] [CrossRef] [PubMed]

- Lei, T.; Chen, X.; Pitner, G.; Wong, H.-S.P.; Bao, Z. Removable and Recyclable Conjugated Polymers for Highly Selective and High-Yield Dispersion and Release of Low-Cost Carbon Nanotubes. J. Am. Chem. Soc. 2016, 138, 802–805. [Google Scholar] [CrossRef]

- Arias, D.H.; Sulas-Kern, D.B.; Hart, S.M.; Kang, H.S.; Hao, J.; Ihly, R.; Johnson, J.C.; Blackburn, J.L.; Ferguson, A.J. Effect of nanotube coupling on exciton transport in polymer-free monochiral semiconducting carbon nanotube networks. Nanoscale 2019, 11, 21196–21206. [Google Scholar] [CrossRef]

- Choi, Y.; Kang, J.; Secor, E.B.; Sun, J.; Kim, H.; Lim, J.A.; Kang, M.S.; Hersam, M.C.; Cho, J.H. Capacitively Coupled Hybrid Ion Gel and Carbon Nanotube Thin-Film Transistors for Low Voltage Flexible Logic Circuits. Adv. Funct. Mater. 2018, 28, 1802610. [Google Scholar] [CrossRef]

- Wang, J.; Lei, T. Separation of Semiconducting Carbon Nanotubes Using Conjugated Polymer Wrapping. Polymers 2020, 12, 1548. [Google Scholar] [CrossRef] [PubMed]

- Yang, M.H.; Teo, K.B.K.; Gangloff, L.; Milne, W.I.; Hasko, D.G.; Robert, Y.; Legagneux, P. Advantages of top-gate, high-k dielectric carbon nanotube field-effect transistors. Appl. Phys. Lett. 2006, 88, 113507. [Google Scholar] [CrossRef]

- Cao, C.; Andrews, J.B.; Franklin, A.D. Completely Printed, Flexible, Stable, and Hysteresis-Free Carbon Nanotube Thin-Film Transistors via Aerosol Jet Printing. Adv. Electron. Mater. 2017, 3, 1700057. [Google Scholar] [CrossRef]

- Gu, H.; Swager, T.M. Fabrication of Free-standing, Conductive, and Transparent Carbon Nanotube Films. Adv. Mater. 2008, 20, 4433–4437. [Google Scholar] [CrossRef]

- Zou, J.; Liu, L.; Chen, H.; Khondaker, S.I.; McCullough, R.D.; Huo, Q.; Zhai, L. Dispersion of Pristine Carbon Nanotubes Using Conjugated Block Copolymers. Adv. Mater. 2008, 20, 2055–2060. [Google Scholar] [CrossRef]

- Samanta, S.K.; Fritsch, M.; Scherf, U.; Gomulya, W.; Bisri, S.Z.; Loi, M.A. Conjugated polymer-assisted dispersion of single-wall carbon nanotubes: The power of polymer wrapping. Acc. Chem. Res. 2014, 47, 2446–2456. [Google Scholar] [CrossRef]

- Lee, D.T.; Chung, J.W.; Park, G.; Kim, Y.T.; Lee, C.Y.; Cho, Y.; Yoo, P.J.; Han, J.-H.; Shin, H.-J.; Kim, W.J. Effect of semiconductor polymer backbone structures and side-chain parameters on the facile separation of semiconducting single-walled carbon nanotubes from as-synthesized mixtures. Appl. Surf. Sci. 2018, 429, 264–271. [Google Scholar] [CrossRef]

- McGill, S.A.; Rao, S.G.; Manandhar, P.; Xiong, P.; Hong, S. High-performance, hysteresis-free carbon nanotube field-effect transistors via directed assembly. Appl. Phys. Lett. 2006, 89, 163123. [Google Scholar] [CrossRef]

- Lee, J.S.; Ryu, S.; Yoo, K.; Choi, I.S.; Yun, W.S.; Kim, J. Origin of Gate Hysteresis in Carbon Nanotube Field-Effect Transistors. J. Phys. Chem. C 2007, 111, 12504–12507. [Google Scholar] [CrossRef]

- Jin, S.H.; Islam, A.E.; Kim, T.-I.; Kim, J.-H.; Alam, M.A.; Rogers, J.A. Sources of Hysteresis in Carbon Nanotube Field-Effect Transistors and Their Elimination Via Methylsiloxane Encapsulants and Optimized Growth Procedures. Adv. Funct. Mater. 2012, 22, 2276–2284. [Google Scholar] [CrossRef]

- Kim, W.; Javey, A.; Vermesh, O.; Wang, Q.; Li, A.Y.; Dai, H. Hysteresis Caused by Water Molecules in Carbon Nanotube Field-Effect Transistors. Nano Lett. 2003, 3, 193–198. [Google Scholar] [CrossRef]

- Derenskyi, V.; Gomulya, W.; Rios, J.M.S.; Fritsch, M.; Fröhlich, N.; Jung, S.; Allard, S.; Bisri, S.Z.; Gordiichuk, P.; Herrmann, A.; et al. Carbon Nanotube Network Ambipolar Field-Effect Transistors with 108On/Off Ratio. Adv. Mater. 2014, 26, 5969–5975. [Google Scholar] [CrossRef] [PubMed]

- Xu, Q.; Zhao, J.; Pecunia, V.; Xu, W.; Zhou, C.; Dou, J.; Gu, W.; Lin, J.; Mo, L.; Zhao, Y.; et al. Selective Conversion from p-Type to n-Type of Printed Bottom-Gate Carbon Nanotube Thin-Film Transistors and Application in Complementary Metal–Oxide–Semiconductor Inverters. ACS Appl. Mater. Interfaces 2017, 9, 12750–12758. [Google Scholar] [CrossRef] [PubMed]

- Cao, Q.; Rogers, J.A. Ultrathin Films of Single-Walled Carbon Nanotubes for Electronics and Sensors: A Review of Fundamental and Applied Aspects. Adv. Mater. 2009, 21, 29–53. [Google Scholar] [CrossRef]

- Zaumseil, J. Single-walled carbon nanotube networks for flexible and printed electronics. Semicond. Sci. Technol. 2015, 30, 074001. [Google Scholar] [CrossRef]

- Lee, S.-H.; Xu, Y.; Khim, D.; Park, W.-T.; Kim, D.-Y.; Noh, Y.-Y. Effect of Polymer Gate Dielectrics on Charge Transport in Carbon Nanotube Network Transistors: Low-k Insulator for Favorable Active Interface. ACS Appl. Mater. Interfaces 2016, 8, 32421–32431. [Google Scholar] [CrossRef]

- Wang, H.; Cobb, B.; Van Breemen, A.; Gelinck, G.G.; Bao, Z. Highly Stable Carbon Nanotube Top-Gate Transistors with Tunable Threshold Voltage. Adv. Mater. 2014, 26, 4588–4593. [Google Scholar] [CrossRef] [PubMed]

- Wu, M.-Y.; Zhao, J.; Xu, F.; Chang, T.-H.; Jacobberger, R.M.; Ma, Z.; Arnold, M.S. Highly stretchable carbon nanotube transistors enabled by buckled ion gel gate dielectrics. Appl. Phys. Lett. 2015, 107, 053301. [Google Scholar] [CrossRef]

- Cai, L.; Zhang, S.; Miao, J.; Wei, Q.; Wang, C. Capacitance-Voltage Characteristics of Thin-film Transistors Fabricated with Solution-Processed Semiconducting Carbon Nanotube Networks. Nano Online 2016, 10, 1–6. [Google Scholar] [CrossRef] [PubMed]

- Xu, Y.; Minari, T.; Tsukagoshi, K.; Chroboczek, J.A.; Ghibaudo, G. Direct evaluation of low-field mobility and access resistance in pentacene field-effect transistors. J. Appl. Phys. 2010, 107, 114507. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kim, K.-T.; Lee, K.W.; Moon, S.; Park, J.B.; Park, C.-Y.; Nam, S.-J.; Kim, J.; Lee, M.-J.; Heo, J.S.; Park, S.K. Conformally Gated Surface Conducting Behaviors of Single-Walled Carbon Nanotube Thin-Film-Transistors. Materials 2021, 14, 3361. https://doi.org/10.3390/ma14123361

Kim K-T, Lee KW, Moon S, Park JB, Park C-Y, Nam S-J, Kim J, Lee M-J, Heo JS, Park SK. Conformally Gated Surface Conducting Behaviors of Single-Walled Carbon Nanotube Thin-Film-Transistors. Materials. 2021; 14(12):3361. https://doi.org/10.3390/ma14123361

Chicago/Turabian StyleKim, Kyung-Tae, Keon Woo Lee, Sanghee Moon, Joon Bee Park, Chan-Yong Park, Seung-Ji Nam, Jaehyun Kim, Myoung-Jae Lee, Jae Sang Heo, and Sung Kyu Park. 2021. "Conformally Gated Surface Conducting Behaviors of Single-Walled Carbon Nanotube Thin-Film-Transistors" Materials 14, no. 12: 3361. https://doi.org/10.3390/ma14123361

APA StyleKim, K.-T., Lee, K. W., Moon, S., Park, J. B., Park, C.-Y., Nam, S.-J., Kim, J., Lee, M.-J., Heo, J. S., & Park, S. K. (2021). Conformally Gated Surface Conducting Behaviors of Single-Walled Carbon Nanotube Thin-Film-Transistors. Materials, 14(12), 3361. https://doi.org/10.3390/ma14123361