Fabrication and Evaluation of N-Channel GaN Metal–Oxide–Semiconductor Field-Effect Transistors Based on Regrown and Implantation Methods

Abstract

1. Introduction

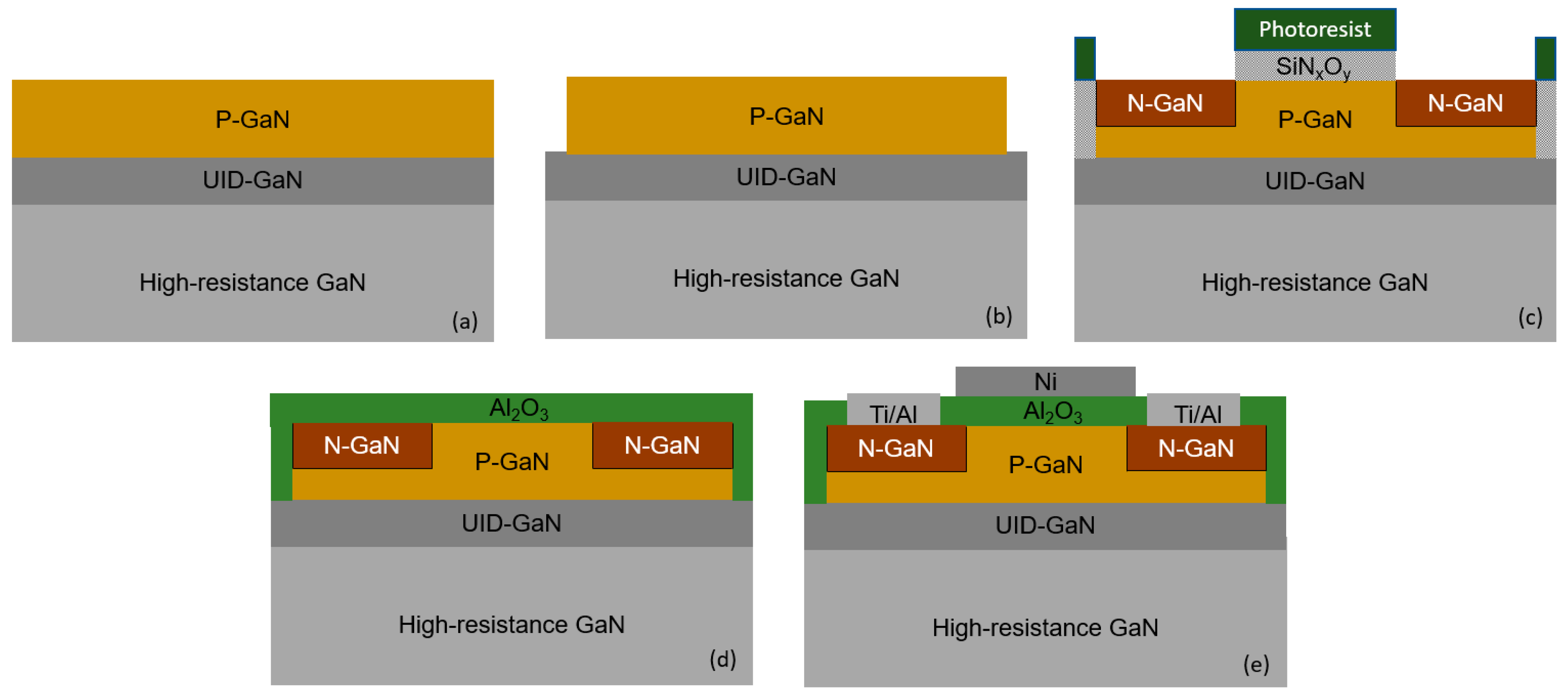

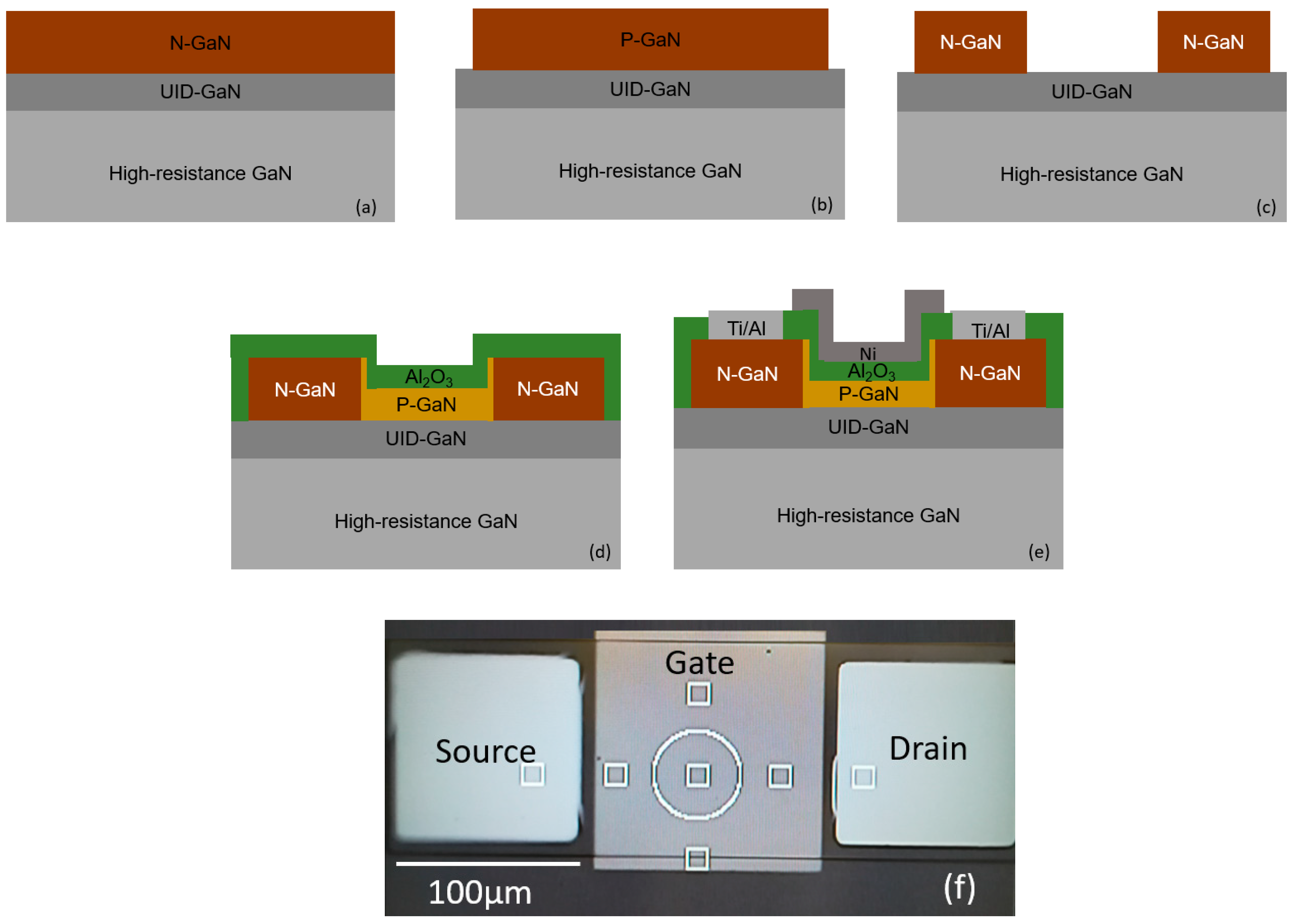

2. Experimental

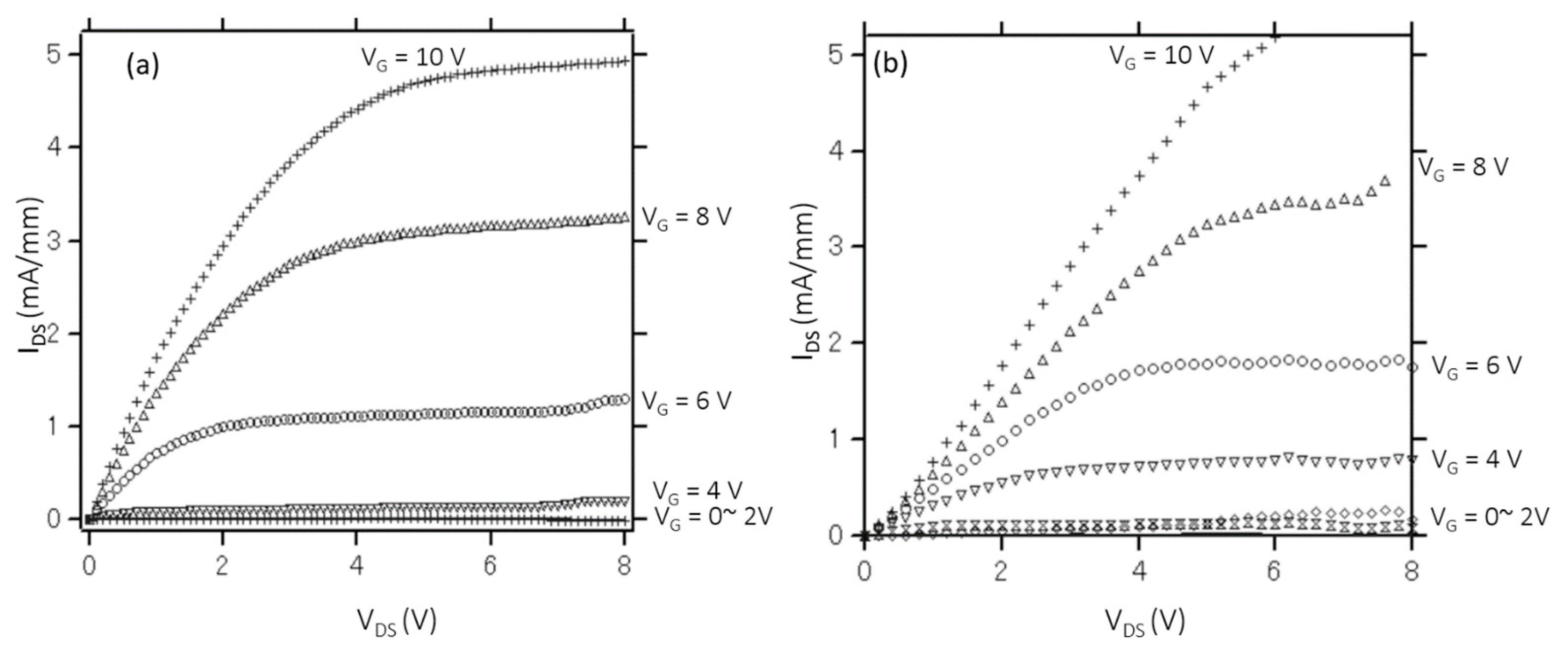

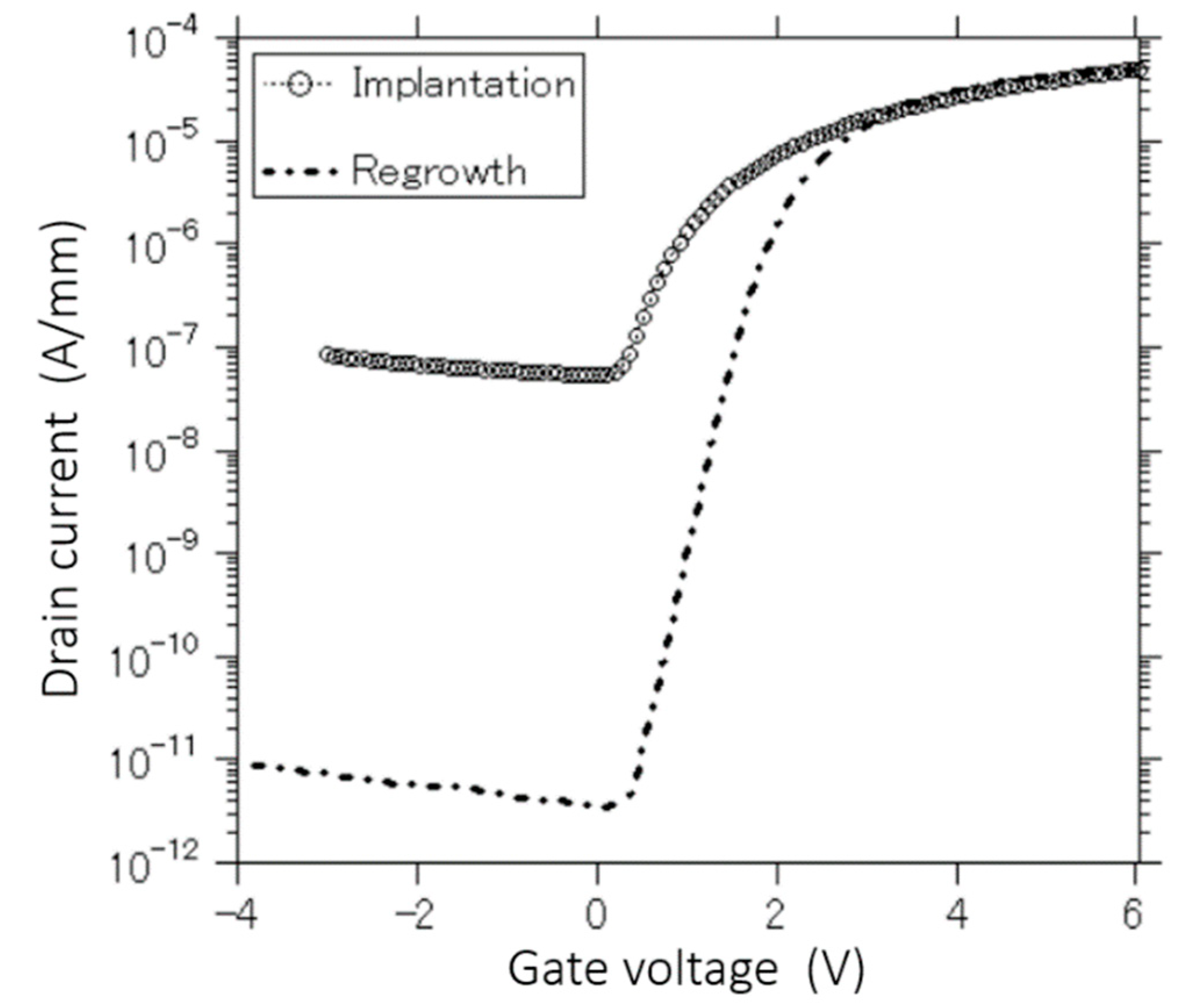

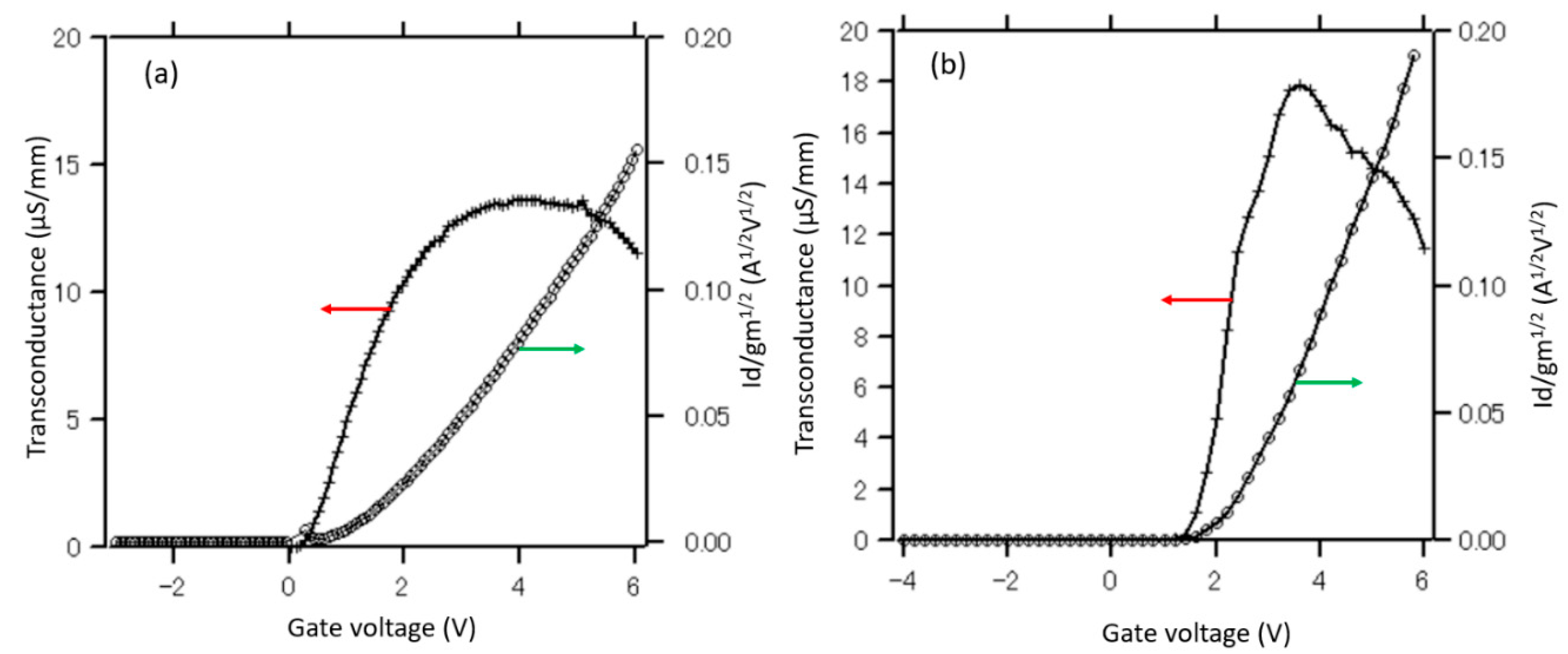

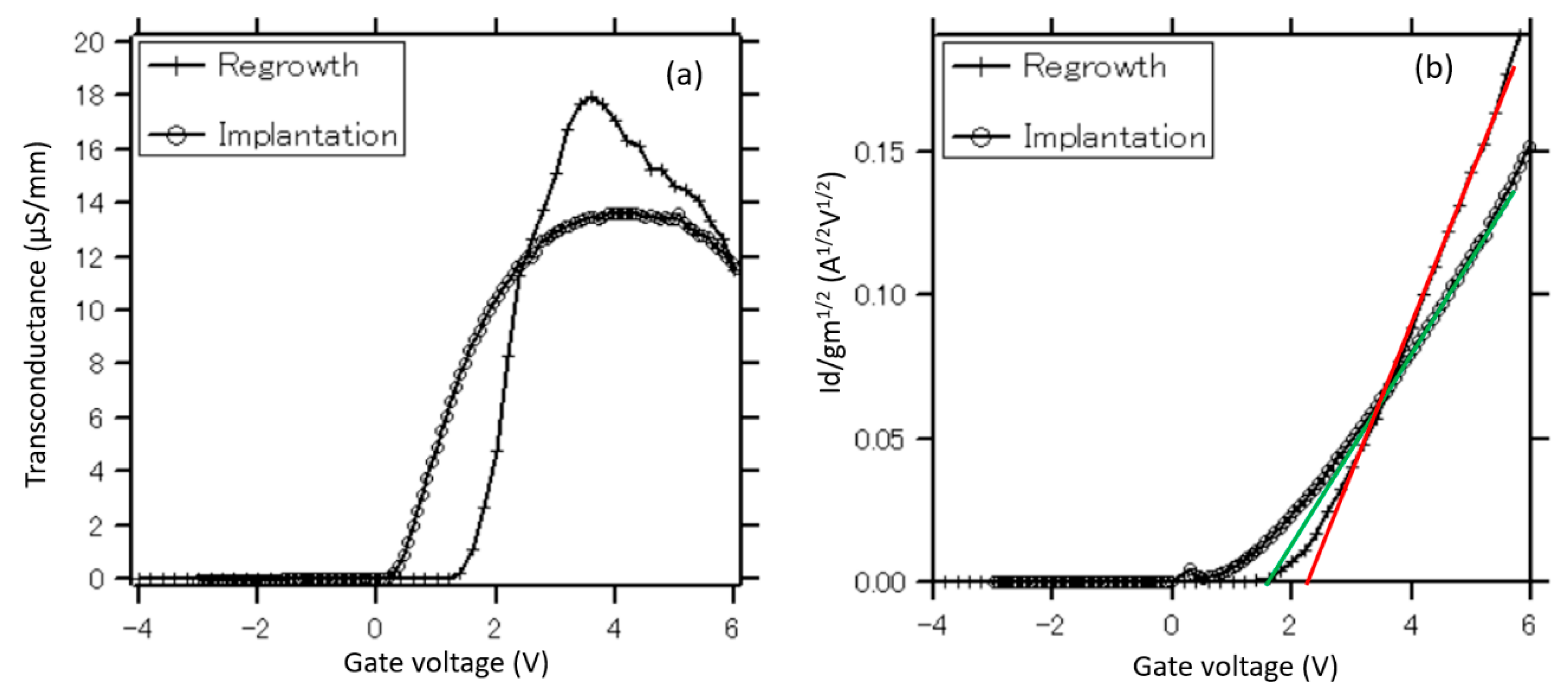

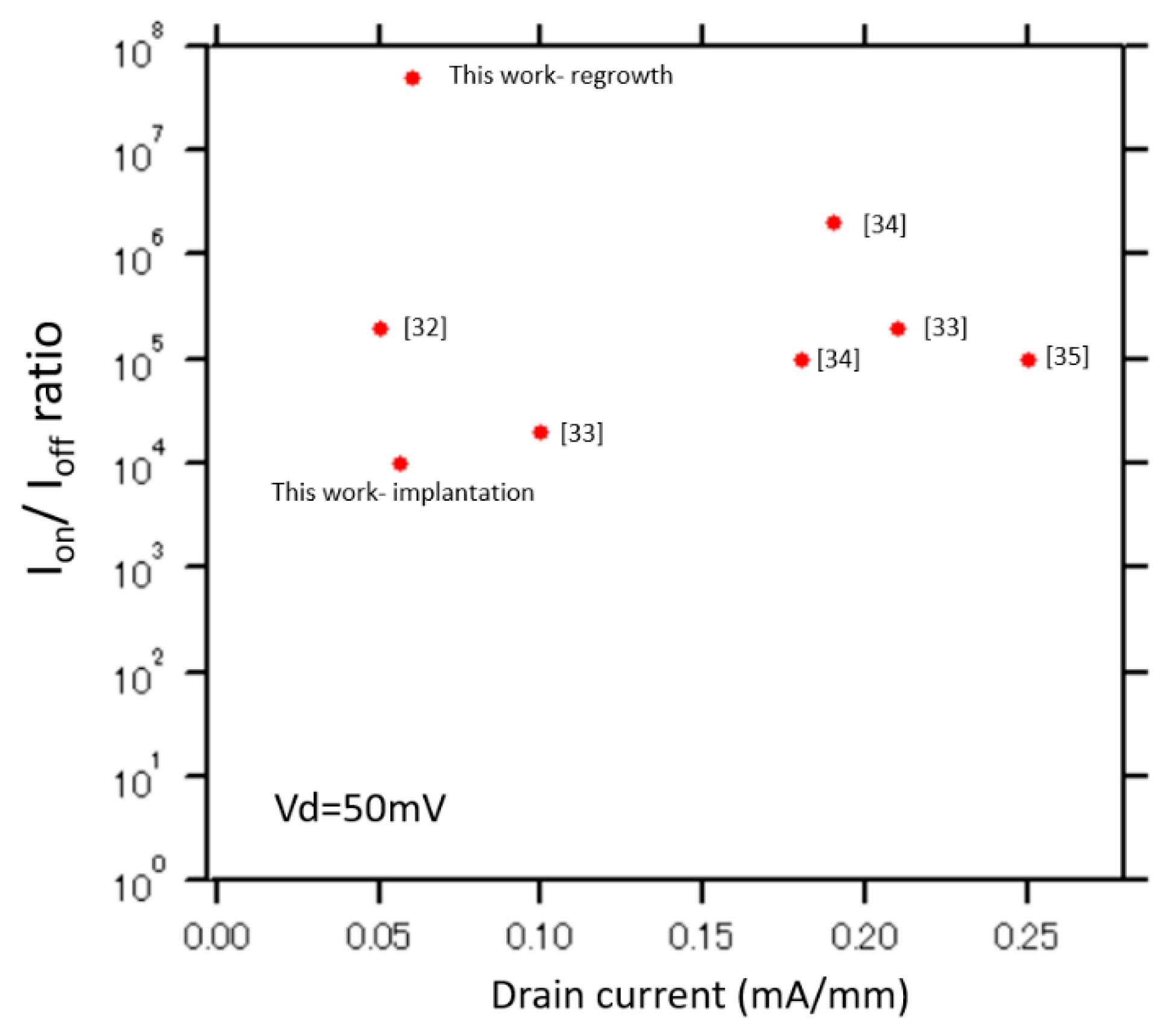

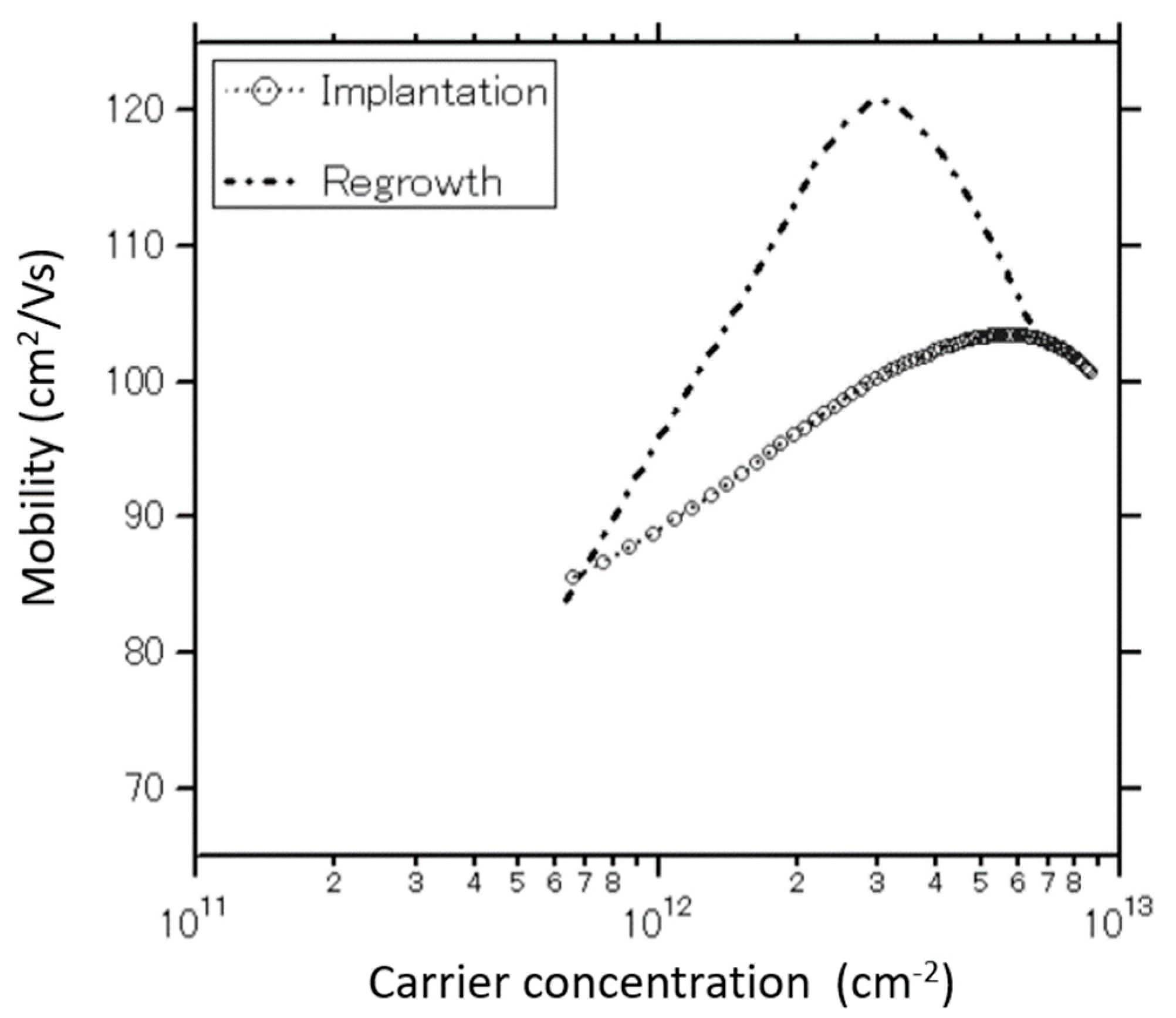

3. Results and Discussion

4. Conclusions

Author Contributions

Acknowledgments

Conflicts of Interest

References

- Roccaforte, F.; Giannazzo, F.; Iucolano, F.; Eriksson, J.; Weng, M.H.; Raineri, V. Surface and interface issues in wide band gap semiconductor electronics. Appl. Surf. Sci. 2010, 256, 5727–5735. [Google Scholar] [CrossRef]

- Saito, W.; Takada, Y.; Kuraguchi, M.; Tsuda, K.; Omura, I. Recessed-gate structure approach toward normally off high-Voltage AlGaN/GaN HEMT for power electronics applications. IEEE Electron Device Lett. 2006, 53, 356–362. [Google Scholar] [CrossRef]

- Uemoto, Y.; Hikita, M.; Ueno, H.; Matsuo Ishida, H.; Yanagihara, M.; Ueda, T.; Tanaka, T.; Ueda, D. Gate Injection Transistor (GIT)—A Normally-Off AlGaN/GaN Power Transistor Using Conductivity Modulation. IEEE Trans. Electron Devices 2007, 54, 3393–3399. [Google Scholar] [CrossRef]

- Hwang, I.; Kim, J.; Choi, H.S.; Choi, H.; Lee, J.; Kim, K.Y.; Park, J.-B.; Lee, J.C.; Ha, J.; Oh, J.; et al. p-GaN Gate HEMTs With Tungsten Gate Metal for High Threshold Voltage and Low Gate Current. IEEE Electron Device Lett. 2013, 34, 202. [Google Scholar] [CrossRef]

- Irokawa, Y.; Nakano, Y.; Ishiko, M.; Kachi, T.; Kim, J.; Ren, F.; Gila, B.P.; Onstine, A.H.; Abernathy, C.R.; Pearton, S.J.; et al. MgO/p-GaN enhancement mode metal-oxide semiconductor field-effect transistors. Appl. Phys. Lett. 2004, 84, 2919. [Google Scholar] [CrossRef]

- Huang, W.; Khan, T.; Chow, T.P. Enhancement-Mode n-Channel GaN MOSFETs on p and n-GaN/Sapphire Substrates. IEEE Electron Device Lett. 2006, 27, 796. [Google Scholar] [CrossRef]

- Otake, H.; Egami, S.; Ohta, H.; Nanishi, Y.; Takasu, H. GaN-Based Trench Gate Metal Oxide Semiconductor Field Effect Transistors with Over 100 cm2/(V s) Channel Mobility. Jpn. J. Appl. Phys. 2007, 46, L599–L601. [Google Scholar] [CrossRef]

- Kodama, M.; Sugimoto, M.; Hayashi, E.; Soejima, N.; Ishiguro, O.; Kanechika, M.; Itoh, K.; Ueda, H.; Uesugi, T.; Kachi, T. GaN-Based Trench Gate Metal Oxide Semiconductor Field-Effect Transistor Fabricated with Novel Wet Etching. Appl. Phys. Express 2008, 1, 021104. [Google Scholar] [CrossRef]

- Otake, H.; Chikamatsu, K.; Yamaguchi, A.; Fujishima, T.; Ohta, H. Vertical GaN-Based Trench Gate Metal Oxide Semiconductor Field-Effect Transistors on GaN Bulk Substrates. Appl. Phys. Express 2008, 1, 011105. [Google Scholar] [CrossRef]

- Niiyama, Y.; Ootomo, S.; Li, J.; Nomura, T.; Kato, S.; Chow, T.P. Normally off operation GaN-based MOSFETs for power electronics applications. Semicond. Sci. Technol. 2010, 25, 125006. [Google Scholar] [CrossRef]

- Kambayashi, H.; Satoh, Y.; Kokawa, T.; Ikeda, N.; Nomura, T.; Kato, S.; Teramoto, A.; Sugawa, S.; Ohmi, T. High Power Normally-Off GaN MOSFET. ECS Trans. 2011, 41, 87. [Google Scholar]

- Trung, N.H.; Taoka, N.; Yamada, H.; Takahashi, T.; Yamada, T.; Shimizu, M. Experimental Demonstration of n- and p-channel GaN-MOSFETs toward Power IC Applications. ECS J. Solid State Sci. Technol. 2020, 9, 015001. [Google Scholar] [CrossRef]

- Takashima, S.; Ueno, K.; Matsuyama, H.; Inamoto, T.; Edo, M.; Takahashi, M.S.; Nakagawa, K. Control of the inversion-channel MOS properties by Mg doping in homoepitaxial p-GaN layers. Appl. Phys. Express 2017, 10, 121004. [Google Scholar] [CrossRef]

- Zhang, K.; Liao, M.; Imura, M.; Nabatame, T.; Ohi, A.; Sumiya, M.; Sang, L. Electrical hysteresis in p-GaN metal–oxide–semiconductor capacitor with atomic-layer-deposited Al2O3 as gate dielectric. Appl. Phys. Express 2016, 9, 121002. [Google Scholar] [CrossRef]

- Chang, Y.C.; Lee, Y.J.; Chiu, Y.N.; Lin, T.D.; Wu, S.Y.; Chiu, H.C.; Kwo, J.; Wang, Y.H.; Hong, M. MBE grown high κ dielectrics Ga2O3(Gd2O3) on GaN. J. Cryst. Growth 2007, 301–302, 390–393. [Google Scholar] [CrossRef]

- Ren, F.; Hong, M.; Chu, S.N.G.; Marcus, M.A.; Schurman, M.J.; Baca, A.; Pearton, S.J.; Abernathy, C.R. Effect of temperature on Ga2O3(Gd2O3)/GaN metal–oxide–semiconductor field-effect transistors. Appl. Phys. Lett. 1998, 73, 3893. [Google Scholar] [CrossRef]

- Chang, Y.C.; Chiu, H.C.; Lee, Y.J.; Huang, M.L.; Lee, K.Y.; Hong, M.; Chiu, Y.N.; Kwo, J.; Wang, Y.H. Structural and electrical characteristics of atomic layer deposited high κ HfO2 on GaN. Appl. Phys. Lett. 2007, 90, 232904. [Google Scholar] [CrossRef]

- Saripalli, Y.N.; Pei, L.; Biggerstaff, T.; Ramachandran, S.; Duscher, G.J.; Johnson, M.A.L.; Zeng, C.; Dandu, K.; Jin, Y.; Barlage, D.W. Transmission electron microscopy studies of regrown GaN Ohmic contacts on patterned substrates for metal oxide semiconductor field effect transistor applications. Appl. Phys. Lett. 2007, 90, 204106. [Google Scholar] [CrossRef]

- Yamada, T.; Ito, J.; Asahara, R.; Watanabe, K.; Nozaki, M.; Hosoi, T.; Shimura, T.; Watanabe, H. Improved interface properties of GaN-based metal-oxide-semiconductor devices with thin Ga-oxide interlayers. Appl. Phys. Lett. 2017, 110, 261603. [Google Scholar] [CrossRef]

- Sun, M.; Zhang, Y.; Gao, X.; Palacios, T. High-performance GaN vertical fin power transistors on bulk GaN substrates. IEEE Electron Device Lett. 2017, 38, 509–512. [Google Scholar] [CrossRef]

- Lee, H.B.; Cho, H.I.; An, H.S.; Bae, Y.H.; Lee, M.B.; Lee, J.H.; Hahm, S.H. A normally off GaN n-MOSFET with Schottky-barrier source and drain on a Si-auto-doped p-GaN/Si. IEEE Electron Device Lett. 2006, 27, 81–83. [Google Scholar]

- Kucheyeva, S.O.; Williamsa, J.S.; Pearton, S. Ion implantation into GaN. J. Mater. Sci. Eng. 2001, 33, 51–107. [Google Scholar] [CrossRef]

- Neumayer, D.A.; Ekerdt, J.G. Growth of Group III Nitrides. A Review of Precursors and Techniques. Chem. Mater. 1996, 8, 9. [Google Scholar] [CrossRef]

- Cico, K.; Kuzmik, J.; Gregusova, D.; Stoklas, R.; Lalimsky, T.; Georgakilas, A.; Pogany, D.; Frohlich, K. Optimization and performance of Al2O3/GaN metal-oxide-semiconductor structures. Microelectron. Reliab. 2007, 47, 790–793. [Google Scholar] [CrossRef]

- Chang, Y.H.; Chiu, H.C.; Chang, W.H.; Kwo, J.; Tsai, C.C.; Hong, J.M.; Hong, M. GaN metal-oxide-semiconductor diodes with molecular beam epitaxy-Al2O3 as a template followed by atomic layer deposition growth. Cryst. Growth 2009, 311, 2084–2086. [Google Scholar] [CrossRef]

- Hori, Y.; Mizue, C.; Hashizume, T. Process Conditions for Improvement of Electrical Properties of Al2O3/n-GaN Structures Prepared by Atomic Layer Deposition. Jpn. J. Appl. Phys. 2010, 49, 080201. [Google Scholar] [CrossRef]

- Ostermaier, C.; Lee, H.C.; Hyun, S.Y.; Ahn, S.I.; Kim, K.W.; Cho, H.I.; Ha, J.B.; Lee, J.H. Interface characterization of ALD deposited Al2O3 on GaN by CV method. Phys. Status Solidi C 2008, 5, 1992–1994. [Google Scholar] [CrossRef]

- Kaneki, S.; Ohira, J.; Toiya, S.; Yatabe, Z.; Asubar, J.T.; Hashizume, T. Highly-stable and low-state-density Al2O3/GaN interfaces using epitaxial n-GaN layers grown on free-standing GaN substrates. Appl. Phys. Lett. 2016, 109, 162104. [Google Scholar] [CrossRef]

- Hossain, T.; Wei, D.; Edgar, J.H.; Garces, N.Y.; Nepal, N.; Hite, J.K.; Mastro, M.A.; Eddy, C.R.; Meyer, H.M. Effect of GaN surface treatment on Al2O3/n-GaN MOS capacitors. J. Vac. Sci. Technol. B 2015, 33, 061201. [Google Scholar] [CrossRef]

- Long, R.D.; McIntyre, P.C. Surface Preparation and Deposited Gate Oxides for Gallium Nitride Based Metal Oxide Semiconductor Devices. Materials 2012, 5, 1297–1335. [Google Scholar] [CrossRef]

- Taoka, N.; Trung, N.H.; Yamada, H.; Takahashi, T.; Yamada, T.; Kubo, T.; Egawa, T.; Shimizu, M. Surface and Bulk Carrier Transports in Accumulation-mode GaN MOSFETs. In Proceedings of the 49th IEEE Semiconductor Interface Specialists Conference 2018, San Diego, CA, USA, 5–8 December 2018. [Google Scholar]

- Chang, Y.C.; Chang, W.H.; Chiu, H.C.; Tung, L.T.; Lee, C.H.; Shiu, K.H.; Hong, M.; Kwo, J.; Hong, J.M.; Tsai, C.C. Inversion-channel GaN metal-oxide-semiconductor field-effect transistor with atomic-layer-deposited Al2O3 as gate dielectric. Appl. Phys. Lett. 2008, 93, 053504. [Google Scholar] [CrossRef]

- Kim, D.; Chang, S.; Lee, C.; Bae, Y.; Cristoloveanu, S.; Lee, J.; Hahm, S. Performance of GaN Metal–Oxide–Semiconductor Field-Effect Transistor with Regrown n+-Source/Drain on a Selectively Etched GaN. Jpn. J. Appl. Phys. 2013, 52, 061001. [Google Scholar] [CrossRef]

- Kambayashi, H.; Niiyama, Y.; Ootomo, S.; Nomura, T.; Iwami, M.; Satoh, Y.; Sadahiro, K.; Yoshida, S. Normally Off n-Channel GaN MOSFETs on Si Substrates Using an SAG Technique and Ion Implantation. IEEE Electron Device Lett. 2007, 28, 1077–1079. [Google Scholar] [CrossRef]

- Niiyama, Y.; Shinagawa, T.; Ootomo, S.; Kambayashi, H.; Nomura, T.; Katos, S. High-power operation of normally-off GaN MOSFETs. Furukawa Rev. 2009, 36, 1–5. [Google Scholar]

- Sun, S.C.; Plummer, J.D. Electron mobility in inversion and accumulation layers on thermally oxidized silicon surfaces. IEEE Trans. Electron Devices 1980, 27, 1497–1508. [Google Scholar] [CrossRef]

- Schwierz, F. An electron mobility model for wurtzite GaN. Solid-State Electron. 2005, 49, 889–895. [Google Scholar] [CrossRef]

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Nguyen, H.T.; Yamada, H.; Yamada, T.; Takahashi, T.; Shimizu, M. Fabrication and Evaluation of N-Channel GaN Metal–Oxide–Semiconductor Field-Effect Transistors Based on Regrown and Implantation Methods. Materials 2020, 13, 899. https://doi.org/10.3390/ma13040899

Nguyen HT, Yamada H, Yamada T, Takahashi T, Shimizu M. Fabrication and Evaluation of N-Channel GaN Metal–Oxide–Semiconductor Field-Effect Transistors Based on Regrown and Implantation Methods. Materials. 2020; 13(4):899. https://doi.org/10.3390/ma13040899

Chicago/Turabian StyleNguyen, Huu Trung, Hisashi Yamada, Toshikazu Yamada, Tokio Takahashi, and Mitsuaki Shimizu. 2020. "Fabrication and Evaluation of N-Channel GaN Metal–Oxide–Semiconductor Field-Effect Transistors Based on Regrown and Implantation Methods" Materials 13, no. 4: 899. https://doi.org/10.3390/ma13040899

APA StyleNguyen, H. T., Yamada, H., Yamada, T., Takahashi, T., & Shimizu, M. (2020). Fabrication and Evaluation of N-Channel GaN Metal–Oxide–Semiconductor Field-Effect Transistors Based on Regrown and Implantation Methods. Materials, 13(4), 899. https://doi.org/10.3390/ma13040899