Stable Logic Operation of Fiber-Based Single-Walled Carbon Nanotube Transistor Circuits Toward Thread-Like CMOS Circuitry

Abstract

1. Introduction

2. Experimental Procedure

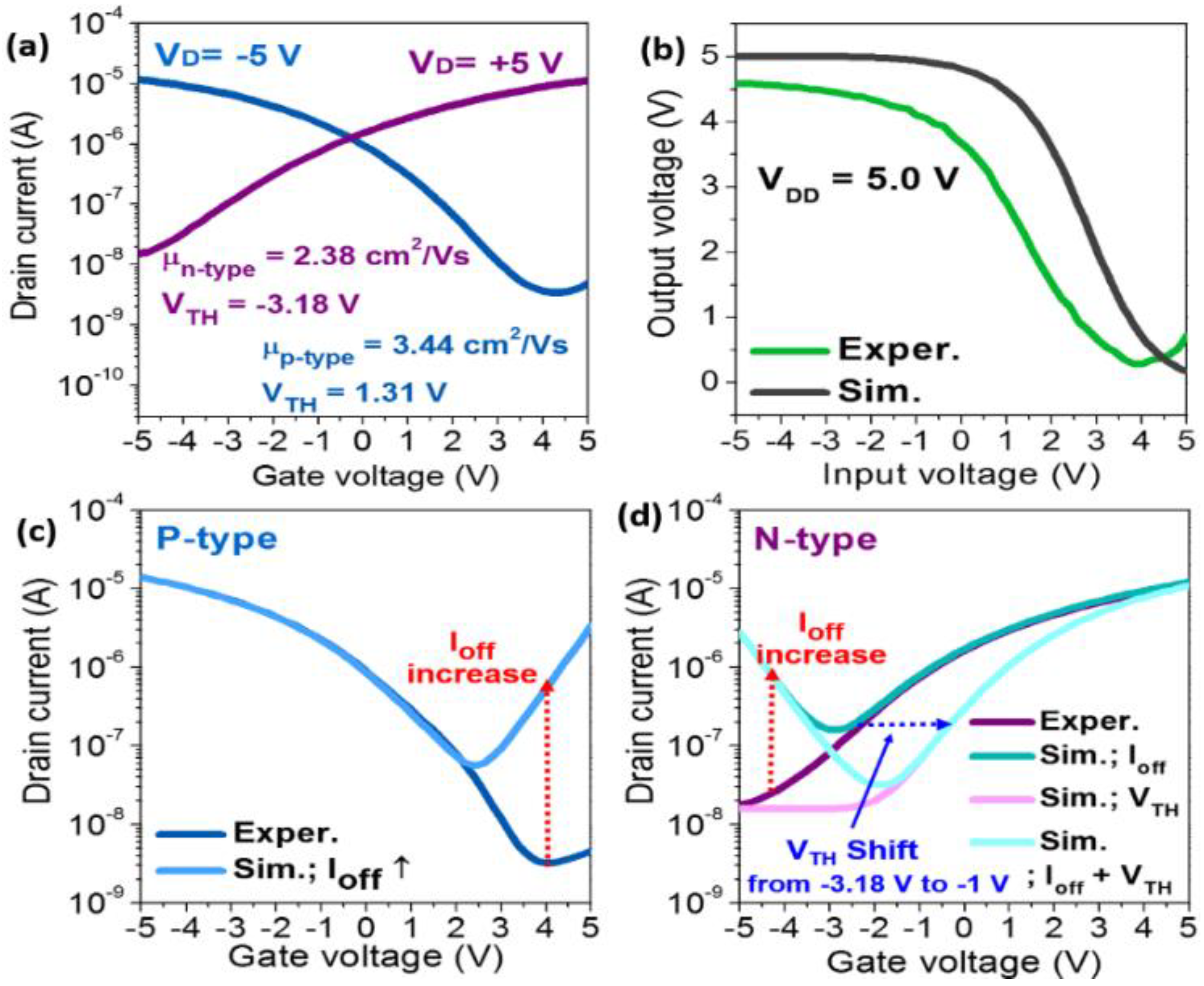

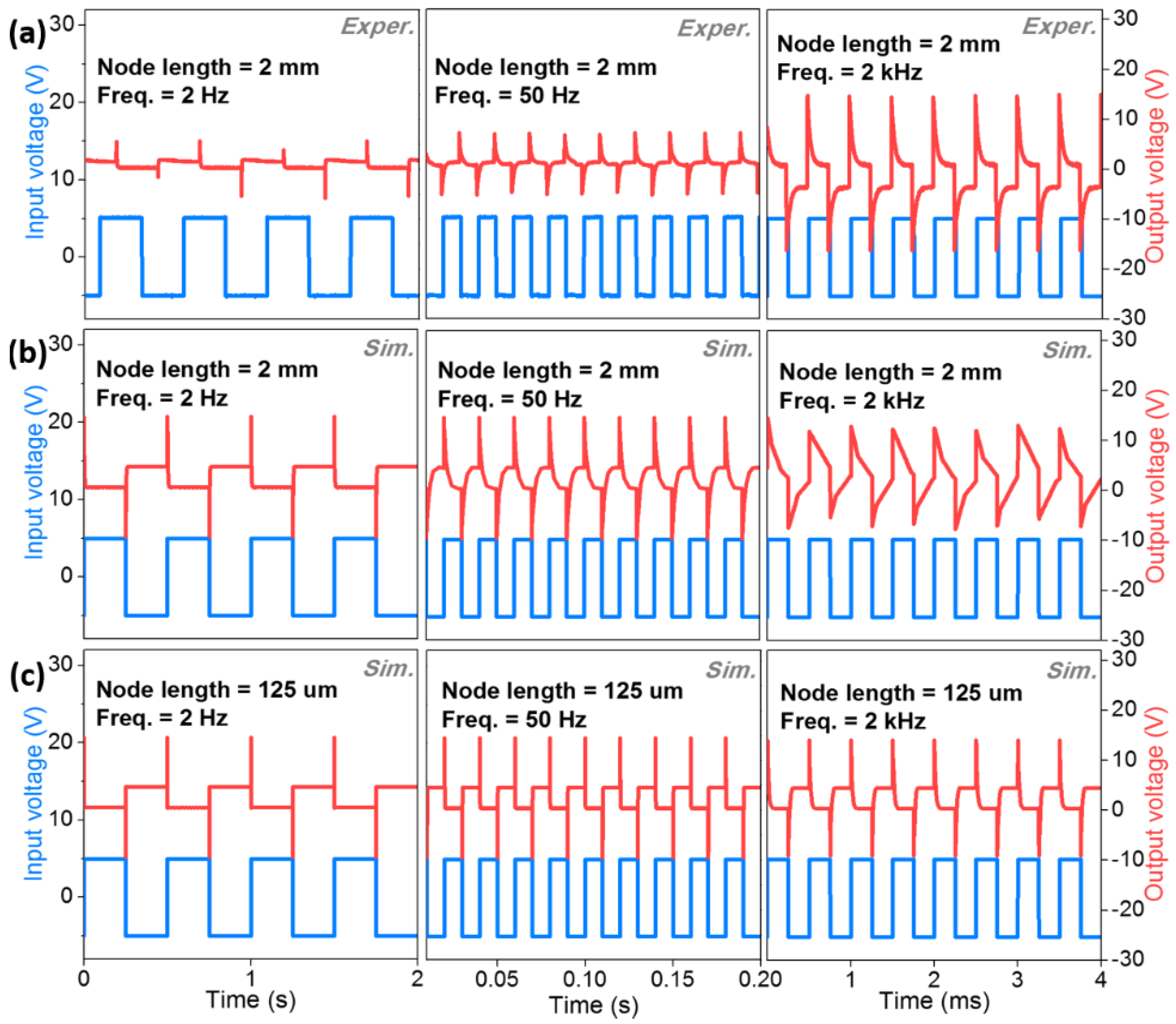

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Sekitani, T.; Noguchi, Y.; Hata, K.; Fukushima, T.; Aida, T.; Someya, T. A rubberlike stretchable active matrix using elastic conductors. Science 2008, 321, 1468–1472. [Google Scholar] [CrossRef] [PubMed]

- Yan, C.; Kang, W.; Wang, J.; Cui, M.; Wang, X.; Foo, C.Y.; Chee, K.J.; Lee, P.S. Stretchable and wearable electrochromic devices. ACS Nano 2014, 8, 316–322. [Google Scholar] [CrossRef] [PubMed]

- Matsuhisa, N.; Kaltenbrunner, M.; Yokota, T.; Jinno, H.; Kuribara, K.; Sekitani, T.; Someya, T. Printable elastic conductors with a high conductivity for electronic textile applications. Nat. Commun. 2015, 6, 7461. [Google Scholar] [CrossRef] [PubMed]

- Heo, J.S.; Eom, J.; Kim, Y.H.; Park, S.K. Recent Progress of Textile-Based Wearable Electronics: A Comprehensive Review of Materials, Devices and Applications. Small 2017, 14, 1703034. [Google Scholar] [CrossRef] [PubMed]

- Zeng, W.; Shu, L.; Li, Q.; Chen, S.; Wang, F.; Tao, X.-M. Fiber-Based Wearable Electronics: A Review of Materials, Fabrication, Devices, and Applications. Adv. Mater. 2014, 26, 5310–5336. [Google Scholar] [CrossRef] [PubMed]

- Yoon, J.; Jeong, Y.; Kim, H.; Yoo, S.; Jung, H.; Kim, Y.; Hwang, Y.; Hyun, Y.; Hong, W.; Lee, B.; et al. Robust and stretchable indium gallium zinc oxide-based electronic textiles formed by cilia-assisted transfer printing. Nat. Commun. 2016, 7, 11477. [Google Scholar] [CrossRef] [PubMed]

- Zhang, Z.; Guo, K.; Li, Y.; Li, X.; Guan, G.; Li, H.; Luo, Y.; Zhao, F.; Zhang, Q.; Wei, B.; et al. A colour-tunable, weavable fibre-shaped polymer light-emitting electrochemical cell. Nat. Photonics 2015, 9, 233–238. [Google Scholar] [CrossRef]

- Kwon, S.; Kim, H.; Choi, S.; Jeong, E.; Kim, D.; Lee, S.; Lee, H.; Seo, Y.; Choi, K. Weavable and Highly Efficient Organic Light-Emitting Fibers for Wearable Electronics: A Scalable, Low-Temperature Process. Nano Lett. 2018, 18, 347–356. [Google Scholar] [CrossRef] [PubMed]

- Zhou, T.; Zhang, C.; Han, C.B.; Fan, F.R.; Tang, W.; Wang, Z.L. Woven Structured Triboelectric Nanogenerator for Wearable Devices. ACS Appl. Mater. Interfaces 2014, 6, 14695–14701. [Google Scholar] [CrossRef] [PubMed]

- Lai, Y.-C.; Deng, J.; Zhang, S.-L.; Niu, S.; Guo, H.; Wang, Z.-L. Single-Thread-Based Wearable and Highly Stretchable Triboelectric Nanogenerators and Their Applications in Cloth-Based Self-Powered Human-Interactive and Biomedical Sensing. Adv. Funct. Mater. 2017, 27, 1604462. [Google Scholar] [CrossRef]

- Li, W.; Torres, D.; Díaz, R.; Wang, Z.; Wu, C.; Wang, C.; Wang, Z.L.; Sepúlveda, N. Nanogenerator-based dual-functional and self-powered thin patch loudspeaker or microphone for flexible electronics. Nat. Commun. 2017, 8, 15310. [Google Scholar] [CrossRef] [PubMed]

- Heo, J.S.; Kim, T.; Ban, S.G.; Kim, D.; Lee, J.H.; Jur, J.; Kim, M.G.; Kim, Y.H.; Hong, Y.; Park, S.K. Thread-Like CMOS Logic Circuits Enabled by Reel-Processed Single-Walled Carbon Nanotube Transistors via Selective Doping. Adv. Mater. 2017, 29, 1701822. [Google Scholar] [CrossRef] [PubMed]

- Lee, J.M.; Cho, I.T.; Lee, J.H.; Kwon, H.I. Full-Swing InGaZnO Thin Film Transistor Inverter with Depletion Load. Jpn. J. Appl. Phys. 2009, 48, 100202. [Google Scholar] [CrossRef]

- Roy, K.; Mukhopadhyay, S.; Mahmoodi-Meimand, H. Leakage current mechanisms and leakage reduction techniques in deep-submicrometer CMOS circuits. Proc. IEEE 2003, 91, 305–327. [Google Scholar] [CrossRef]

- Fischer, A.; Zündorf, H.; Kaschura, F.; Widmer, J.; Leo, K.; Kraft, U.; Klauk, H. Nonlinear Contact Effects in Staggered Thin-Film Transistors. Phys. Rev. Appl. 2017, 8, 54012. [Google Scholar] [CrossRef]

- Naab, B.D.; Guo, S.; Olthof, S.; Evans, E.G.B.; Wei, P.; Millhauser, G.L.; Kahn, A.; Barlow, S.; Marder, S.R.; Bao, Z. Mechanistic Study on the Solution-Phase n-Doping of 1,3-Dimethyl-2-aryl-2,3-dihydro-1 H -benzoimidazole Derivatives. J. Am. Chem. Soc. 2013, 135, 15018–15025. [Google Scholar] [CrossRef] [PubMed]

- Cerdeira, A.; Estrada, M.; Garcia, R.; Ortiz-Conde, A.; Garcia Sanchez, F.J. New procedure for the extraction of basic a-Si:H TFT model parameters in the linear and saturation regions. Solid-State Electron. 2001, 45, 1077–1080. [Google Scholar] [CrossRef]

- Ding, L.; Wang, S.; Zhang, Z.; Zeng, Q.; Wang, Z.; Pei, T.; Yang, L.; Liang, X.; Shen, J.; Chen, Q.; et al. Y-Contacted High-Performance n-Type Single-Walled Carbon Nanotube Field-Effect Transistors: Scaling and Comparison with Sc-Contacted Devices. Nano Lett. 2009, 9, 4209–4214. [Google Scholar] [CrossRef] [PubMed]

- Ding, L.; Zhang, Z.; Liang, S.; Pei, T.; Wang, S.; Li, Y.; Zhou, W.; Liu, J.; Peng, L. CMOS-based carbon nanotube pass-transistor logic integrated circuits. Nat. Commun. 2012, 3, 677. [Google Scholar] [CrossRef] [PubMed]

- Ante, F.; Kälblein, D.; Zaki, T.; Zschieschang, U.; Takimiya, K.; Ikeda, M.; Sekitani, T.; Someya, T.; Burghartz, J.N.; Kern, K.; et al. Contact Resistance and Megahertz Operation of Aggressively Scaled Organic Transistors. Small 2012, 8, 73–79. [Google Scholar] [CrossRef] [PubMed]

- Zaki, T.; Scheinert, S.; Horselmann, I.; Rodel, R.; Letzkus, F.; Richter, H.; Zschieschang, U.; Klauk, H.; Burghartz, J.N. Accurate Capacitance Modeling and Characterization of Organic Thin-Film Transistors. IEEE Trans. Electron Devices 2014, 61, 98–104. [Google Scholar] [CrossRef]

- Kim, J.H.; Kim, J.K.; Jo, S.H.; Kang, J.G.; Jo, J.W.; Lee, M.W.; Moon, J.H.; Yang, L.; Kim, M.G.; Kim, Y.H.; et al. Ultrahigh Detective Heterogeneous Photosensor Arrays with In-Pixel Signal Boosting Capability for Large-Area and Skin-Compatible Electronics. Adv. Mater. 2016, 28, 3078–3086. [Google Scholar] [CrossRef] [PubMed]

- Shi, K.; Zhang, F.; Di, C.; Yan, T.; Zou, Y.; Zhou, X.; Zhu, D.; Wang, J.; Pei, J. Toward High Performance n-Type Thermoelectric Materials by Rational Modification of BDPPV Backbones. J. Am. Chem. Soc. 2015, 137, 6979–6982. [Google Scholar] [CrossRef] [PubMed]

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Heo, J.S.; Kim, K.-T.; Ban, S.-G.; Kim, Y.-J.; Kim, D.; Kim, T.; Hong, Y.; Kim, I.-S.; Park, S.K. Stable Logic Operation of Fiber-Based Single-Walled Carbon Nanotube Transistor Circuits Toward Thread-Like CMOS Circuitry. Materials 2018, 11, 1878. https://doi.org/10.3390/ma11101878

Heo JS, Kim K-T, Ban S-G, Kim Y-J, Kim D, Kim T, Hong Y, Kim I-S, Park SK. Stable Logic Operation of Fiber-Based Single-Walled Carbon Nanotube Transistor Circuits Toward Thread-Like CMOS Circuitry. Materials. 2018; 11(10):1878. https://doi.org/10.3390/ma11101878

Chicago/Turabian StyleHeo, Jae Sang, Kyung-Tae Kim, Seok-Gyu Ban, Yoon-Jeong Kim, Daesik Kim, Taehoon Kim, Yongtaek Hong, In-Soo Kim, and Sung Kyu Park. 2018. "Stable Logic Operation of Fiber-Based Single-Walled Carbon Nanotube Transistor Circuits Toward Thread-Like CMOS Circuitry" Materials 11, no. 10: 1878. https://doi.org/10.3390/ma11101878

APA StyleHeo, J. S., Kim, K.-T., Ban, S.-G., Kim, Y.-J., Kim, D., Kim, T., Hong, Y., Kim, I.-S., & Park, S. K. (2018). Stable Logic Operation of Fiber-Based Single-Walled Carbon Nanotube Transistor Circuits Toward Thread-Like CMOS Circuitry. Materials, 11(10), 1878. https://doi.org/10.3390/ma11101878