The Applicability of Traditional Protection Methods to Lines Emanating from VSC-HVDC Interconnectors and a Novel Protection Principle

Abstract

:1. Introduction

2. Control System of the VSC-HVDC Interconnector

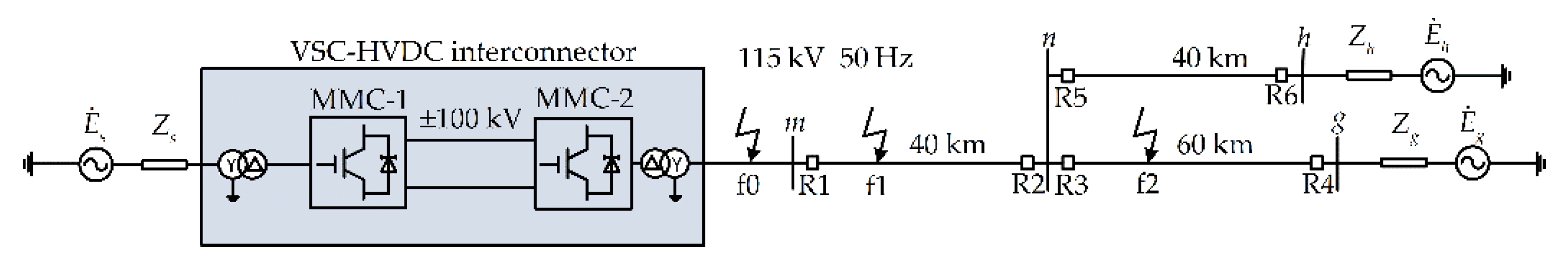

2.1. An AC/DC Hybrid System

2.2. FRT Control

- Once the positive-sequence voltage of the interconnector AC bus drops below 90% of the rated voltage, the two outer power control loops of the converter are blocked.

- The command reference of positive-sequence reactive current iqref+ is adaptively adjusted according to the magnitude of positive-sequence voltage. Taking a as the ratio of positive-sequence voltage of the interconnector AC bus to the rated phase voltage. If 0.2 ≤ a < 0.9, iqref+ will increase linearly from iq0 to 1.05 times the rated current with the decrease of a, where iq0 is the command reference of positive-sequence reactive current before fault and iq0 is regarded as zero when iq0 < 0 before the fault. If a < 0.2, iqref+ will be set as 1.05 times the rated current. iqref+ is given by:where IN is the rated AC current expressed in abc frame, and it should be multiplied by to be expressed in the d-q frame. The relationship between iqref+ and a is shown in Figure 2.

- If the fault side converter works as an inverter before the fault, the command reference of positive-sequence active current idref+ will be set as ; otherwise idref+ will be set as . idref+ is given by:where id0 is the command reference of positive-sequence active current before the fault.

2.3. Output Characteristics of the VSC-HVDC Interconnector after a Fault

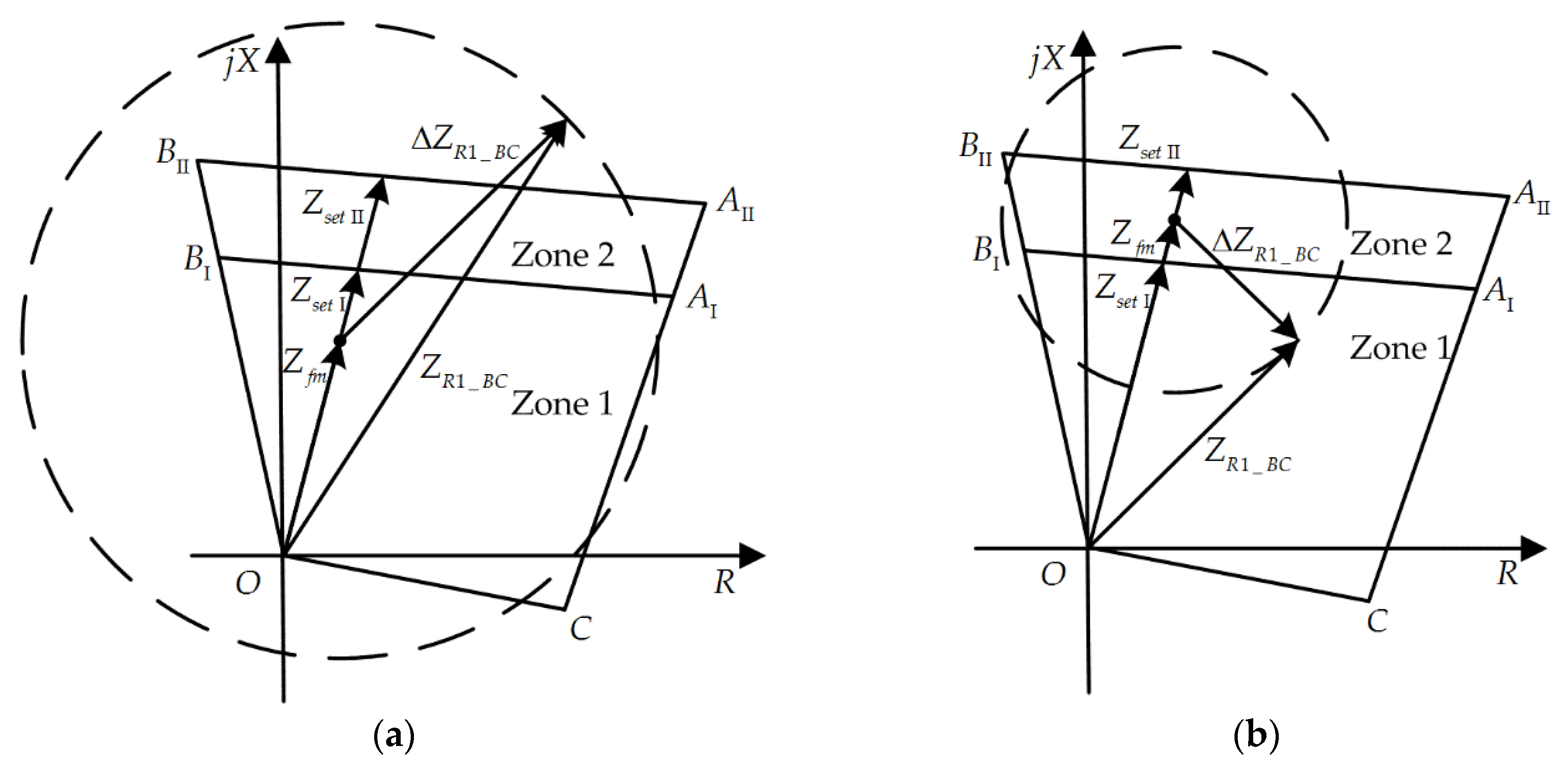

3. Applicability Analysis of Phase-to-Phase Distance Protection

3.1. Applicability Analysis of R1

3.2. Applicability Analysis of R2

3.3. Simulation Results

3.3.1. Case Study

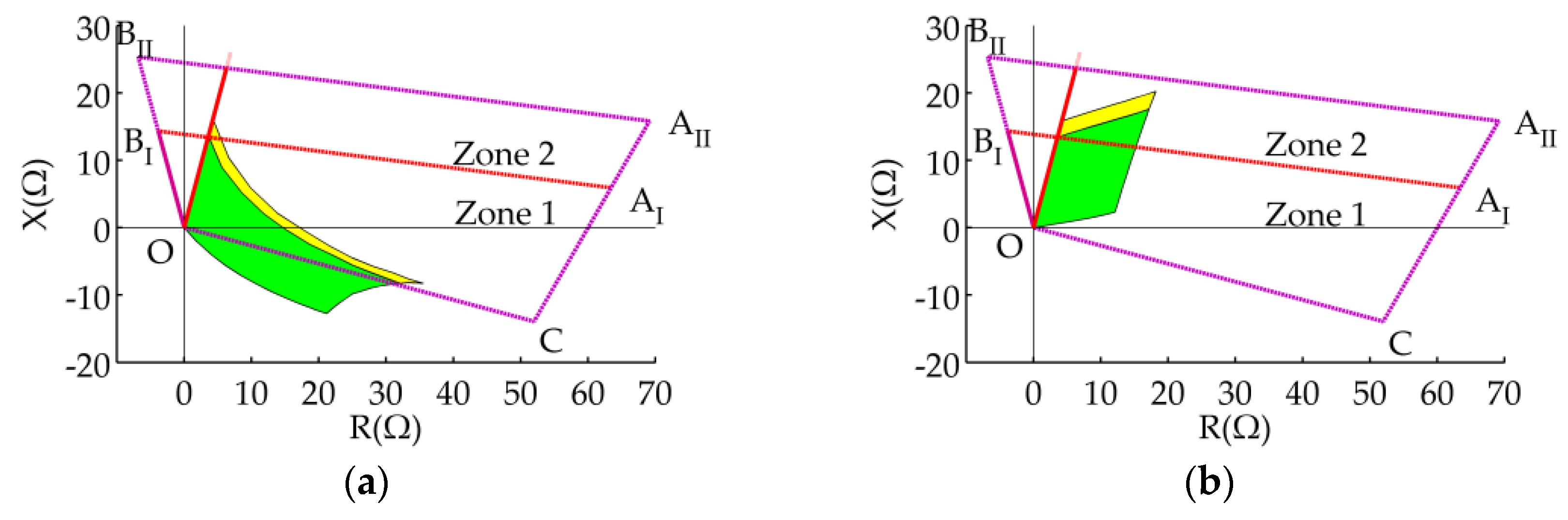

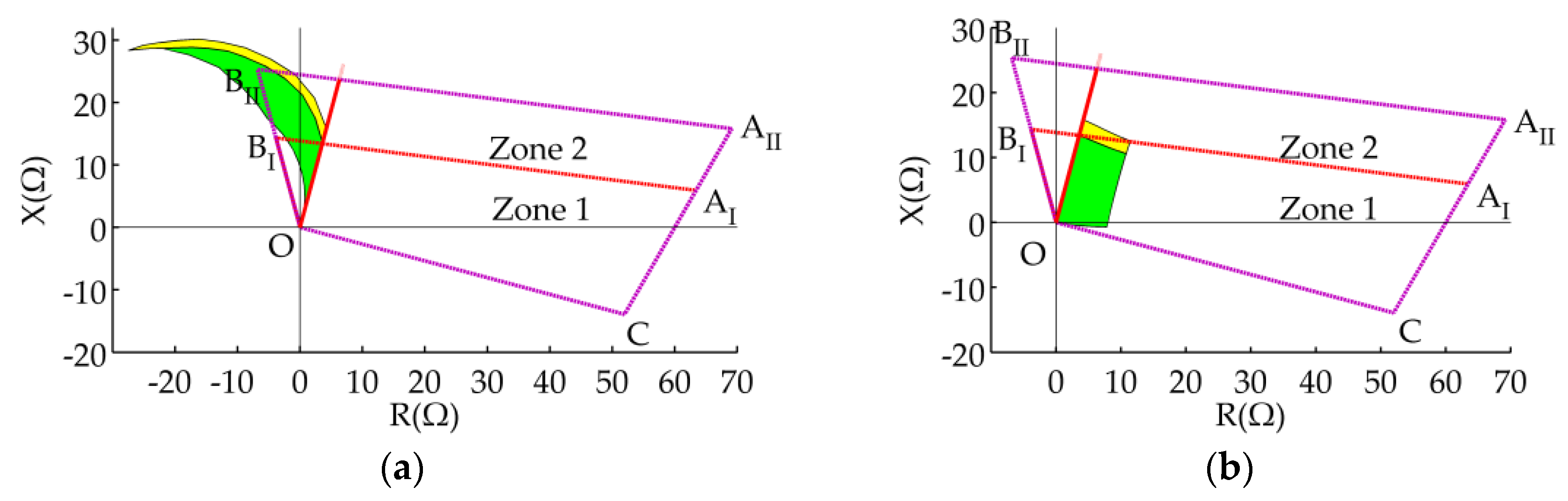

3.3.2. Area of Measured Impedance

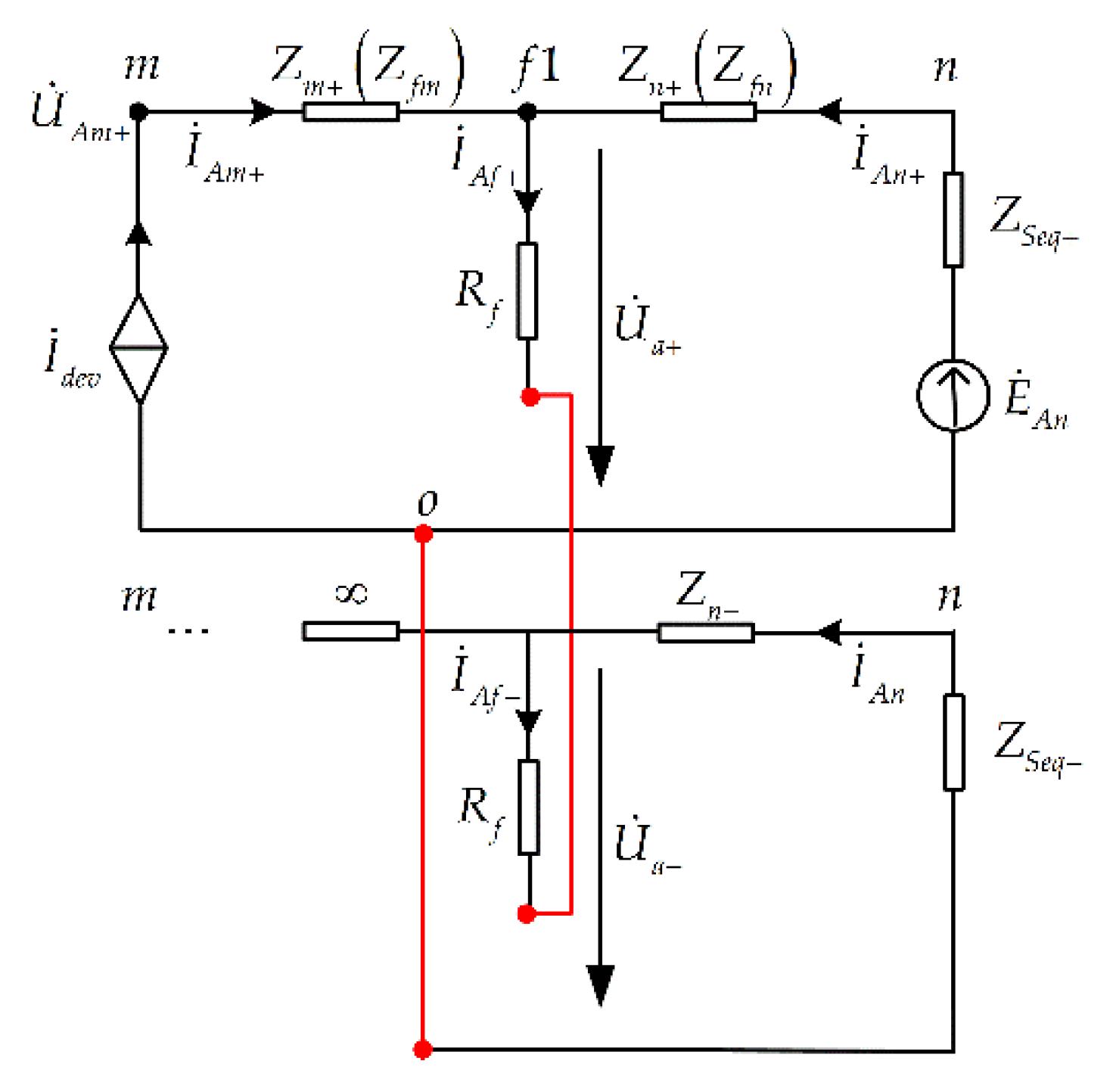

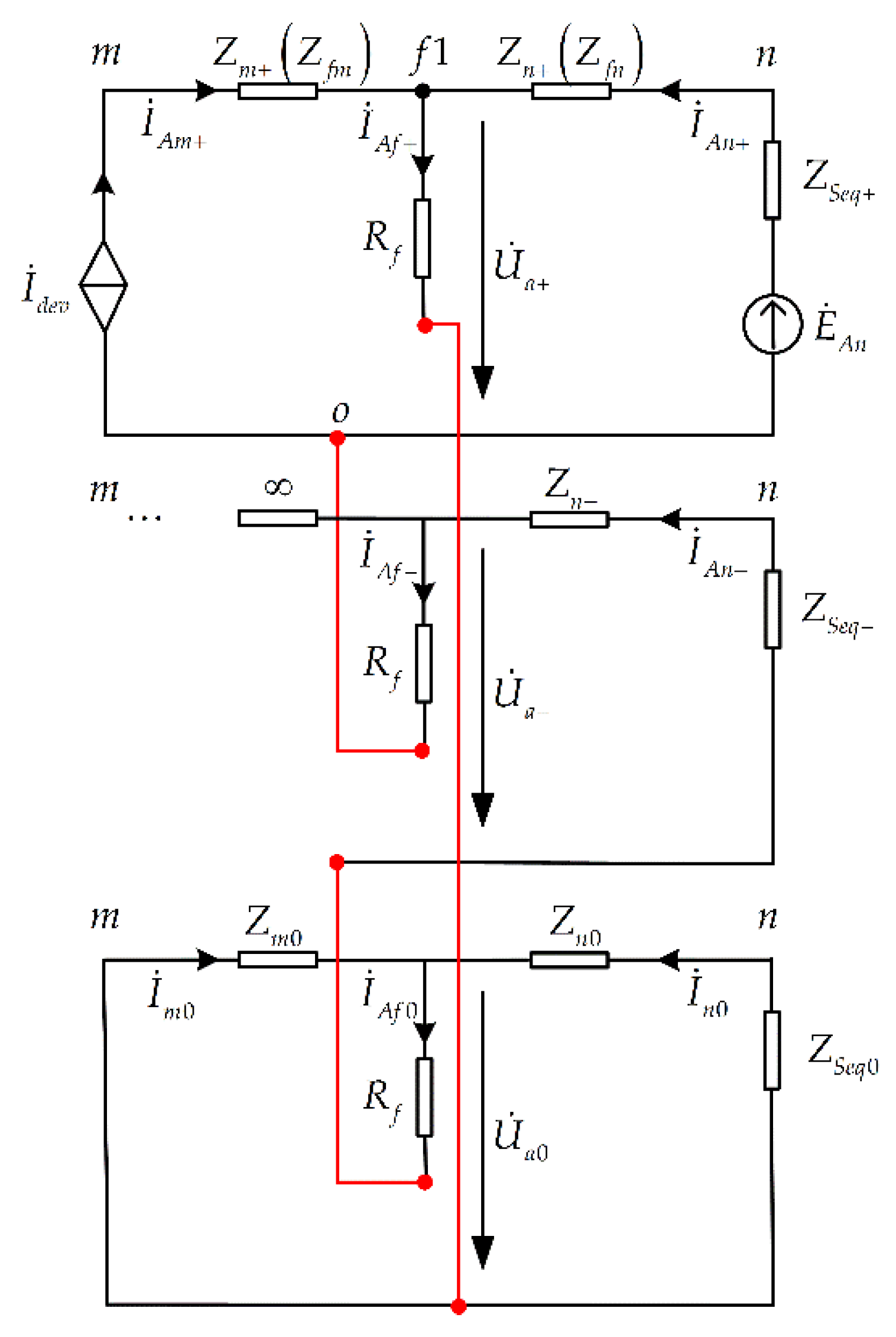

4. Applicability Analysis of Ground Distance Protection

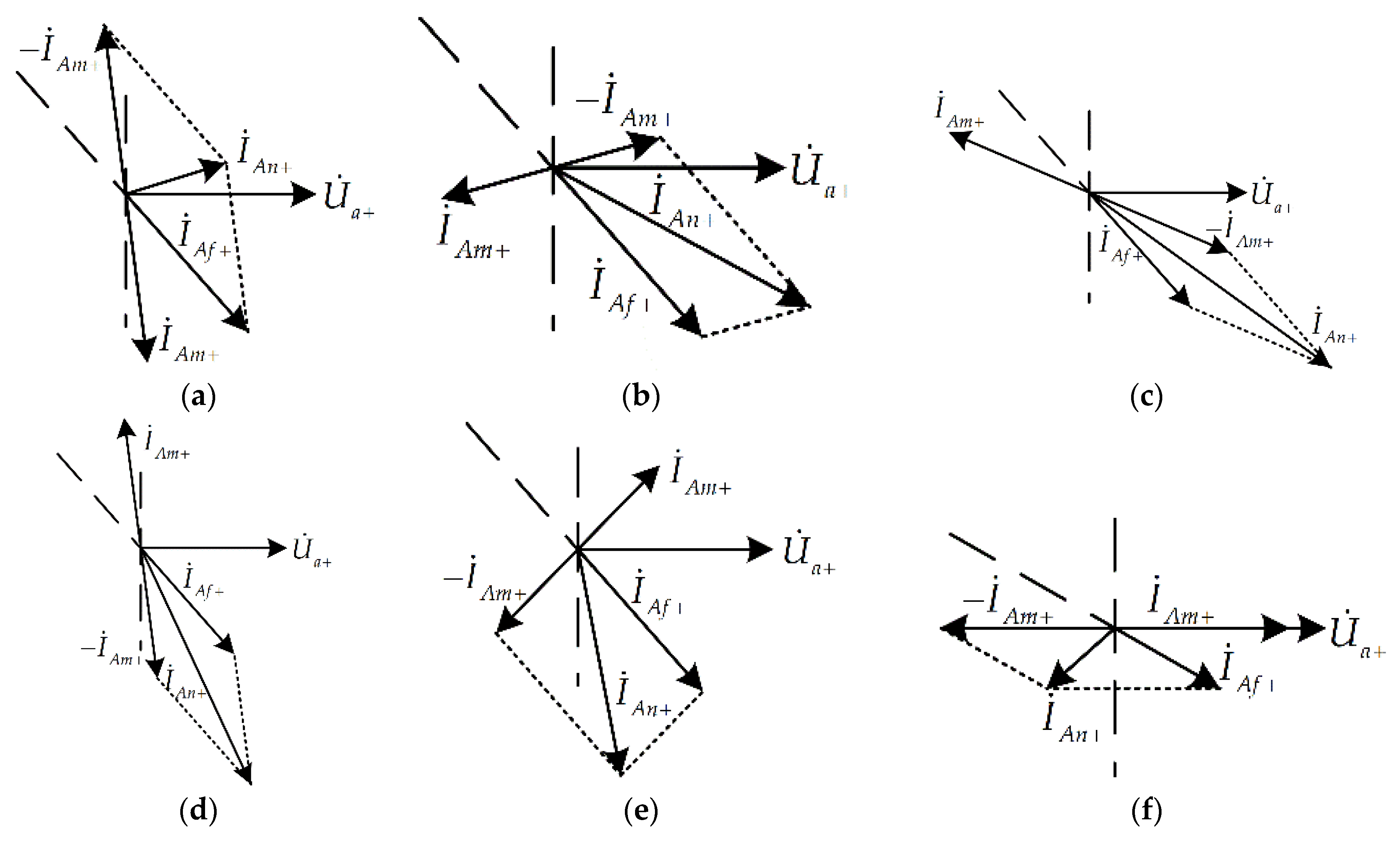

4.1. Applicability Analysis of R1 and R2

4.1.1. Analysis of the Phase Relationship between Positive-Sequence Voltage at the Fault Location and İAm+

4.1.2. Analysis of the Range of the Angle of Additional Impedance

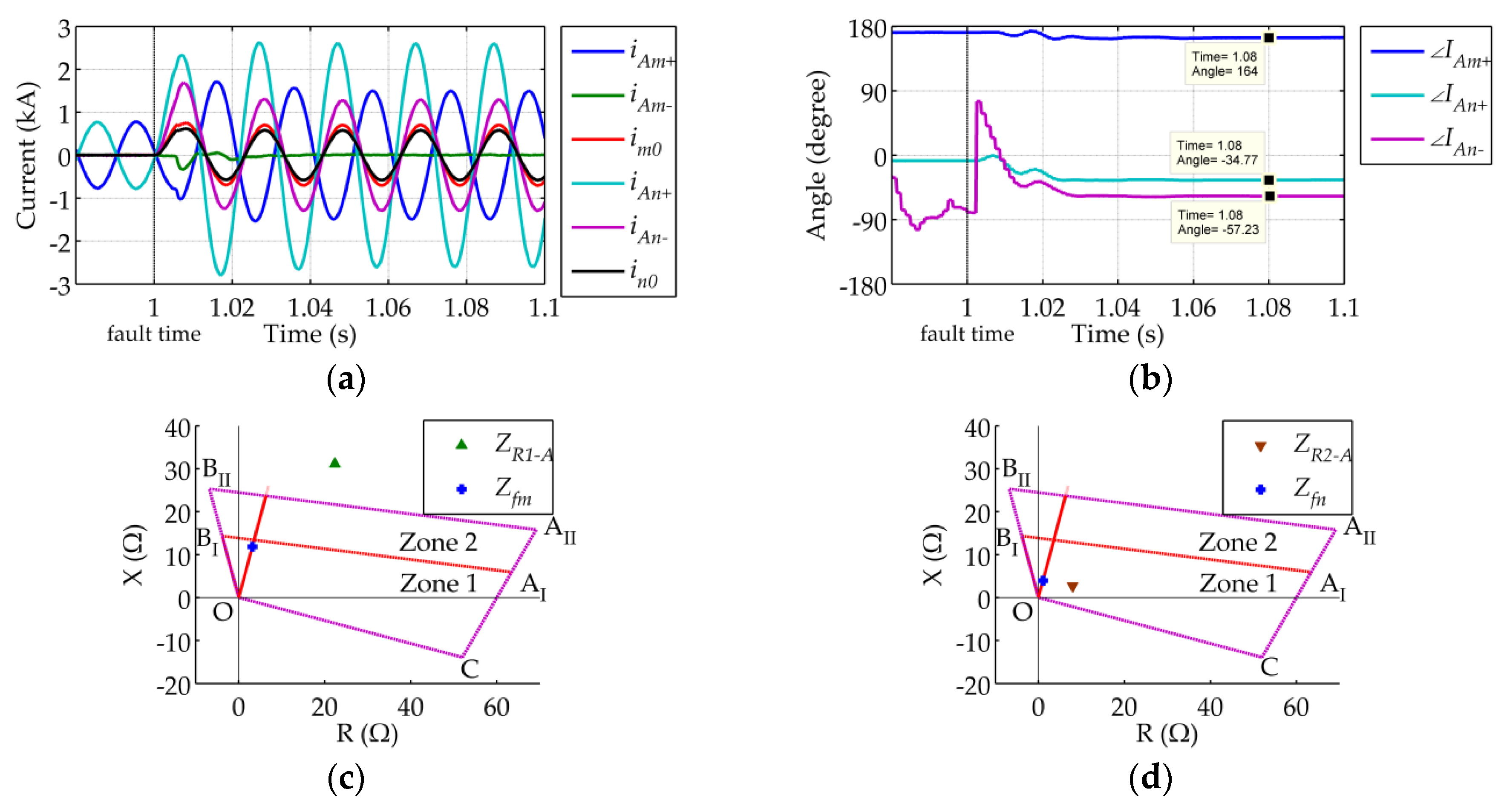

4.2. Simulation Results

4.2.1. Case 1

4.2.2. Case 2

5. Applicability Analysis of Pilot Protection

6. A Novel Pilot Protection Principle and Verification

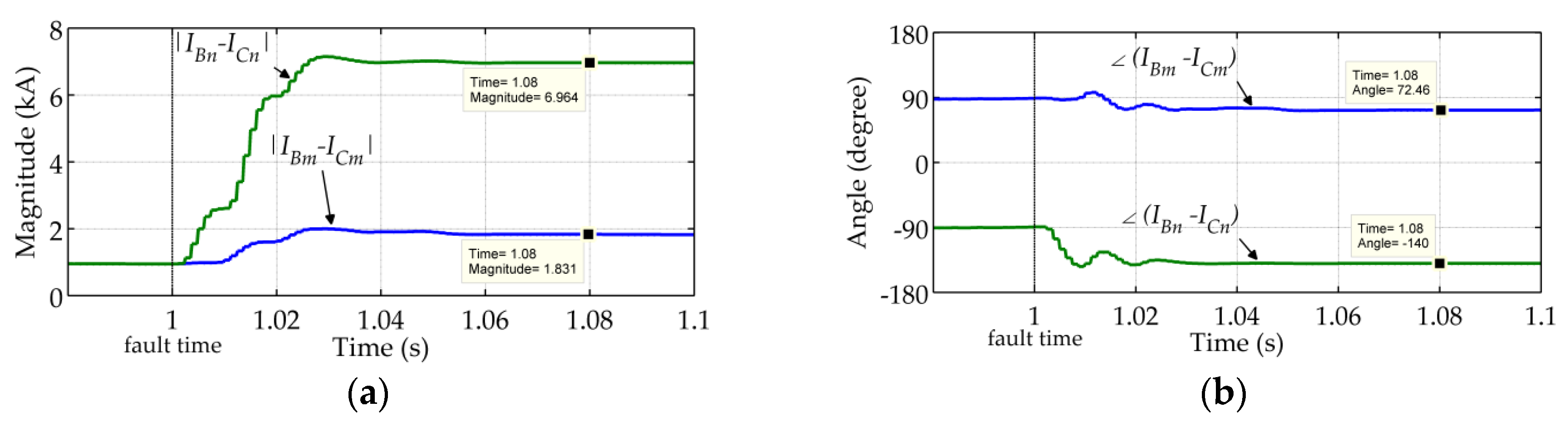

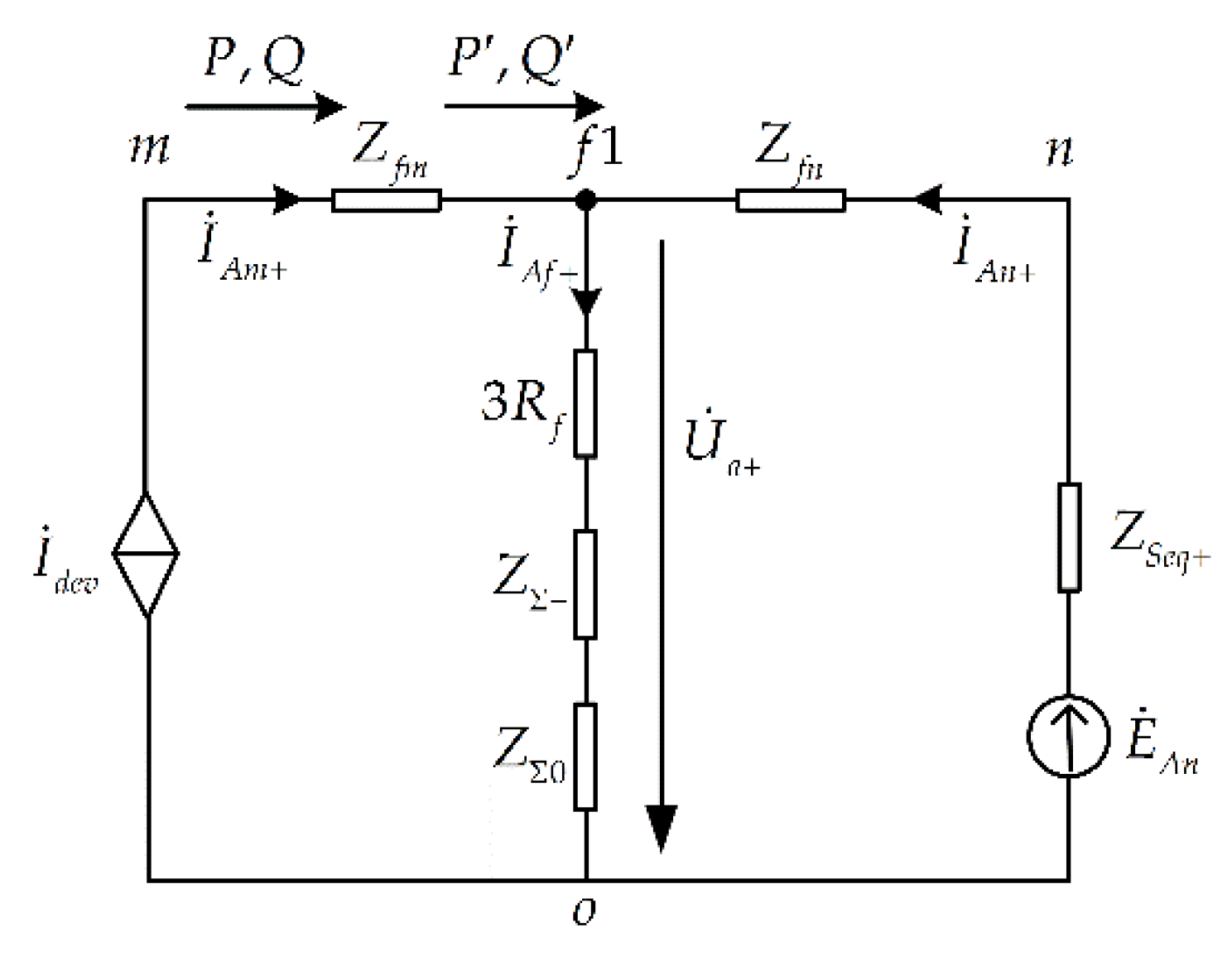

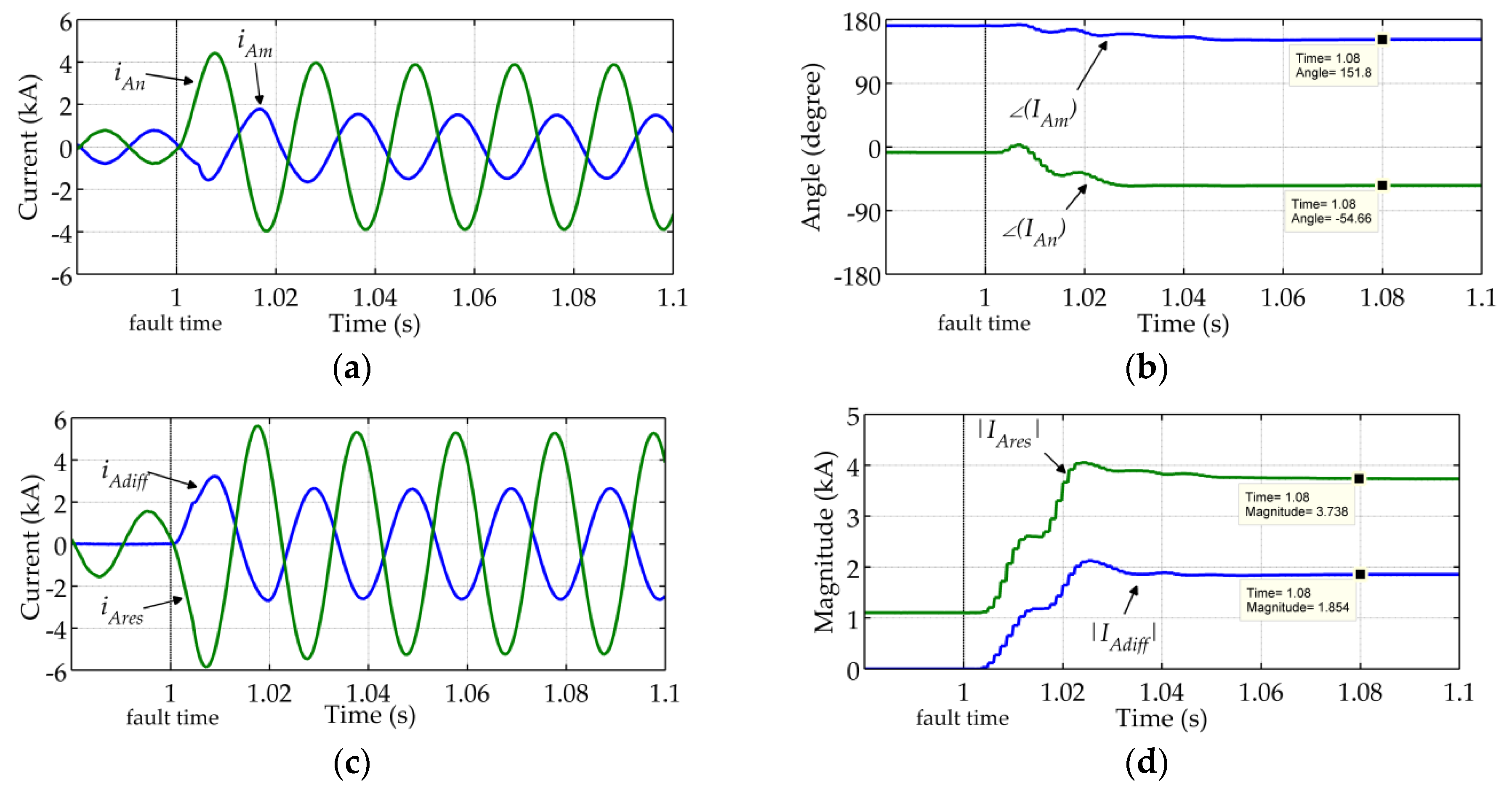

6.1. A Protection Principle Based on the Magnitude Comparison of Currents Flowing through Both Sides of the Line

6.2. Verification

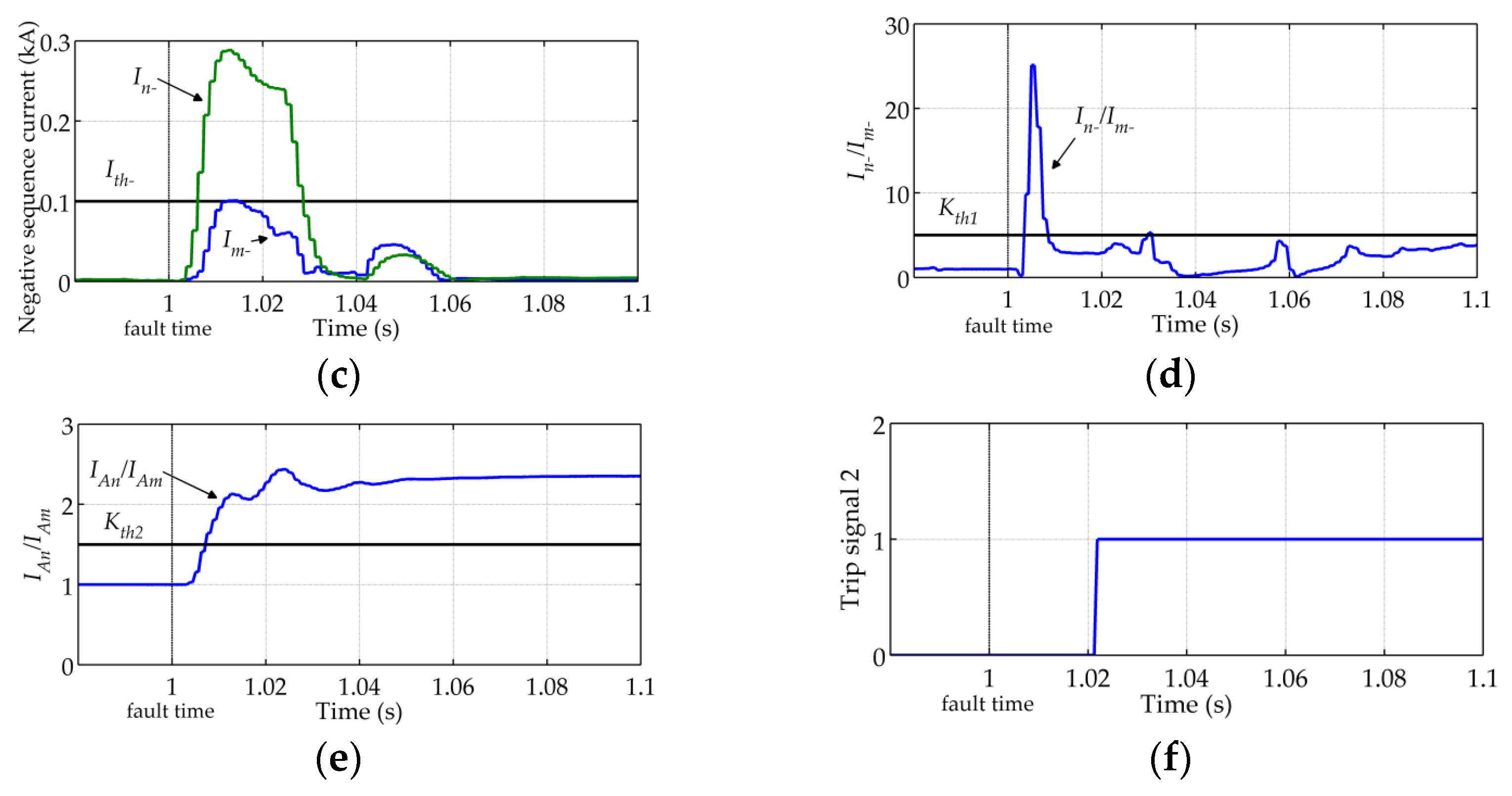

6.2.1. Internal Unbalanced Fault

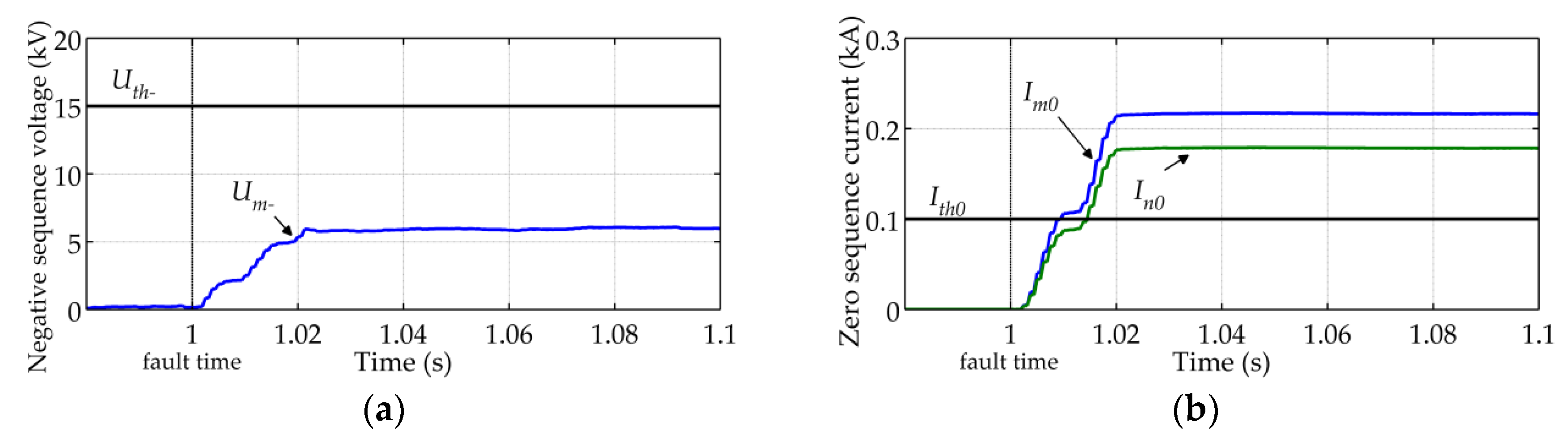

6.2.2. Internal Balanced Fault

6.2.3. External Fault

7. Conclusions

- The output characteristics of the VSC-HVDC interconnector after faults are related to the operation state before the fault, fault location, fault type, fault resistance, etc. The magnitudes of output positive-sequence currents of the interconnector are limited after the fault, and the power factor angle of the interconnector at the fault side is in the range of 0°–360°.

- The fault ride-through (FRT) strategy which is applicable to the VSC-HVDC interconnector operating characteristic of working in all four quadrants of the P-Q operating plane and capable of eliminating negative-sequence currents under unbalanced faults is proposed.

- Theoretical analysis and simulation results show that traditional phase-to-phase distance protection, ground distance protection, and pilot protection are all inapplicable to lines emanating from the interconnector, while these protections are still applicable to AC lines that are not directly emanating from the interconnector. An investigation with a real protection system will be further conducted to confirm the theoretical analysis.

- A novel pilot protection principle based on the ratio between phase currents and the ratio between negative-sequence currents flowing through both sides of the line is proposed for AC lines emanating from the interconnector. Simulation results shows that the proposed protection principle can accurately recognize internal faults and external faults including balanced and unbalanced faults, and has the ability to eliminate the influence of fault resistance.

Acknowledgments

Author Contributions

Conflicts of Interest

Appendix

References

- Ooi, B.T.; Wang, X. Boost-type PWM HVDC transmission system. IEEE Trans. Power Deliv. 1991, 6, 1557–1563. [Google Scholar] [CrossRef]

- Yazdani, A.; Iravani, R. Voltage-Sourced Converters in Power Systems: Modeling, Control, and Applications; Wiley and IEEE Press: Hoboken, NJ, USA, 2010; pp. 1–20. [Google Scholar]

- Flourentzou, N.; Agelidis, V.G.; Demetriades, G.D. VSC-based HVDC power transmission systems: An overview. IEEE Trans. Power Electron. 2009, 24, 592–602. [Google Scholar] [CrossRef]

- Asplund, G. Application of HVDC Light to power system enhancement. In Proceedings of the IEEE Power Engineering Society Winter Meeting, Singapore, 23–27 January 2000; pp. 2498–2503.

- Noroozian, M.; Edris, A.A.; Kidd, D.; Keri, A.J.F. The potential use of voltage-sourced converter-based back-to-back tie in load restorations. IEEE Trans. Power Deliv. 2003, 18, 1416–1421. [Google Scholar] [CrossRef]

- Zhang, R.; Zhao, C. Prony analysis of electrical transient characteristics of AC system during HVDC commutation failure. In Proceedings of the IPEC, Singapore, 27–29 October 2010; pp. 807–812.

- Huang, S.; Shen, H.; Fei, B.; Li, O. Effect of commutation failure on the distance protection and the countermeasures. IET Gener. Transm. Distrib. 2015, 9, 838–844. [Google Scholar] [CrossRef]

- Zhang, P.; Li, H.; Wang, G.; Zhu, G. The impact of HVDC commutation failure on the distance protection. In Proceedings of the Power and Energy Engineering Conference (APPEEC), Chengdu, China, 28–31 March 2010; pp. 1–4.

- Liu, Q.; Cai, Z.; Huang, M.; Liu, Z.; Li, Y.; Li, X.; Zhu, L. Influence of HVDC commutation failure on directional comparison pilot protection of AC system. In Proceedings of the Third International Conference on Electric Utility Deregulation and Restructuring and Power Technologies (DRPT), Nanjing, China, 6–9 April 2008; pp. 1943–1948.

- Shen, H.; Huang, S.; Fei, B. Transient characteristic of HVDC system during commutation failure, its effect on differential protection and countermeasures. Electr. Power Autom. Equip. 2015, 35, 109–114. (In Chinese) [Google Scholar]

- Abbas, A.M.; Lehn, P.W. PWM based VSC-HVDC systems—A review. In Proceedings of the Power & Energy Society (PES) General Meeting, Calgary, AB, Canada, 26–30 July 2009; pp. 1–9.

- Hooshyar, A.; Azzouz, M.A.; El-Saadany, E.F. Distance protection of lines emanating from full-scale converter-interfaced renewable energy power plants-part I: Problem statement. IEEE Trans. Power Deliv. 2015, 30, 1770–1780. [Google Scholar] [CrossRef]

- Hooshyar, A.; Azzouz, M.A.; El-Saadany, E.F. Distance protection of lines emanating from full-scale converter-interfaced renewable energy power plants-part II: Solution description and evaluation. IEEE Trans. Power Deliv. 2015, 30, 1781–1791. [Google Scholar] [CrossRef]

- Lesnicar, A.; Marquardt, R. An innovative modular multilevel converter topology suitable for a wide power range. In Proceedings of the IEEE Power Tech Conference, Bologna, Italy, 23–26 June 2003.

- Song, H.S.; Nam, K. Dual current control scheme for PWM converter under unbalanced input voltage conditions. IEEE Trans. Ind. Electron. 1999, 46, 953–959. [Google Scholar] [CrossRef]

- Zhang, G.; Xu, Z. A new real-time negative and positive sequence components detecting method based on space vector. In Proceedings of the IEEE Power Engineering Society Winter Meeting, Columbus, OH, USA, 28 January–1 February 2001; pp. 275–280.

- Lee, S.J.; Kang, J.K.; Sul, S.K. A new phase detecting method for power conversion systems considering distorted conditions in power system. In Proceedings of the IEEE Industry Applications Conference: Thirty-Fourth IAS Annual Meeting, Phoenix, AZ, USA, 3–7 October 1999; pp. 2167–2172.

- Zhao, X.; Li, G.; Zhao, C. Research on submodule capacitance voltage balancing of MMC based on carrier phase shifted SPWM technique. In Proceedings of the China International Conference on Electricity Distribution (CICED), Nanjing, China, 13–16 September 2010; pp. 1–6.

- Saeedifard, M.; Iravani, R. Dynamic performance of a modular multilevel back-to-back HVDC system. IEEE Trans. Power Deliv. 2010, 25, 2903–2912. [Google Scholar] [CrossRef]

- Guan, M.; Xu, Z. Modeling and control of a modular multilevel converter-based HVDC system under unbalanced grid conditions. IEEE Trans. Power Electron. 2012, 27, 4858–4867. [Google Scholar] [CrossRef]

- Ren, J.; Zhao, J.; Yu, D.; Li, K.; Niu, L.; Liang, Y. Mode switching control strategy for VSC-HVDC transmission system. Autom. Electr. Power Syst. 2012, 36, 69–73. (In Chinese) [Google Scholar]

- IEEE PES Power System Relaying and Control Committee. Available online: http://www.pes-psrc.org/Reports/D4_Application_of_Overreaching_Distance%20_Relays.pdf (accessed on 4 April 2016).

- Horowitz, S.H.; Phadke, A.G. Power System Relaying, 3rd ed.; Wiley and Research Studies Press: Chichester, UK, 2008; pp. 101–129. [Google Scholar]

- Altuve, H.; Benmouyal, G.; Roberts, J.; Tziouvaras, D.A. Transmission line differential protection with an enhanced characteristic. In Proceedings of the Eighth IEE International Conference on Developments in Power System Protection, Amsterdam, The Netherlands, 5–8 April 2004; pp. 414–419.

- Phadke, A.G.; Thorp, J.S. Computer Relaying for Power Systems, 2nd ed.; Wiley and Research Studies Press: Chichester, UK, 2009; pp. 55–108. [Google Scholar]

| Parameter | Positive-Sequence | Zero-Sequence |

|---|---|---|

| R/(Ω/km) | 0.105 | 0.315 |

| L/(mH/km) | 1.258 | 3.774 |

© 2016 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC-BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Xue, S.; Yang, J.; Chen, Y.; Wang, C.; Shi, Z.; Cui, M.; Li, B. The Applicability of Traditional Protection Methods to Lines Emanating from VSC-HVDC Interconnectors and a Novel Protection Principle. Energies 2016, 9, 400. https://doi.org/10.3390/en9060400

Xue S, Yang J, Chen Y, Wang C, Shi Z, Cui M, Li B. The Applicability of Traditional Protection Methods to Lines Emanating from VSC-HVDC Interconnectors and a Novel Protection Principle. Energies. 2016; 9(6):400. https://doi.org/10.3390/en9060400

Chicago/Turabian StyleXue, Shimin, Jingyue Yang, Yanxia Chen, Cunping Wang, Zhe Shi, Miao Cui, and Botong Li. 2016. "The Applicability of Traditional Protection Methods to Lines Emanating from VSC-HVDC Interconnectors and a Novel Protection Principle" Energies 9, no. 6: 400. https://doi.org/10.3390/en9060400

APA StyleXue, S., Yang, J., Chen, Y., Wang, C., Shi, Z., Cui, M., & Li, B. (2016). The Applicability of Traditional Protection Methods to Lines Emanating from VSC-HVDC Interconnectors and a Novel Protection Principle. Energies, 9(6), 400. https://doi.org/10.3390/en9060400