Single DC-Sourced 9-level DC/AC Topology as Transformerless Power Interface for Renewable Sources

Abstract

:1. Introduction

| Publications | Year | No. Levels | No. Transformers | No. IGBTs | No. Capacitors | No. Inductors | No. Diodes |

|---|---|---|---|---|---|---|---|

| Proposed Topology | 2014 | 9 | 0 | 12 | 2 | 2 | 4 |

| [6] | 2014 | 9 | 0 | 11 | 3 | 1 | 4 |

| [7] | 2014 | 7 | 0 | 10 | 4 | 1 | 0 |

| [8] | 2014 | 7 | 1 | 8 | 3 | 2 | 5 |

| [9] | 2013 | 5 | 0 | 8 | 1 | 0 | 0 |

| [10] | 2012 | 5 | 0 | 8 | 2 | 0 | 0 |

| [11] | 2011 | 7 | 0 | 7 | 4 | 1 | 10 |

| [12] | 2011 | 7 | 0 | 14 | 3 | 1 | 11 |

| [13] | 2009 | 5 | 0 | 8 | 1 | 0 | 0 |

| [14] | 2009 | 7 | 0 | 8 | 1 | 0 | 0 |

| [15] | 2009 | 9 | 4 | 9 | 0 | 0 | 0 |

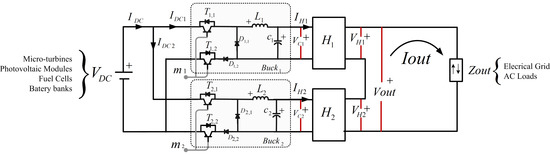

2. Operation Principle of Proposed Converter

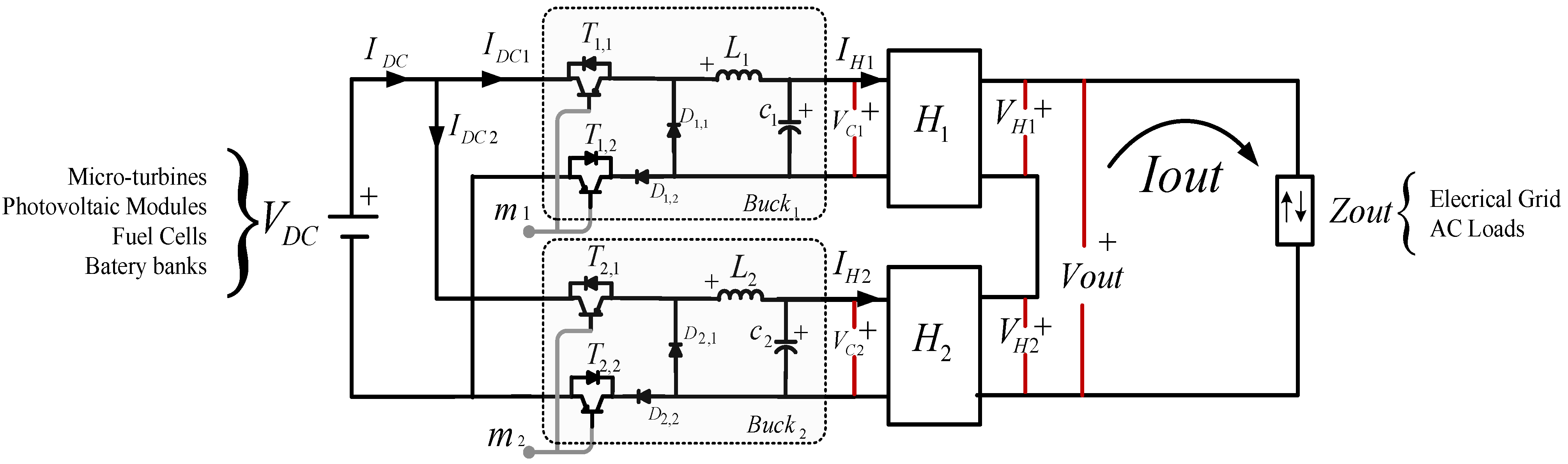

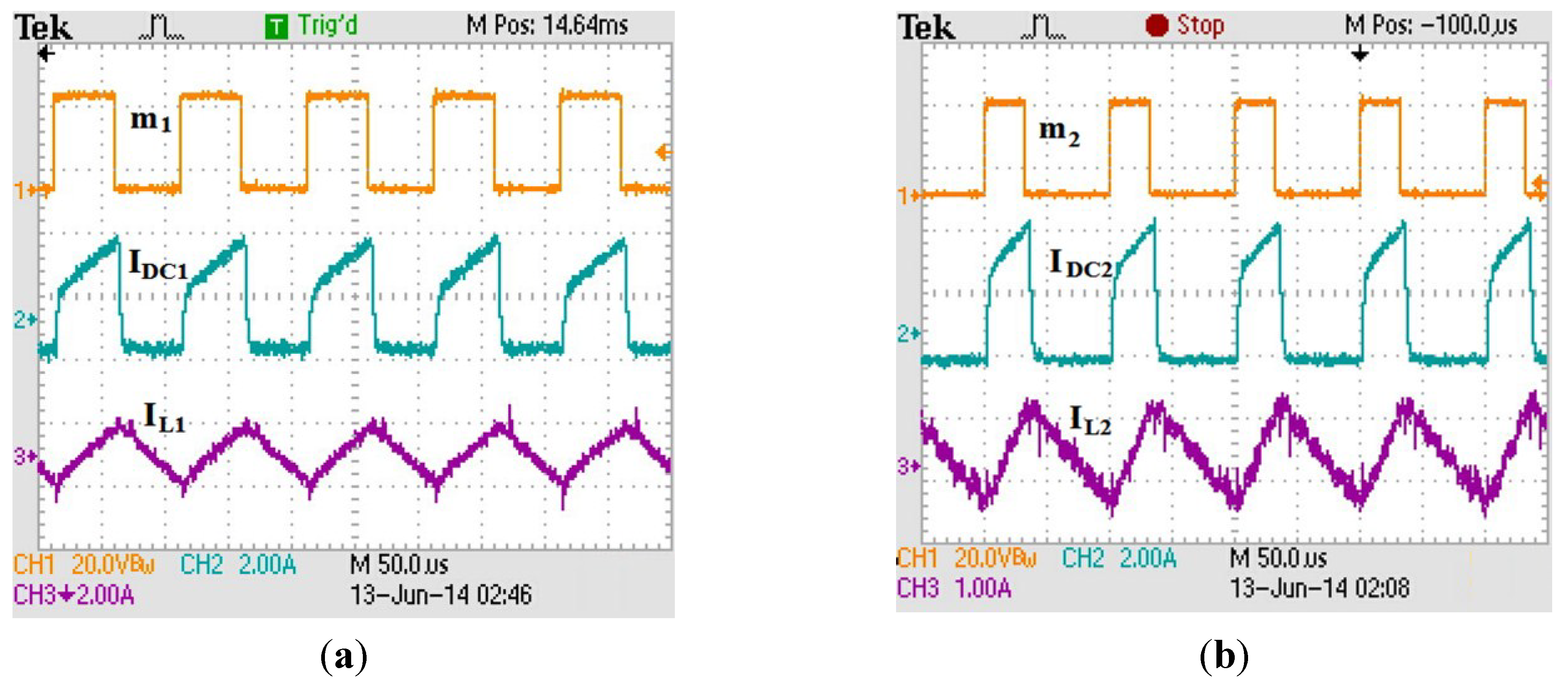

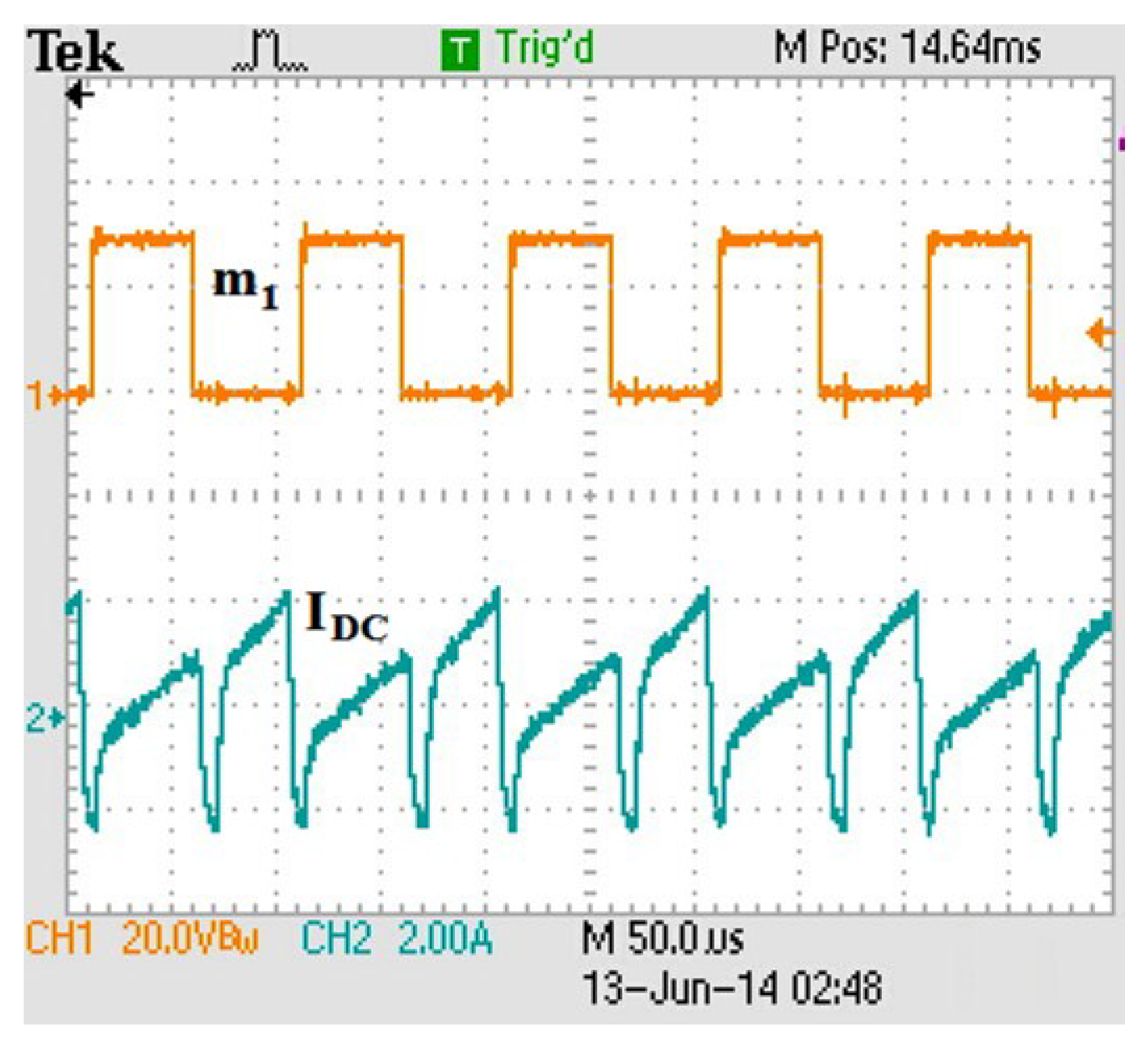

2.1. Isolated Bucks Converters

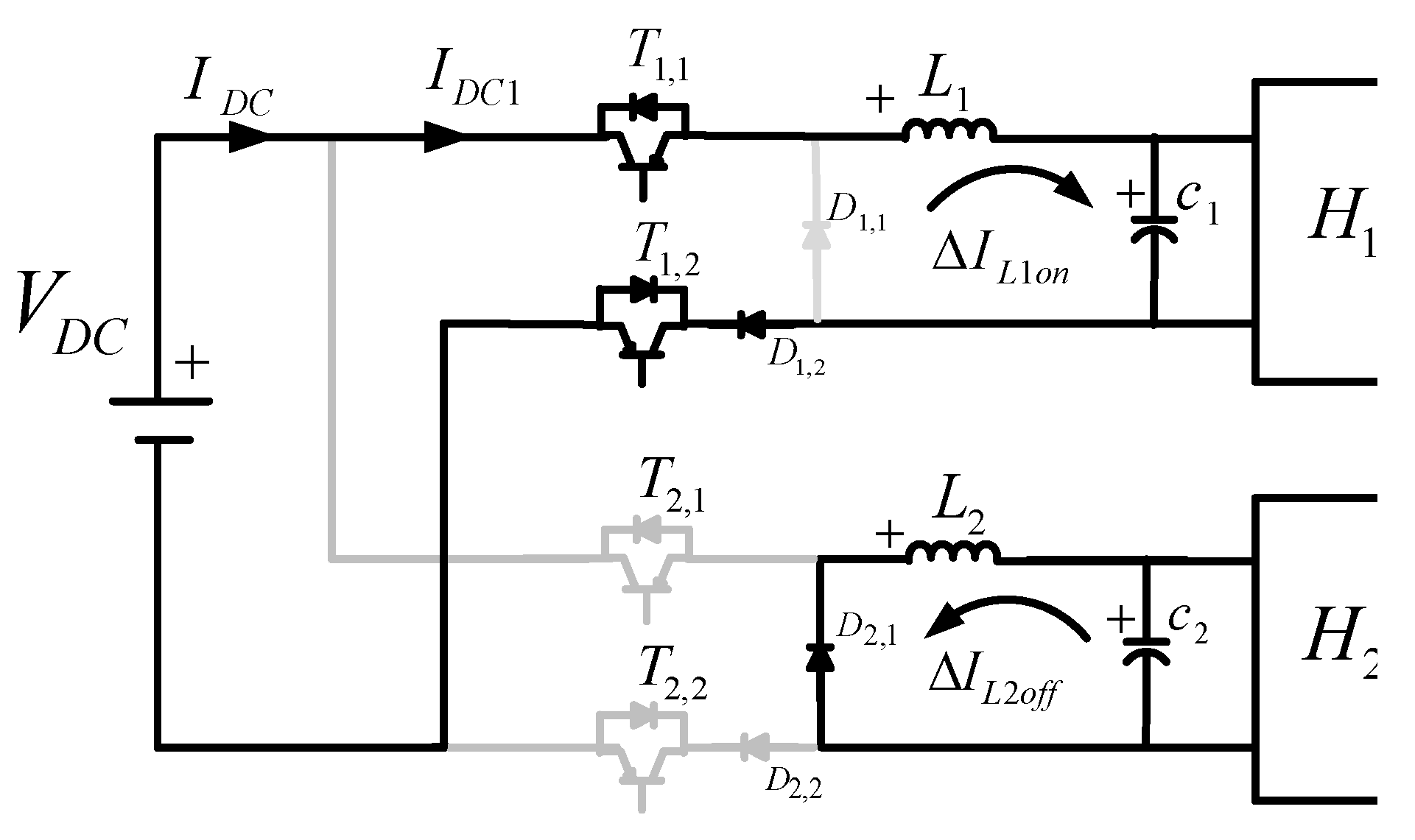

| Topological State | m1 | m2 | IL1 | IL2 | ID1,1 | ID1,2 | ID2,1 | ID2,2 | IDC |

|---|---|---|---|---|---|---|---|---|---|

| (i) | 0 | 0 | ΔIL1off | ΔIL2off | ΔIL1off | 0 | ΔIL2off | 0 | 0 |

| (ii) | 1 | 0 | ΔIL1on | ΔIL2off | 0 | ΔIL1on | ΔIL2off | 0 | ΔIL1on |

| (iii) | 0 | 1 | ΔIL1off | ΔIL2on | ΔIL2off | 0 | 0 | ΔIL2on | ΔIL2on |

| 1 | 1 | Prohibited | |||||||

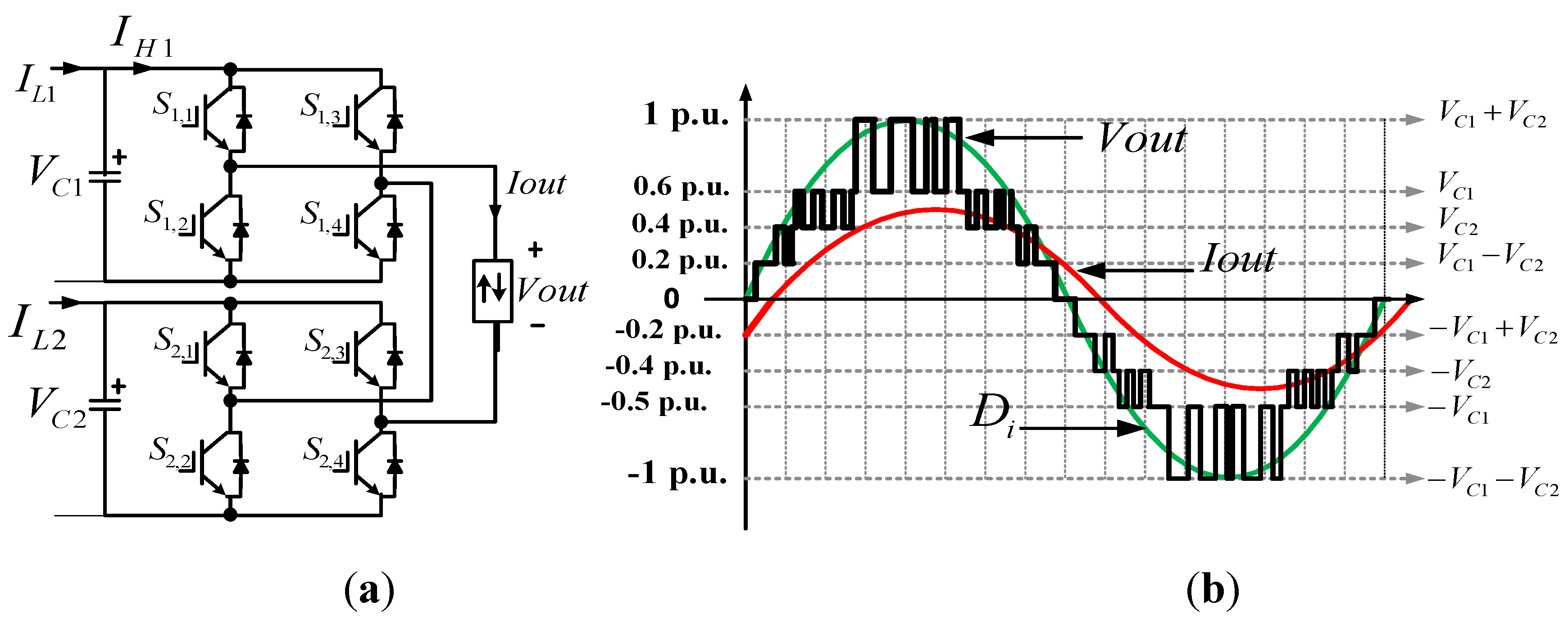

2.2. DC/AC Nine Levels Cascaded Cell Topology

| Vout Level | H1 | H2 | ||||||

|---|---|---|---|---|---|---|---|---|

| S1,1 | S1,2 | S1,3 | S1,4 | S2,1 | S2,2 | S2,3 | S2,4 | |

| VC1 + VC2 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 |

| VC1 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 |

| VC2 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 |

| VC1 − VC2 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 |

| −VC1 + VC2 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 |

| −VC2 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 0 |

| −VC1 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 |

| −VC1 − VC2 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 |

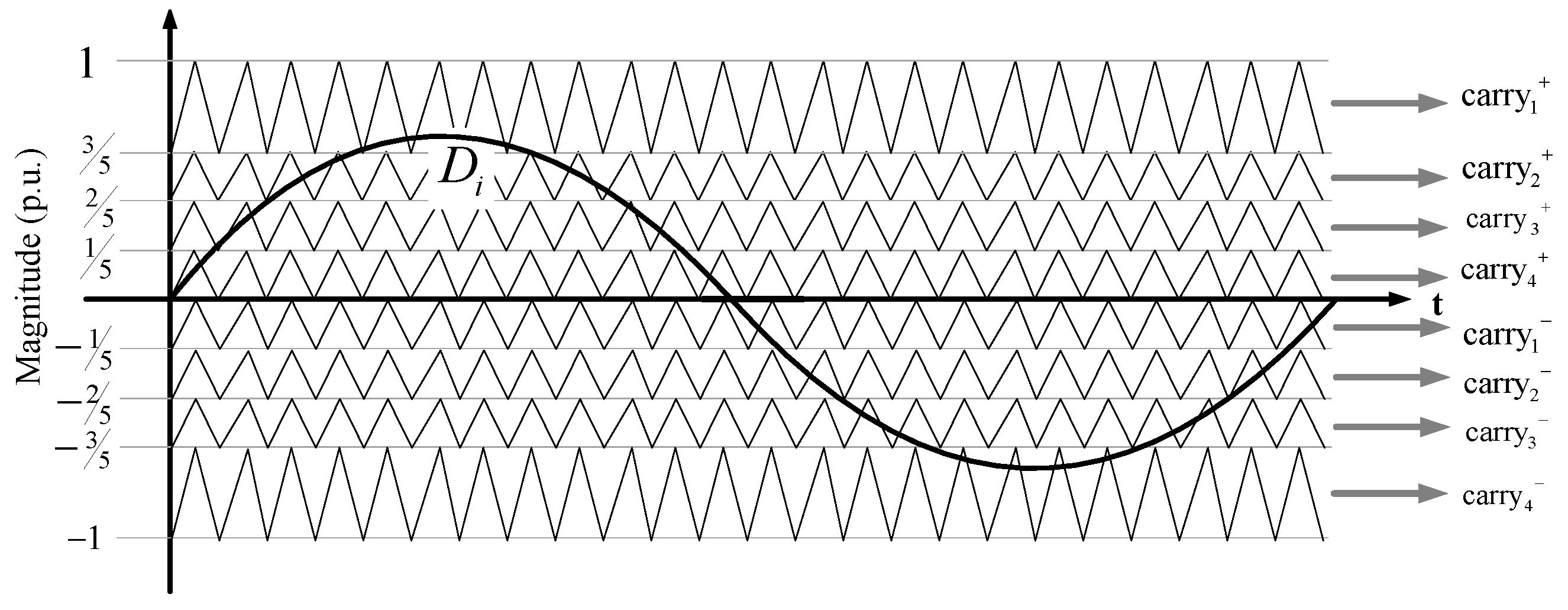

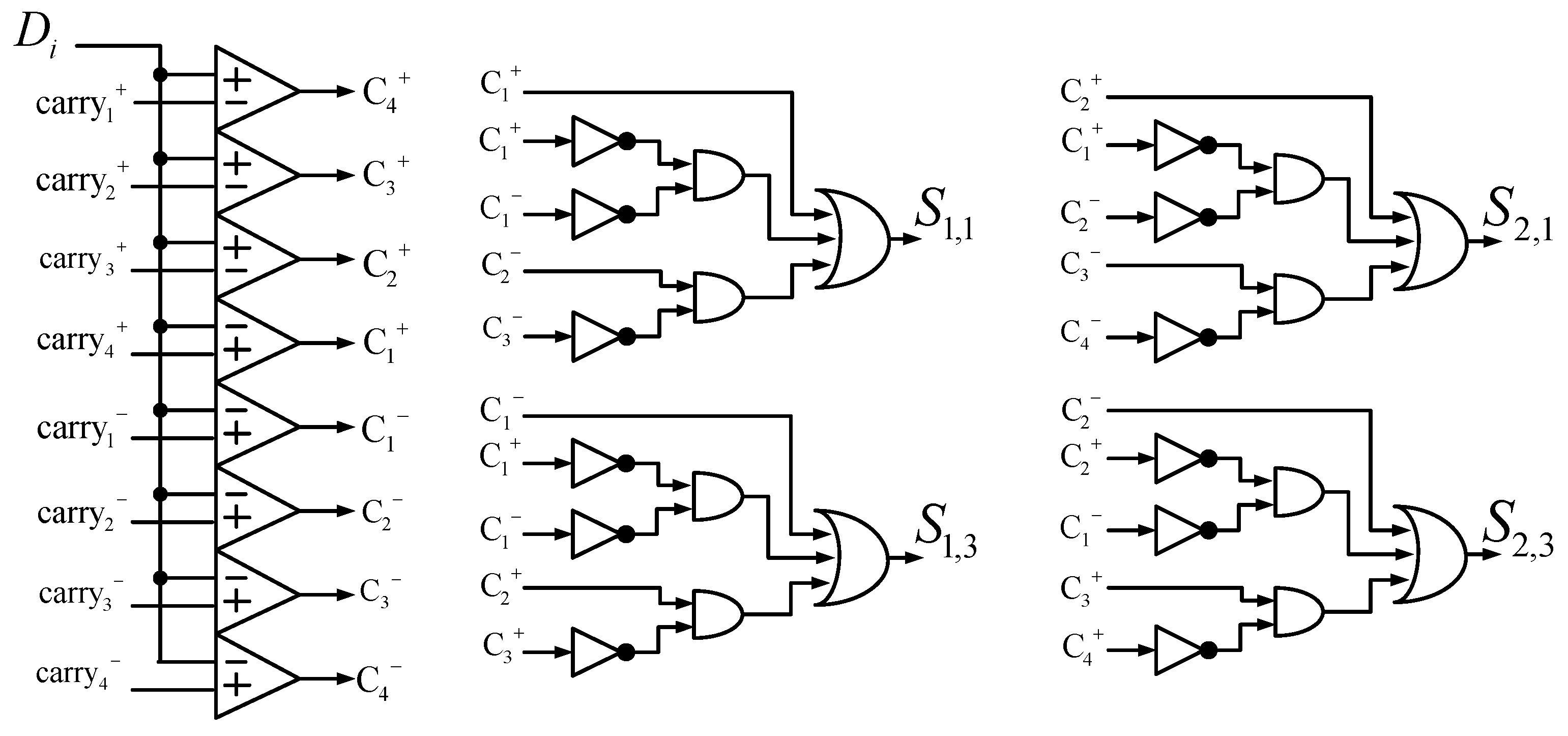

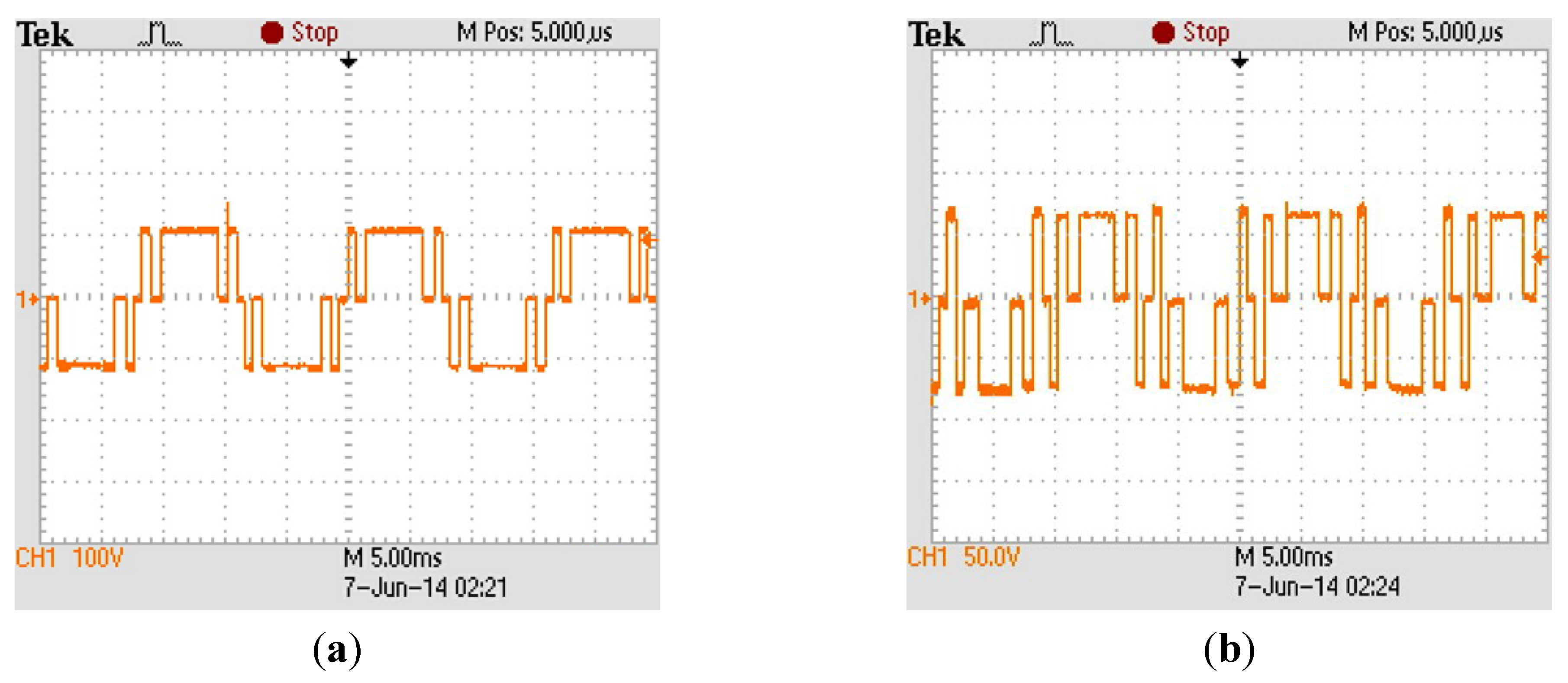

2.3. Nine-Level SPWM Modulation

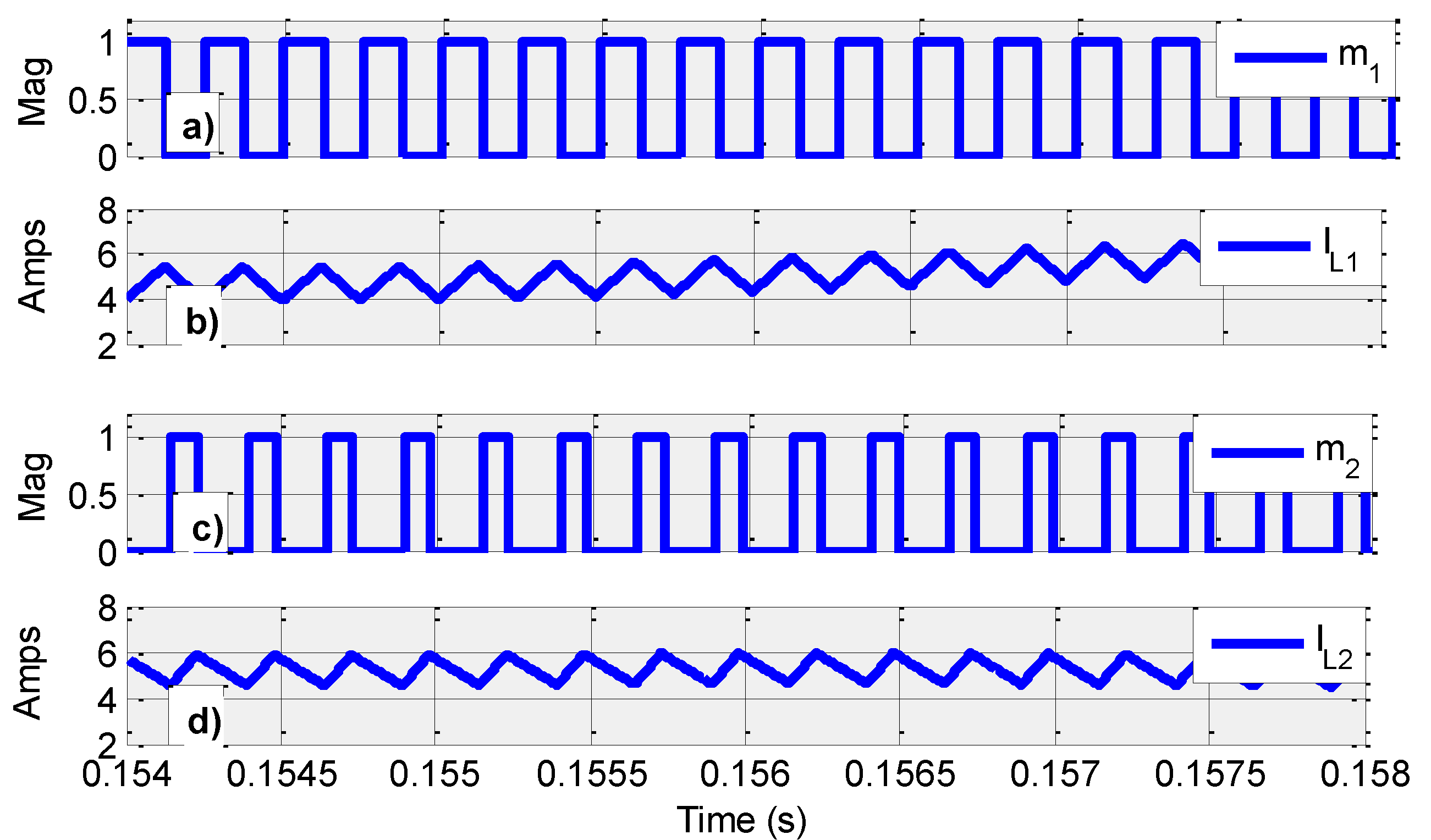

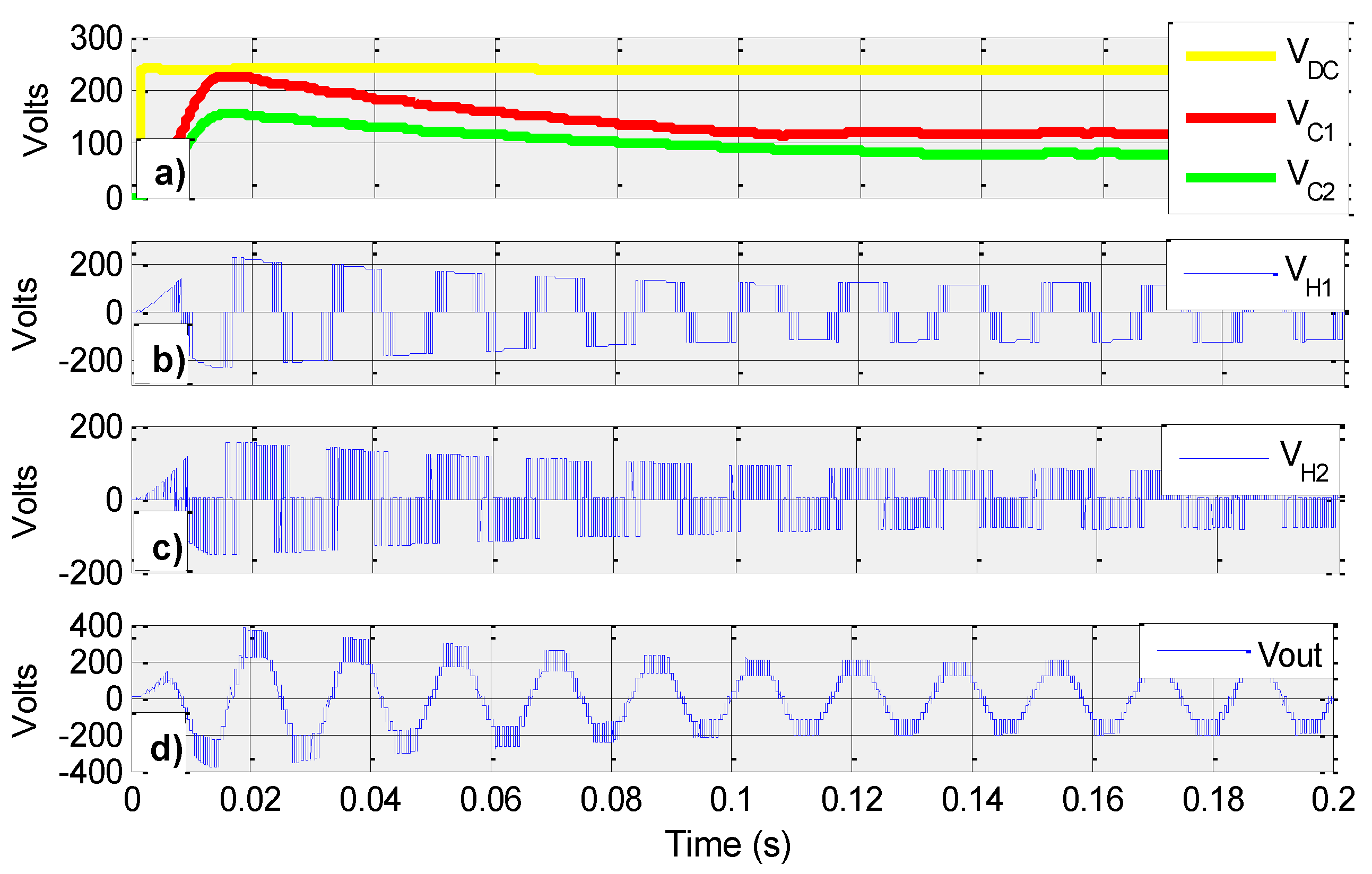

3. Simulation

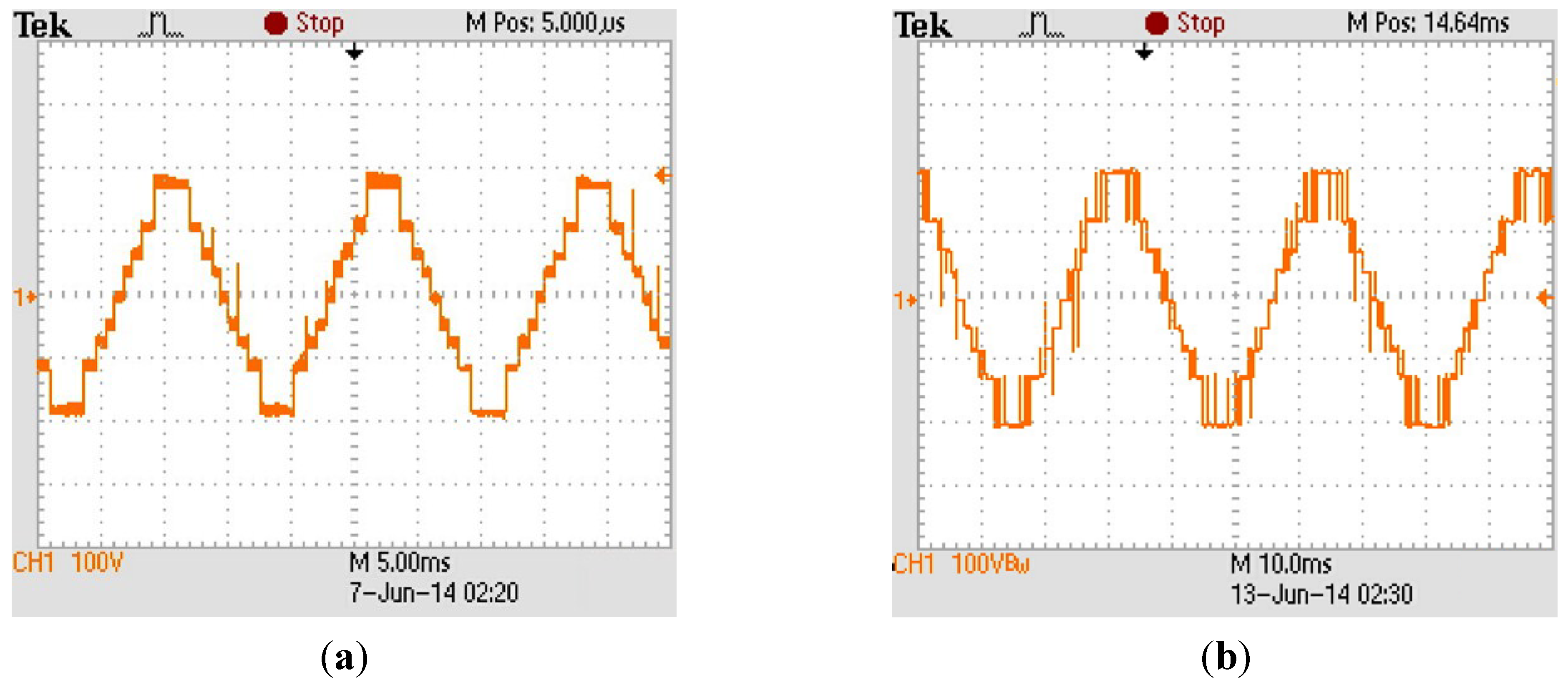

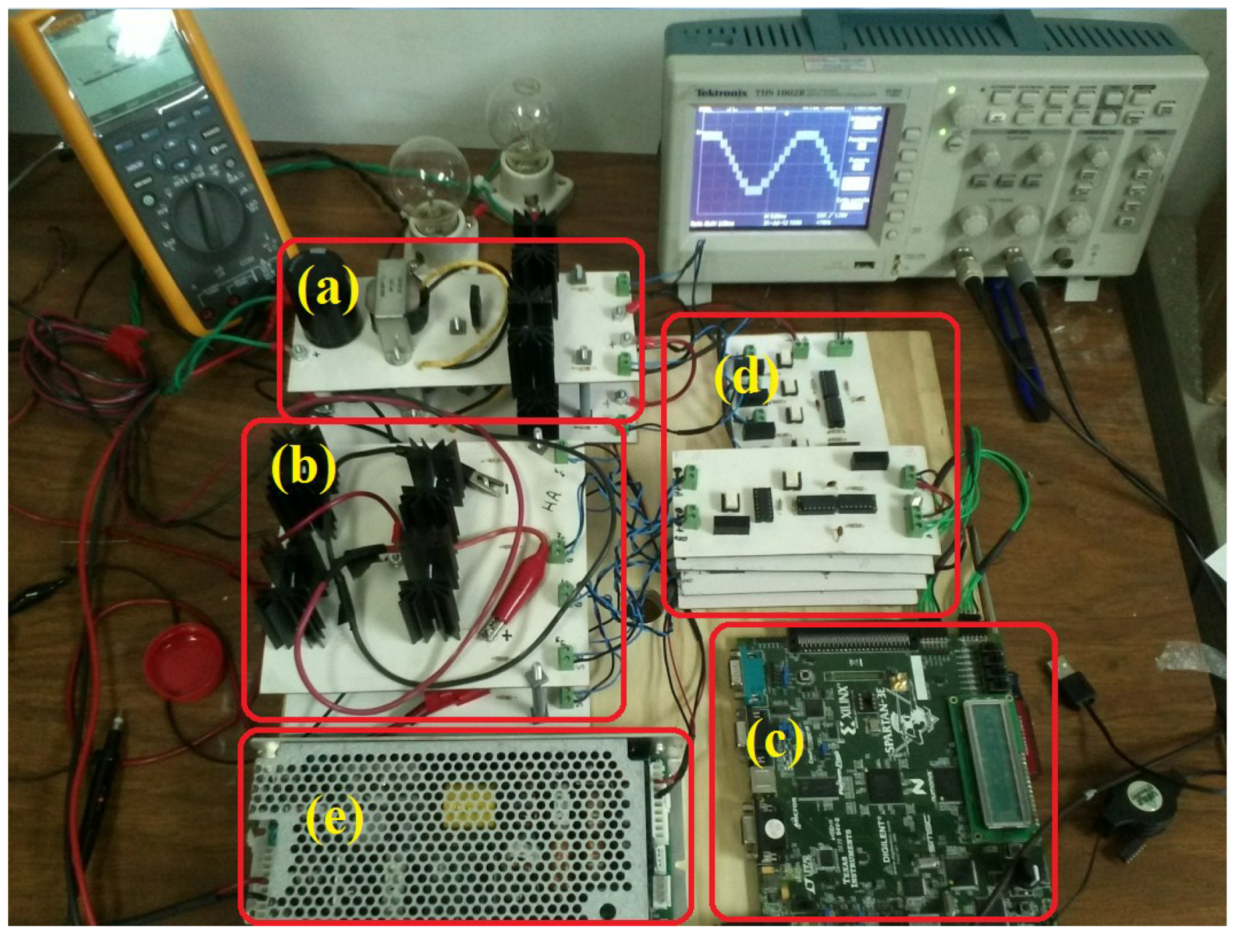

4. Experimental Test

| Variable, Element | Value |

|---|---|

| Bucks Switching Frequency | 16 kHz |

| Multilevel Modulation Frequency | 6 kHz |

| L1= L2 | 6 mH |

| C1 = C2 | 2200 uF |

| VDC | 240 V |

| D1 | 0.5 |

| D2 | 0.33 |

| Di | 0.95∗sin(ωt) |

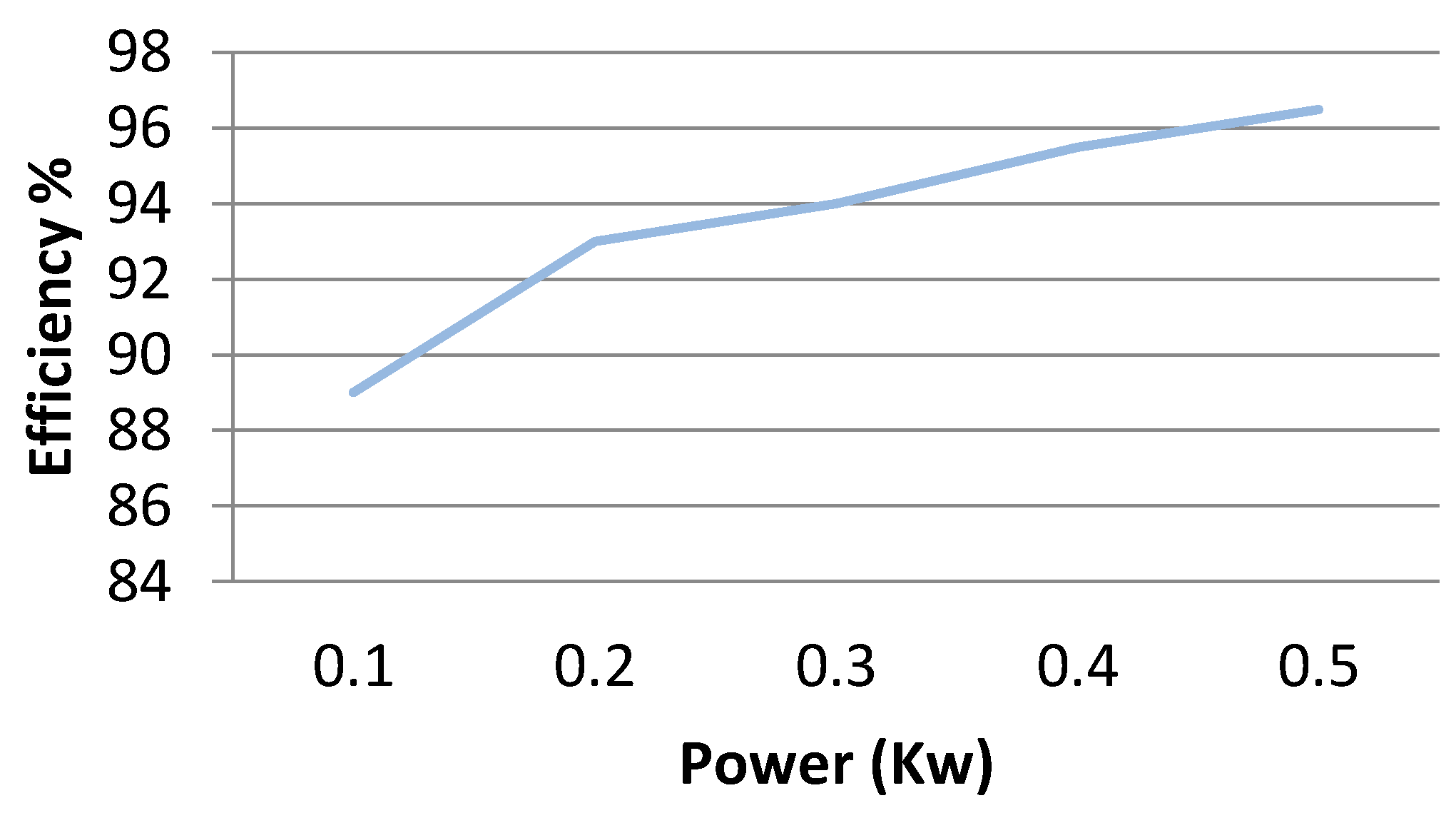

Discussion

| Multilevel Converter | No. IGBTs | No. Capacitors | No. Diodes | No. DC Sources |

|---|---|---|---|---|

| Proposed Topology | 12 | 2 | 6 | 1 |

| Clamped Diode | 16 | 8 | 32 | 1 |

| Flying Capacitor | 16 | 32 | 0 | 1 |

| Cascaded cells | 8 | 0 | 0 | 2 |

5. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Arango, E.; Ramos-Paja, C.A.; Calvente, J.; Giral, R.; Serna, S. Asymmetrical interleaved DC/DC switching converters for photovoltaic and fuel cell applications—Part 1: Circuit generation, analysis and design. Energies 2012, 5, 4590–4623. [Google Scholar] [CrossRef]

- Rodriguez, J.; Lai, J.S.; Peng, F.Z. Multilevel inverters: A survey of topologies, controls, and applications. IEEE Trans. Ind. Electron. 2002, 49, 724–738. [Google Scholar] [CrossRef]

- Tolbert, L.M.; Peng, F.Z. Multilevel converters as a utility interface for renewable energy systems. In Proceedings of the Power Engineering Society Summer Meeting, Seattle, WA, USA, 16–20 July 2000; pp. 1271–1274.

- Walker, G.R.; Sernia, P.C. Cascaded DC–DC converter connection of photovoltaic modules. In Proceedings of the 33rd Annual Power Electronics Specialists Conference, Cairns, Queensland, Australia, 22–27 June 2002; pp. 24–29.

- Gonzalez, R.; Gubia, E.; Lopez, J.; Marroyo, L. Transformerless single-phase multilevel-based photovoltaic inverter. IEEE Trans. Ind. Electron. 2008, 55, 2694–2702. [Google Scholar] [CrossRef]

- Buticchi, G.; Barater, D.; Lorenzani, E.; Concari, C.; Franceschini, G. A nine-level grid-connected converter topology for single-phase transformerless PV systems. IEEE Trans. Ind. Electron. 2014, 61, 3951–3960. [Google Scholar] [CrossRef]

- Tsunoda, A.; Hinago, Y.; Koizumi, H. Level- and phase-shifted PWM for seven-level switched-capacitor inverter using series/parallel conversion. IEEE Trans. Ind. Electron. 2014, 61, 1411–1421. [Google Scholar] [CrossRef]

- Wu, J.C.; Chou, C. A solar power generation system with a seven-level inverter. IEEE Trans. Power Electron. 2014, 29, 3454–3452. [Google Scholar] [CrossRef]

- Sepahvand, H.; Liao, J.; Ferdowsi, M.; Corzine, K.A. Capacitor voltage regulation in single-DC-source cascaded H-bridge multilevel converters using phase-shift modulation. IEEE Trans. Ind. Electron. 2013, 9, 3619–3626. [Google Scholar] [CrossRef]

- Roshankumar, P.; Rajeevan, P.P.; Mathew, K.; Gopakumar, K.; Leon, J.I.; Franquelo, L.G. A five-level inverter topology with single-DC supply by cascading a flying capacitor inverter and an H-bridge. IEEE Tran. Power Electron. 2012, 27, 3505–3512. [Google Scholar] [CrossRef]

- Rahim, N.A.; Chaniago, K.; Selvaraj, J. Single-phase seven-level grid-connected inverter for photovoltaic system. IEEE Trans. Ind. Electron. 2011, 58, 2435–2443. [Google Scholar] [CrossRef]

- Nami, A.; Zare, F.; Ghosh, A.; Blaabjerg, F. A hybrid cascade converter topology with series-connected symmetrical and asymmetrical diode-clamped H-bridge cells. IEEE Trans. Power Electron. 2011, 26, 51–65. [Google Scholar] [CrossRef]

- Vazquez, S.; Leon, J.I.; Franquelo, L.G.; Padilla, J.J.; Carrasco, J.M. DC-voltage-ratio control strategy for multilevel cascaded converters fed with a single DC source. IEEE Trans. Ind. Electron. 2009, 56, 2513–2521. [Google Scholar] [CrossRef]

- Du, Z.; Tolbert, L.M.; Ozpineci, B.; Chiasson, J.N. Fundamental frequency switching strategies of a seven-level hybrid cascaded H-bridge multilevel inverter. IEEE Trans. Power Electron. 2009, 24, 25–33. [Google Scholar] [CrossRef]

- Song, S.G.; Kang, F.S.; Park, S.J. Cascaded multilevel inverter employing three-phase transformers and single DC input. IEEE Trans. Ind. Electron. 2009, 56, 2005–2014. [Google Scholar] [CrossRef]

- Ruiz-Caballero, D.A.; Ramos-Astudillo, R.M.; Mussa, S.A.; Heldwein, M.L. Symmetrical hybrid multilevel DC–AC converters with reduced number of insulated DC supplies. IEEE Trans. Ind. Electron. 2010, 57, 2307–2314. [Google Scholar] [CrossRef]

- Liu, J.; Cheng, K.; Ye, Y. A cascaded multilevel inverter based on switched-capacitor for high-frequency AC power distribution system. IEEE Trans. Power Electron. 2014, 29, 4219–4230. [Google Scholar] [CrossRef]

- Jimenez, O.L.; Vargas, R.A.; Aguayo, J.; Arau, J.E.; Vela, G.; Claudio, A. THD in cascade multilevel inverter symmetric and asymmetric. In Proceedings of the IEEE, Electronics, Robotics and Automotive Mechanics Conference (CERMA), Cuernavaca, Morelos, Mexico, 15–18 November 2011; pp. 289–295.

© 2015 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Rodriguez-Rodríguez, J.R.; Venegas-Rebollar, V.; Moreno-Goytia, E.L. Single DC-Sourced 9-level DC/AC Topology as Transformerless Power Interface for Renewable Sources. Energies 2015, 8, 1273-1290. https://doi.org/10.3390/en8021273

Rodriguez-Rodríguez JR, Venegas-Rebollar V, Moreno-Goytia EL. Single DC-Sourced 9-level DC/AC Topology as Transformerless Power Interface for Renewable Sources. Energies. 2015; 8(2):1273-1290. https://doi.org/10.3390/en8021273

Chicago/Turabian StyleRodriguez-Rodríguez, Juan R., Vicente Venegas-Rebollar, and Edgar L. Moreno-Goytia. 2015. "Single DC-Sourced 9-level DC/AC Topology as Transformerless Power Interface for Renewable Sources" Energies 8, no. 2: 1273-1290. https://doi.org/10.3390/en8021273

APA StyleRodriguez-Rodríguez, J. R., Venegas-Rebollar, V., & Moreno-Goytia, E. L. (2015). Single DC-Sourced 9-level DC/AC Topology as Transformerless Power Interface for Renewable Sources. Energies, 8(2), 1273-1290. https://doi.org/10.3390/en8021273