13-Level Single-Source Switched-Capacitor Boost Multilevel Inverter

Abstract

1. Introduction

2. The Proposed SSCBMLI

2.1. Extensibility of Structure

2.2. Operation, Switching, and Capacitor States

3. Simulation of the Proposed SSCBMLI Topology

3.1. Simulation Specifications

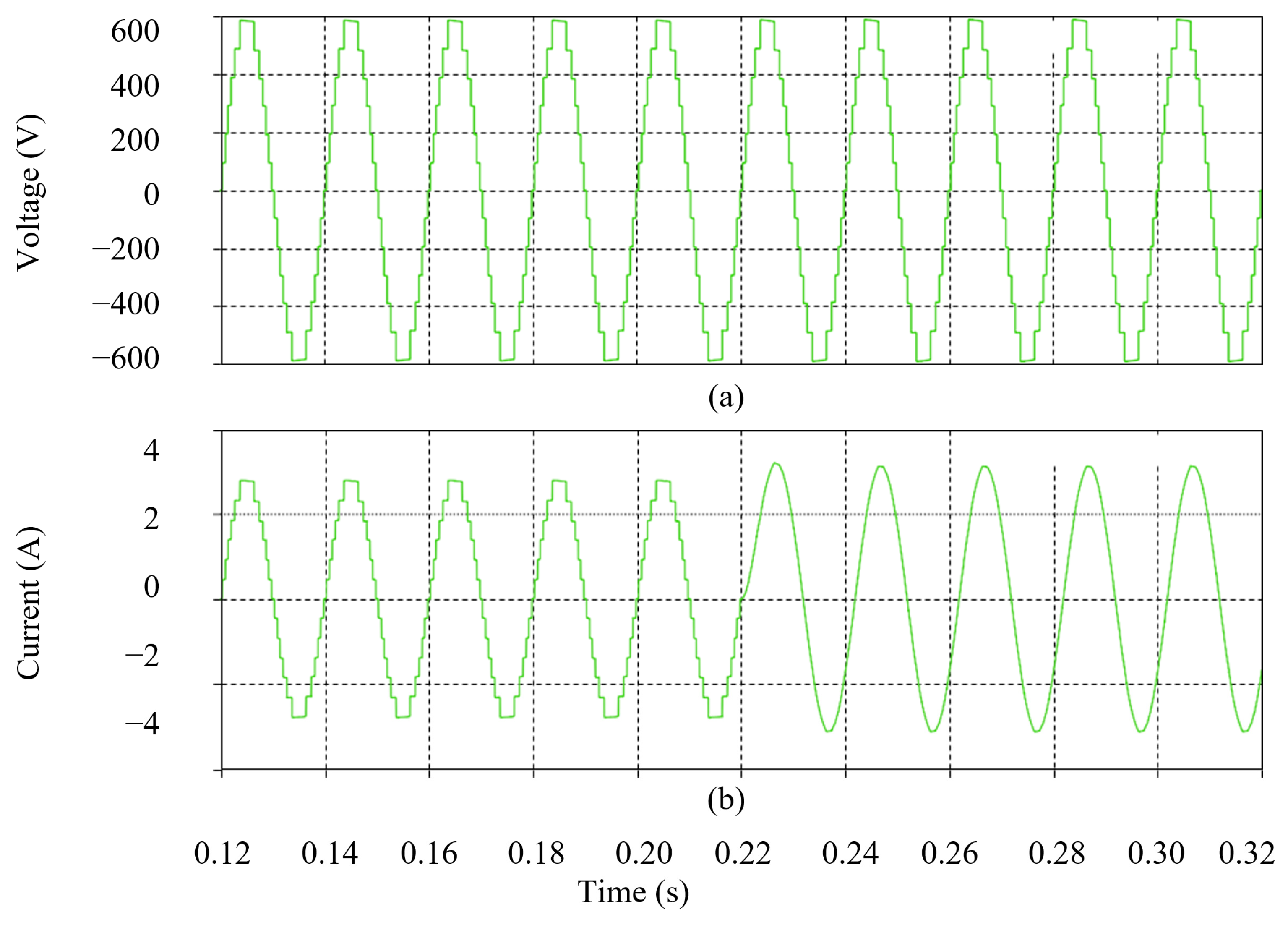

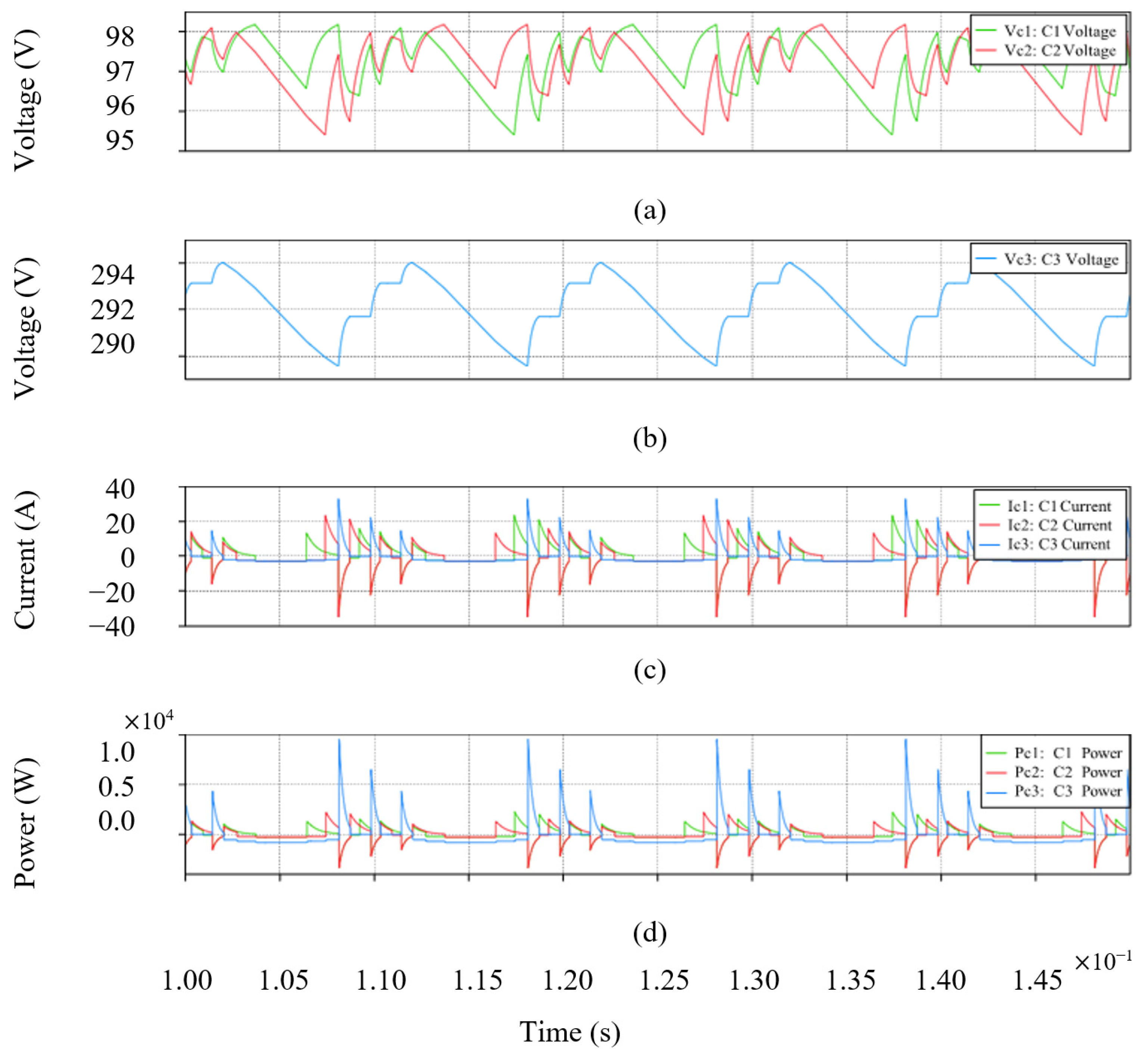

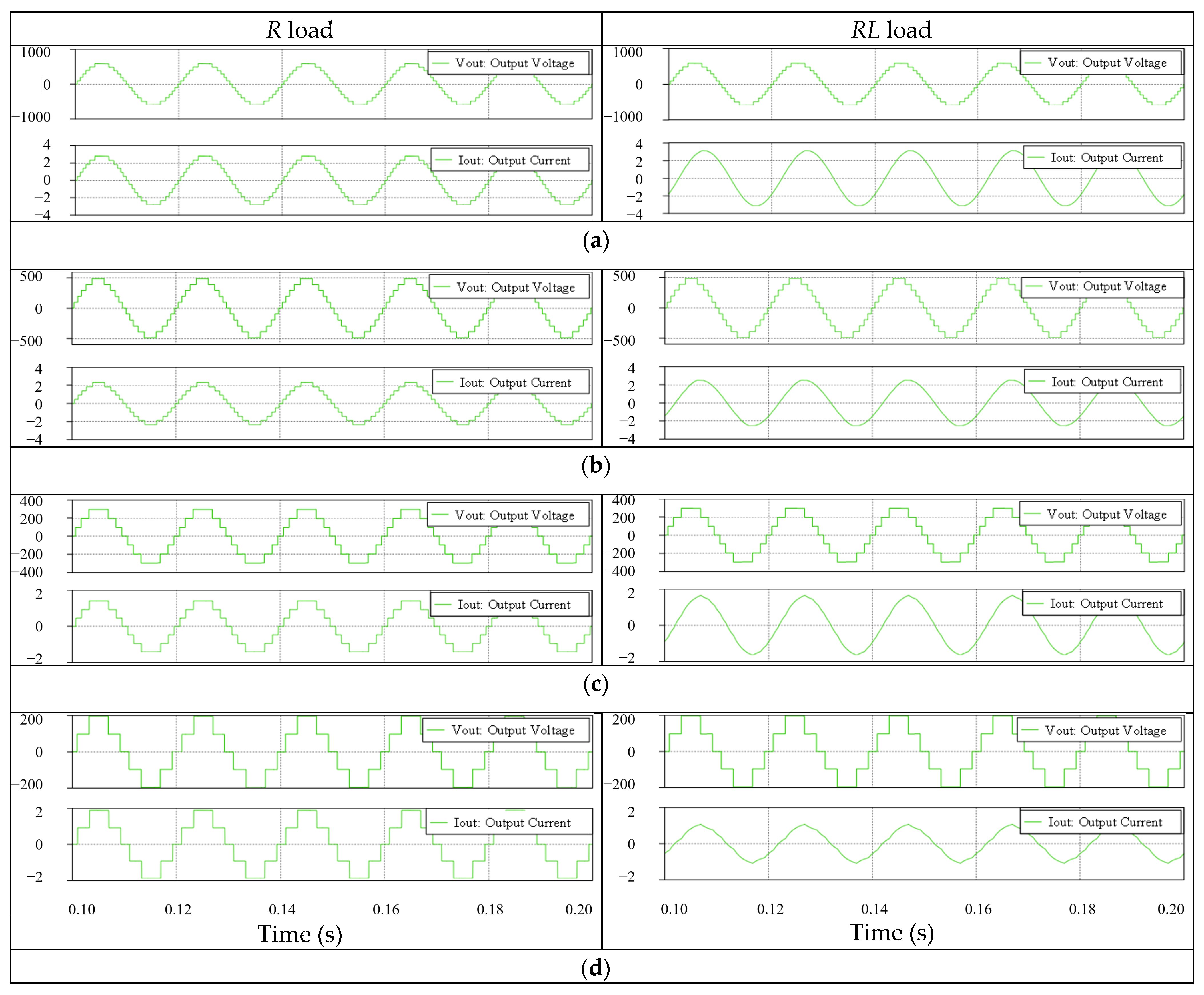

3.2. Simulation Performance Verification

3.3. Total Harmonic Distortion (THD) vs. Modulation Index (MI)

3.4. Efficiency and Power Loss Analysis

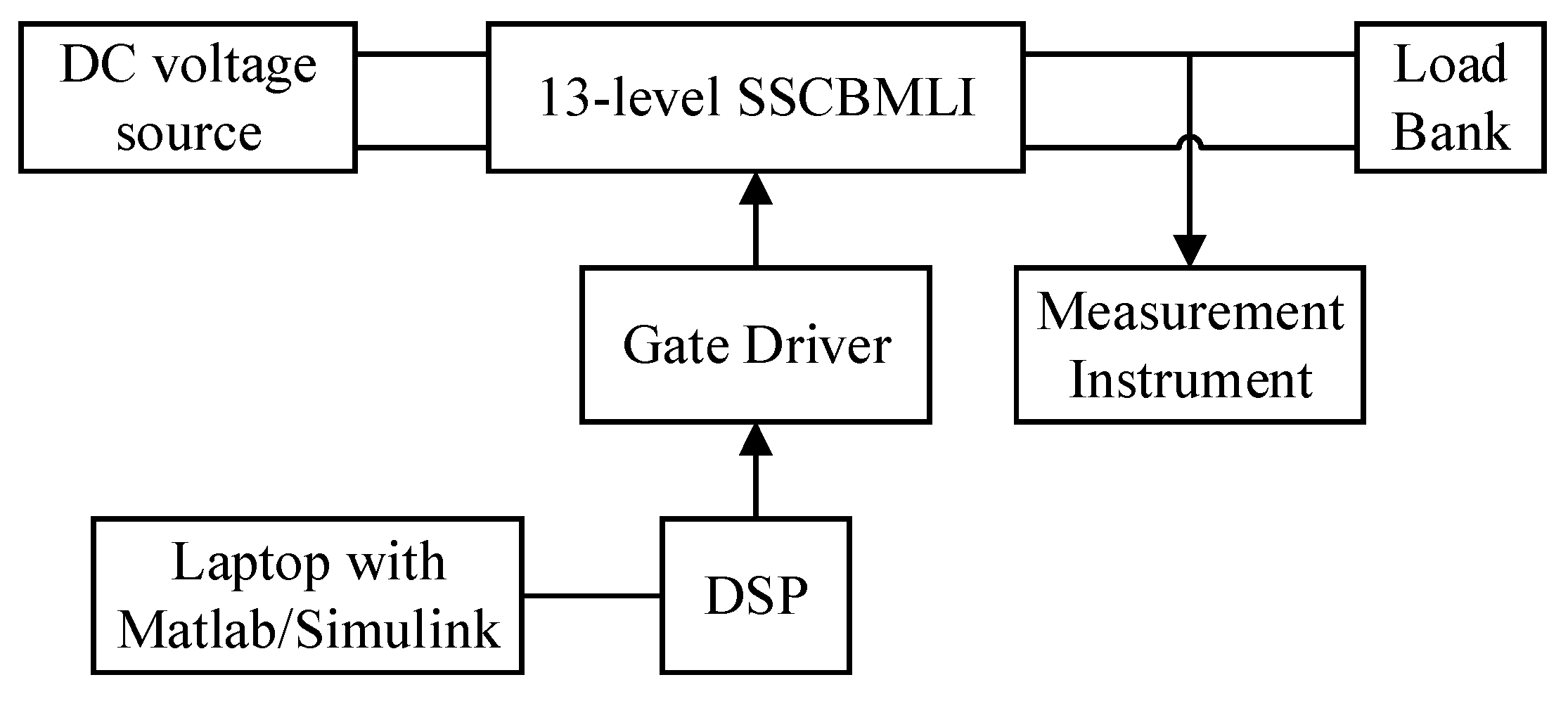

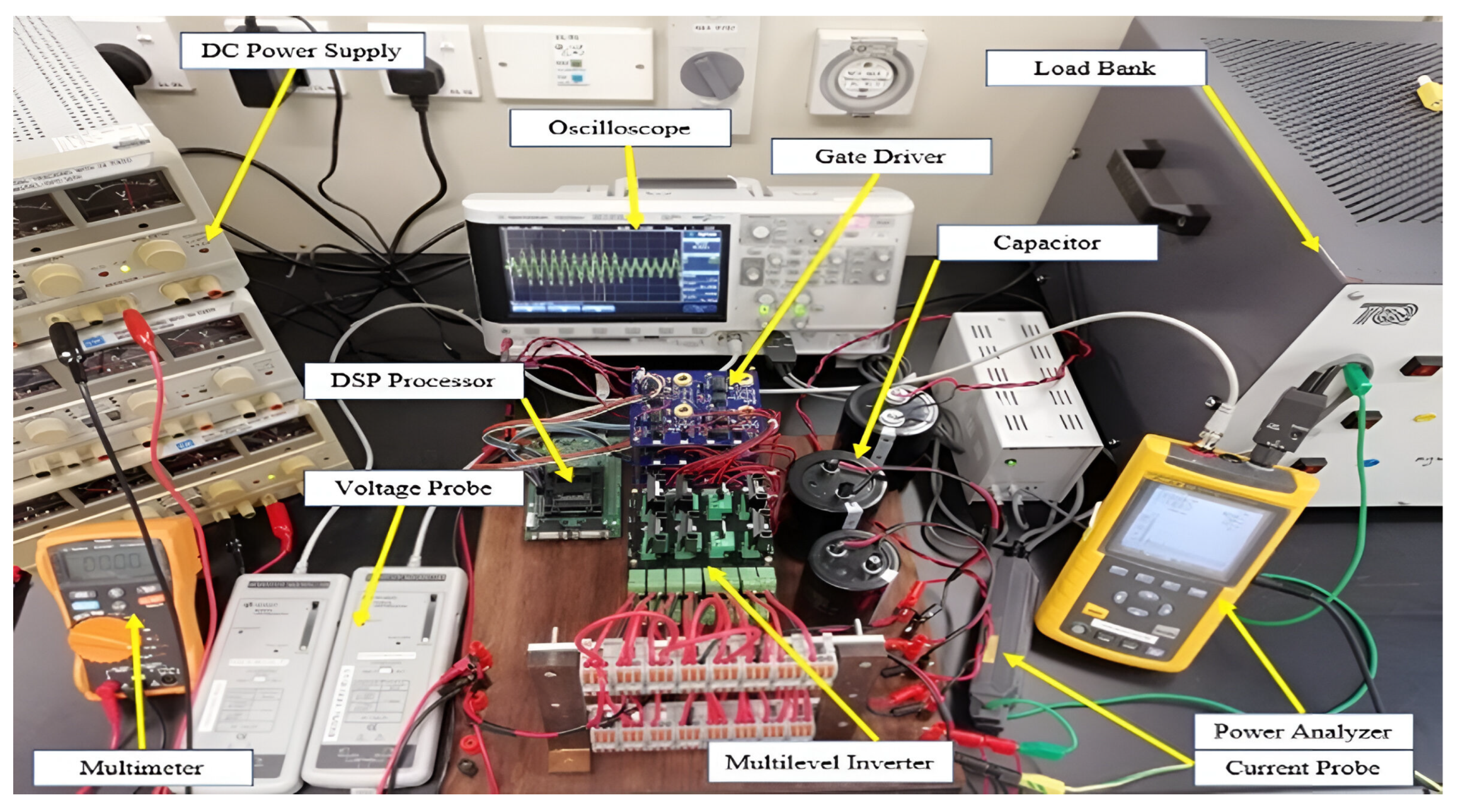

4. Experiment of the Proposed SSCBMLI Topology

4.1. Experiment and Hardware Setup Specifications

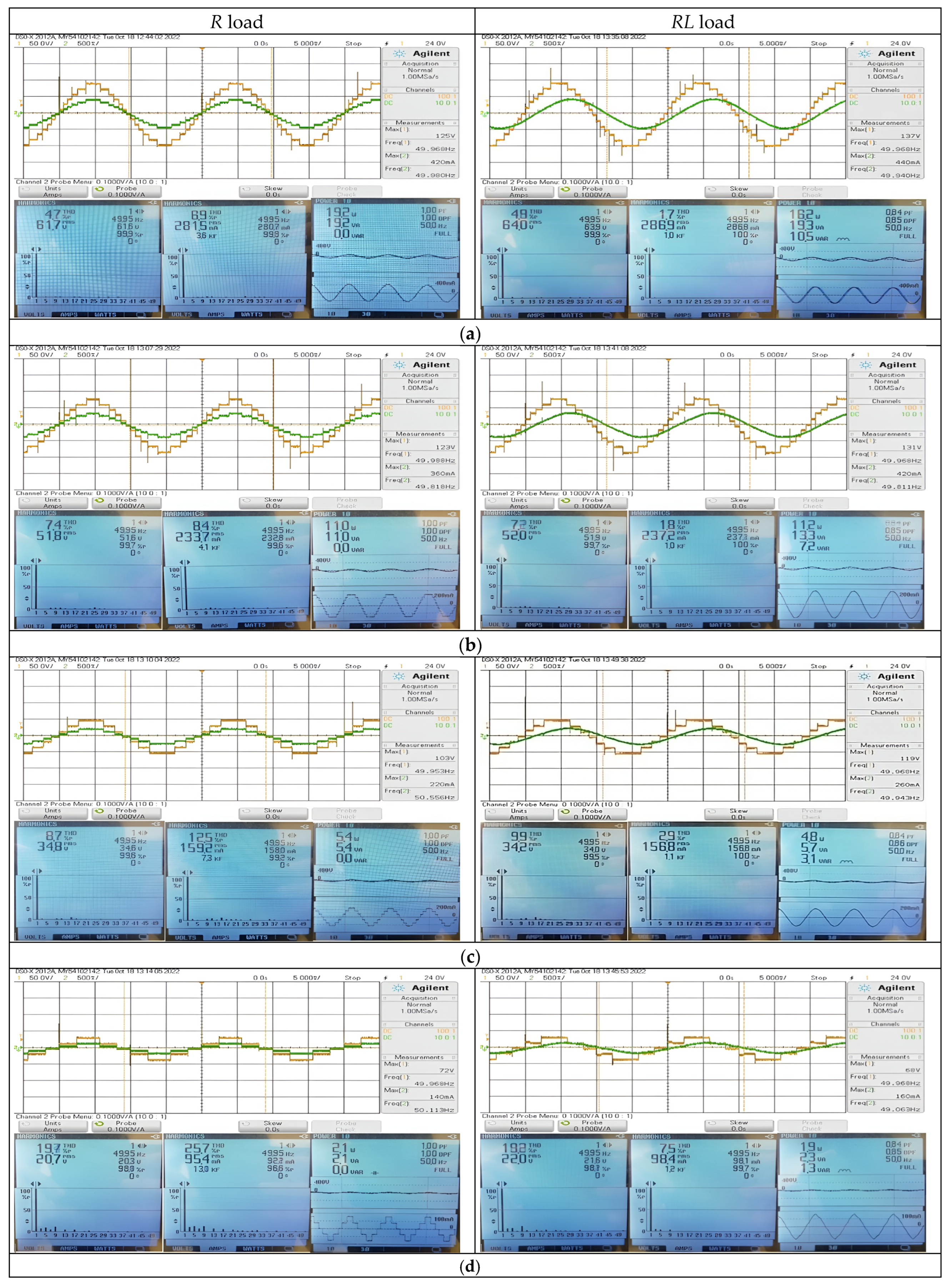

4.2. Experiment Performance Verification

4.3. Comparative Study

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Solangi, K.; Islam, M.; Saidur, R.; Rahim, N.; Fayaz, H. A review on global solar energy policy. Renew. Sustain. Energy Rev. 2011, 15, 2149–2163. [Google Scholar] [CrossRef]

- Carrasco, J.M.; Franquelo, L.G.; Bialasiewicz, J.T.; Galván, E.; PortilloGuisado, R.C.; Prats, M.M.; León, J.I.; Moreno-Alfonso, N. Power-electronic systems for the grid integration of renewable energy sources: A survey. IEEE Trans. Ind. Electron. 2006, 53, 1002–1016. [Google Scholar] [CrossRef]

- Kerekes, T.; Teodorescu, R.; Rodrıguez, P.; Vázquez, G.; Aldabas, E. A new high-efficiency single-phase transformerless PV inverter topology. IEEE Trans. Ind. Electron. 2009, 58, 184–191. [Google Scholar] [CrossRef]

- Suresh, L.P. A brief review on multilevel inverter topologies. In Proceedings of the 2016 International Conference on Circuit, Power and Computing Technologies (ICCPCT), Nagercoil, India, 18–19 March 2016; IEEE: New York, NY, USA, 2016; pp. 1–6. [Google Scholar]

- Koshti, A.K.; Rao, M. A brief review on multilevel inverter topologies. In Proceedings of the 2017 International Conference on Data Management, Analytics and Innovation (ICDMAI), Pune, India, 24–26 February 2017; IEEE: New York, NY, USA, 2017; pp. 187–193. [Google Scholar]

- Rodriguez, J.; Lai, J.-S.; Peng, F.Z. Multilevel inverters: A survey of topologies, controls, and applications. IEEE Trans. Ind. Electron. 2002, 49, 724–738. [Google Scholar] [CrossRef]

- Khoun-Jahan, H.; Shotorbani, A.M.; Abapour, M.; Zare, K.; Hosseini, S.H.; Blaabjerg, F.; Yang, Y. Switched capacitor based cascaded half-bridge multilevel inverter with voltage boosting feature. CPSS Trans. Power Electron. Appl. 2021, 6, 63–73. [Google Scholar] [CrossRef]

- Samadaei, E.; Kaviani, M.; Bertilsson, K. A 13-levels module (k-type) with two DC sources for multilevel inverters. IEEE Trans. Ind. Electron. 2018, 66, 5186–5196. [Google Scholar] [CrossRef]

- Siddique, M.D.; Mekhilef, S.; Sarwar, A.; Alam, A.; Mohamed Shah, N. Dual asymmetrical DC voltage source based switched capacitor boost multilevel inverter topology. IET Power Electron. 2020, 13, 1481–1486. [Google Scholar] [CrossRef]

- Babaie, M.; Sharifzadeh, M.; Kanaan, H.Y.; Al-Haddad, K. Switching-based optimized sliding-mode control for capacitor self-voltage balancing operation of seven-level PUC inverter. IEEE Trans. Ind. Electron. 2020, 68, 3044–3057. [Google Scholar] [CrossRef]

- Sia, Y.W.; Law, K.H.; Gopal, L.; Lim, K.H.; Wong, K.I. A new 2-dimension extendable multisource switched capacitor boost multilevel inverter with reduced components. In Proceedings of the 2021 IEEE International Conference in Power Engineering Application (ICPEA), Selangor, Malaysia, 8–9 March 2021; IEEE: New York, NY, USA, 2021; pp. 192–197. [Google Scholar]

- Sia, Y.W.; Law, K.H.; Gopal, L.; Lim, K.H.; Wong, K.I. A new symmetric and asymmetric step-up switched-capacitor integrated multilevel inverter with self-balanced and inductive load capability. In Proceedings of the 2021 International Conference on Green Energy, Computing and Sustainable Technology (GECOST), Virtual, 7–9 July 2021; IEEE: New York, NY, USA, 2021; pp. 1–5. [Google Scholar]

- Sandeep, N. A 13-level switched-capacitor-based boosting inverter. IEEE Trans. Circuits Syst. II Express Briefs 2020, 68, 998–1002. [Google Scholar] [CrossRef]

- Kim, K.-M.; Han, J.-K.; Moon, G.-W. A high step-up switched-capacitor 13-level inverter with reduced number of switches. IEEE Trans. Power Electron. 2020, 36, 2505–2509. [Google Scholar] [CrossRef]

- Panda, K.P.; Bana, P.R.; Panda, G. A reduced device count single DC hybrid switched-capacitor self-balanced inverter. IEEE Trans. Circuits Syst. II Express Briefs 2020, 68, 978–982. [Google Scholar] [CrossRef]

- Roy, T.; Sadhu, P.K. A step-up multilevel inverter topology using novel switched capacitor converters with reduced components. IEEE Trans. Ind. Electron. 2021, 68, 236–247. [Google Scholar] [CrossRef]

- Panda, K.P.; Bana, P.R.; Panda, G. A switched-capacitor self-balanced high-gain multilevel inverter employing a single DC source. IEEE Trans. Circuits Syst. II Express Briefs 2020, 67, 3192–3196. [Google Scholar] [CrossRef]

- Zeng, J.; Lin, W.; Cen, D.; Liu, J. Novel k-type multilevel inverter with reduced components and self-balance. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 4343–4354. [Google Scholar] [CrossRef]

- Ye, Y.; Chen, S.; Wang, X.; Cheng, K.-W.E. Self-balanced 13-level inverter based on switched capacitor and hybrid PWM algorithm. IEEE Trans. Ind. Electron. 2021, 68, 4827–4837. [Google Scholar] [CrossRef]

- Ye, Y.; Zhang, G.; Wang, X.; Yi, Y.; Cheng, K.W.E. Self-balanced switched-capacitor thirteen-level inverters with reduced capacitors count. IEEE Trans. Ind. Electron. 2022, 69, 1070–1076. [Google Scholar] [CrossRef]

- Anand, V.; Singh, V. A 13-level switched-capacitor multilevel inverter with single DC source. IEEE J. Emerg. Sel. Top. Power Electron. 2022, 10, 1575–1586. [Google Scholar] [CrossRef]

- Ye, Y.; Cheng, K.W.E.; Liu, J.; Ding, K. A step-up switched-capacitor multilevel inverter with self-voltage balancing. IEEE Trans. Ind. Electron. 2014, 61, 6672–6680. [Google Scholar] [CrossRef]

- Taghvaie, A.; Adabi, J.; Rezanejad, M. A self-balanced step-up multilevel inverter based on switched-capacitor structure. IEEE Trans. Power Electron. 2018, 33, 199–209. [Google Scholar] [CrossRef]

| Parameters | Vcn |

|---|---|

| Next | n |

| Ndiode | 2 |

| Ncapacitor | 2 + n |

| Ngate | 4 + 2n |

| Nswitch | 8 + 3n |

| Ncomponent | 13 + 4n |

| Vboost | 3 × 2n |

| Nlevel | (3 × 2n+1) + 1 |

| States | S1 | S1′ | S2 | S2′ | S3 | S3′ | S4 | S5 | S5′ | S6 | S6′ | Cu | Cd | C1 | Vout |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 0 | D | D | C | 0 |

| 2 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | C | C | - | +Vdc |

| 3 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | D | C | - | +2Vdc |

| 4 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | C | D | - | +2Vdc |

| 5 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | D | D | C | +3Vdc |

| 6 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | C | C | D | +4Vdc |

| 7 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | D | C | D | +5Vdc |

| 8 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | C | D | D | +5Vdc |

| 9 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | D | D | D | +6Vdc |

| 10 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | C | C | - | −Vdc |

| 11 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | D | C | - | −2Vdc |

| 12 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | C | D | - | −2Vdc |

| 13 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | D | D | C | −3Vdc |

| 14 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | C | C | D | −4Vdc |

| 15 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | D | C | D | −5Vdc |

| 16 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | C | D | D | −5Vdc |

| 17 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | D | D | D | −6Vdc |

| Specification | Parameters |

|---|---|

| DC voltage source | Vdc = 100 V |

| AC fundamental frequency | f = 50 Hz |

| Diode forward voltage | Vd,f = 1.6 V |

| Diode on-resistance | Rd,on = 826.5 µΩ |

| Switch on-resistance | Rsw,on = 25 mΩ |

| Capacitors | Cu = Cd = 4700 µF, C1 = 3300 µF |

| Capacitor internal resistance | Rcu = Rcd = 32.8 mΩ, Rc1 = 30.0 mΩ |

| Resistive load | Rload = 210 Ω |

| Resistive-inductive load | Rload = 157.5 Ω, Lload = 0.335 H |

| Modulation index | 0.3, 0.5, 0.8, 1.0 |

| Load | MI | Vout (V) | THD (%) | Iout (A) | THD (%) |

|---|---|---|---|---|---|

| R load (210 Ω) | 1.0 | 588.13 | 6.41 | 2.80 | 6.18 |

| 0.8 | 490.44 | 8.65 | 2.33 | 8.45 | |

| 0.5 | 295.76 | 12.38 | 1.41 | 12.18 | |

| 0.3 | 196.68 | 21.45 | 0.94 | 21.28 | |

| RL load (157.5 Ω and 0.335 H) | 1.0 | 589.73 | 6.40 | 3.14 | 0.60 |

| 0.8 | 491.29 | 8.66 | 2.53 | 1.59 | |

| 0.5 | 296.02 | 12.37 | 1.65 | 1.71 | |

| 0.3 | 196.73 | 21.47 | 1.08 | 5.27 |

| Source Power (W) | 50 | 100 | 200 | 500 |

| Capacitor Loss (W) | 0.015 | 0.080 | 0.235 | 1.130 |

| Switch Loss (W) | 0.018 | 0.061 | 0.216 | 1.310 |

| Diode Loss (W) | 1.056 | 2.191 | 4.704 | 13.406 |

| Total Loss (W) | 1.076 | 2.332 | 5.155 | 15.845 |

| Resistance (Ω) | 3640 | 1820 | 910 | 363 |

| Output Voltage (V) | 593.28 | 592.96 | 592.32 | 590.42 |

| Output Current (A) | 0.16 | 0.33 | 0.65 | 1.63 |

| Efficiency (%) | 97.84 | 97.68 | 97.43 | 96.84 |

| Specification | Models, Parameters, and Values | Manufacturer |

|---|---|---|

| DC voltage source | Vdc = 20 V | |

| AC fundamental frequency | f = 50 Hz | |

| MI | 0.3, 0.5, 0.8, 1.0 | |

| R load | R = 210 Ω | |

| RL load | R = 157.5 Ω, L = 0.335 H | |

| Capacitor | C1 = C2 = 4700 µF, C3 = 3300 µF | |

| Diode | MUR1560G | ONSEMI (Scottsdale, AZ, USA) |

| Switch | AUIRGP50B60PD1 and IGW30N60T (for S4 only) | Infineon Technologies (Munich, Germany) |

| DSP controller | EZDSP F28335 | Spectrum Digital (Plano, TX, USA) |

| Gate driver | HCPL-3120 | Broadcom (San Jose, CA, USA) |

| DC power Supply | GW Instek GPC-3030B | Good Will Instrument (New Taipei City, Taiwan) |

| Oscilloscope | DSO-X 2012A | Keysight Technologies (Santa Clara, CA, USA) |

| Power analyzer | Fluke 43B | Fluke Corporation (Everett, WT, USA) |

| Load | MI | Vout (V) | THD (%) | Iout (A) | THD (%) |

|---|---|---|---|---|---|

| R load (210 Ω) | 1.0 | 61.70 | 4.70 | 0.28 | 6.90 |

| 0.8 | 51.80 | 7.40 | 0.23 | 8.40 | |

| 0.5 | 34.38 | 8.70 | 0.16 | 12.50 | |

| 0.3 | 20.70 | 19.70 | 0.10 | 25.70 | |

| RL load (157.5 Ω and 0.335 H) | 1.0 | 64.00 | 4.80 | 0.29 | 1.70 |

| 0.8 | 52.00 | 7.20 | 0.24 | 1.80 | |

| 0.5 | 34.20 | 9.90 | 0.16 | 2.90 | |

| 0.3 | 22.00 | 19.20 | 0.01 | 7.50 |

| Load | MI | Simulation | Experiment | ||

|---|---|---|---|---|---|

| Vout THD (%) | Iout THD (%) | Vout THD (%) | Iout THD (%) | ||

| R load (210 Ω) | 1.0 | 6.41 | 6.18 | 4.70 | 6.90 |

| 0.8 | 8.65 | 8.45 | 7.40 | 8.40 | |

| 0.5 | 12.38 | 12.18 | 8.70 | 12.50 | |

| 0.3 | 21.45 | 21.28 | 19.70 | 25.70 | |

| RL load (157.5 Ω and 0.335 H) | 1.0 | 6.40 | 0.60 | 4.80 | 1.70 |

| 0.8 | 8.66 | 1.59 | 7.20 | 1.80 | |

| 0.5 | 12.37 | 1.71 | 9.90 | 2.90 | |

| 0.3 | 21.47 | 5.27 | 19.20 | 7.50 | |

| Parameter | [8] | [9] | [13] | [14] | [15] | [16] | [17] | [18] | [19] | [20] | [21] | [22] | [23] | Proposed |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Nsource | 2 | 2 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| Ncomponent | 16 | 12 | 18 | 18 | 20 | 21 | 18 | 16 | 18 | 21 | 18 | 25 | 39 | 16 |

| Nswitch | 14 | 11 | 13 | 14 | 12 | 14 | 13 | 12 | 10 | 14 | 15 | 10 | 29 | 11 |

| Ndiode | 0 | 0 | 2 | 1 | 4 | 2 | 2 | 0 | 4 | 4 | 0 | 10 | 5 | 2 |

| Ncapacitor | 2 | 1 | 3 | 3 | 4 | 5 | 3 | 4 | 4 | 3 | 3 | 5 | 5 | 3 |

| Ngate | 11 | 10 | 9 | 10 | 12 | 12 | 10 | 11 | 10 | 8 | 11 | 8 | 17 | 6 |

| Vboost | 2 | 2 | 6 | 6 | 3 | 6 | 6 | 1.5 | 6 | 6 | 6 | 6 | 6 | 6 |

| Extensibility | Yes | No | No | No | No | Yes | No | Yes | No | No | No | Yes | Yes | Yes |

| Component | Manufacturer | Part Number | Rating | Unit Price ($) | [13] | [14] | [16] | [17] | [19] | [20] | [21] | [22] | [23] | Proposed |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| MOSFET | Infineon Technologies (Munich, Germany) | IRF640NPBF | 200 V, 18 A | 1.71 | 4 | 5 | 10 | 5 | 4 | 4 | 3 | 6 | 27 | 4 |

| Vishay Siliconix (Malvern, PA, USA) | IRF740PBF | 400 V, 10 A | 2.78 | 7 | 7 | 0 | 6 | 2 | 6 | 8 | 0 | 0 | 3 | |

| Infineon Technologies (Munich, Germany) | IPP60R190P6XKSA1 | 600 V, 20.2 A | 3.42 | 2 | 2 | 4 | 2 | 4 | 2 | 4 | 4 | 2 | 4 | |

| Diode | SMC Diode Solutions (San Jose, CA, USA) | STF12100 | 100 V, 15 A | 0.28 | 0 | 1 | 2 | 1 | 2 | 2 | 0 | 10 | 5 | 0 |

| Cornell Dubilier (South Plainfield, NJ, USA) | SDURF1520 | 300 V, 15 A | 0.28 | 2 | 0 | 0 | 1 | 2 | 2 | 0 | 0 | 0 | 3 | |

| Knowles (Itasca, IL, USA) | SLPX102M100A3P3 | 100 V, 1000 µF | 3.34 | 2 | 2 | 5 | 2 | 2 | 2 | 1 | 5 | 5 | 2 | |

| EPCOS—TDK Electronics (Tokyo, Japan) | B43416C3108A000 | 300 V, 1000 µF | 6.46 | 1 | 1 | 0 | 1 | 2 | 1 | 2 | 0 | 0 | 1 | |

| Driver | Broadcom Limited (San Jose, CA, USA) | HCPL-3120-060E | 625 Vmax | 3.23 | 9 | 10 | 12 | 10 | 10 | 8 | 11 | 8 | 17 | 6 |

| Heatsink | Ohmite (Melrose Park, IL, USA) | WA-T220-101E | 2.26 | 13 | 14 | 14 | 13 | 10 | 12 | 15 | 10 | 29 | 11 | |

| Total Cost ($) | With Heatsink | 105 | 112 | 118 | 107 | 101.7 | 97.58 | 126.74 | 91.88 | 191.56 | 87.08 | |||

| Without Heatsink | 75.9 | 80.6 | 86.8 | 78.1 | 79.1 | 70.46 | 92.84 | 69.28 | 126.02 | 62.22 | ||||

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Law, K.H.; Sia, Y.W.; Chiong, R.C.W.; Ang, S.P.; Yeo, K.S.K.; Sim, S.Y. 13-Level Single-Source Switched-Capacitor Boost Multilevel Inverter. Energies 2025, 18, 1664. https://doi.org/10.3390/en18071664

Law KH, Sia YW, Chiong RCW, Ang SP, Yeo KSK, Sim SY. 13-Level Single-Source Switched-Capacitor Boost Multilevel Inverter. Energies. 2025; 18(7):1664. https://doi.org/10.3390/en18071664

Chicago/Turabian StyleLaw, Kah Haw, Yew Wei Sia, Raymond Choo Wee Chiong, Swee Peng Ang, Kenneth Siok Kiam Yeo, and Sy Yi Sim. 2025. "13-Level Single-Source Switched-Capacitor Boost Multilevel Inverter" Energies 18, no. 7: 1664. https://doi.org/10.3390/en18071664

APA StyleLaw, K. H., Sia, Y. W., Chiong, R. C. W., Ang, S. P., Yeo, K. S. K., & Sim, S. Y. (2025). 13-Level Single-Source Switched-Capacitor Boost Multilevel Inverter. Energies, 18(7), 1664. https://doi.org/10.3390/en18071664