Design and Demonstration of a 10 kV, 60 A SiC MOSFET-Based Medium-Voltage Power Module

Abstract

1. Introduction

2. Packaging Design of 10 kV SiC Power Module

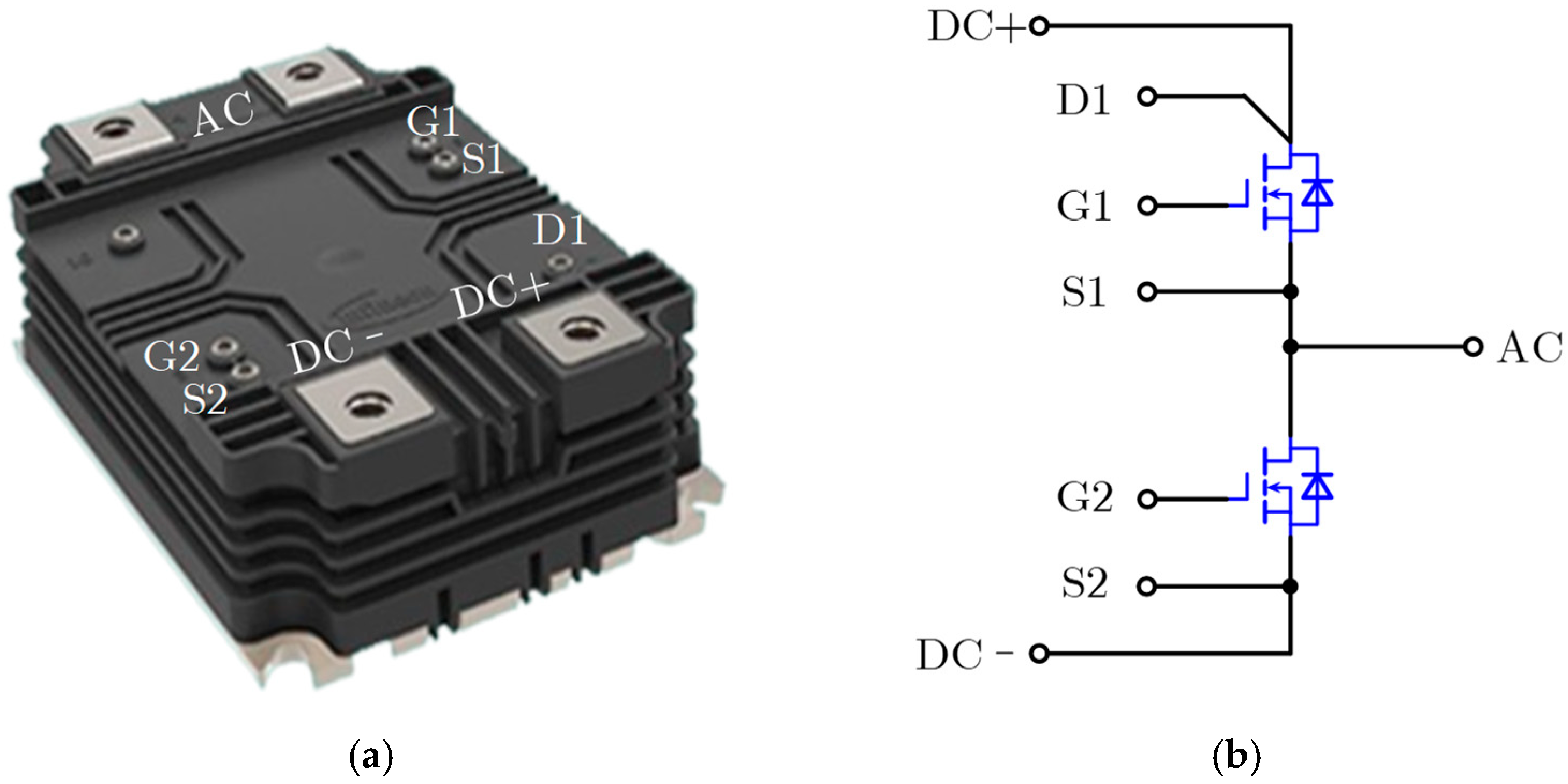

2.1. Configurations and Circuit Topology

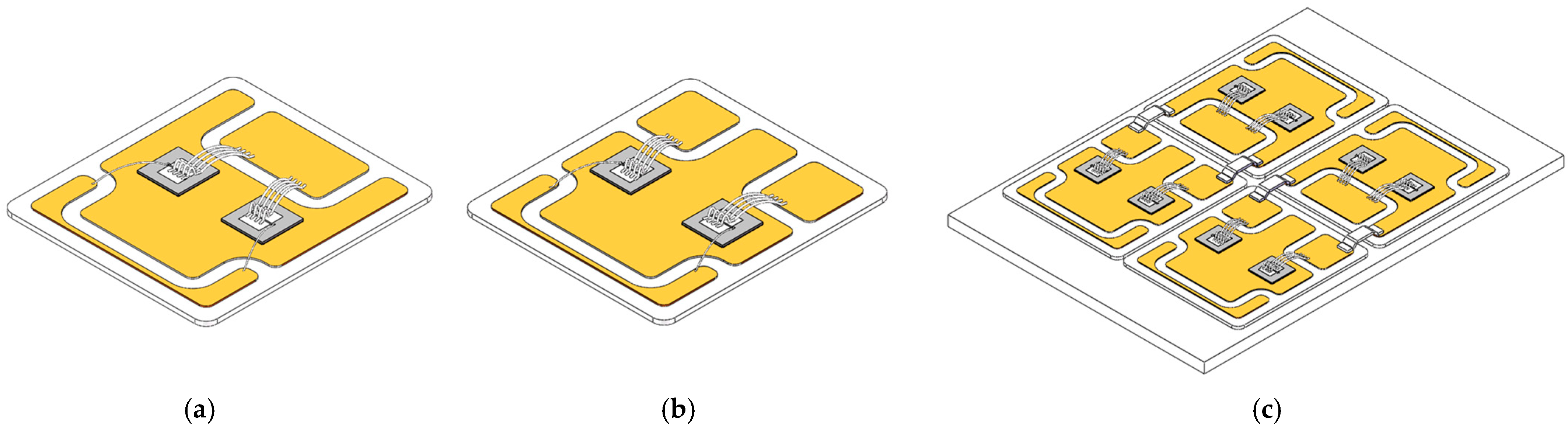

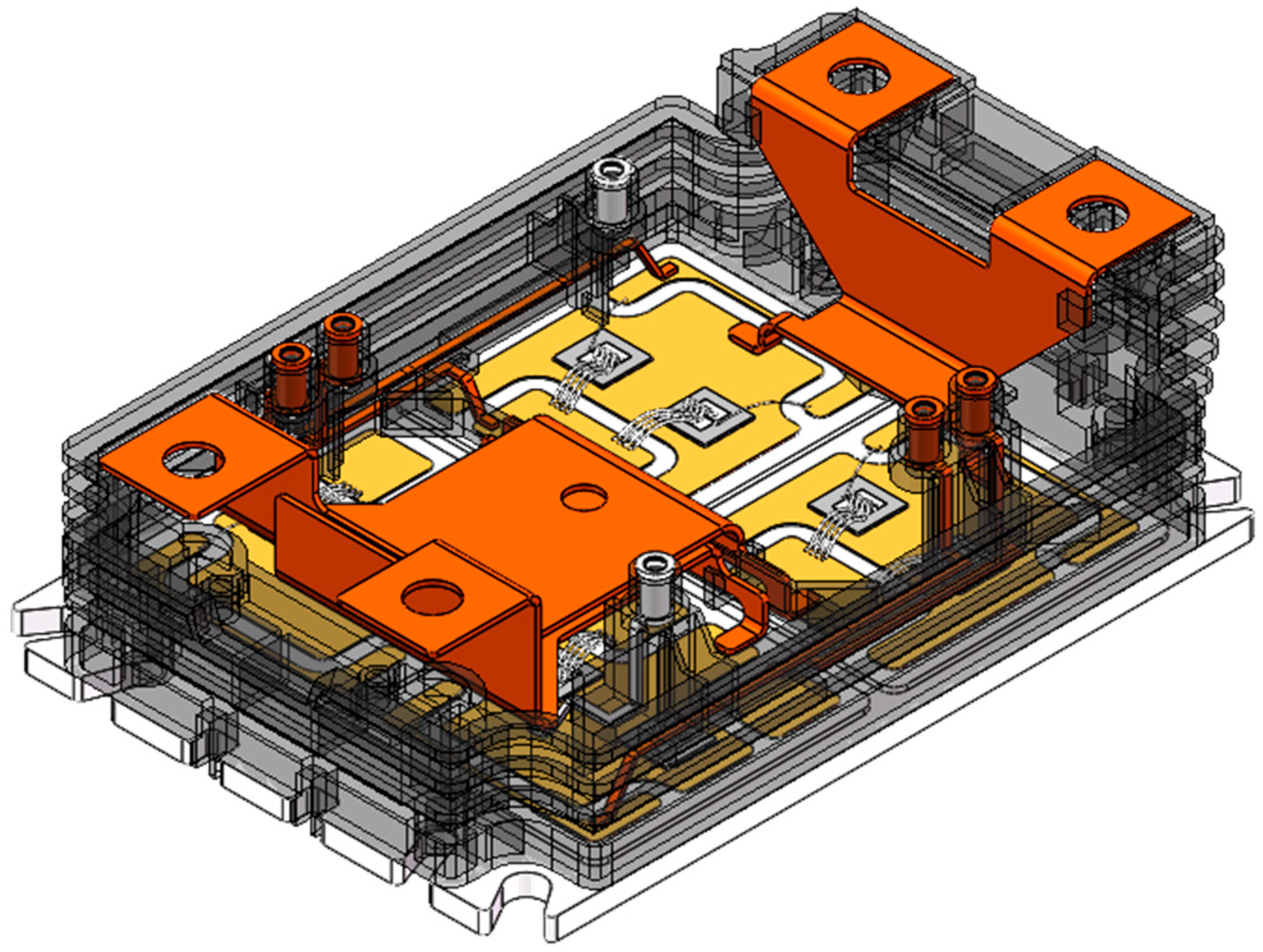

2.2. DBC Layout and Packaging Structure

3. Parasitic and Thermal Performances Evaluation

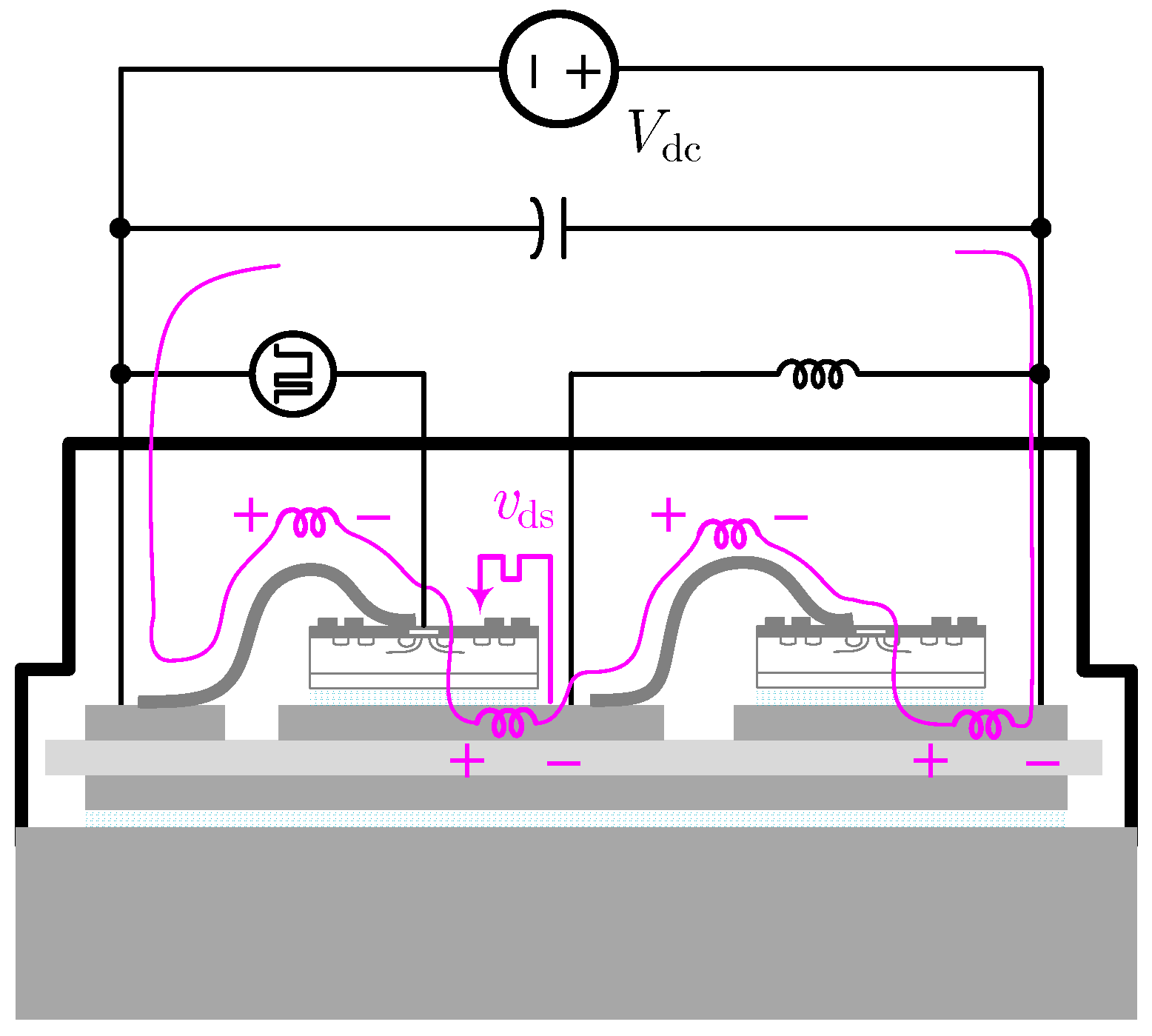

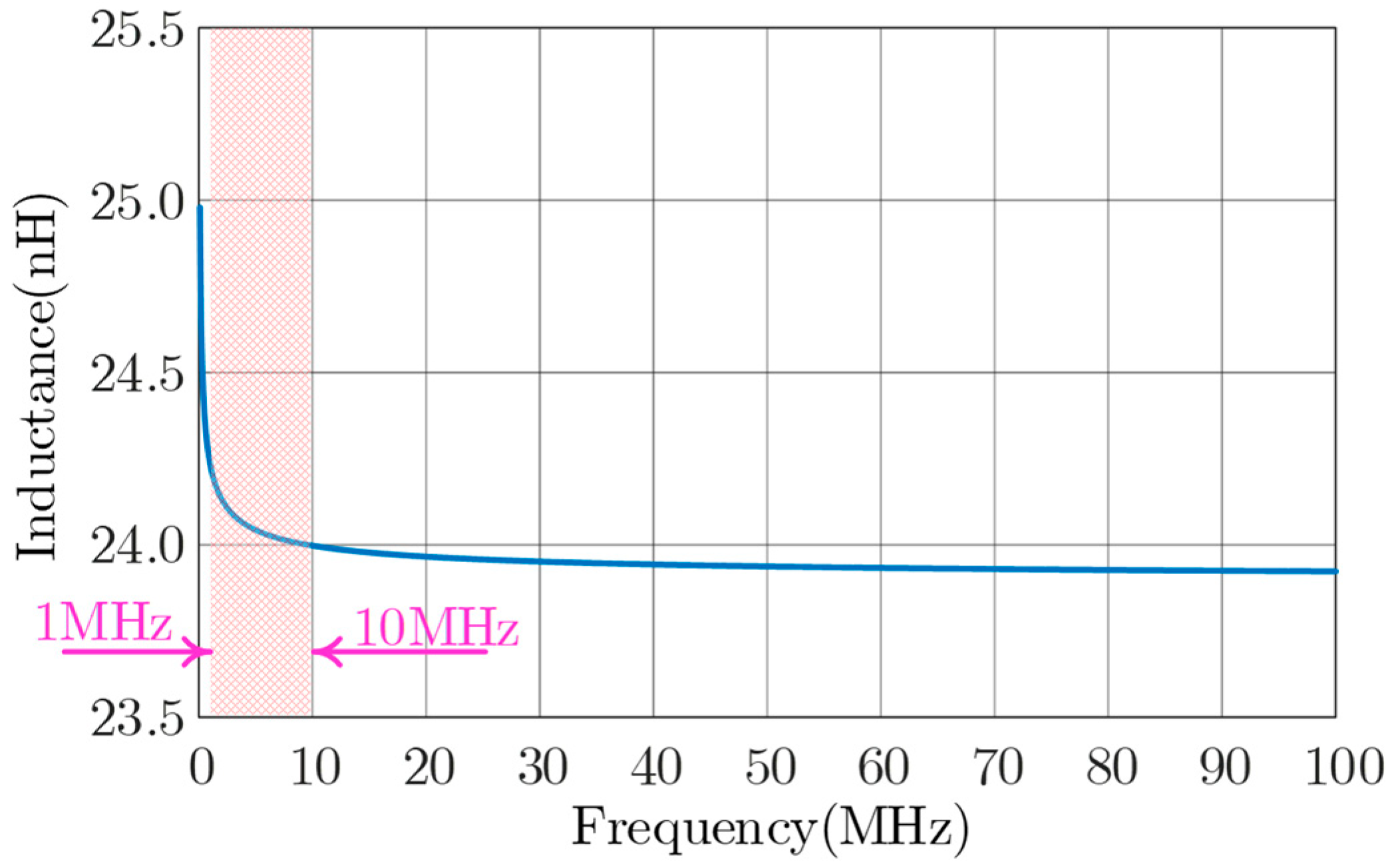

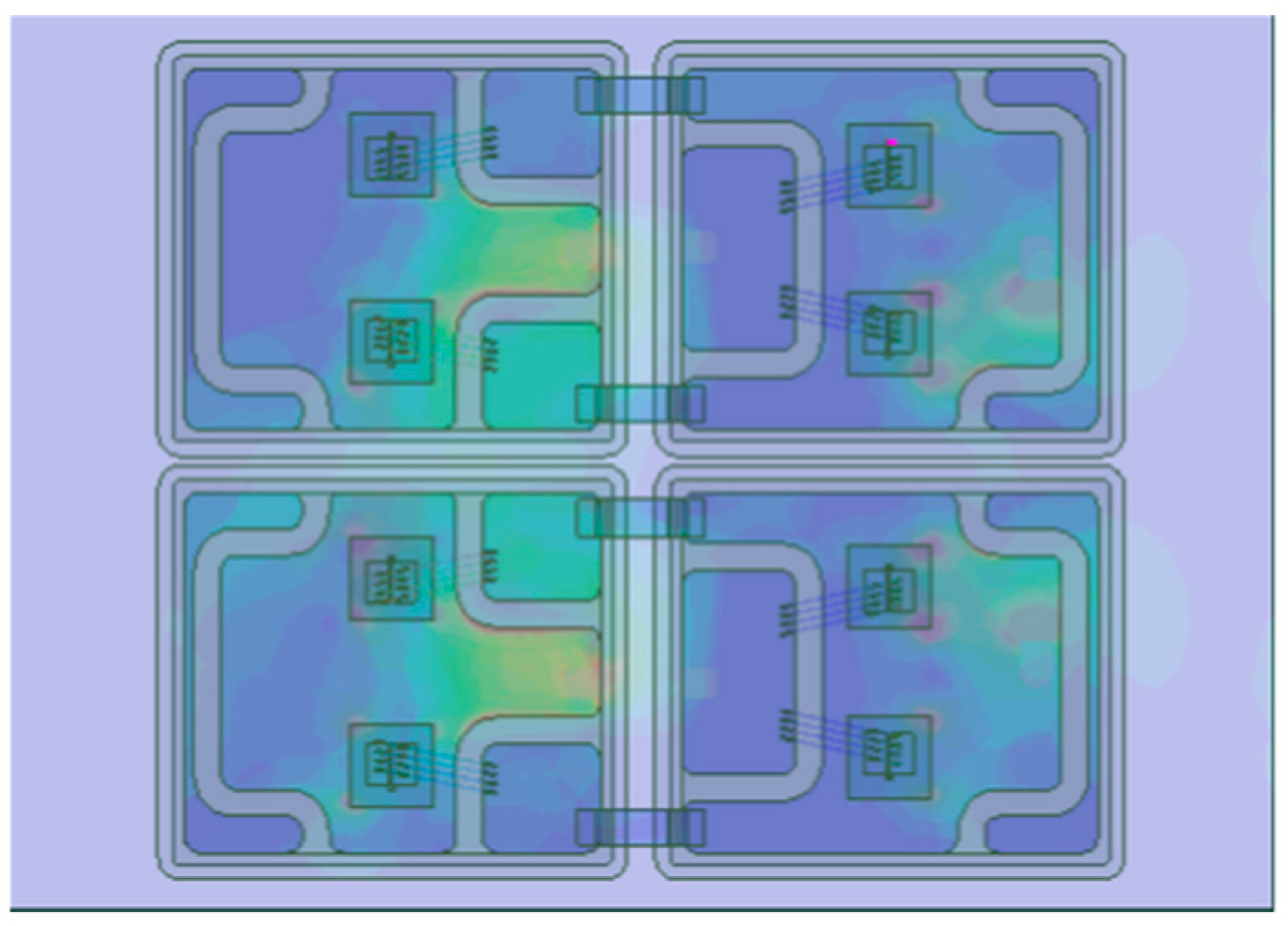

3.1. Extraction of Parasitic Inductance

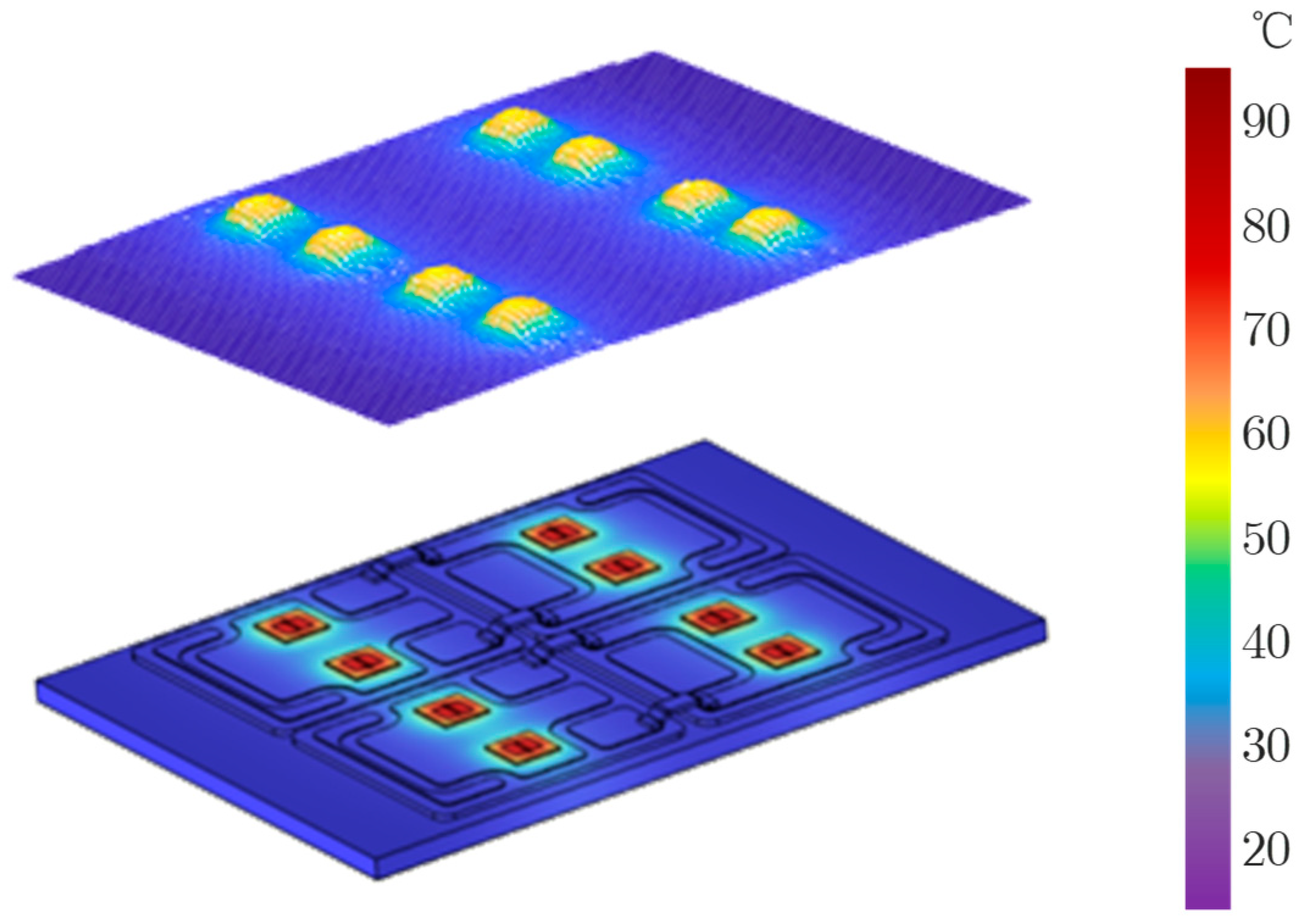

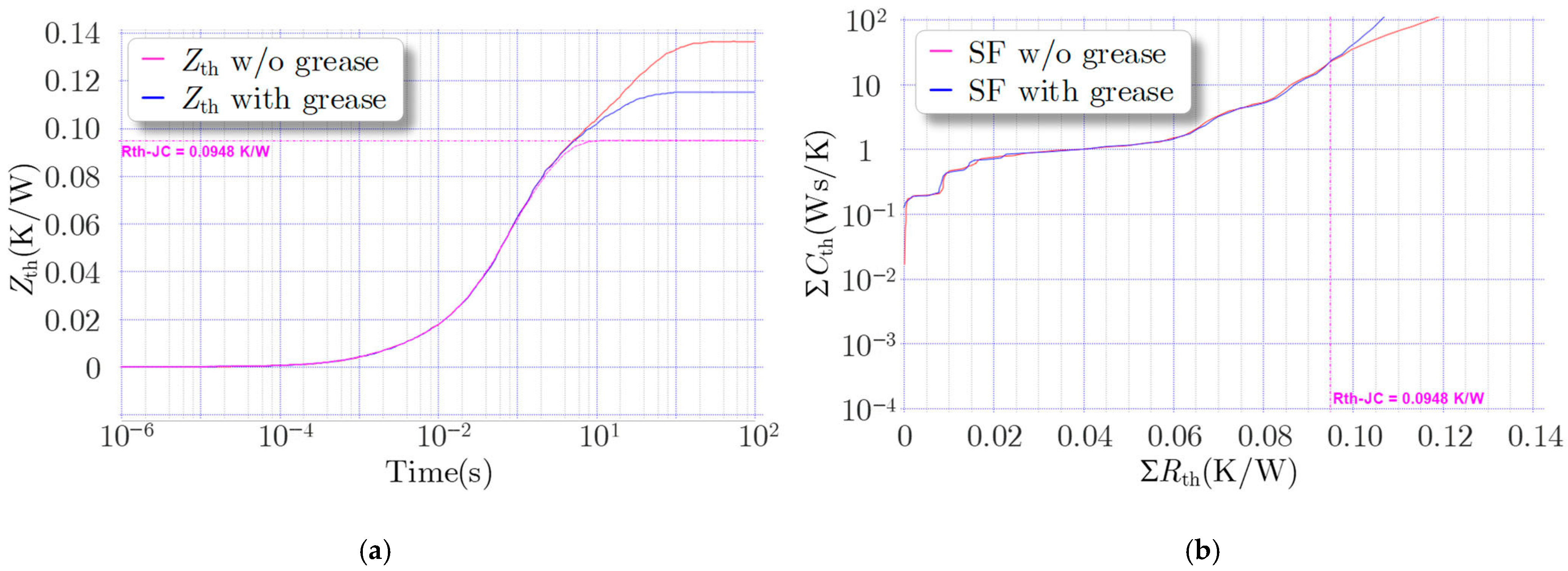

3.2. Extraction of Thermal Impedance

4. Dynamic Characterization Based on Double-Pulse Test

4.1. Test Platform

4.2. Experimental Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Johannesson, D.; Nawaz, M.; Ilves, K. Assessment of 10 kV, 100 A Silicon Carbide MOSFET Power Modules. IEEE Trans. Power Electron. 2018, 33, 5215–5225. [Google Scholar] [CrossRef]

- Liu, G.; Wu, Y.; Li, K.; Zhang, H. Development of high power SiC devices for rail traction power systems. J. Cryst. Growth 2019, 507, 442–452. [Google Scholar] [CrossRef]

- Yang, X.; Li, J.; Ding, Y.; Wang, L. Observation of Transient Parity-Time Symmetry in Electronic Systems. Phys. Rev. Lett. 2022, 128, 065701. [Google Scholar] [CrossRef] [PubMed]

- Rothmund, D.; Guillod, T.; Bortis, D.; Kolar, J.W. 99% Efficient 10 kV SiC-Based 7 kV/400 V DC Transformer for Future Data Centers. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 7, 753–767. [Google Scholar] [CrossRef]

- Marzoughi, A.; Burgos, R.; Boroyevich, D. Investigating Impact of Emerging Medium-Voltage SiC MOSFETs on Medium-Voltage High-Power Industrial Motor Drives. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 7, 1371–1387. [Google Scholar] [CrossRef]

- Vechalapu, K.; Bhattacharya, S. Performance Comparison of 10 kV-15 kV High Voltage SiC Modules and High Voltage Switch Using Series Connected 1.7 kV LV SiC MOSFET Devices. In Proceedings of the 2016 IEEE Energy Conversion Congress and Exposition (ECCE), Milwaukee, WI, USA, 18–22 September 2016. [Google Scholar]

- Takahashi, M.; Sun, Z.; Watanabe, A.; Yamamoto, H. Thermo-Mechanical Analysis on 10 kV SiC-MOSFETs to Improve the Reliability of Solder Layers. Microelectron. Reliab. 2025, 172, 115826. [Google Scholar] [CrossRef]

- Zhao, S.; Yang, X.; Wu, X.; Liu, G. Investigation on Creep-Fatigue Interaction Failure of Die-Attach Solder Layers in IGBTs Under Power Cycling. IEEE Trans. Power Electron. 2025, 40, 7261–7274. [Google Scholar] [CrossRef]

- Ryu, S.-H.; Krishnaswami, S.; O'Loughlin, M.; Richmond, J.; Agarwal, A.; Palmour, J. 10-kV, 123-mΩ·cm2 4H-SiC Power DMOSFETs. IEEE Electron. Device Lett. 2004, 25, 556–558. [Google Scholar] [CrossRef]

- Ryu, S.-H.; Krishnaswami, S.; Hull, B.; Richmond, J.; Agarwal, A.; Hefner, A. 10 kV, 5A 4H-SiC Power DMOSFET. In Proceedings of the 2006 IEEE International Symposium on Power Semiconductor Devices and ICs (ISPSD), Naples, Italy, 4–8 June 2006. [Google Scholar]

- Callanan, R.; Agarwal, A.K.; Burk, A.A.; Das, M.K.; Hull, B.; Husna, F.; Powell, A.; Richmond, J.; Ryu, S.-H.; Zhang, Q. Recent Progress in SiC DMOSFETs and JBS Diodes at Cree. In Proceedings of the 2008 IEEE Industrial Electronics Conference (IECON), Orlando, FL, USA, 10–13 November 2008. [Google Scholar]

- Pala, V.; Brunt, E.V.; Cheng, L.; O’Loughlin, M.; Richmond, J.; Burk, A.; Allen, S.T.; Grider, D.; Palmour, J.W.; Scozzie, C.J. 10 kV and 15 kV Silicon Carbide Power MOSFETs for Next-Generation Energy Conversion and Transmission Systems. In Proceedings of the 2014 IEEE Energy Conversion Congress and Exposition (ECCE), Pittsburgh, PA, USA, 14–18 September 2014. [Google Scholar]

- Nielsen, M.R.; Kjær, M.; Zhao, H.; Bech, M.M.; Munk-Nielsen, S. Comparison of Two Third-Generation 10 kV SiC MOSFET Die’s Switching Performance on a System Level. In Proceedings of the 2024 IEEE 10th International Power Electronics and Motion Control Conference (IPEMC-ECCE Asia), Chengdu, China, 17–20 May 2024. [Google Scholar]

- Passmore, B.; Cole, Z.; McGee, B.; Wells, M.; Stabach, J.; Bradshaw, J. The Next Generation of High Voltage (10 kV) Silicon Carbide Power Modules. In Proceedings of the 2016 IEEE Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Fayetteville, AR, USA, 7–9 November 2016. [Google Scholar]

- Mocevic, S.; Yu, J.; Xu, Y.; Stewart, J.; Wang, J.; Cvetkovic, I.; Dong, D.; Burgos, R.; Boroyevich, D. Power Cell Design and Assessment Methodology Based on a High-Current 10-kV SiC MOSFET Half-Bridge Module. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 9, 3916–3935. [Google Scholar] [CrossRef]

- Reigosa, P.D.; Iannuzzo, F.; Munk-Nielsen, S.; Blaabjerg, F. New Layout Concepts in MW-Scale IGBT Modules for Higher Robustness During Normal and Abnormal Operations. In Proceedings of the 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 20–24 March 2016; pp. 288–294. [Google Scholar]

- Wu, R.; Smirnova, L.; Wang, H.; Iannuzzo, F.; Blaabjerg, F. Comprehensive Investigation on Current Imbalance Among Parallel Chips Inside MW-Scale IGBT Power Modules. In Proceedings of the 2015 9th International Conference on Power Electronics and ECCE Asia (ICPE-ECCE Asia), Seoul, Republic of Korea, 1–5 June 2015; pp. 850–856. [Google Scholar]

- DiMarino, C.M.; Mouawad, B.; Johnson, C.M.; Boroyevich, D.; Burgos, R. 10-kV SiC MOSFET Power Module with Reduced Common-Mode Noise and Electric Field. IEEE Trans. Power Electron. 2020, 35, 6050–6060. [Google Scholar] [CrossRef]

- Jørgensen, A.B.; Christensen, N.; Dalal, D.N.; Sønderskov, S.D.; Bęczkowski, S.; Uhrenfeldt, C.; Munk-Nielsen, S. Reduction of Parasitic Capacitance in 10 kV SiC MOSFET Power Modules Using 3D FEM. In Proceedings of the 2017 19th European Conference on Power Electronics and Applications (EPE’17 ECCE Europe), Warsaw, Poland, 11–14 September 2017; pp. P.1–P.8. [Google Scholar]

- Hebedean, C.; Munteanu, C.; Racasan, A.; Pacurar, C. Parasitic Capacitance Removal with an Embedded Ground Layer. In Proceedings of the EUROCON 2013, Zagreb, Croatia, 1–4 July 2013; pp. 1886–1891. [Google Scholar]

- Li, X.; Chen, Y.; Chen, H.; Paul, R.; Song, X.; Mantooth, H.A. A 10 kV SiC MOSFET Power Module with Optimized System Interface and Electric Field Distribution. IEEE Trans. Power Electron. 2024, 39, 9540–9553. [Google Scholar] [CrossRef]

- Wang, L.; Gong, J.; Long, T.; Blaabjerg, F.; Hu, B.; Wang, Y.; Zeng, Z. Direct Metallization-Based DBC-Free Power Modules for Near-Junction Water Cooling: Analysis and Experimental Comparison. IEEE Trans. Power Electron. 2024, 39, 7052–7063. [Google Scholar] [CrossRef]

- Li, Y.; ul-Hassan, M.; Mirza, A.B.; Xie, Y.; Deng, S.; Vala, S.; Luo, F.; Feng, X.; Narumanchi, S.; Flicker, J. State-of-the-Art Medium- and High-Voltage Silicon Carbide Power Modules, Challenges and Mitigation Techniques: A Review. IEEE Trans. Compon. Packag. Manuf. Technol. 2024, 14, 2177–2195. [Google Scholar] [CrossRef]

- Infineon Technologies, AG. XHP™ IGBT Modules. Available online: https://www.infineon.com/cms/en/product/power/igbt/igbt-modules/xhp/ (accessed on 23 June 2025).

- Defining the Future of IGBT High-Power Modules; Electronics Maker: New Delhi, India, 9 April 2015. Available online: https://electronicsmaker.com/defining-the-future-of-igbt-high-power-modules (accessed on 2 August 2025).

- Wang, X.; Chen, Y.; Zhu, W.; Xin, L.; Yang, T.; Sun, K.; Shao, Q.; Chen, Z.; Zhou, S.; Kou, C. Three-Level Parallel Structure Based on XHP Packaging Device and Converter Equipment. CN Patent 216437080U, 3 May 2022. [Google Scholar]

- Zhu, A.; Gao, H.; Xia, Y.; Wu, X.; Huang, A.; Peng, C. Adaptive Stray Inductance Extraction Algorithm Using Linear Regression for Power Module with High Noise Immunity and Accuracy. CPSS Trans. Power Electron. Appl. 2022, 7, 176–185. [Google Scholar] [CrossRef]

- Zhang, Z.; Guo, B.; Wang, F.; Liu, J.; Wang, H. Methodology for Switching Characterization Evaluation of Wide Band-Gap Devices in a Phase-Leg Configuration. In Proceedings of the 2014 IEEE Applied Power Electronics Conference and Exposition (APEC), Fort Worth, TX, USA, 16–20 March 2014; pp. 2534–2541. [Google Scholar]

- Hall, S.H. High-Speed Digital System Design: A Handbook of Interconnect Theory and Design Practices; Wiley-Interscience: New York, NY, USA, 2000. [Google Scholar]

- Li, W.; Mao, S.; Wang, Z.; Liu, H.; Yang, J. Modeling and Analysis of the Switching Characteristics Difference for Paralleling SiC MOSFETs in Multichip Power Modules. In Proceedings of the 2021 IEEE Workshop on Wide Bandgap Power Devices and Applications in Asia (WiPDA Asia), Shenzhen, China, 23–25 August 2021; pp. 217–223. [Google Scholar]

- Li, W.; Mao, S.; Liu, H.; Yang, J.; Wang, Z. Current Uniformity Optimization of Multi-Chip SiC Module for High-Power Applications. In Proceedings of the 2022 IEEE International Power Electronics and Application Conference and Exposition (PEAC), Wuhan, China, 4–7 November 2022; pp. 545–550. [Google Scholar]

- JESD 51–14; Transient Dual Interface Test Method for the Measurement of the Thermal Resistance Junction-to-Case of Semiconductor Devices with Heat Flow Through a Single Path. JEDEC Solid State Technology Association: Arlington, VA, USA, 2010.

- Andreas, V.; Hornkamp, M. IGBT Modules: Technologies, Driver and Application; Infineon Technologies AG: Munich, Germany, 2012. [Google Scholar]

| Conductor Segment | DC+ to DHS | SHS to AC | AC to DLS | SLS to DC− |

|---|---|---|---|---|

| DC+ to DHS | 16.7 nH | −0.93 nH | 0.66 nH | 7.69 nH |

| SHS to AC | 0.39 nH | 10.91 nH | −8.31 nH | −0.83 nH |

| AC to DLS | 0.66 nH | −8.31 nH | 8.29 nH | −0.69 nH |

| SLS to DC− | −7.69 nH | −0.83 nH | −0.69 nH | 19.69 nH |

| Parameters | Value |

|---|---|

| DC Link Capacitors, Cdc | 10 kV, 19 μF |

| Load Inductor, Ld | 6 mH |

| DC Link Voltage, Vdc | 7 kV |

| Gate Voltage (on/off), Vg | 18/−5 V |

| Gate Resistance, Rg | 10 Ω |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Xiao, K.; Zhang, Y.; Tan, S.; Pan, J.; Feng, H.; Liang, Y.; Zeng, Z. Design and Demonstration of a 10 kV, 60 A SiC MOSFET-Based Medium-Voltage Power Module. Energies 2025, 18, 4407. https://doi.org/10.3390/en18164407

Xiao K, Zhang Y, Tan S, Pan J, Feng H, Liang Y, Zeng Z. Design and Demonstration of a 10 kV, 60 A SiC MOSFET-Based Medium-Voltage Power Module. Energies. 2025; 18(16):4407. https://doi.org/10.3390/en18164407

Chicago/Turabian StyleXiao, Kai, Yining Zhang, Shuming Tan, Jianyu Pan, Hao Feng, Yuxi Liang, and Zheng Zeng. 2025. "Design and Demonstration of a 10 kV, 60 A SiC MOSFET-Based Medium-Voltage Power Module" Energies 18, no. 16: 4407. https://doi.org/10.3390/en18164407

APA StyleXiao, K., Zhang, Y., Tan, S., Pan, J., Feng, H., Liang, Y., & Zeng, Z. (2025). Design and Demonstration of a 10 kV, 60 A SiC MOSFET-Based Medium-Voltage Power Module. Energies, 18(16), 4407. https://doi.org/10.3390/en18164407