A Novel Two-Transformer Full-Bridge Converter with Integrated Boost Converter for Hold-Up Time Compensation

Abstract

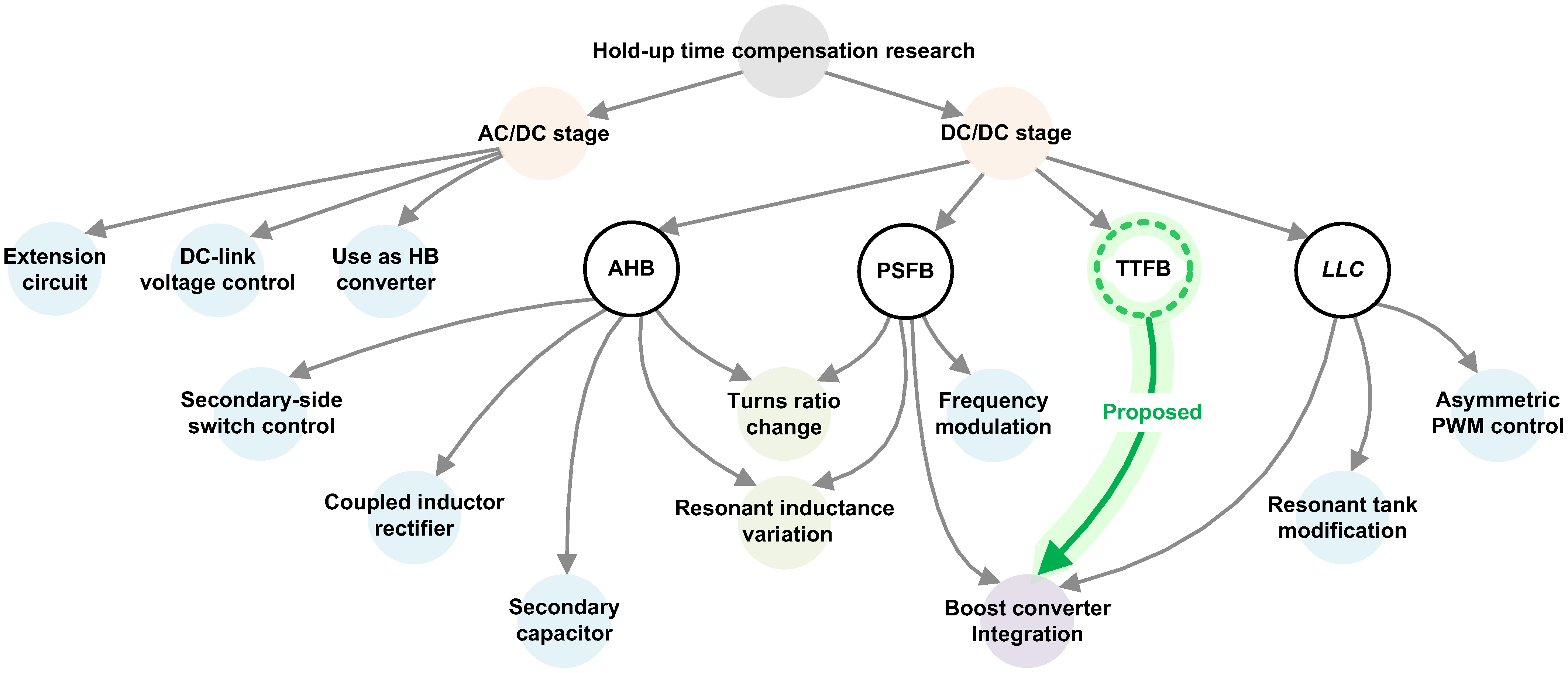

1. Introduction

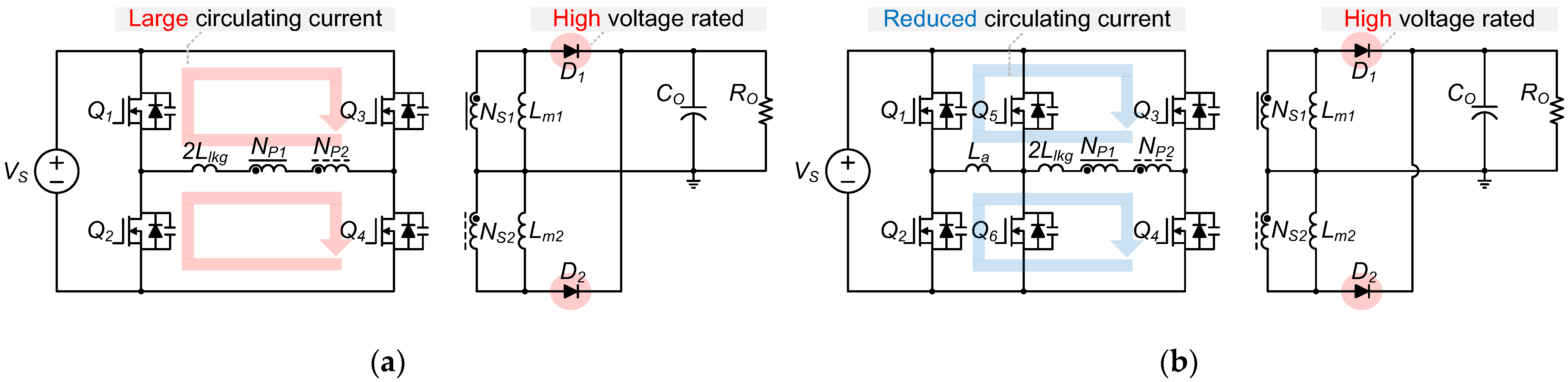

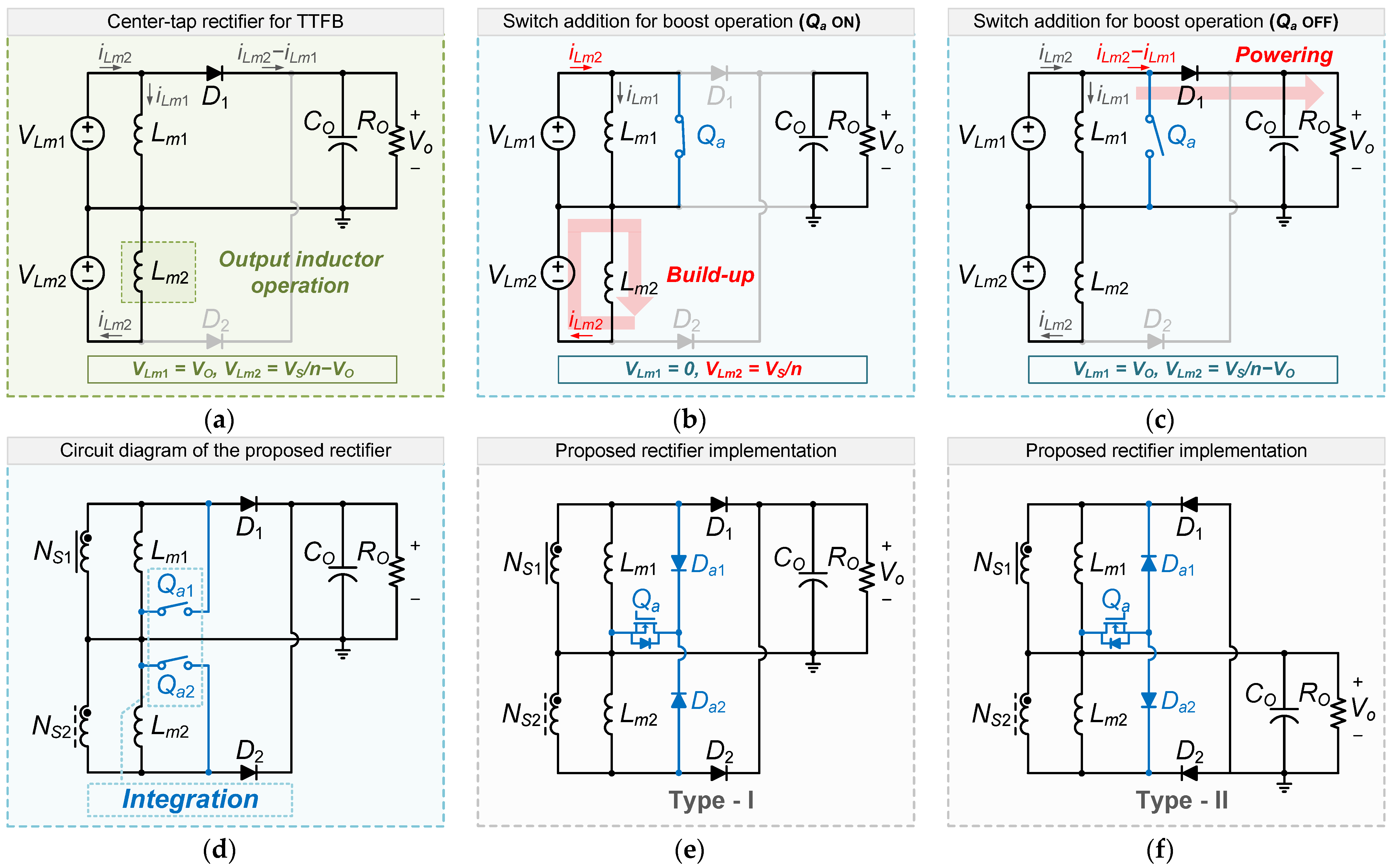

2. Features of the Proposed Converter

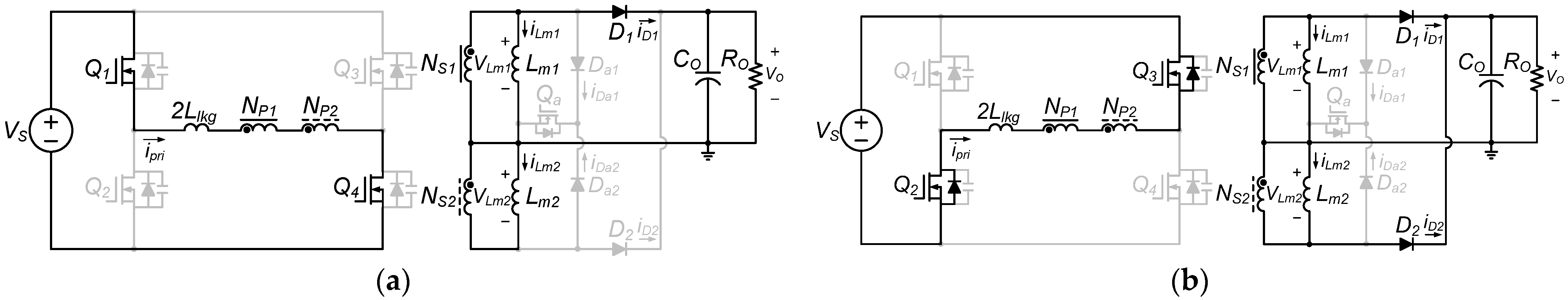

2.1. Derivation of the Proposed Converter

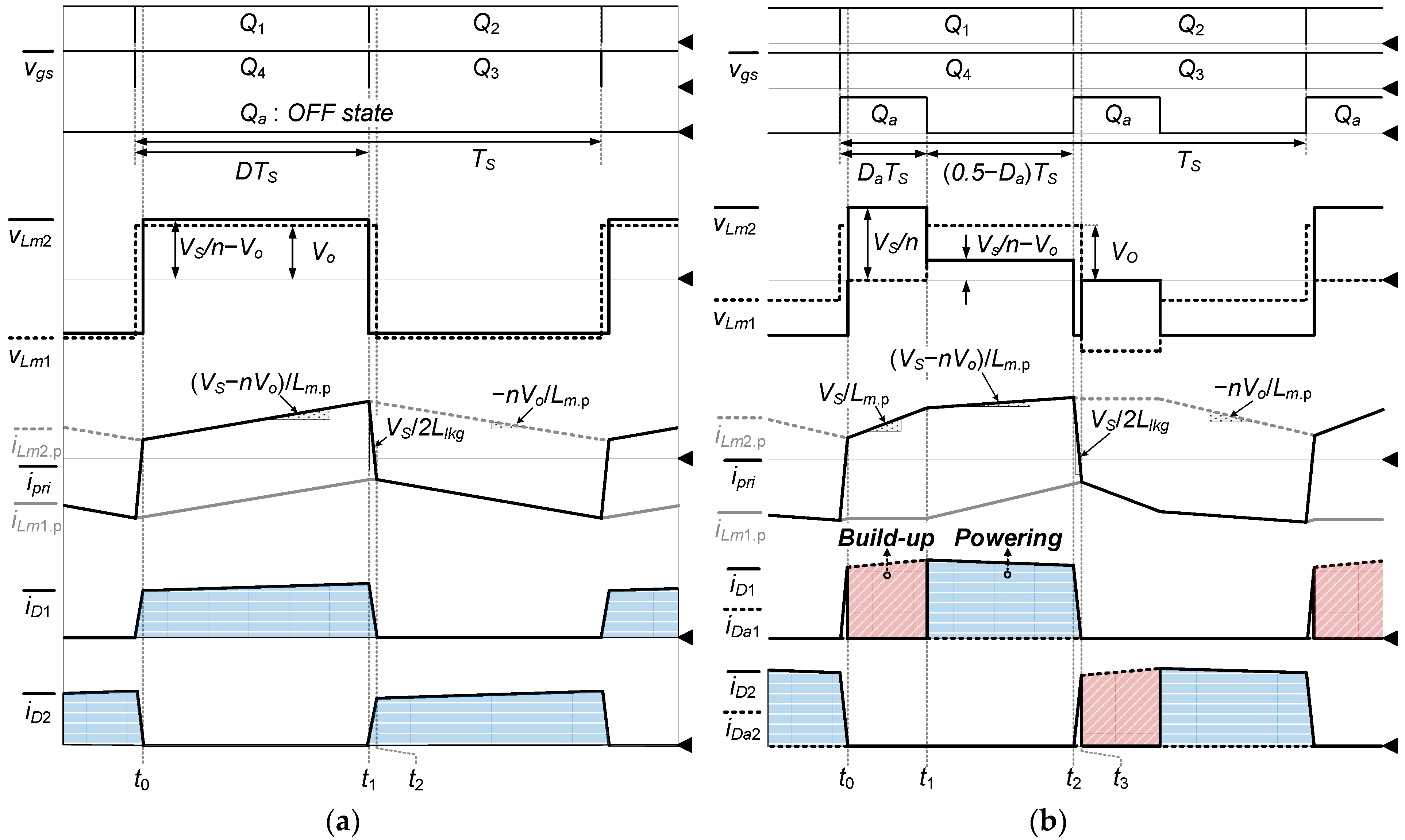

2.2. Operational Principles

- (1)

- The two transformers are identical, with the same turns ratio (Np1/Ns1 = Np2/Ns2 = n), magnetizing inductance (Lm1 = Lm2 = Lm), and leakage inductance (Llkg1 = Llkg2 = Llkg).

- (2)

- Magnetizing inductance Lm is sufficiently larger than leakage inductance Llkg (Lm >> Llkg).

- (3)

- The magnetizing inductances reflected to the primary side are denoted as Lm1.p and Lm2.p, and their values are equal to Lm.p.

- (4)

- Switches Q1–Q4 operate ideally, except for output capacitance and body diode.

- (5)

- The additional switch Qa operates ideally, except for body diode.

- (6)

- The duty loss is neglected, and the output voltage is constant.

2.2.1. Mode Analysis: Nominal State Operation

2.2.2. Mode Analysis: Hold-Up State Operation

3. Analysis of the Proposed Converter

3.1. Transformer Turns Ratio Design

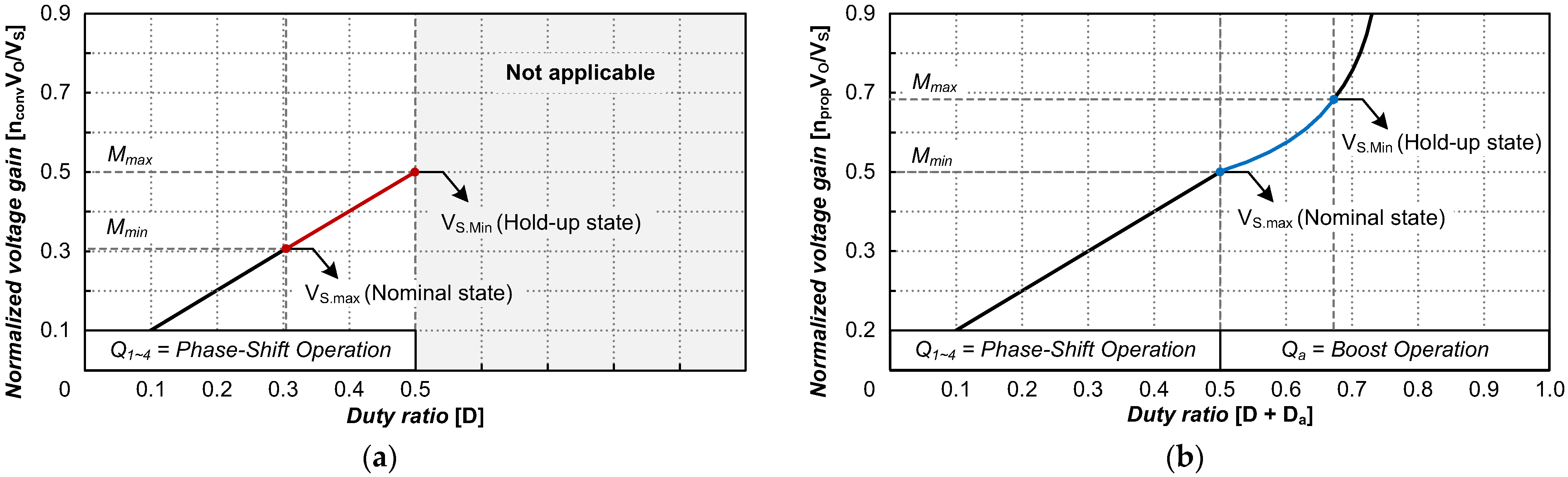

3.2. Voltage Gain Comparison

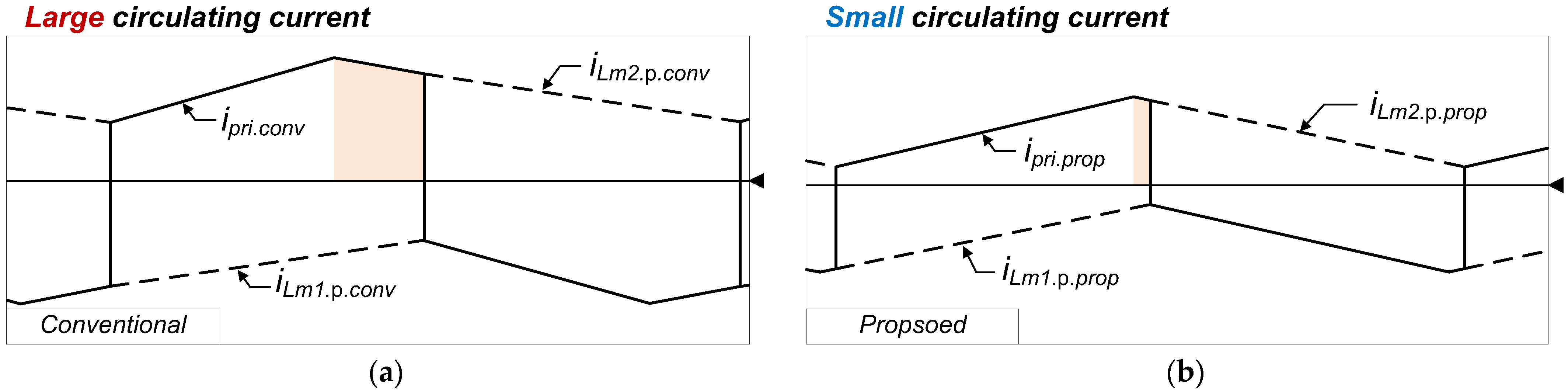

3.3. Circulating Current Comparison

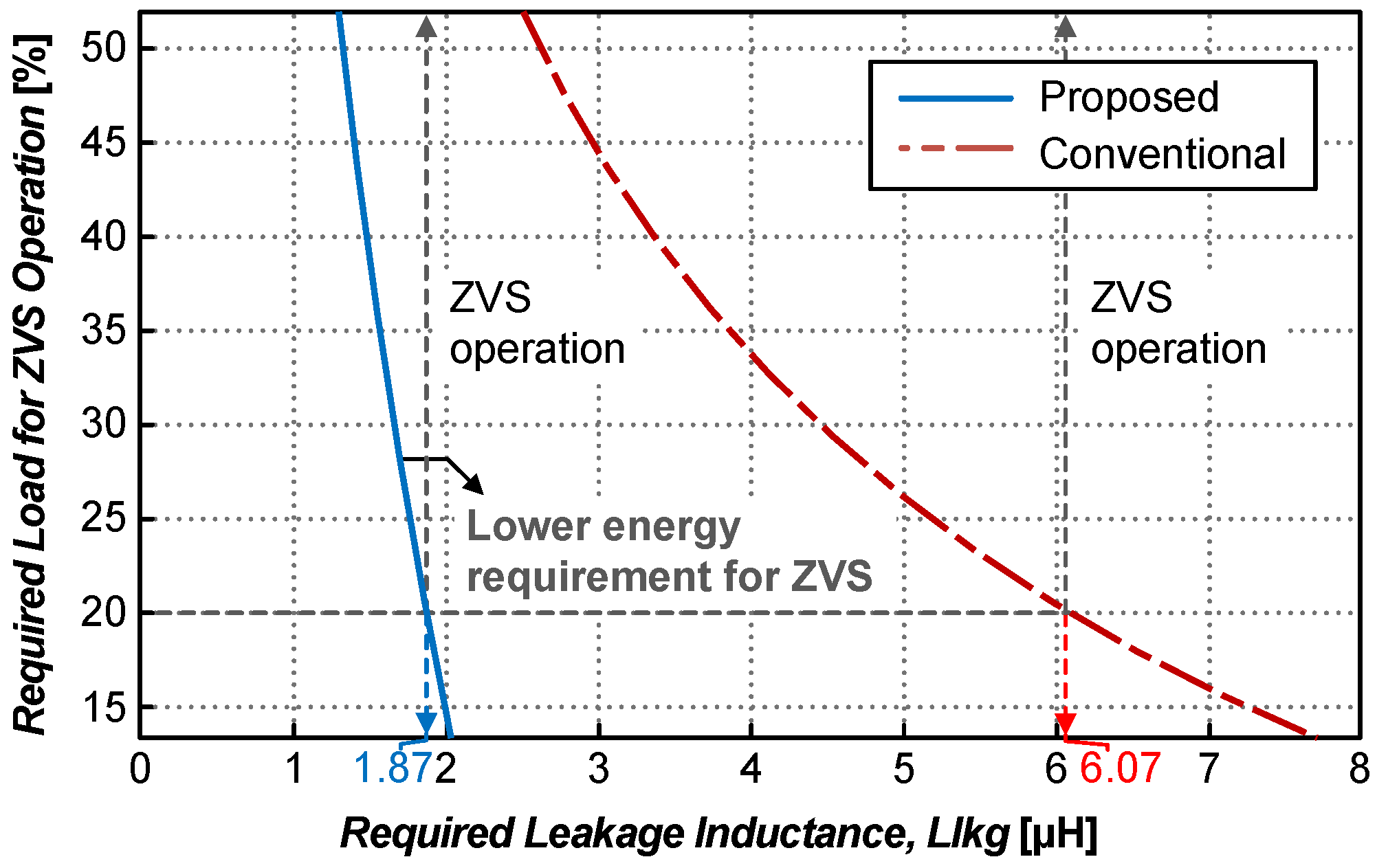

3.4. ZVS Condition

3.5. Voltage Stress on Rectifier Diodes

3.6. Conduction Losses in Power Devices

- Conduction losses in power MOSFETs:

- 2.

- Conduction losses in rectifier diodes:

3.7. Comparison with Previous Works

- Balanced rectifier stress: Unbalanced voltage stress on rectifier diodes requires components with different voltage ratings. The rectifier diodes in the proposed converter are balanced, enabling optimized component selection.

- Output inductor reduction: An inductor is one of the most expensive and bulky components in a system. Eliminating it reduces system cost, improves power density, and simplifies circuit design. The proposed converter eliminates the output inductor, reducing the complexity while maintaining high performance.

- Output current ripple: A larger peak-to-peak output current increases the current stress on the power semiconductor devices and imposes more stringent design requirements on the output capacitors. Since one transformer also functions as the output inductor, the proposed converter mitigates the output current ripple without requiring an additional inductor.

- Additional components: To reduce the cost, the number of additional components should be minimized. The proposed converter introduces only three additional semiconductor devices.

- Conducting components: To achieve high efficiency, the number of conducting devices should be minimized. As the proposed converter uses a center-tap rectifier, only one diode conducts during the nominal state.

- Control complexity: A simplified control algorithm lowers hardware cost and reduces the time and effort required for design and verification. The proposed controller operates at a fixed switching frequency and applies PWM only to an auxiliary switch during the hold-up state, thereby maintaining a relatively low complexity.

- Extended voltage gain range: Extending the voltage gain range preserves output regulation over a wide input range and allows optimal selection of design parameters—such as the transformer turns ratio and device ratings—to achieve high efficiency.

3.8. Link Capacitor Design

3.9. Comparision with Other Topologies

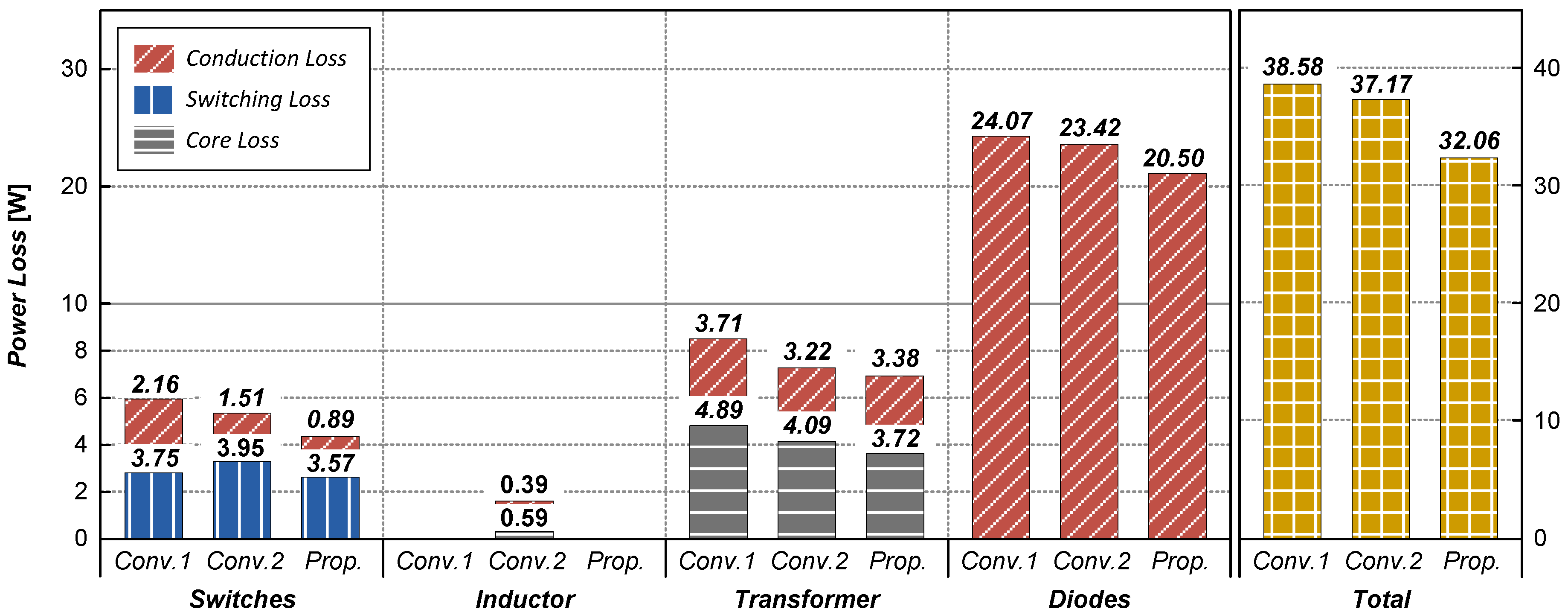

- Power Loss Comparison

- 2.

- Power Density Comparison

- 3.

- Cost Comparison

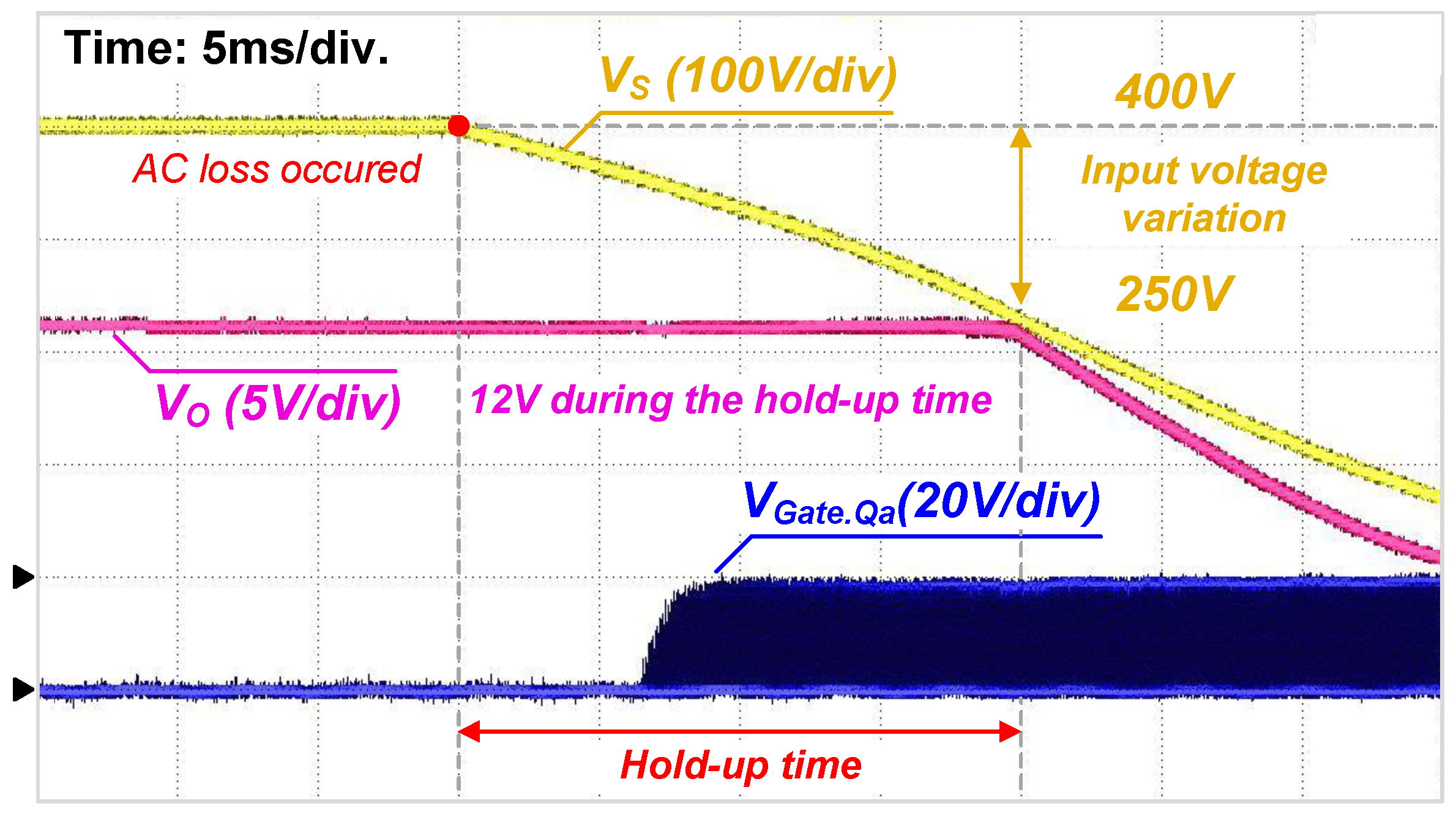

4. Experimental Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- EN 50155; Railway Applications—Rolling Stock—Electronic Equipment. European Committee for Electrotechnical Standardization (CENELEC): Brussels, Belgium, 2021.

- IEC 62040-3 Ed 3.0; Uninterruptible Power Systems (UPS)—Part 3: Method of Specifying the Performance and Test Requirements. International Electrotechnical Commission: Geneva, Switzerland, 2021.

- MIL-STD-704E; Aircraft Electric Power Characteristics. Department of Defense: Arlington, VA, USA, 1991.

- Wang, X.; Tian, F.; Batarseh, I. High efficiency parallel post regulator for wide range input DC-DC converter. IEEE Trans. Power Electron. 2008, 23, 852–858. [Google Scholar] [CrossRef]

- Lee, S.-H.; Jeong, S.-W.; Kim, J.-K. Integrated asymmetric half-bridge converter with boost operation for wide input voltage range. IEEE Trans. Ind. Electron. 2023, 70, 2472–2483. [Google Scholar] [CrossRef]

- Sun, Y.; Zhang, L.; Zhang, Z.; Wang, D. Overview of research status of DC bias and its suppression in power transformers. Energies 2022, 15, 8842. [Google Scholar] [CrossRef]

- Jang, Y.; Jovanovic, M.M.; Dillman, D.L. Hold-up time extension Circuit with integrated magnetics. IEEE Trans. Power Electron. 2006, 21, 394–400. [Google Scholar] [CrossRef]

- Takahashi, M.; Nishijima, K.; Nagao, M.; Sato, T.; Nabeshima, T. A high efficiency high power density AC-DC converter with holdup time extension capability. In Proceedings of the IEEE 33rd International Telecommunications Energy Conference (INTELEC), Amsterdam, The Netherlands, 9–13 October 2011; pp. 1–7. [Google Scholar]

- Lai, Y.-S.; Su, Z.-J.; Chen, W.-S. New Hybrid Control Technique to Improve Light Load Efficiency While Meeting the Hold-up Time Requirement for Two-Stage Server Power. IEEE Trans. Power Electron. 2014, 29, 4763–4775. [Google Scholar] [CrossRef]

- Baek, J.-I.; Kim, J.-K.; Lee, J.-B.; Youn, H.-S.; Moon, G.-W. A Boost PFC Stage Utilized as Half-Bridge Converter for High-Efficiency DC–DC Stage in Power Supply Unit. IEEE Trans. Power Electron. 2017, 32, 7449–7457. [Google Scholar] [CrossRef]

- Cho, K.-M.; Oh, W.-S.; Lee, K.-W.; Moon, G.-W. A new half bridge converter for the personal computer power supply. In Proceedings of the IEEE Power Electronics Specialists Conference, Rhodes, Greece, 15–19 June 2008; pp. 986–991. [Google Scholar]

- Han, J.-K.; Kim, J.-W.; Lee, B.-H.; Lai, J.-S.; Moon, G.-W. High-efficiency asymmetrical half-bridge converter with a new coupled inductor rectifier (CIR). IEEE Trans. Power Electron. 2019, 34, 11541–11552. [Google Scholar] [CrossRef]

- Bae, J.; Kim, J.-S.; Lee, M.; Han, J.-K.; Moon, G.-W. High-efficiency asymmetrical half-bridge converter with linear voltage gain. IEEE Trans. Power Electron. 2022, 37, 14850–14861. [Google Scholar] [CrossRef]

- Yeon, C.-O.; Lee, J.-B.; Lee, I.-O.; Moon, G.-W. Wide ZVS range asymmetric half-bridge converter with clamp switch and diode for high conversion efficiency. IEEE Trans. Ind. Electron. 2016, 63, 2862–2870. [Google Scholar] [CrossRef]

- Park, M.-H.; Yeon, C.-O.; Park, J.-S.; Lim, C.-Y.; Han, J.-K.; Moon, G.-W. Wide-range ZVS asymmetric half-bridge converter with clamping switches for small DC offset current. In Proceedings of the IEEE 8th International Power Electronics and Motion Control Conference, Hefei, China, 22–26 May 2016; pp. 2262–2269. [Google Scholar]

- Kathiresan, R.; Das, P.; Reindl, T.; Panda, S.K. A Novel ZVS DC-DC Full-Bridge Converter With Hold-up Time Operation. IEEE Trans. Ind. Electron. 2017, 64, 4491–4500. [Google Scholar] [CrossRef]

- Lin, B.-R. Low-primary current and wide hold-up time DC–DC converter: Analysis and implementation. IET Power Electron. 2018, 11, 1822–1829. [Google Scholar] [CrossRef]

- Kim, Y.-D.; Cho, K.-M.; Kim, D.-Y.; Moon, G.-W. Wide-Range ZVS phase-shift full-bridge converter with reduced conduction loss caused by circulating current. IEEE Trans. Power Electron. 2013, 28, 3308–3316. [Google Scholar] [CrossRef]

- Han, J.-K.; Kim, K.-W.; Lim, C.-Y.; Kim, D.; Moon, G.-W. A new full-bridge converter with phase-shifted coupled inductor rectifier. In Proceedings of the 10th International Conference on Power Electronics and ECCE Asia, Busan, Republic of Korea, 27–30 May 2019; pp. 2874–2879. [Google Scholar]

- Kim, B.-C.; Park, K.-B.; Moon, G.-W. Asymmetric PWM control scheme during hold-up time for LLC resonant converter. IEEE Trans. Ind. Electron. 2012, 59, 2992–2997. [Google Scholar] [CrossRef]

- Lee, J.-B.; Kim, J.-K.; Baek, J.-I.; Kim, J.-H.; Moon, G.-W. Resonant capacitor on/off control of half-bridge LLC converter for high-efficiency server power supply. IEEE Trans. Ind. Electron. 2016, 63, 5410–5415. [Google Scholar] [CrossRef]

- Teng, J.-H.; Chen, S.-S.; Chou, Z.-X.; Liu, B.-H. Novel half-bridge LLC resonant converter with variable resonant inductor. IEEE Trans. Ind. Appl. 2023, 59, 6952–6962. [Google Scholar] [CrossRef]

- Jeong, Y.; Lee, M.-S.; Park, J.-D.; Kim, J.-K.; Rorrer, R.A.L. Hold-up time compensation circuit of half-bridge LLC resonant converter for high light-load efficiency. IEEE Trans. Power Electron. 2020, 35, 13126–13135. [Google Scholar] [CrossRef]

- Kim, J.-W.; Moon, G.-W. A new LLC series resonant converter with a narrow switching frequency variation and reduced conduction losses. IEEE Trans. Power Electron. 2014, 29, 4278–4287. [Google Scholar] [CrossRef]

- Koo, G.-B.; Moon, G.-W.; Youn, M.-J. Analysis and design of phase shift full bridge converter with series-connected two transformers. IEEE Trans. Power Electron. 2004, 19, 411–419. [Google Scholar] [CrossRef]

- Leu, Y.-H.; Chen, C.-L. Analysis and design of two-transformer asymmetrical half-bridge converter. In Proceedings of the IEEE Power Electronics Specialists Conference, Cairns, Australia, 23–27 June 2002; pp. 943–948. [Google Scholar]

- Arias, M.; Diaz, M.F.; Lamar, D.G.; Linera, F.M.F.; Sebastián, J. Small-signal and large-signal analysis of the two-transformer asymmetrical half-bridge converter operating in continuous conduction mode. IEEE Trans. Power Electron. 2014, 29, 3547–3562. [Google Scholar] [CrossRef]

- Park, C.; Mitsunao, F.; Takahashi, H.; Li, Z.; Wu, B. On-On and On-Off mode Phase-Shifted Full-Bridge TriMagiC Converter™ with Liqualloy™ Planar Transformers. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition, Houston, TX, USA, 20–24 March 2022; pp. 701–708. [Google Scholar]

- Lee, D.-W.; Youn, H.-S.; Kim, J.-K. Development of phase-shift full-bridge converter with integrated winding planar two-transformer for LDC. IEEE Trans. Transp. Electrific. 2023, 9, 1215–1226. [Google Scholar] [CrossRef]

- Yoon, H.-K.; Han, S.-K.; Choi, E.-S.; Moon, G.-W.; Youn, M.-J. Zero-voltage switching and soft-commutation two-transformer full-bridge PWM converter using the voltage-ripple. IEEE Trans. Ind. Electron. 2008, 55, 1478–1488. [Google Scholar] [CrossRef]

- Koo, G.-B.; Moon, G.-W.; Youn, M.-J. New zero-voltage-switching phase-shift full-bridge converter with low conduction losses. IEEE Trans. Ind. Electron. 2005, 52, 228–235. [Google Scholar] [CrossRef]

- Jeong, S.-W.; Lee, S.-H.; Kwon, D.-H.; Kim, J.-Y.; Kim, J.-K. Two-transformer phase-shift full-bridge converter with a new rectifier for reducing conduction loss. IEEE Trans. Power Electron. 2023, 38, 15634–15644. [Google Scholar] [CrossRef]

- Yao, C.; Ruan, X.; Wang, X. Automatic mode-shifting control strategy with input voltage feed-forward for full-bridge-boost dc–dc converter suitable for wide input voltage range. IEEE Trans. Power Electron. 2015, 30, 1668–1682. [Google Scholar] [CrossRef]

- He, Y.; Perreault, D.J. Diode Evaluation and Series Diode Balancing for High-Voltage High-Frequency Power Converters. IEEE Trans. Power Electron. 2020, 35, 6301–6314. [Google Scholar] [CrossRef]

| Previous Work | [13] | [14] | [17] | [18] | [22] | [24] | Proposed |

|---|---|---|---|---|---|---|---|

| Topology | AHB | AHB | PSFB | PSFB | LLC | LLC | TTFB |

| Key Idea | Secondary Capacitor | Turns Ratio Change | Turns Ratio Change | Resonant Inductance Variation | Resonant Tank Modification | Integrated Boost Converter | Integrated Boost Converter |

| 1. Balanced Rectifier Stress | Unbalanced | Unbalanced | Balanced | Balanced | Balanced | Balanced | Balanced |

| 2. Output Inductor Reduction | No | No | No | No | Yes | Yes | Yes |

| 3. Output Current Ripple | Low | Low | Low | Low | High | High | Low |

| 4. Additional Components | 3 | 3 | 8 | 3 | 5 | 2 | 3 |

| 5. Conducting Components * | 2 | 1 | 1 | 1 | 1 | 2 | 1 |

| 6. Control Complexity | Simple | Moderate | Simple | Moderate | Complex | Complex | Moderate |

| 7. Extended Voltage Gain Range | No | Yes | Yes | No | Yes | Yes | Yes |

| Topology | LLC | TTFB | Prop. |

|---|---|---|---|

| Power Density [W/cm3] | 3.64 | 3.02 | 4.62 |

| Topology | LLC | TTFB | Prop. |

|---|---|---|---|

| Total Cost | USD 17.4 | USD 16.57 | USD 19.53 |

| Components | Conventional 1 [25] | Conventional 2 [18] | Proposed | |

|---|---|---|---|---|

| Switch | Q1–Q4 | IPP60R160P7 (VDS = 650 V, RDS(on) = 160 mΩ) | IPP60R160P7 (VDS = 650 V, RDS(on) = 160 mΩ) | |

| Q5–Q6 | – | IPP60R160P7 (VDS = 650 V, RDS(on) = 160 mΩ) | – | |

| Qa | – | – | IRFB7530PBF (VDS = 60 V, RDS(on) = 1.65 mΩ) | |

| Diode | D1, D2 | STPS40M80CT (VR = 80 V, VF = 0.475 V) | STPS40M60CT (VR = 60 V, VF = 0.385 V) | |

| Da1, Da2 | – | – | ||

| Transformer | T1, T2 | Lm.p = 300 μH, Llkg.p = 13 μH (Core:PQ3220) | Lm.p = 300 μH, Llkg.p = 14 μH (Core:PQ3220) | |

| Turns ratio (NP:NS) = 27:3 | Turns ratio (NP:NS) = 42:3 | |||

| strands strands | strands strands | |||

| Inductor | La | – | 100 μH (Core:PQ2020) | – |

| turns | ||||

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lee, B.-S.; Kim, Y.-A.; Kim, J.-K. A Novel Two-Transformer Full-Bridge Converter with Integrated Boost Converter for Hold-Up Time Compensation. Energies 2025, 18, 4268. https://doi.org/10.3390/en18164268

Lee B-S, Kim Y-A, Kim J-K. A Novel Two-Transformer Full-Bridge Converter with Integrated Boost Converter for Hold-Up Time Compensation. Energies. 2025; 18(16):4268. https://doi.org/10.3390/en18164268

Chicago/Turabian StyleLee, Bom-Seok, Yun-Ah Kim, and Jae-Kuk Kim. 2025. "A Novel Two-Transformer Full-Bridge Converter with Integrated Boost Converter for Hold-Up Time Compensation" Energies 18, no. 16: 4268. https://doi.org/10.3390/en18164268

APA StyleLee, B.-S., Kim, Y.-A., & Kim, J.-K. (2025). A Novel Two-Transformer Full-Bridge Converter with Integrated Boost Converter for Hold-Up Time Compensation. Energies, 18(16), 4268. https://doi.org/10.3390/en18164268