1. Introduction

The increasing deployment of DC distribution systems in renewable energy integration, shipboard microgrids, and high-efficiency data centers has introduced new challenges regarding fault protection. Unlike AC systems, DC networks lack natural current zero-crossing, making fault current interruption more difficult and resulting in prolonged arcing and higher stress on switching devices [

1,

2]. Moreover, DC fault currents rise rapidly due to the low impedance of the system, and their effective suppression requires fast-acting protection mechanisms, such as those demonstrated in hybrid MMC-based HVDC systems [

3].

While DC CBs are essential for protection, their performance may be constrained during severe transient events, due to inherent limitations in terms of switching speed and energy dissipation capacity [

4]. Hybrid-type DC CBs, which combine mechanical and solid-state switches, have been proposed to improve interruption speed. However, they still face practical challenges such as high implementation costs, a bulky structure, and increased component stress during fault clearing, which hinder their adoption in compact or large-scale DC grid applications [

5,

6].

To address these limitations, fault current limiters (FCLs) have been explored as auxiliary protection devices that mitigate the stress imposed on DC circuit breakers. By suppressing peak fault currents before interruption, FCLs enhance protection coordination and improve system reliability [

7]. Among the various technologies, superconducting FCLs (SFCLs) have gained attention due to their ability to introduce rapid impedance changes with negligible steady-state losses. However, their dependence on cryogenic infrastructure limits their applicability in practical MVDC and HVDC systems. Nevertheless, recent studies have demonstrated their feasibility, for example, in an overvoltage-triggered SFCL scheme for multiterminal HVDC networks [

8], as well as in hybrid SFCL topologies combining resistive and superconducting paths for MVDC shipboard applications [

9]. Additional variants, such as modified flux-coupling-type SFCLs with parallel superconducting branches, have also been studied for their fault current limiting performance and applicability to DC system protection [

10].

Due to the challenges associated with cryogenic cooling and system complexity, non-superconducting FCL approaches have gained increasing attention. These include self-adaptive FCLs integrated with hybrid solid-state DC breakers [

11], impedance-modulated circuits for MMC-based HVDC systems [

12], and self-powered solid-state FCLs tailored for VSC-based DC distribution networks [

13]. While these techniques offer advantages in terms of selectivity and response speed, several limitations remain. Fuse-based methods suffer from non-reusability and limited tunability, while control-intensive non-superconducting FCLs depend on real-time sensing and active coordination, which complicates system integration.

In contrast, the proposed PCS-based fault current limiter (FCL) achieves rapid fault isolation through passive triggering and minimal control circuitry, while maintaining structural simplicity and adaptability. Conventional fuse-based solutions suffer from non-reusability and limited tunability, whereas control-intensive FCLs rely on real-time sensing and coordination, complicating system integration. To overcome these limitations, pyro conduction switches (PCSs) and pyro-fuses have emerged as compact and effective alternatives for DC fault isolation. These devices utilize pyrotechnic actuators to achieve ultra-fast mechanical disconnection with minimal control overhead [

14]. Their effectiveness has been demonstrated in applications such as eVTOL systems [

15] and fusion-based protection devices [

16,

17], where arc dynamics have been further analyzed using enhanced Mayr and Schavemaker models [

18]. However, their application as FCLs in DC distribution systems remains limited, especially in configurations requiring coordination with auxiliary protection components [

19].

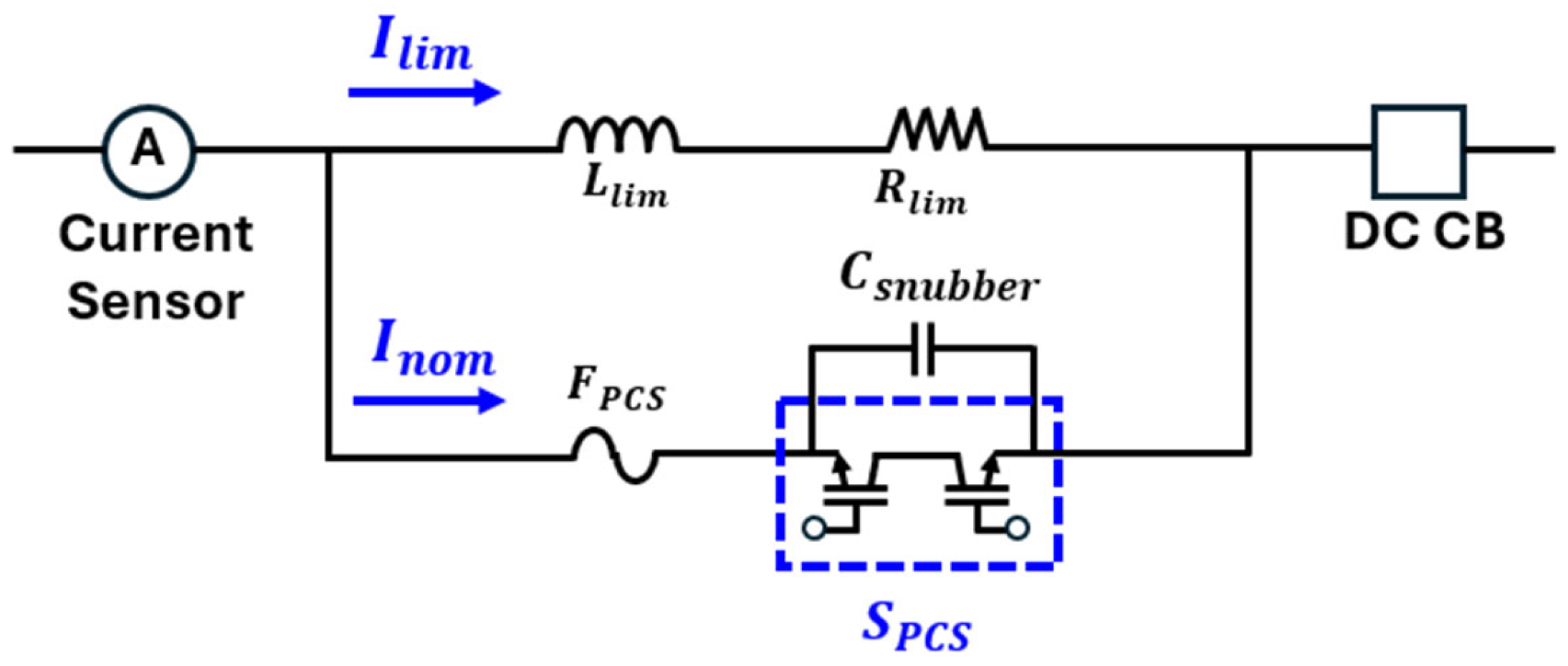

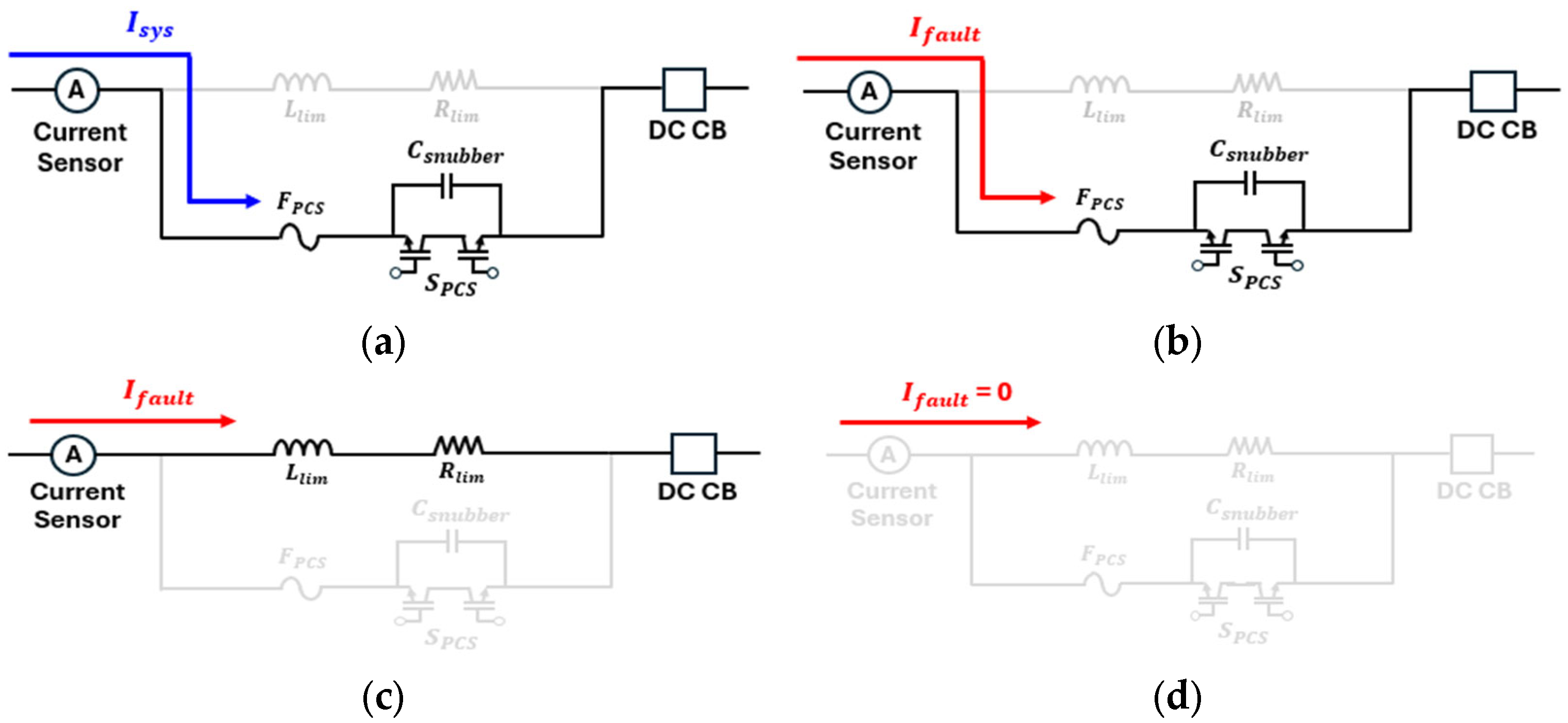

In this study, a hybrid FCL incorporating a PCS is proposed for DC distribution systems. The proposed design employs a pyro fuse for fast isolation, an IGBT switch to control conduction, a limiting inductor to moderate the fault current’s rise rate, and a damping resistor for energy absorption. Once a fault is detected, the main conduction branch is broken, redirecting the current into a current limiting branch, which suppresses the fault peak and reduces stress on the DC circuit breaker.

Therefore, this study proposes and validates a compact and tunable fault current limiter (FCL) based on a pyro conductor switch (PCS) for application in DC distribution systems. The main contributions of this research are as follows: the development of a hybrid FCL topology combining passive triggering and fast current suppression using a pyro fuse and IGBT; the establishment of a PSCAD/EMTDC-based simulation framework to evaluate performance under various system conditions; the construction and testing of a laboratory-scale prototype to validate the simulation results; and the demonstration of performance tunability through parametric analysis, supporting practical deployment in MVDC protection applications. These contributions collectively aim to advance scalable and reliable protection strategies for next-generation DC distribution networks.

4. PCS Fault Current Limiter Prototype

Based on the simulation results, which verified the effectiveness of the proposed PCS fault current limiter under various operating conditions, a prototype was designed and developed to demonstrate its performance in a laboratory setting. The experimental setup was constructed to replicate the key parameters observed in the simulations, enabling a consistent and meaningful evaluation of the limiter’s current suppression and interruption characteristics.

4.1. Prototype and Test Bed

The circuit diagram shown in

Figure 9 presents the experimental test-bed configuration that was developed to evaluate the performance of the proposed PCS fault current limiter. The setup consists of two main sections: the DC power source and the PCS facility. On the DC power source side, a three-phase diode bridge rectifier converts the AC input (

) into DC voltage (

), which is stabilized using a capacitor,

C. This portion represents the controlled DC power supply that was used in the experiment.

On the PCS facility side, the PCS fault current limiter circuit is implemented. When the making switch () is closed, the current flows through the current limiting components and . The parallel path includes the , and . Under normal operating conditions, remains turned on to bypass the limiter. When is turned on, turns off in order to force the current through the limiting path ( and ), thereby suppressing the current. A current sensor is placed before the load to measure and the is responsible for the final current interruption. The load is represented by , which is a fixed resistive element with a value of 10 Ω.

The experimental setup, as illustrated in

Figure 10, consists of a DC power source, a PCS fault current limiter unit, and a load system integrated with the measurement and control components. The key components, including the limiting elements (

and

), IGBT switches, pyro fuse, and DC relay, are installed in a modular rack-based structure to facilitate ease of configuration and monitoring. The controller unit is responsible for managing the timing and coordination of switching elements during the test sequences.

Table 2 summarizes the main specifications of the devices used in the test bed. Both the making IGBT and PCS IGBT are rated at 1700 V and 150 A, with a short-term withstanding capability of up to 950 A. The high-speed pyro fuse is capable of interrupting 60 A within 50–80 ms under 600

or 500

conditions. The DC relay operates with a rated voltage of 1000 Vdc and a current rating of 100 A, enabling safe disconnection after fault current suppression. The current sensor used in this study is the HCP8150A model from Cybertek (Shenzhen City, China), with a continuous maximum input range of 150 A.

4.2. Test Results

The experiments were performed under uncontrolled ambient laboratory conditions as environmental factors such as temperature and humidity were not expected to significantly affect the results. Due to the nature of the test setup, each condition was verified through a single trial, which was sufficient to confirm functional operation.

Figure 11 presents the experimental measurement results for the PCS fault current limiter during a 50 A current limiting test. At t = 0 s, the making switch is turned on, allowing current to flow through the PCS circuit. Initially, the IGBT switch conducts and forms the main current path. At t = 0.2 ms, the IGBT is turned off, causing the current to be redirected into the current-limiting branch. The current is then suppressed to reach a steady value, indicated as the limiting current, and is maintained for approximately

= 0.024 s.

Figure 12 presents a comparison between the simulation and the experimental results of the PCS fault current limiter operation under Case I conditions. The plot shows the load current profiles obtained from the PSCAD simulation and experimental measurement during the current limiting process. The

is turned on at time zero, initiating current flow through the system. As the current increases, the PCS fault current limiter activates its limiting function, and the current stabilizes at approximately 50 A. This limiting condition is maintained for a duration of about

= 0.024 s.

The experimental results closely follow the simulation curve, in terms of both current magnitude and response time. Minor oscillations observed in the experimental data reflect real-world switching and measurement noise, but the overall waveform trend aligns well with the simulated response. At approximately 24 ms, the DC relay is turned on, resulting in a sharp drop in current and a successful interruption. This close agreement between PSCAD and experimental results indicates the accuracy of the simulation model and suggests that the PCS fault current limiter performs reliably under the tested conditions.

Figure 13 presents the experimental results for four case studies (Case I–Case IV), demonstrating the current limiting performance of the PCS fault current limiter under varying system impedance conditions. The figure shows the measured load current profiles after the making switch is turned on at t = 0 s. As the

and

increases, the limited current decreases accordingly, indicating that the PCS fault current limiter can adjust its performance according to circuit conditions. The specific resistance, inductance, limited current, and calculated limiting percentages for each case are summarized in

Table 3. The results show that adjusting the current-limiting parameters, such as

and

, enables effective control of fault current suppression. For example, Case I yields the highest limited current due to lower impedance, while Case IV achieves the lowest fault current with higher limiting values. These findings demonstrate the tunability of the proposed FCL design to meet various protection requirements.

Figure 14 illustrates the sum of energy dissipated in

and

under different system conditions, showing an increasing trend up to Case III, followed by a slight decrease in Case IV due to a greater current reduction. The interruption time remains consistently at around 21 ms across all cases and is primarily determined by the operating delay of the DC relay, rather than a variation in system impedance. It should be noted that the applied fault current remained below the pyro fuse activation threshold and no melting or disconnection occurred. The observed suppression reflects the system’s behavior prior to fuse triggering. Further tests under higher fault current conditions are planned to evaluate full-scale fuse operation.

The impedance-dependent limiting characteristics demonstrated in this study are consistent with previous findings, where resistance and inductance values were shown to directly influence the fault current suppression in DC systems. In particular, an R–L-based current limiting method, when applied to a ± 10 kV VSC-DC distribution network, indicated that increasing the impedance enhances current suppression effectiveness, which supports the tunability of the proposed PCS-based FCL design [

24]. In addition, the close agreement between the simulation results and the experimental measurements indicates the accuracy and reliability of the developed model. Such consistency aligns with prior studies that emphasized the role of simulation-based design for optimizing protection strategies in low-voltage DC distribution networks [

25].

Experimental validation efforts in the literature also demonstrate that solid-state fault current limiters can achieve a limiting performance that closely matches simulation predictions when the switching sequences and impedance parameters are properly coordinated [

26,

27]. These results collectively strengthen the practical feasibility of the PCS-based FCL architecture proposed in this work, particularly for compact and modular DC distribution environments.

5. Discussion

The proposed PCS-based FCL was experimentally validated under four distinct limiting impedance conditions, demonstrating strong consistency with the simulation results. The measured limited current values and suppression rates closely matched those obtained from PSCAD/EMTDC simulations, indicating the validity of the proposed model and its applicability to practical DC protection scenarios. This consistency indicates that the adopted simulation methodology can reliably predict real-world performance, thereby reducing the need for repeated hardware iterations during the design phase.

Variations in the limiting branch parameters clearly demonstrated the dependence of current suppression on impedance. In particular, increasing both resistance and inductance led to a notable reduction in peak fault current, validating the tunability of the PCS-based FCL. Such adjustability allows the limiter to be configured for diverse system protection requirements, including selective operation and coordination with other protective devices. The switching components, including the IGBT and pyro conductor, operated stably and consistently in all test cases, enabling the rapid diversion of fault current into the limiting path.

Beyond its technical performance, the PCS-based FCL features a modular topology that facilitates adaptation to various voltage levels through parameter scaling. The use of passive components and a simple control scheme further enhance its integration potential. Future work should assess the thermal endurance of the limiting resistor under repeated fault conditions and examine the long-term mechanical reliability of the PCS, including its susceptibility to premature triggering caused by vibration or ambient heat. Moreover, as the PCS is a single-use switching component, its deployment may raise cost and maintenance concerns, particularly in systems requiring frequent fault handling or high availability. These practical considerations will be essential for extending the applicability of the proposed design to distributed and multi-terminal DC systems. In addition, the current ripples observed in the experimental waveforms (e.g., in

Figure 4) suggest that performance could be improved further by implementing suitable filtering and control strategies, especially for sensitive downstream equipment.

6. Conclusions

In this study, a PCS-based fault current limiter was proposed and validated for DC distribution systems through PSCAD/EMTDC simulations and laboratory-scale experiments. The limiter demonstrated tunable fault current suppression, with peak current reductions ranging from 17.2% to 47.7%, consistent interruption times of approximately 21 ms, and maximum energy dissipation reaching 196.6 J. The close agreement between the simulation and the experimental results supports the reliability of the proposed modeling framework for predictive design and performance tuning.

The modular architecture and minimal control requirements make the PCS-based FCL a promising solution for compact and scalable DC protection. Potential applications include DC-fed data centers, EV charging infrastructure, and renewable-integrated microgrids. While the proposed limiter showed stable operation under low-voltage conditions, further validation at medium-voltage levels is needed to assess its dielectric strength and endurance under repetitive fault conditions. Additionally, the one-time usability of the pyro fuse remains a practical limitation.

Future work will enhance the thermal and mechanical robustness of a PCS-based FCL for use in repeated fault conditions and high-energy environments, including improvements in pyro housing durability and thermal management. The design will be scaled to MVDC levels, with an emphasis on insulation coordination, and protection schemes will be developed to enable selective coordination with high-speed DC breakers in multi-terminal networks.