Modeling and Experimental Validation of a Voltage-Controlled Split-Pi Converter Interfacing a High-Voltage ESS with a DC Microgrid

Abstract

:1. Introduction

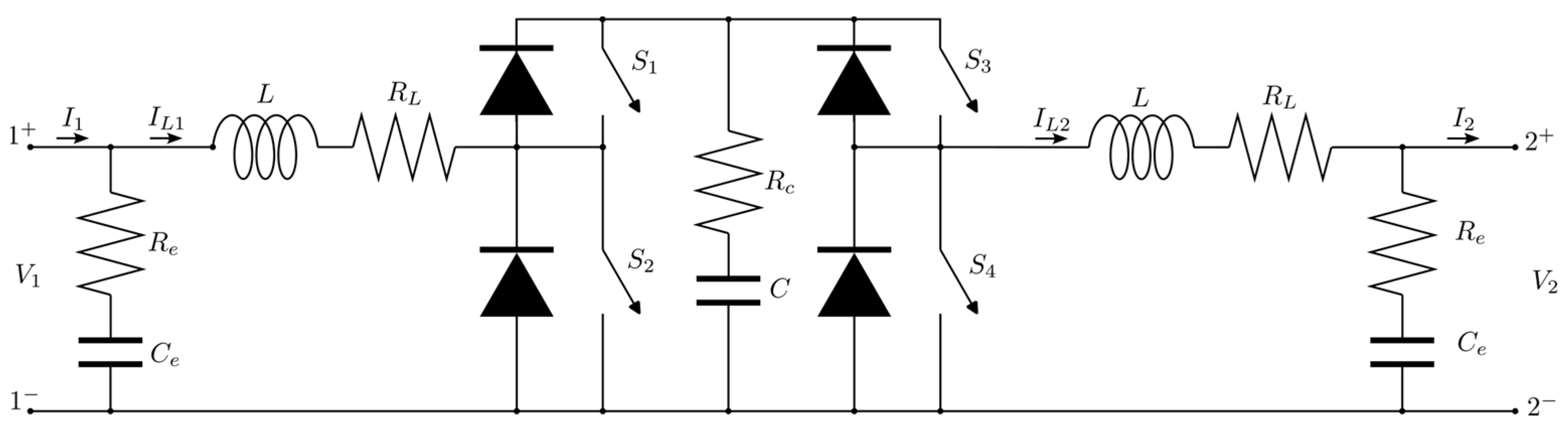

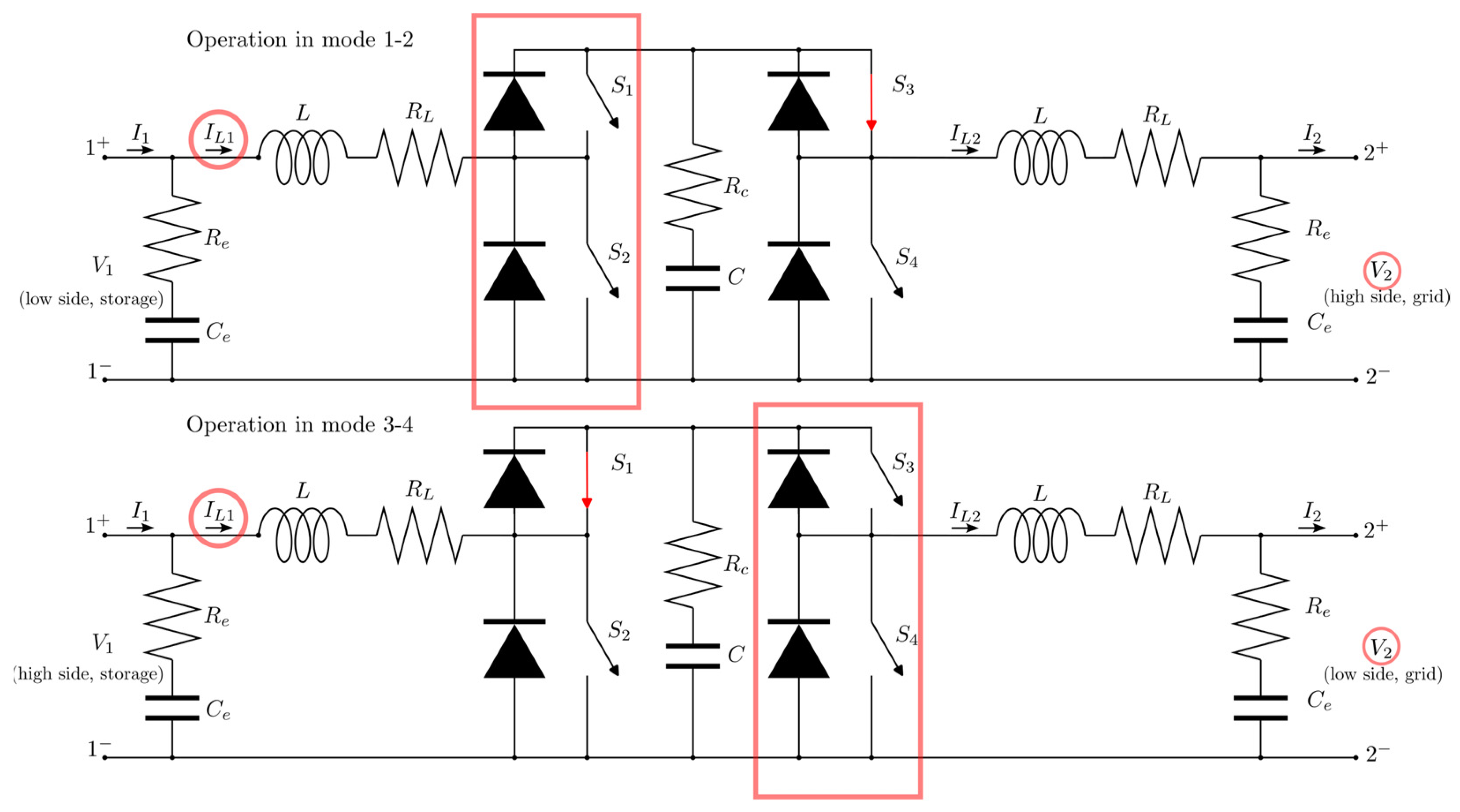

2. Comparison between Operation in Modes 1–2 vs. Modes 3–4 and Overview of Previous Work

2.1. Comparison between Operation in Modes 1–2 vs. Modes 3–4

2.2. Overview of the Case Study

2.3. DC Microgrid Scenarios

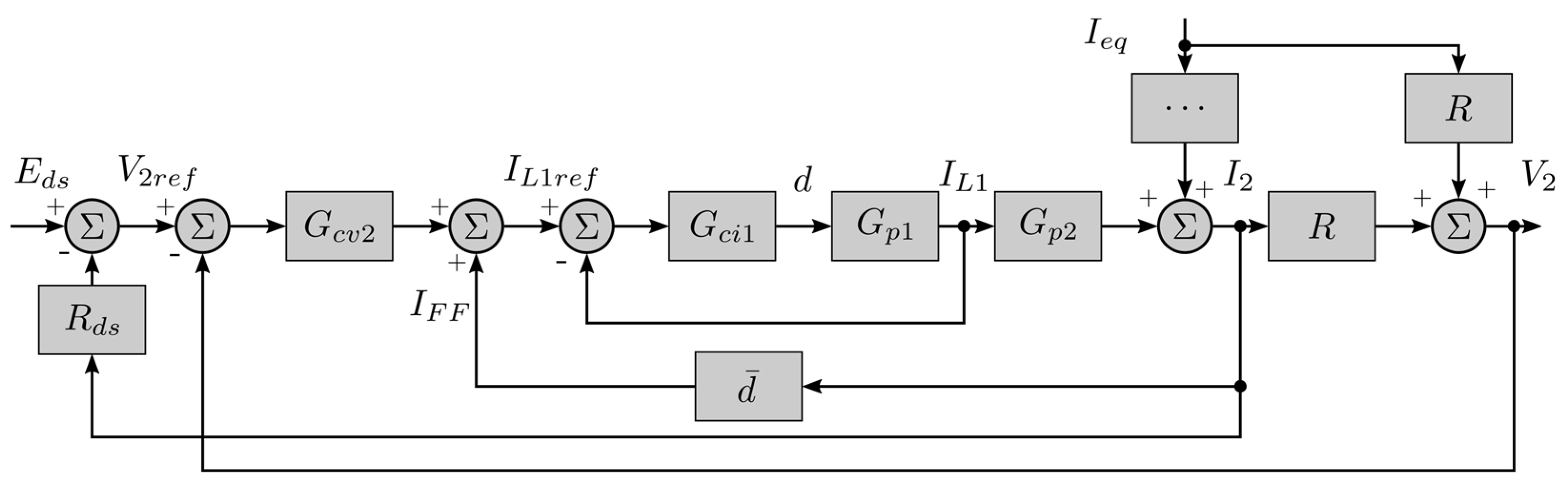

2.4. Closed-Loop Control Scheme

3. State-Space Model and Control System Design

3.1. State-Space Model

3.2. Control System Design

4. Simulation Results

- Solver type: variable-step

- Solver: ode23tb (stiff/TR-BDF2)

- Max step size: 1/(10·Fsw)

- Solver reset method: robust.

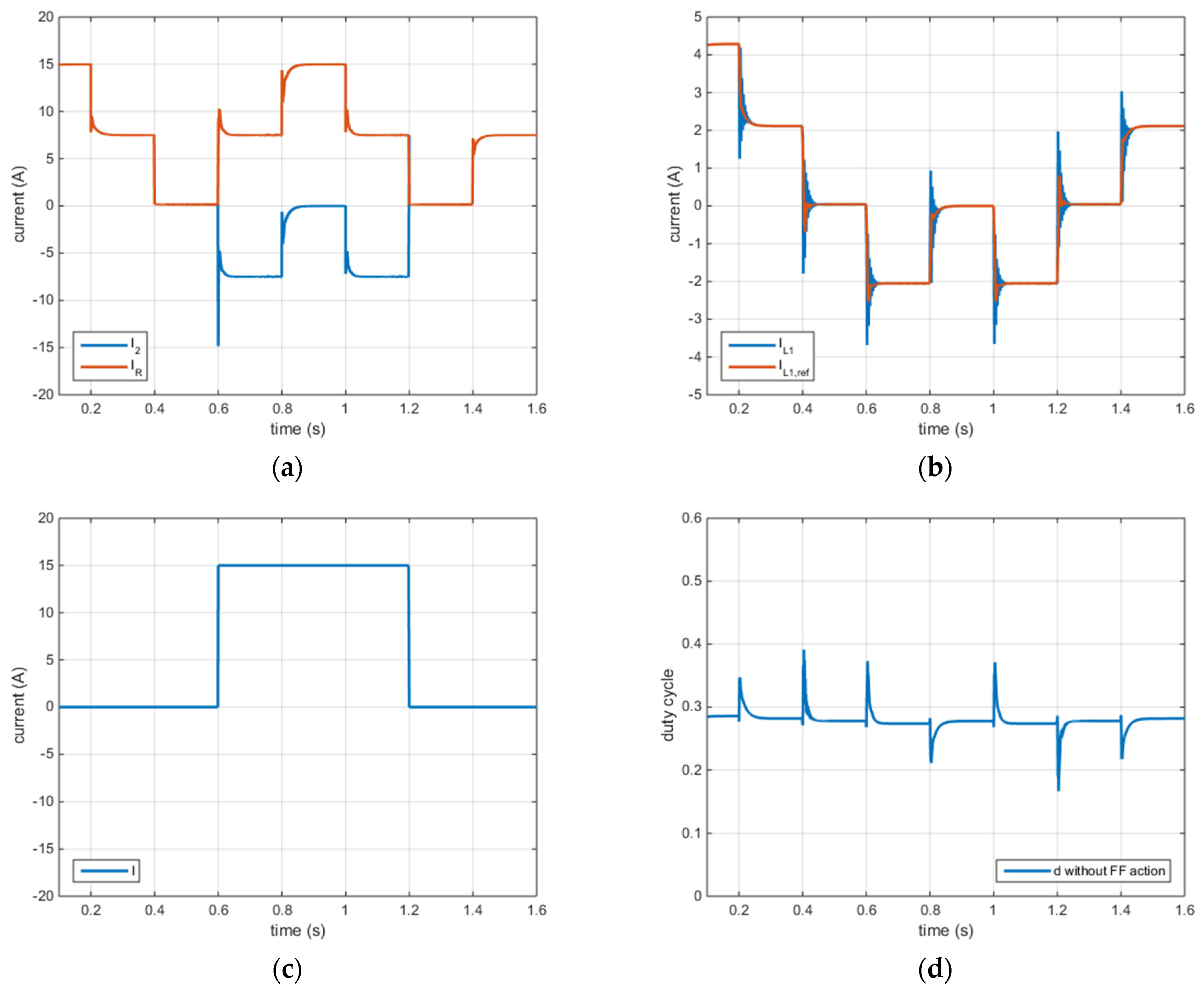

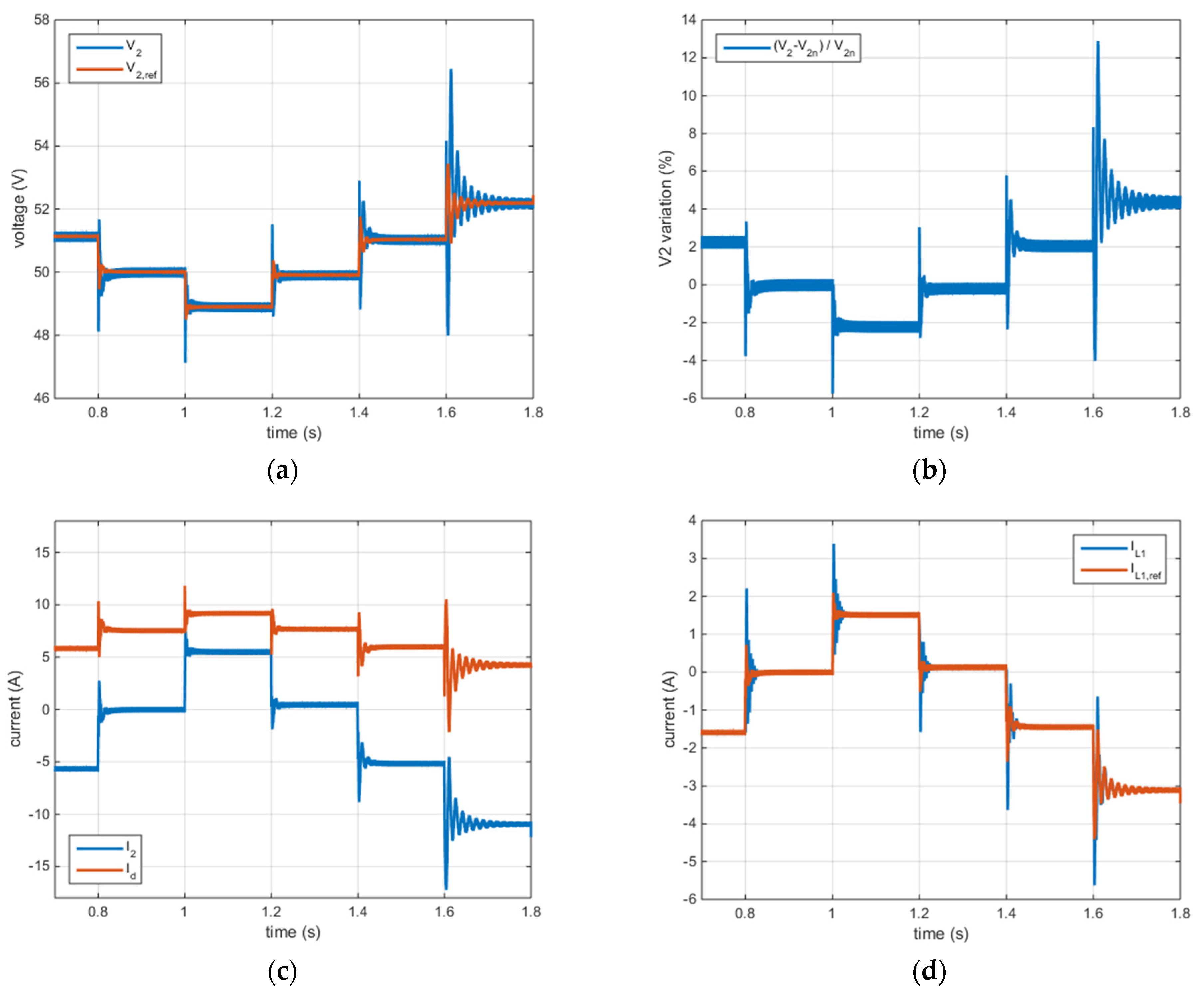

4.1. Baseline Scenario and Scenario #1 (SS-GN)

4.2. Scenario #2 (SD-GN)

4.3. Scenario #3 (SD-GD)

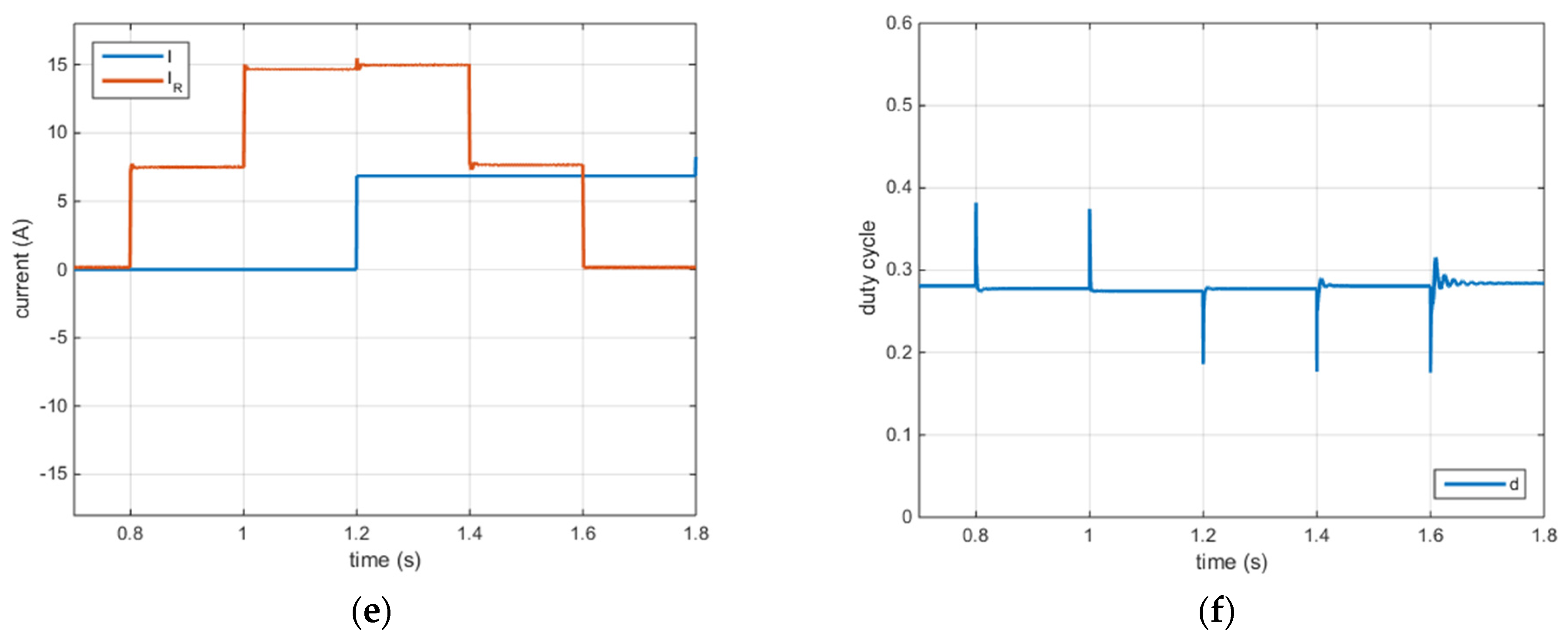

5. Experimental Validation

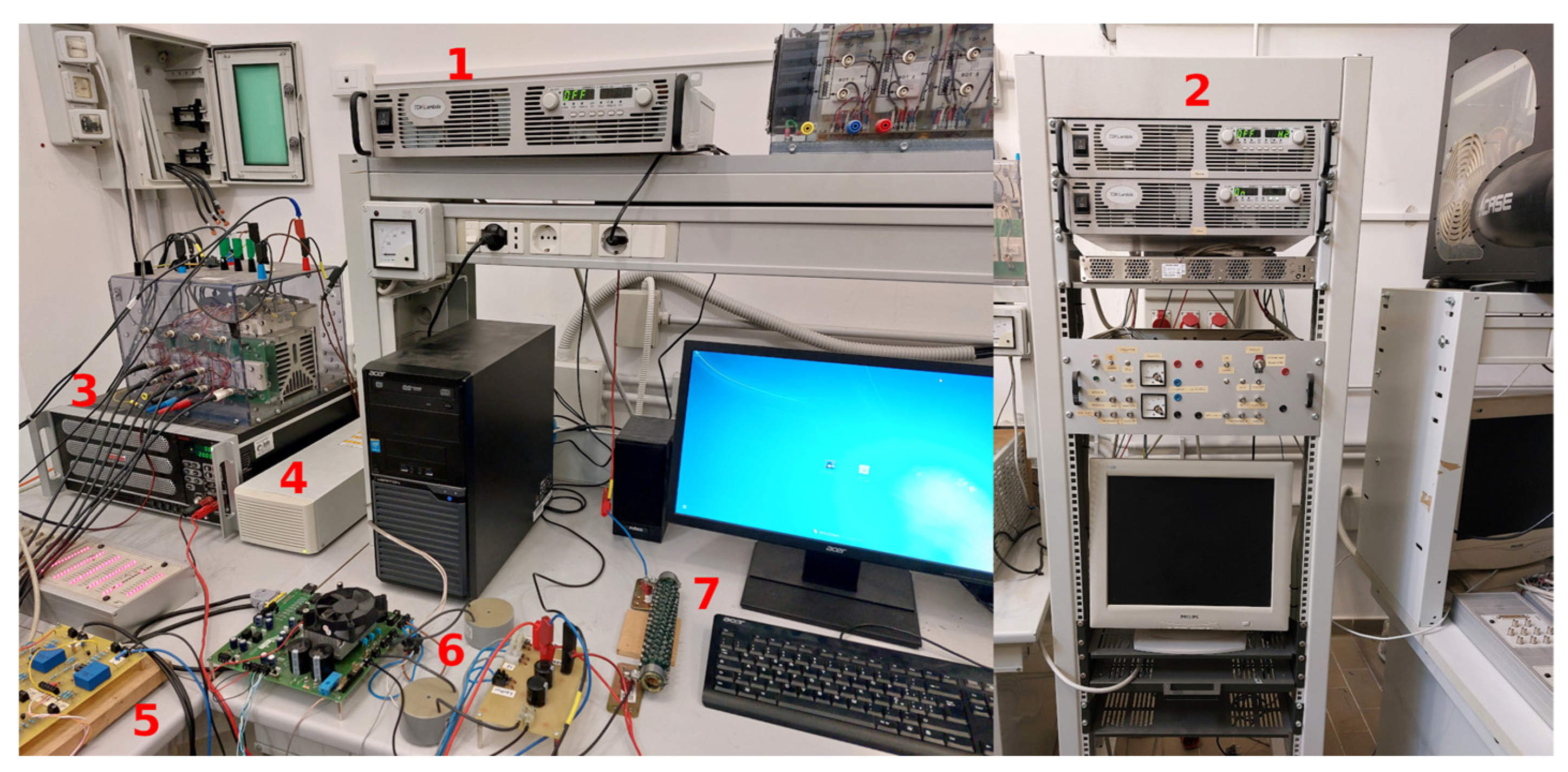

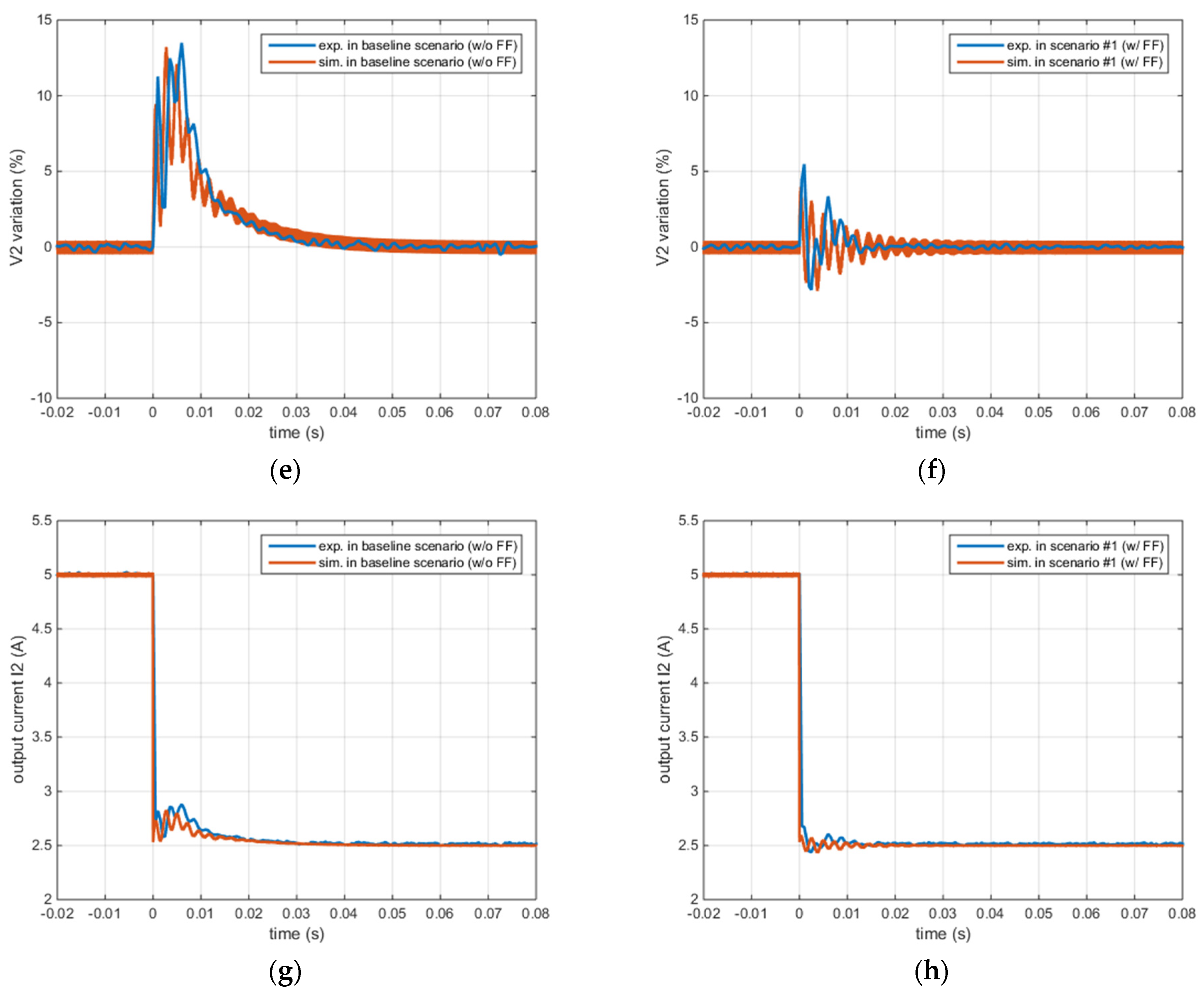

5.1. Baseline Scenario and Scenario #1 (SS-GN)

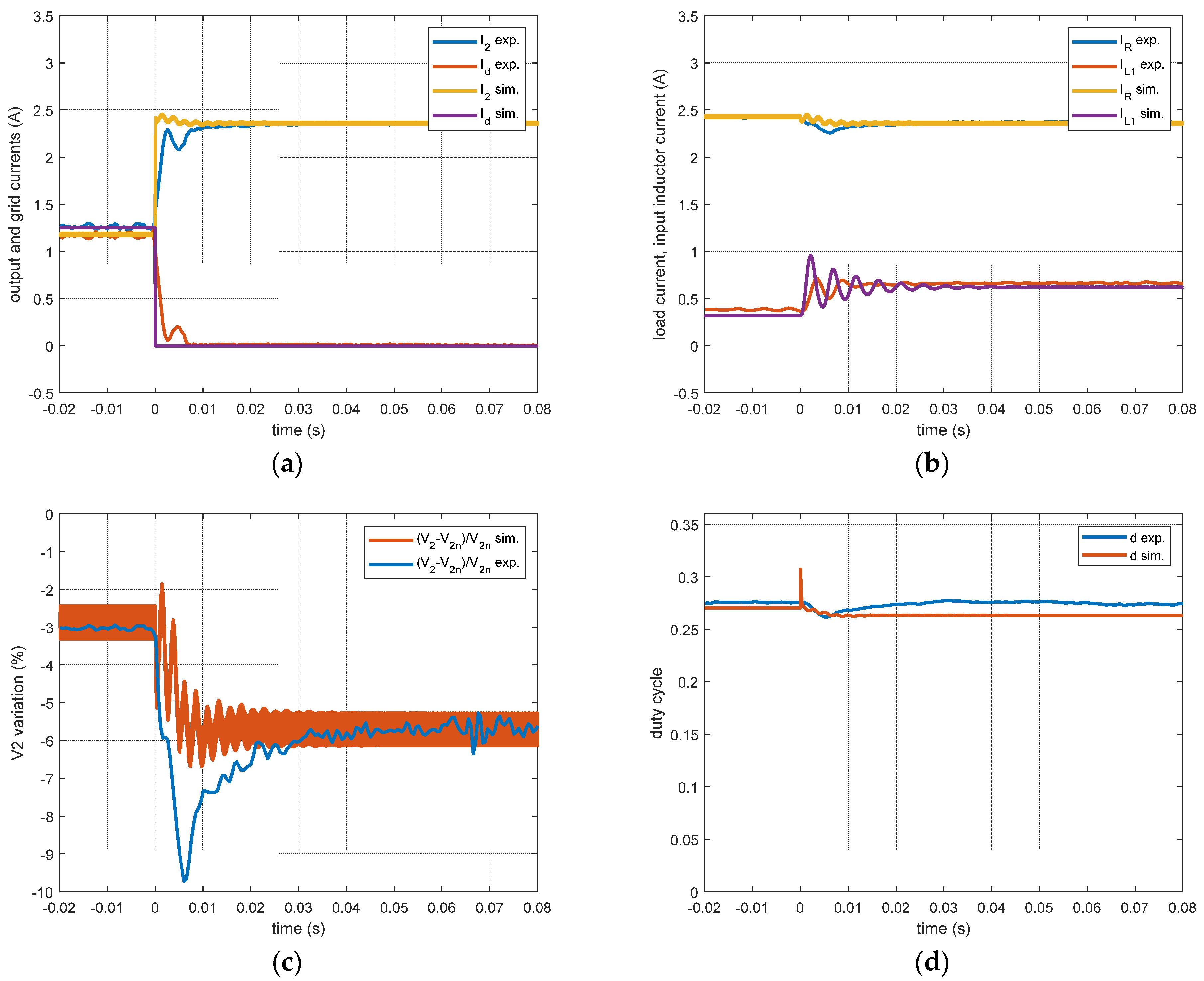

5.2. Scenario #2 (SD-GN)

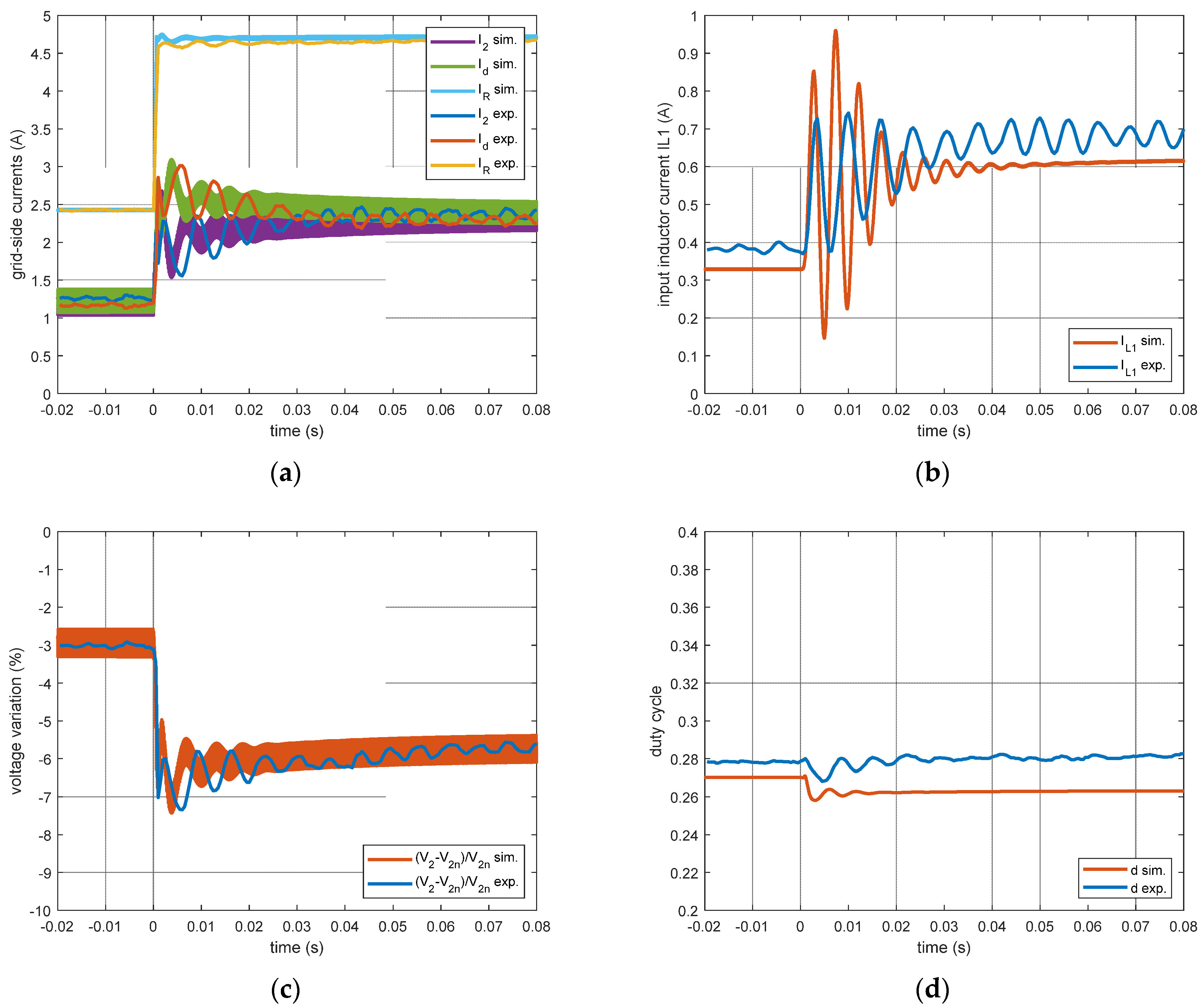

5.3. Scenario #3 (SD-GD)

6. Robustness Analysis and Limitations of the Split-Pi Converter

6.1. Robustness Analysis

6.2. Limitations of the Split-Pi Converter

7. Conclusions and Future Work

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Nomenclature

| d | Duty cycle |

| Average duty cycle | |

| Phase margin | |

| mg | Gain margin |

| u | Input vector of the state-space model |

| x | State vector of the state-space model |

| Average state vector for state-space model linearization | |

| y | Output vector of the state-space model |

| Crossover frequency | |

| A,B,C,D | Matrices of the state-space model |

| C | Bulk capacitor |

| Ce | External input/output capacitors |

| Ed | No-load voltage of the microgrid’s equivalent droop-controlled generator |

| Eds | No-load voltage chosen to control the storage converter in droop mode |

| Fsw | Switching frequency |

| Gci1(s) | Transfer function of the controller for the current loop (IL1) |

| Gcv2(s) | Transfer function of the controller for the voltage loop (V2) |

| Gp1(s) | Transfer function of the process (IL1 vs. d) |

| Gp2(s) | Transfer function of the process (I2 vs. IL1) |

| I | Current supplied by the microgrid’s equivalent current generator managed by the EMS |

| I1 | Input current (port 1, storage-side) |

| I1n | Nominal input current (port 1, storage-side) |

| I2 | Output current (port 2, grid-side) |

| I2n | Nominal output current (port 2, grid-side) |

| Id | Current supplied by the microgrid’s equivalent droop-controlled generator |

| Icx | Maximum ESS charging current |

| Idx | Maximum ESS discharging current |

| Ieq | Microgrid’s equivalent current generator considered as active load in scenarios #1–#3 |

| IL1 | Current of the leftmost inductor (port 1, storage-side) |

| IL10 | Average current of the leftmost inductor (port 1, storage-side) |

| IL2 | Current of the rightmost inductor (port 2, grid-side) |

| IL20 | Average current of the rightmost inductor (port 2, grid-side) |

| Kii | Integral gain of the PI regulator of the current loop (IL1) |

| Kiv | Integral gain of the PI regulator of the voltage loop (V2) |

| Kpi | Proportional gain of the PI regulator of the current loop (IL1) |

| Kpv | Proportional gain of the PI regulator of the voltage loop (V2) |

| L | Inductor at input/output ports |

| Pn | Nominal power of the storage converter |

| R | Equivalent load resistance considered in scenarios #1–#3 |

| Rc | Parasitic resistance of the bulk capacitor |

| Rd | Droop resistance of the microgrid’s equivalent droop-controlled generator |

| Rds | Droop resistance of the storage converter |

| Re | Parasitic resistance of external input/output capacitors |

| RL | Parasitic resistance of input/output inductors |

| Rn | Nominal load resistance |

| V1 | Input voltage (port 1, storage-side) |

| V1n | Nominal input voltage (port 1, storage-side) |

| V2 | Output voltage (port 2, grid-side) |

| V2n | Nominal output voltage (port 2, grid-side) |

| V2ref | Reference output voltage for the storage converter (grid-side) |

| Vc | Voltage of the bulk capacitor |

| Vc0 | Average voltage of the bulk capacitor |

| Ve | Voltage of the external capacitor |

| Ve0 | Average voltage of the external capacitor |

References

- Chub, A.; Vinnikov, D.; Kosenko, R.; Liivik, E.; Galkin, I. Bidirectional DC–DC Converter for Modular Residential Battery Energy Storage Systems. IEEE Trans. Ind. Electron. 2020, 67, 1944–1955. [Google Scholar] [CrossRef]

- Sim, J.; Lee, J.; Choi, H.; Jung, J.H. High Power Density Bidirectional Three-Port DC-DC Converter for Battery Applications in DC Microgrids. In Proceedings of the 2019 10th International Conference on Power Electronics and ECCE Asia (ICPE 2019—ECCE Asia), Busan, Korea, 27–30 May 2019; Volume 3, pp. 843–848. [Google Scholar]

- Di Piazza, M.C.; Luna, M.; Pucci, M.; La Tona, G.; Accetta, A. Electrical Storage Integration into a DC Nanogrid Testbed for Smart Home Applications. In Proceedings of the 2018 IEEE International Conference on Environment and Electrical Engineering and 2018 IEEE Industrial and Commercial Power Systems Europe (EEEIC/I&CPS Europe), Palermo, Italy, 12–15 June 2018; pp. 1–5. [Google Scholar] [CrossRef]

- Byrne, R.H.; Nguyen, T.A.; Copp, D.A.; Chalamala, B.R.; Gyuk, I. Energy Management and Optimization Methods for Grid Energy Storage Systems. IEEE Access 2018, 6, 13231–13260. [Google Scholar] [CrossRef]

- Tytelmaier, K.; Husev, O.; Veligorskyi, O.; Yershov, R. A review of non-isolated bidirectional dc-dc converters for energy storage systems. In Proceedings of the 2016 II International Young Scientists Forum on Applied Physics and Engineering (YSF), Kharkiv, Ukraine, 10–14 October 2016; pp. 22–28. [Google Scholar] [CrossRef]

- Chen, J.; Nguyen, M.-K.; Yao, Z.; Wang, C.; Gao, L.; Hu, G. DC-DC Converters for Transportation Electrification: Topologies, Control, and Future Challenges. IEEE Electrif. Mag. 2021, 9, 10–22. [Google Scholar] [CrossRef]

- Gorji, S.A.; Sahebi, H.G.; Ektesabi, M.; Rad, A.B. Topologies and Control Schemes of Bidirectional DC–DC Power Converters: An Overview. IEEE Access 2019, 7, 117997–118019. [Google Scholar] [CrossRef]

- Beheshtaein, S.; Cuzner, R.M.; Forouzesh, M.; Savaghebi, M.; Guerrero, J.M. DC Microgrid Protection: A Comprehensive Review. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 6677, 1. [Google Scholar] [CrossRef]

- Odo, P. A Comparative Study of Single-phase Non-isolated Bidirectional dc-dc Converters Suitability for Energy Storage Application in a dc Microgrid. In Proceedings of the 2020 IEEE 11th International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Dubrovnik, Croatia, 28 September–1 October 2020; pp. 391–396. [Google Scholar] [CrossRef]

- Al-Obaidi, N.A.; Abbas, R.A.; Khazaal, H.F. A Review of Non-Isolated Bidirectional DC-DC Converters for Hybrid Energy Storage System. In Proceedings of the 2022 5th International Conference on Engineering Technology and its Applications (IICETA), Al-Najaf, Iraq, 31 May–1 June 2022; pp. 248–253. [Google Scholar] [CrossRef]

- Crocker, T.R. Power Converter and Method for Power Conversion. U.S. Patent US 20040212357A1, 28 October 2004. [Google Scholar]

- Khan, S.A.; Pilli, N.K.; Singh, S.K. Hybrid Split Pi converter. In Proceedings of the 2016 IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES), Trivandrum, India, 14–17 December 2016; pp. 1–6. [Google Scholar] [CrossRef]

- Sobhan, S.; Bashar, K.L. A novel Split-Pi Converter with High Step-Up Ratio. In Proceedings of the 2017 IEEE Region 10 Humanitarian Technology Conference (R10-HTC), Dhaka, Bangladesh, 21–23 December 2017; pp. 255–258. [Google Scholar] [CrossRef]

- Ahmad, T.; Sobhan, S. Performance Analysis of Bidirectional Split-Pi Converter Integrated with Passive Ripple Cancelling Circuit. In Proceedings of the 2017 International Conference on Electrical, Computer and Communication Engineering (ECCE), Cox’s Bazar, Bangladesh, 16–18 February 2017; pp. 433–437. [Google Scholar] [CrossRef]

- Sabatta, D.; Meyer, J. Super Capacitor Management Using a Split-Pi Symmetrical Bi-Directional DC-DC Power Converter with Feed-forward Gain Control. In Proceedings of the 2018 International Conference on the Domestic Use of Energy (DUE), Cape Town, South Africa, 3–5 April 2018; pp. 1–5. [Google Scholar] [CrossRef]

- Alzahrani, A.; Shamsi, P.; Ferdowsi, M. Single and Interleaved Split-pi DC-DC Converter. In Proceedings of the 2017 IEEE 6th International Conference on Renewable Energy Research and Applications (ICRERA), San Diego, CA, USA, 5–8 November 2017; pp. 995–1000. [Google Scholar] [CrossRef]

- Karbivska, T.; Kozhushko, Y.; Barath, J.G.N.; Bondarenko, O. Split-Pi Converter for Resistance Welding Application. In Proceedings of the 2020 IEEE KhPI Week on Advanced Technology (KhPIWeek), Kharkiv, Ukraine, 5–10 October 2020; pp. 391–395. [Google Scholar] [CrossRef]

- Investigations on Interleaved and Coupled Split-Pi DC-DC Converter for Hybrid Electric Vehicle Applications. Int. J. Renew. Energy Res. 2021, 11, 1–10. [CrossRef]

- Monteiro, V.; Oliveira, C.; Rodrigues, A.; Sousa, T.J.C.; Pedrosa, D.; Machado, L.; Afonso, J.L. A Novel Topology of Multilevel Bidirectional and Symmetrical Split-Pi Converter. In Proceedings of the 2020 IEEE 14th International Conference on Compatibility, Power Electronics and Power Engineering (CPE-POWERENG), Setubal, Portugal, 8–10 July 2020; pp. 511–516. [Google Scholar] [CrossRef]

- Singhai, M.; Pilli, N.; Singh, S.K. Modeling and Analysis of Split-Pi Converter Using State Space Averaging Technique. In Proceedings of the 2014 IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES), Mumbai, India, 16–19 December 2014; pp. 1–6. [Google Scholar] [CrossRef]

- Subramaniyan, G.; Krishnasamy, V.; Mohammed, J.S. Modeling and Design of Split-Pi Converter. Energies 2022, 15, 5690. [Google Scholar] [CrossRef]

- Maclaurin, A.; Okou, R.; Barendse, P.; Khan, M.A.; Pillay, P. Control of a Flywheel Energy Storage System for Rural Applications Using a Split-Pi DC-DC Converter. In Proceedings of the 2011 IEEE International Electric Machines & Drives Conference (IEMDC), Niagara Falls, ON, Canada, 15–18 May 2011; pp. 265–270. [Google Scholar] [CrossRef]

- Luna, M.; Sferlazza, A.; Accetta, A.; Di Piazza, M.C.; La Tona, G.; Pucci, M. Modeling and Performance Assessment of the Split-Pi Used as a Storage Converter in All the Possible DC Microgrid Scenarios. Part I: Theoretical Analysis. Energies 2021, 14, 4902. [Google Scholar] [CrossRef]

- Luna, M.; Sferlazza, A.; Accetta, A.; Di Piazza, M.C.; La Tona, G.; Pucci, M. Modeling and Performance Assessment of the Split-Pi Used as a Storage Converter in All the Possible DC Microgrid Scenarios. Part II: Simulation and Experimental Results. Energies 2021, 14, 5616. [Google Scholar] [CrossRef]

- Middlebrook, R.D.; Cuk, S. A General Unified Approach to Modelling Switching-Converter Power Stages. In Proceedings of the IEEE Power Electronics Specialists Conference, Cleveland, OH, USA, 8–10 June 1976; pp. 18–34. [Google Scholar] [CrossRef]

- Mohan, N.; Undeland, T.M.; Robbins, W.P. Power Electronics. Converters, Applications and Design, 3rd ed.; John Wiley and Sons, Inc.: Hoboken, NJ, USA, 2003. [Google Scholar]

- Fung, H.-W.; Wang, Q.-G.; Lee, T.-H. PI Tuning in Terms of Gain and Phase Margins. Automatica 1998, 34, 1145–1149. [Google Scholar] [CrossRef]

| Mode | Voltage Relationship | Power Flow Direction |

|---|---|---|

| 1 | V1 ≤ V2 | port 1 → port 2 |

| 2 | V1 ≤ V2 | port 2 → port 1 |

| 3 | V1 > V2 | port 1 → port 2 |

| 4 | V1 > V2 | port 2 → port 1 |

| Parameter | Symbol | Value |

|---|---|---|

| Switching frequency | Fsw | 20 kHz |

| Nominal input voltage | V1n | 180 V |

| Nominal output voltage | V2n | 50 V |

| Nominal power | Pn | 750 W |

| Nominal load resistance | Rn | 3.333 Ω |

| Nominal input current | I1n | 4.167 A |

| Max. charge/discharge current | Icx, Idx | 5 A |

| Nominal output current | I2n | 15 A |

| Nominal duty-cycle | 0.277 | |

| Inductance value of L | L | 1000 µH |

| Parasitic resistance of L | RL | 65 mΩ |

| Capacitance value of Ce | Ce | 200 µF |

| Parasitic resistance of Ce | Re | 260 mΩ |

| Capacitance value of C | C | 540 µF |

| Parasitic resistance of C | Rc | 125 mΩ |

| Microgrid Scenario | Storage Converter | Other Microgrid Generators |

|---|---|---|

| #1 (SS-GN) | Droop mode with droop resistance Rd = 0 (stiff) | No other generator present (passive load) or all current-controlled by the EMS |

| #2 (SD-GN) | Droop mode with droop resistance Rd ≠ 0 | No other generator present (passive load) or all current-controlled by the EMS |

| #3 (SD-GD) | Droop mode with droop resistance Rd ≠ 0 | At least one is droop-controlled, and none has Rd = 0 |

| #4 (SC-GD) | Current mode | At least one is droop-controlled, and none has Rd = 0 |

| #5 (SC-GS) | Current mode | One is droop-controlled and has Rd = 0 (stiff); the others, if present, are current-controlled by the EMS |

| Loop Controller and Scenario | Values of ωc, mφ, and mg | PI and PID Coefficients |

|---|---|---|

| Gci1 for current IL1 baseline, #1 (SS-GN), and #2 (SD-GN) | ωc = 1200 rad/s mφ = 94° mg = ∞ | Kpi = 4.507·10−3 Kii = 31.2608 Kdi = 1.711·10−5 N = 37.9651 + pole @ 4.0·104 rad/s |

| Gci1 for current IL1 #3 (SD-GD) | ωc = 1200 rad/s mφ = 89.8° mg = ∞ | Kpi = 3.207·10−3 Kii = 26.6073 Kdi = 1.343·10−5 N = 41.876 + pole @ 4.0·104 rad/s |

| Gcv2 for voltage V2 w/o FF baseline | ωc = 100 rad/s mφ = 120° mg = 31 dB | Kpv = 0.1275 Kiv = 11.885 + pole @ 666 rad/s |

| Gcv2 for voltage V2 w/FF #1 (SS-GN) and #2 (SD-GN) | ωc = 100 rad/s mφ = 120° mg = 29.4 dB | Kpv = 0.076 Kiv = 5.1286 + pole @ 666 rad/s |

| Gcv2 for voltage V2 w/FF #3 (SD-GD) | ωc = 100 rad/s mφ = 120° mg = 43.9 dB | Kpv = 0.097 Kiv = 4.7315 + pole @ 666 rad/s |

| ΔC | ΔRc | Max. |ΔV2| | Stable Operation |

|---|---|---|---|

| +20% | +10% | 14.3% | yes |

| −20% | −10% | 17.8% | yes |

| ΔL Left | ΔRL Left | ΔL Right | ΔRL Right | Max. |ΔV2| | Stable Operation |

|---|---|---|---|---|---|

| +15% | +7.5% | +10% | +5% | 15.0% | yes |

| −15% | −7.5% | −10% | −5% | 15.3% | yes |

| +10% | +5% | +15% | +7.5% | 14.8% | yes |

| −10% | −5% | −15% | −7.5% | 14.4% | yes |

| ΔCe Left | ΔRe Left | ΔCe Right | ΔRe Right | Max. |ΔV2| | Stable Operation |

|---|---|---|---|---|---|

| +20% | +10% | +10% | +5% | 11.7% | yes |

| −20% | −10% | −10% | −5% | 13.6% | yes |

| +10% | +5% | +20% | +10% | 11.0% | yes |

| −10% | −5% | −20% | −10% | 15.1% | yes |

| ΔC | ΔRc | Max. |ΔV2| | Stable Operation |

|---|---|---|---|

| +20% | +10% | 15.4% | yes |

| −20% | −10% | 16.0% | yes |

| ΔL Left | ΔRL Left | ΔL Right | ΔRL Right | Max. |ΔV2| | Stable Operation |

|---|---|---|---|---|---|

| +15% | +7.5% | +10% | +5% | 15.9% | yes |

| −15% | −7.5% | −10% | −5% | 13.2% | yes |

| +10% | +5% | +15% | +7.5% | 15.7% | yes |

| −10% | −5% | −15% | −7.5% | 12.2% | yes |

| ΔCe Left | ΔRe Left | ΔCe Right | ΔRe Right | Max. |ΔV2| | Stable Operation |

|---|---|---|---|---|---|

| +20% | +10% | +10% | +5% | 11.7% | yes |

| −20% | −10% | −10% | −5% | 13.9% | yes |

| +10% | +5% | +20% | +10% | 10.8% | yes |

| −10% | −5% | −20% | −10% | 15.4% | yes |

| ΔC | ΔRc | Max. |ΔV2| | Stable Operation |

|---|---|---|---|

| +20% | +10% | not defined | never |

| −20% | −10% | 12.8% | yes, except between 1.6 s and 1.8 s |

| ΔL Left | ΔRL Left | ΔL Right | ΔRL Right | Max. |ΔV2| | Stable Operation |

|---|---|---|---|---|---|

| +15% | +7.5% | +10% | +5% | 19.2% | yes, except between 1.0 s and 1.2 s |

| −15% | −7.5% | −10% | −5% | 12.2% | yes |

| +10% | +5% | +15% | +7.5% | 19.3% | yes, except between 1.6 s and 1.8 s |

| −10% | −5% | −15% | −7.5% | 11.7% | yes |

| ΔCe Left | ΔRe Left | ΔCe Right | ΔRe Right | Max. |ΔV2| | Stable Operation |

|---|---|---|---|---|---|

| +20% | +10% | +10% | +5% | 12.6% | yes |

| −20% | −10% | −10% | −5% | 13.3% | yes |

| +10% | +5% | +20% | +10% | 12.2% | yes |

| −10% | −5% | −20% | −10% | 13.7% | yes |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Luna, M.; Sferlazza, A.; Accetta, A.; Di Piazza, M.C.; La Tona, G.; Pucci, M. Modeling and Experimental Validation of a Voltage-Controlled Split-Pi Converter Interfacing a High-Voltage ESS with a DC Microgrid. Energies 2023, 16, 1612. https://doi.org/10.3390/en16041612

Luna M, Sferlazza A, Accetta A, Di Piazza MC, La Tona G, Pucci M. Modeling and Experimental Validation of a Voltage-Controlled Split-Pi Converter Interfacing a High-Voltage ESS with a DC Microgrid. Energies. 2023; 16(4):1612. https://doi.org/10.3390/en16041612

Chicago/Turabian StyleLuna, Massimiliano, Antonino Sferlazza, Angelo Accetta, Maria Carmela Di Piazza, Giuseppe La Tona, and Marcello Pucci. 2023. "Modeling and Experimental Validation of a Voltage-Controlled Split-Pi Converter Interfacing a High-Voltage ESS with a DC Microgrid" Energies 16, no. 4: 1612. https://doi.org/10.3390/en16041612

APA StyleLuna, M., Sferlazza, A., Accetta, A., Di Piazza, M. C., La Tona, G., & Pucci, M. (2023). Modeling and Experimental Validation of a Voltage-Controlled Split-Pi Converter Interfacing a High-Voltage ESS with a DC Microgrid. Energies, 16(4), 1612. https://doi.org/10.3390/en16041612