Advanced Control Algorithm for Three-Phase Shunt Active Power Filter Using Sliding DFT

Abstract

1. Introduction

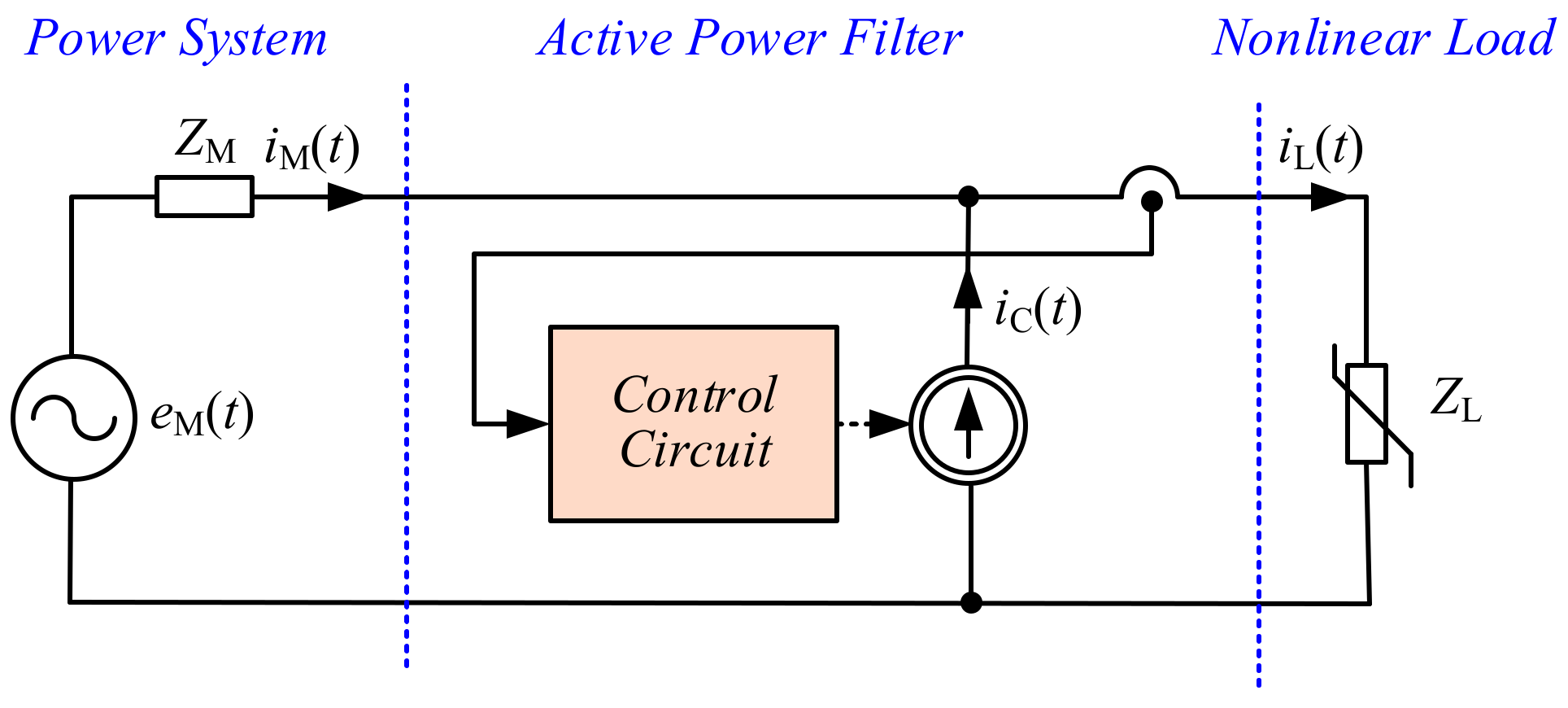

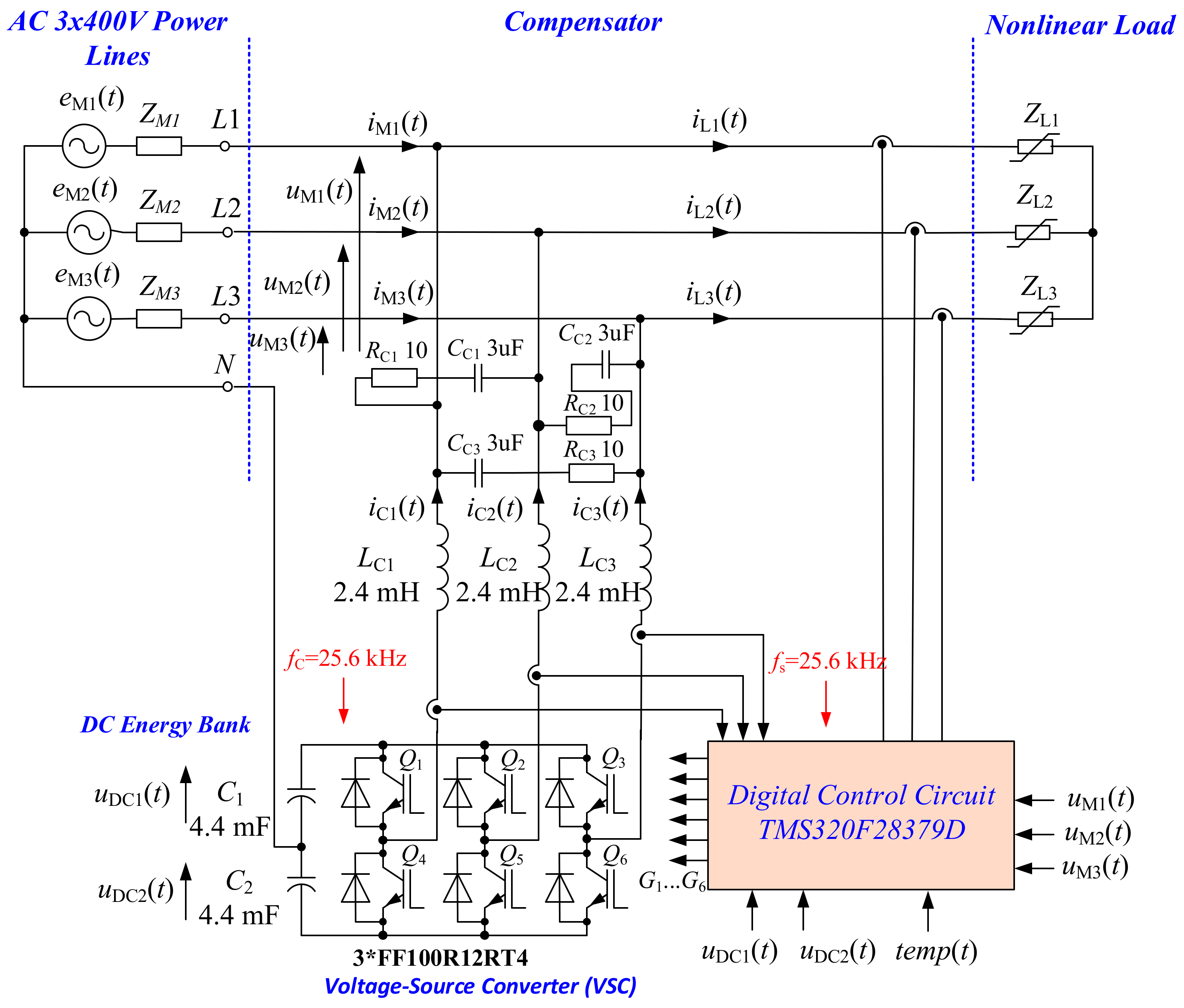

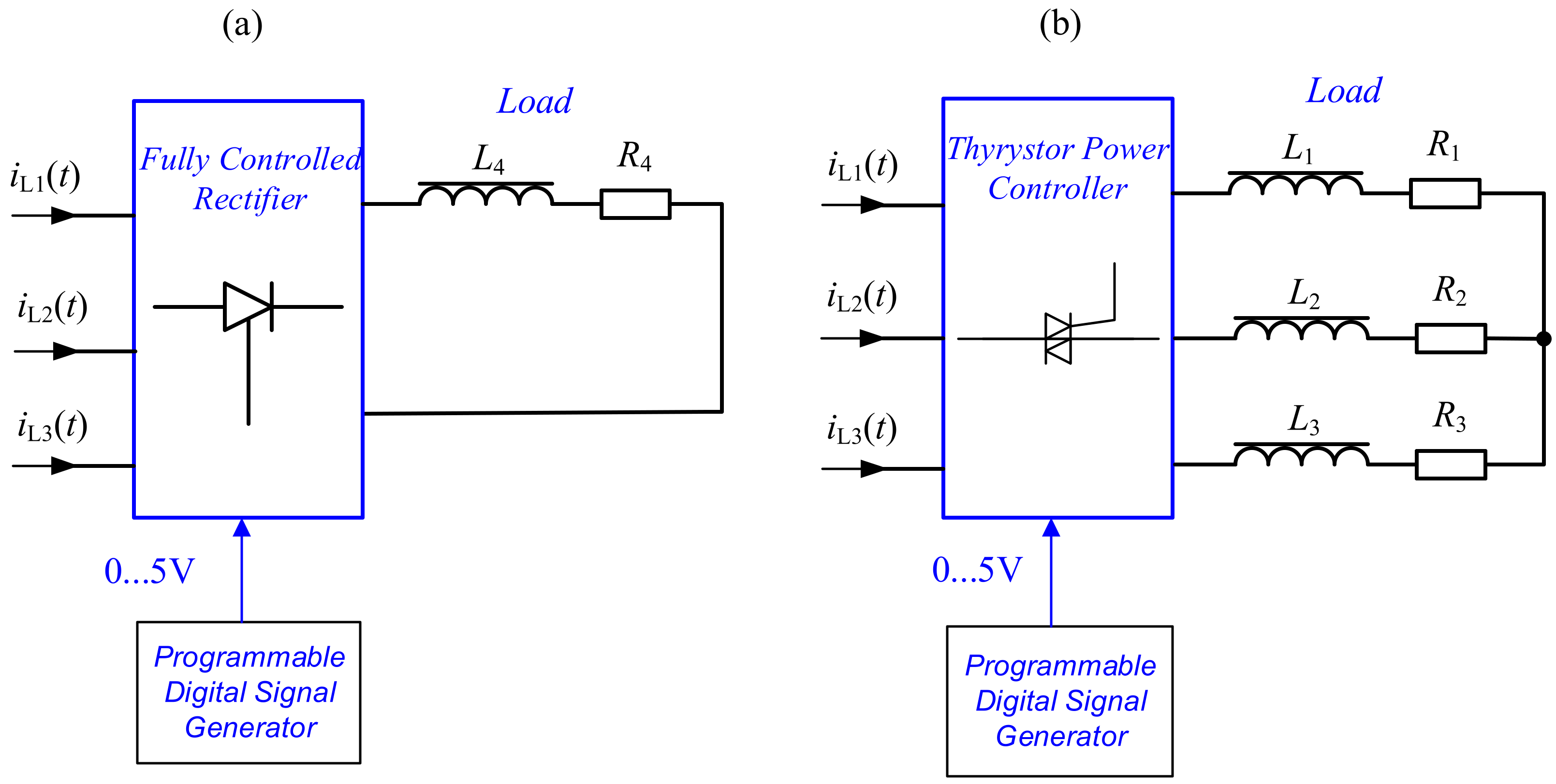

2. Circuit and Operation Description

- Compensation of line current harmonics;

- Compensation of reactive power;

- Application of the sliding DFT in control algorithm;

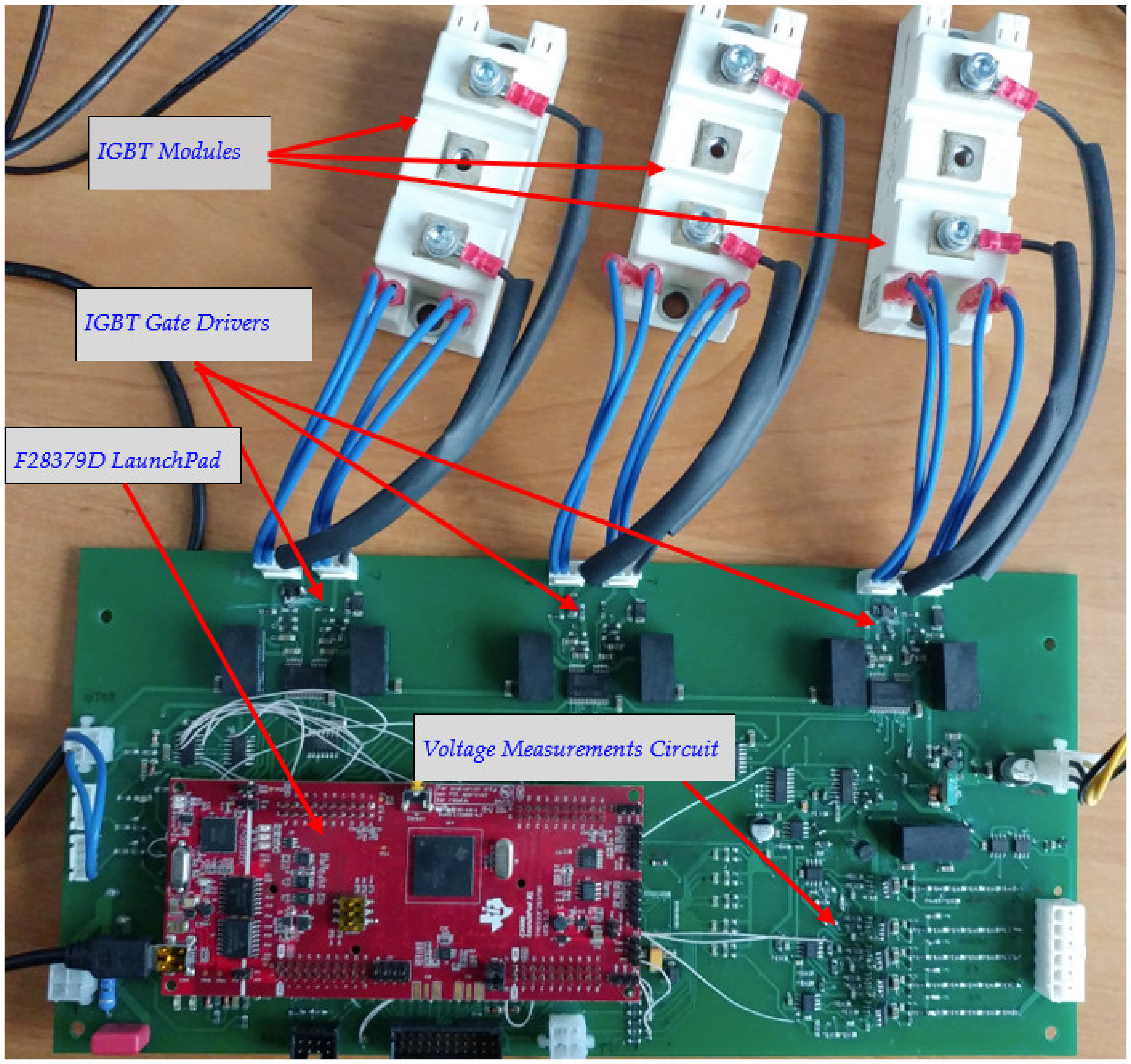

- Implementation of the control system using the TMS320F28379D DSP microcontroller;

- Maximum amplitude of compensation current iC(t) is limited to 50 A;

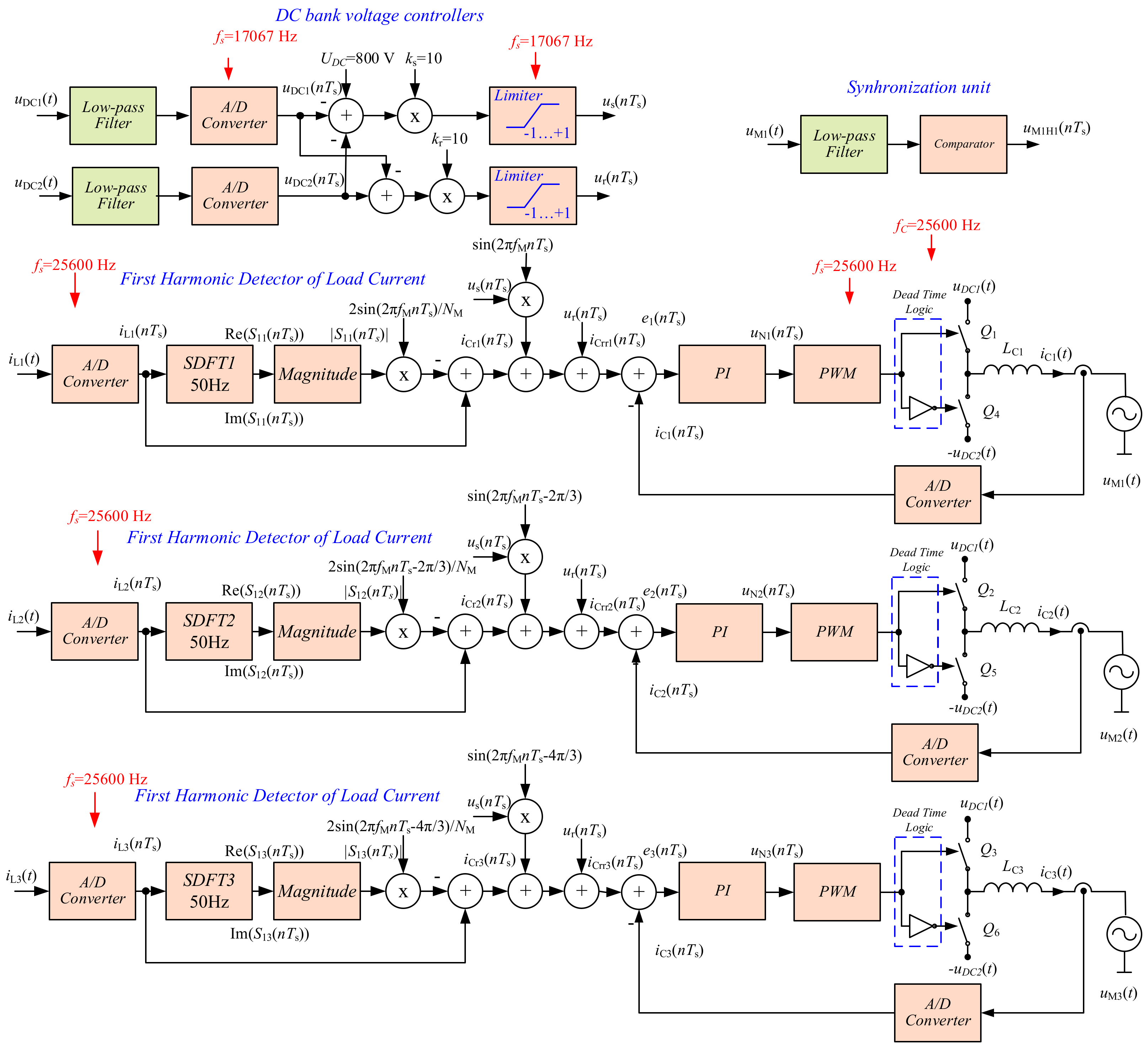

3. Control Circuit of APF

3.1. Control Algorithm

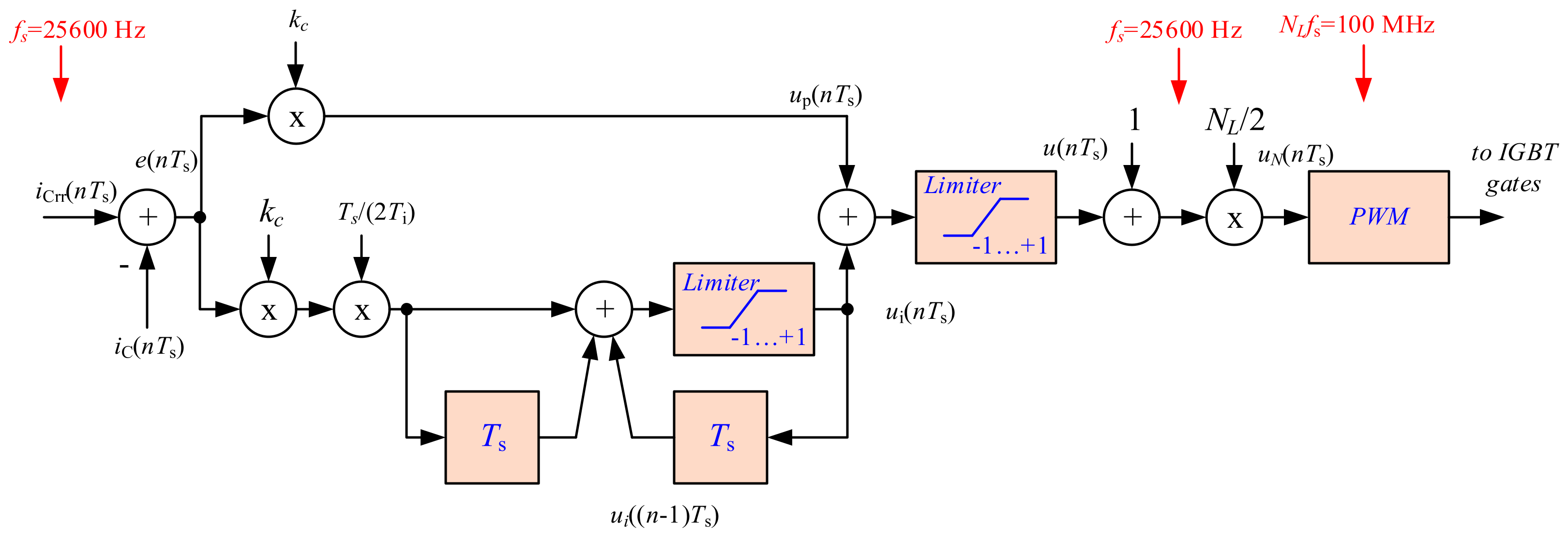

3.2. Digital Current Controller

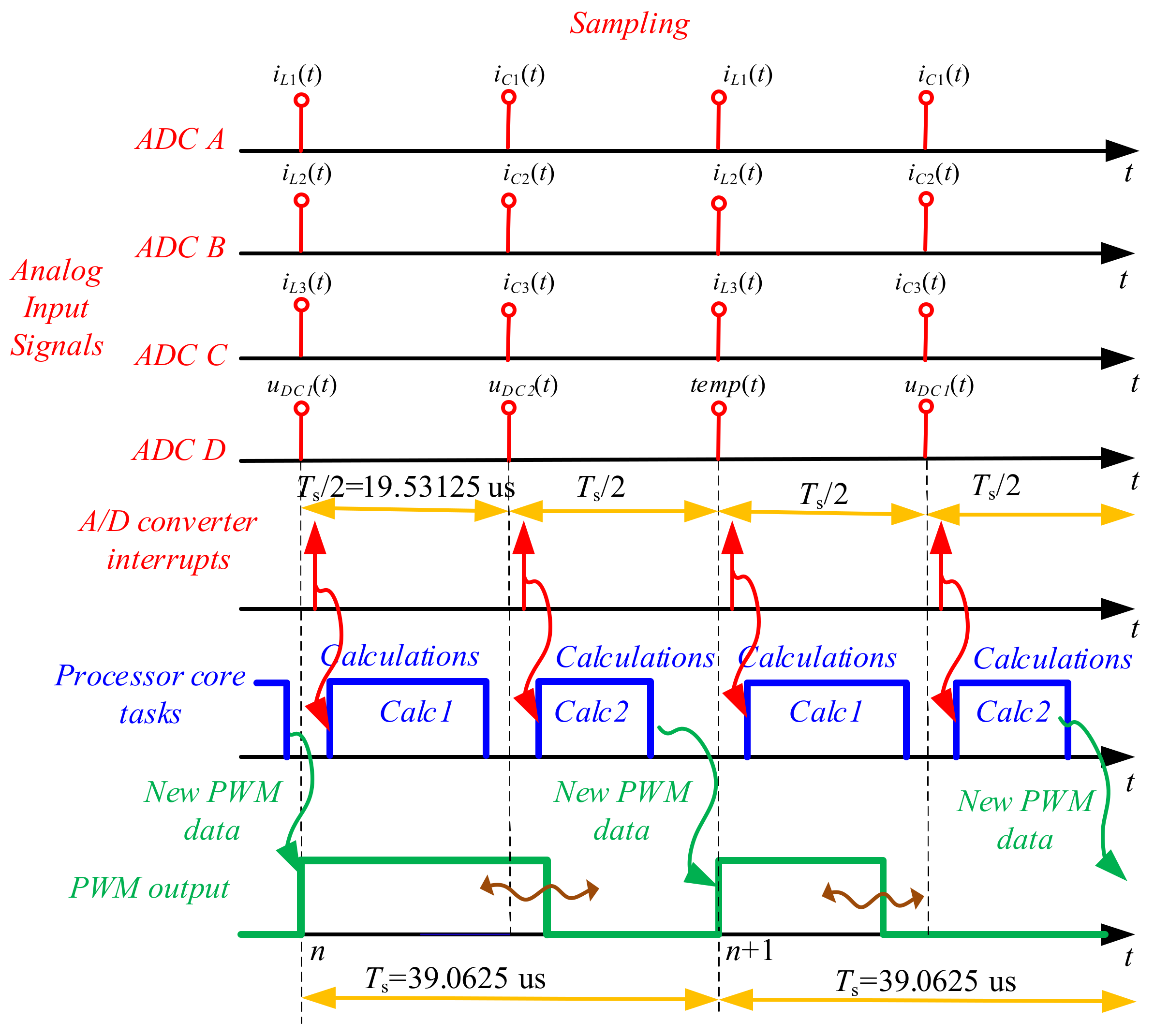

3.3. Analog Signal Sampling

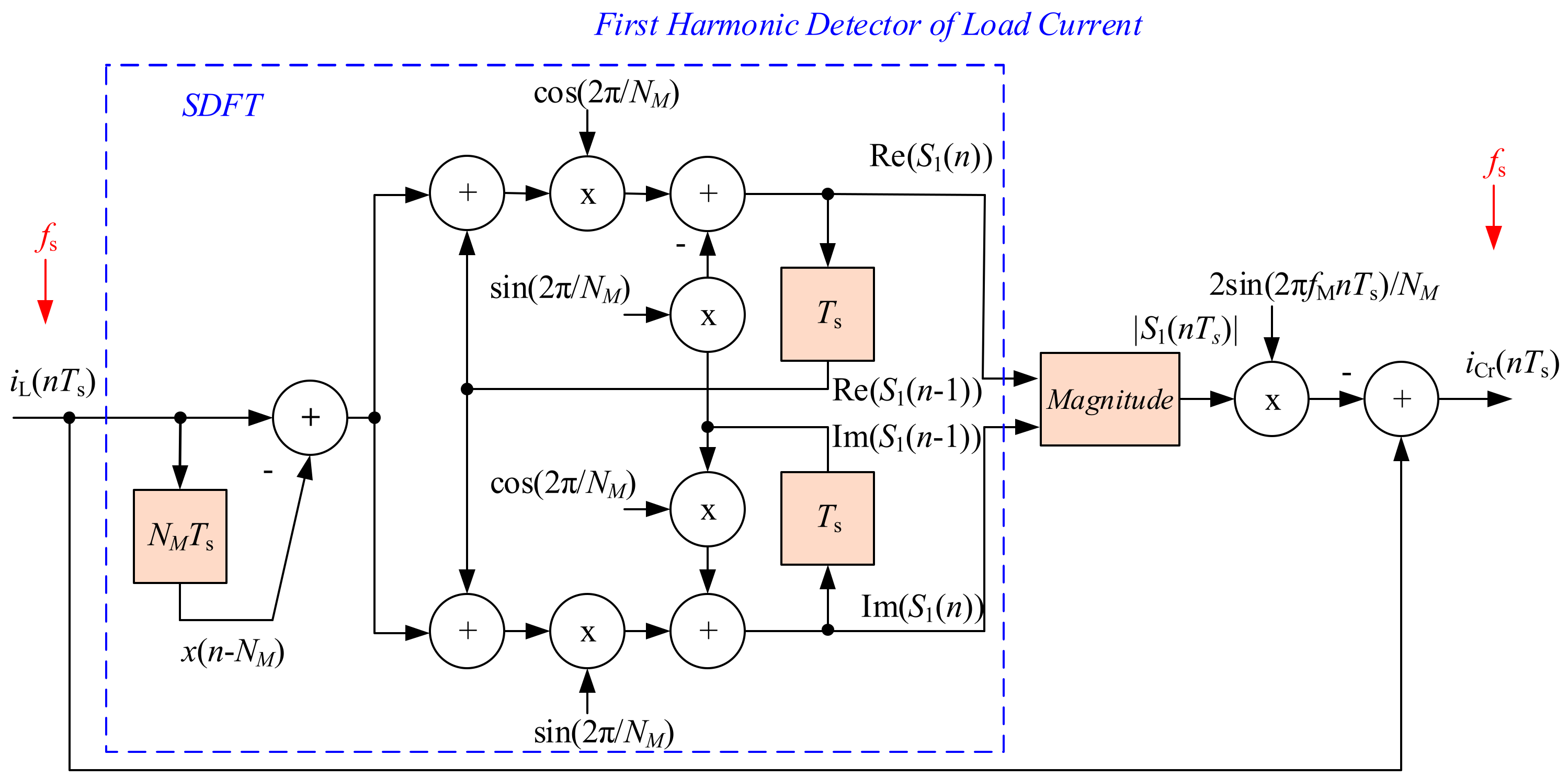

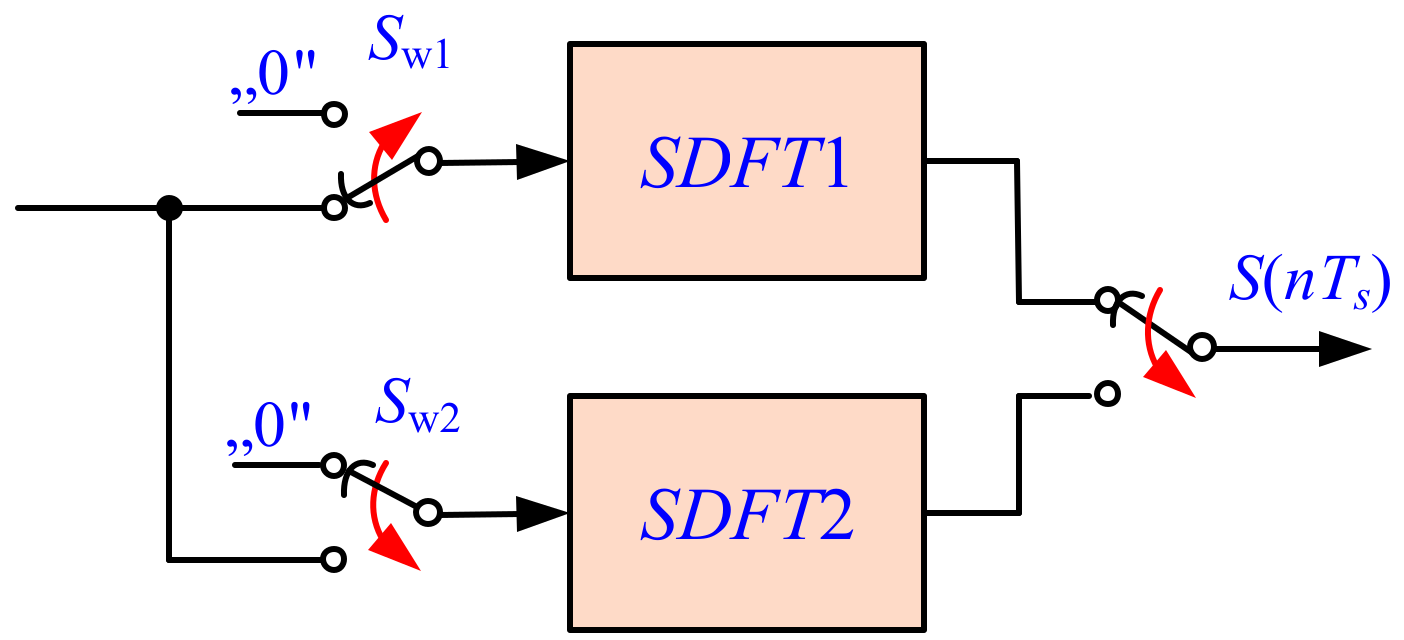

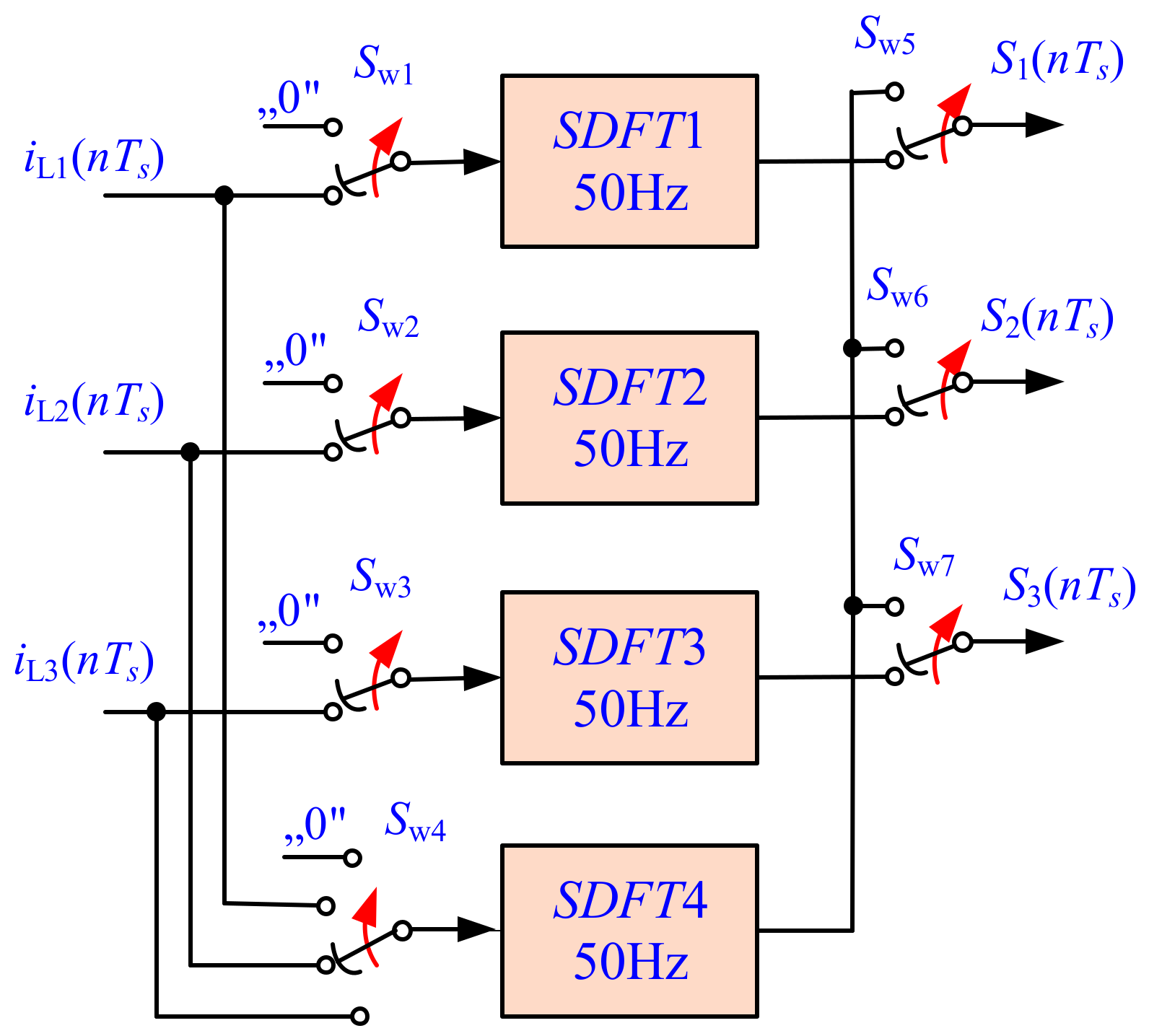

3.4. Sliding DFT Algorithm

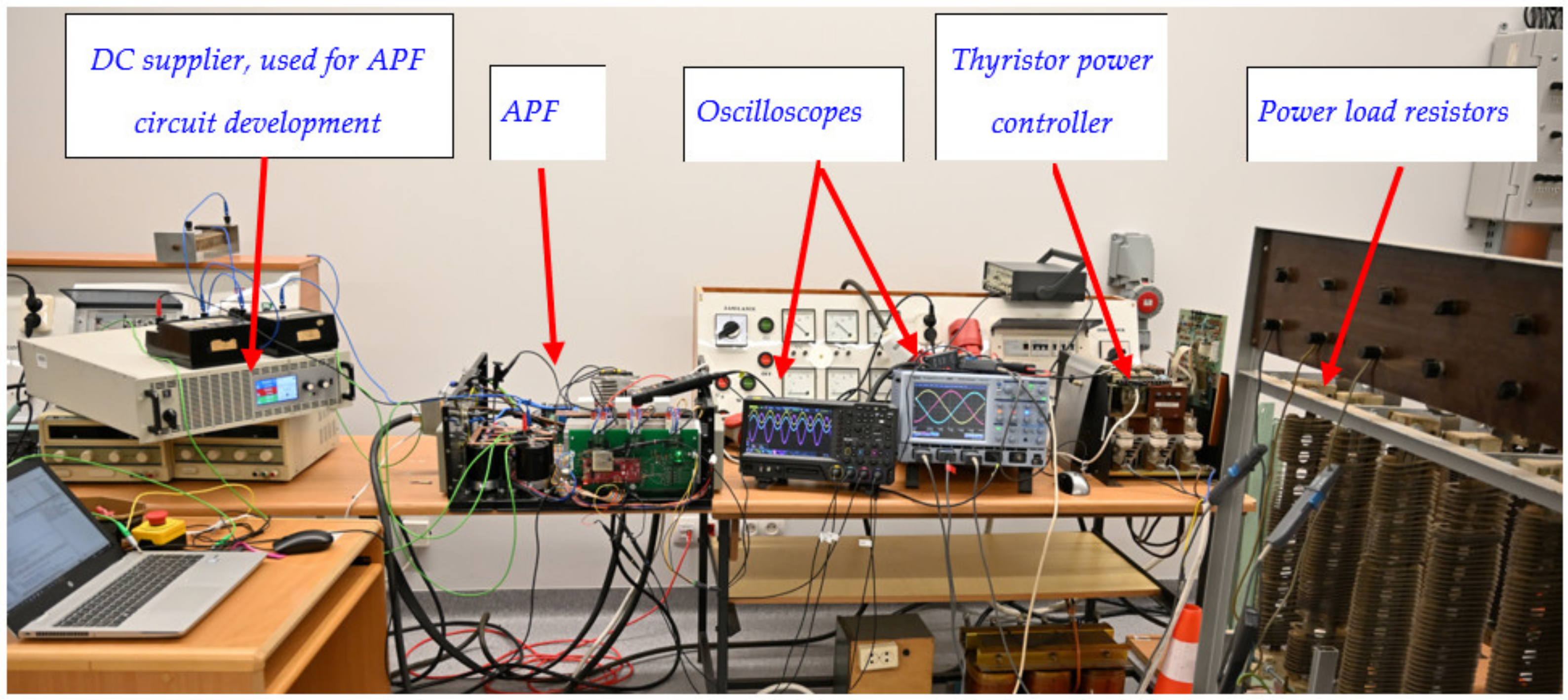

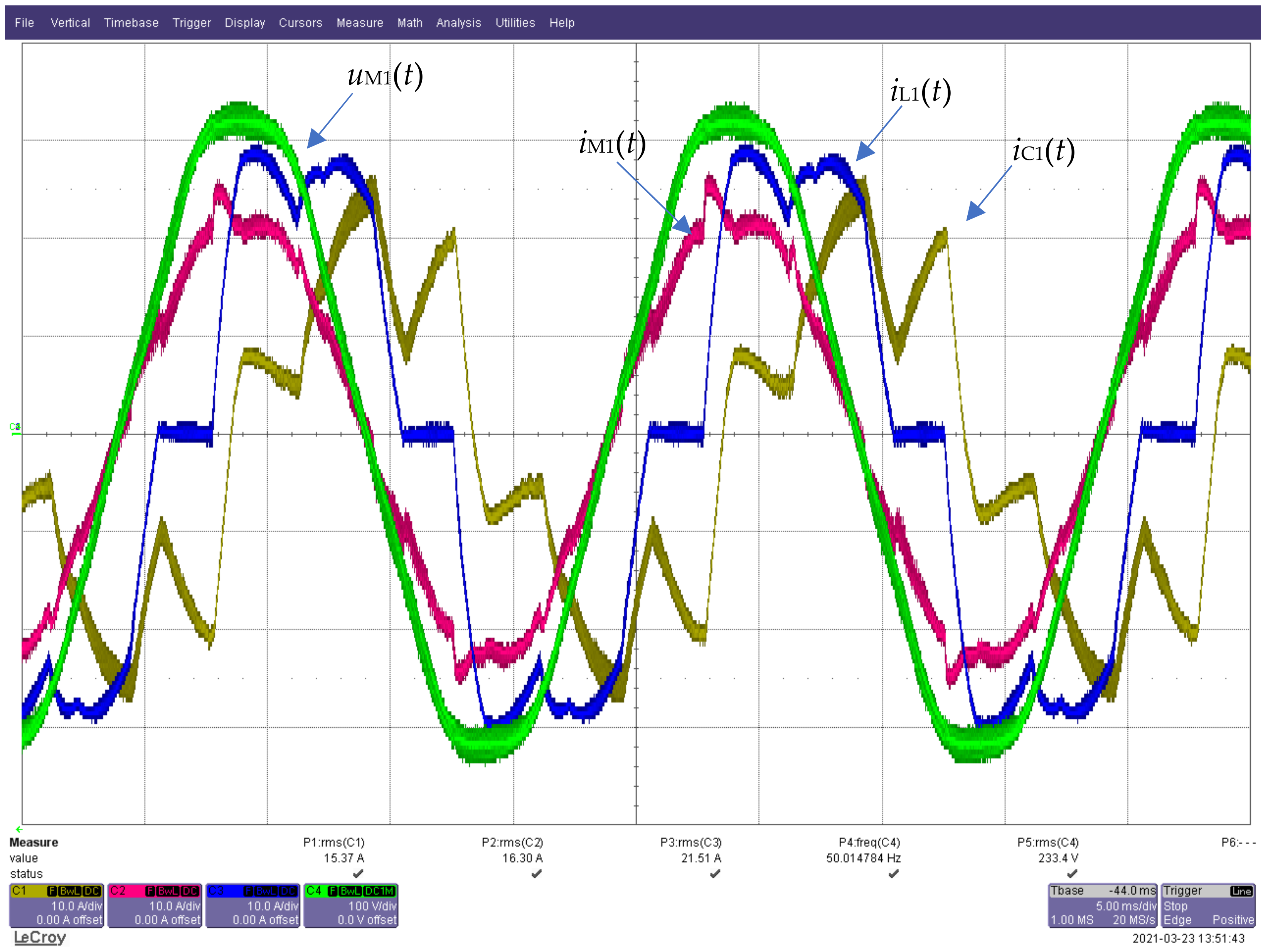

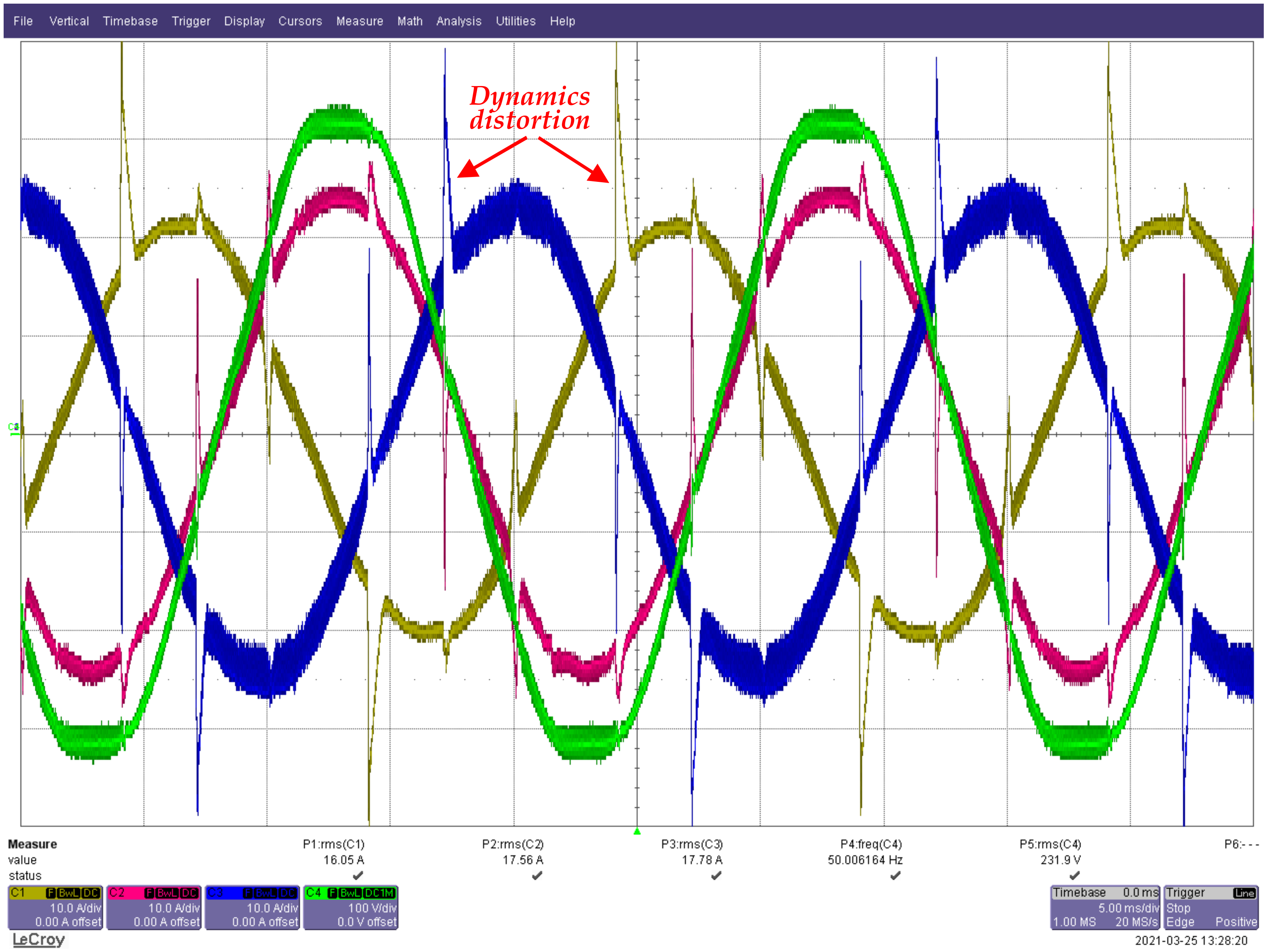

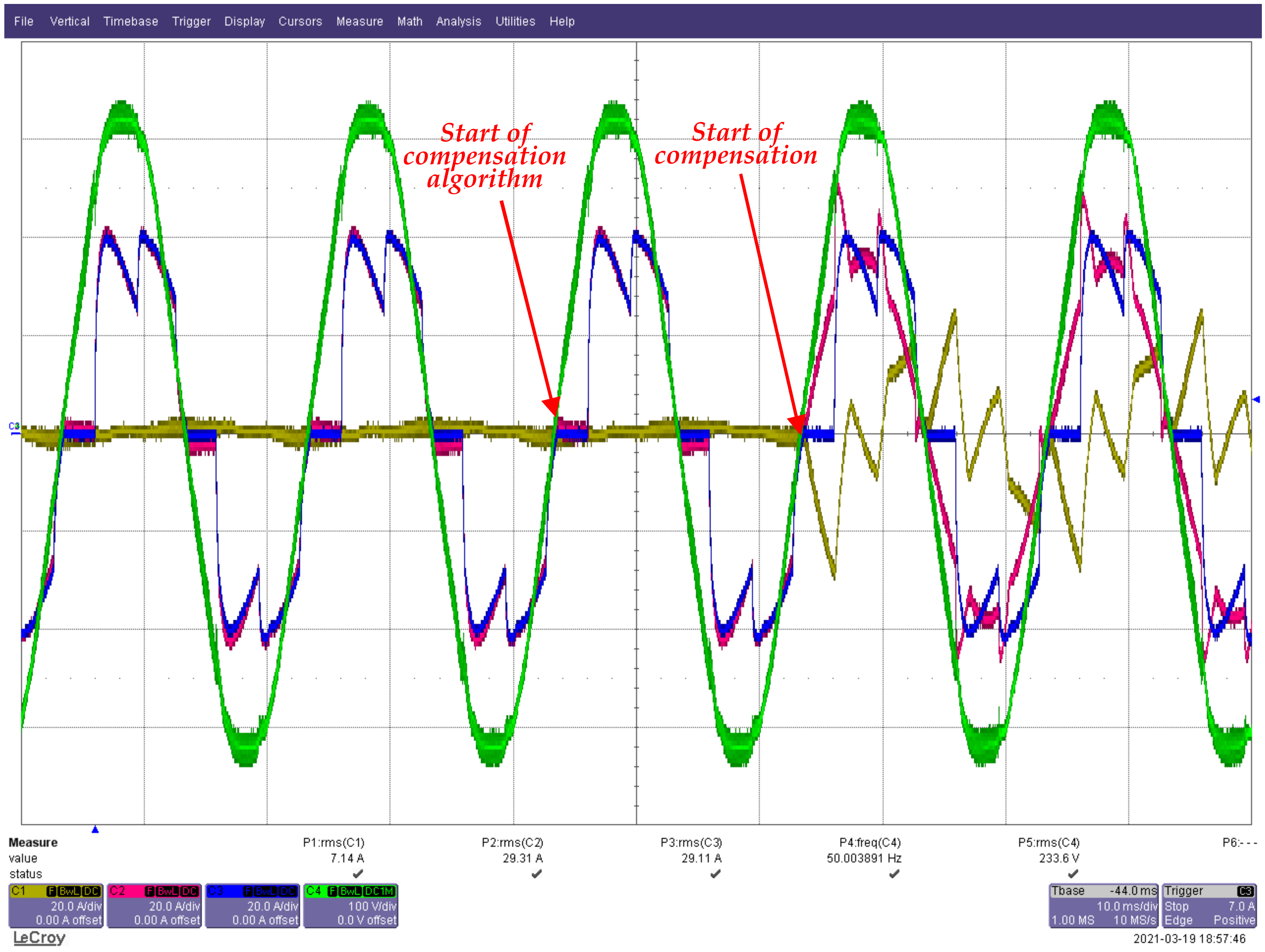

4. Laboratory Test of the APF

5. Discussion and Conclusions

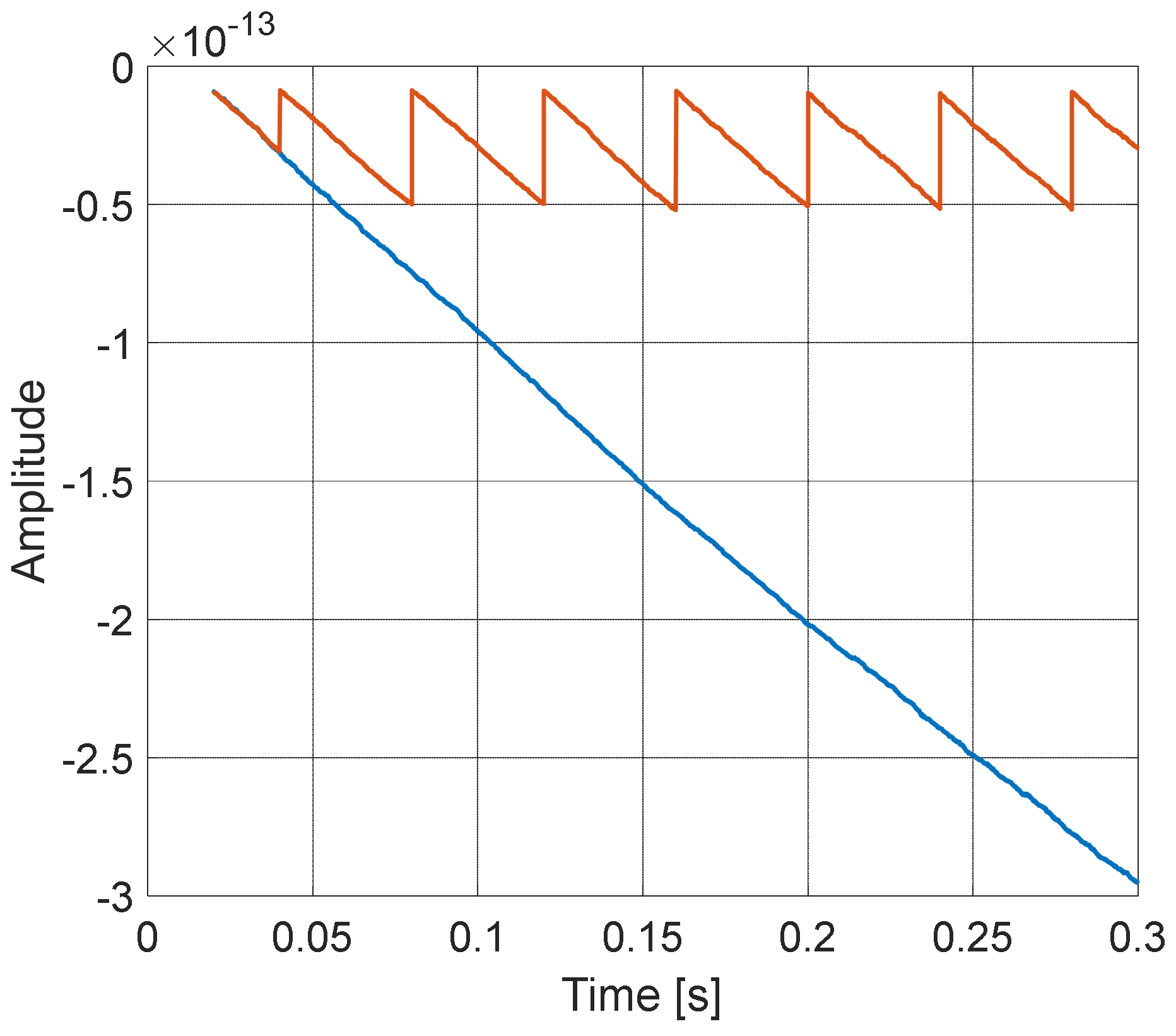

- Development of a method for stabilizing the SDFT algorithm for implementation using single precision floating point;

- The three-phase SSDFT requires only about 25% more arithmetic operations than classic SDFT;

- Development of a method for sampling signals using a limited number of sample and hold systems;

- The sample and hold circuits are triggered by a hardware counter, which minimizes the jitter phenomenon.

- Design and implementation of a complex and difficult device, such as APF.

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

List of Abbreviations and Symbols

| A/D | Analog-to-digital converter |

| APF | Active power filter |

| DFT | Discrete Fourier transformation |

| DSP | Digital signal processor |

| EMC | Electromagnetic compatibility |

| IC | Integrated circuit |

| PI | Proportional–integral controller |

| PLL | Phase lock loop |

| IGBT | Insulated gate bipolar transistor |

| MCU | Microcontroller unit |

| PWM | Pulse width modulation |

| SDFT | Sliding discrete Fourier transformation |

| SSDFT | Switching sliding discrete Fourier transformation |

| THD | Total harmonics distortion ratio |

| fc | Transistor switching frequency |

| fs | Sampling frequency |

| iL | Load current |

| iC | Compensation current |

| iM | Line current |

| NM | Number samples per line period |

| S1(n) | Discrete signal representing first harmonic complex spectral component of load current |

| Ts | Sampling period |

| uDC1, uDC1 | DC bank voltages |

| uM | Line voltage |

| u | Current controller output signal |

| us | DC bank voltage controller output signal |

| ur | DC bank difference voltage controller output signal |

References

- Ciok, Z.; Królikowski, L.; Nowakowski, R.; Szymczak, P. Michał Doliwo-Dobrowolski-Współtwórca Cywilizacji Technicznej XX Wieku; Wiadomości Elektrotechniczne: Warsaw, Poland, 2009; R. 77, nr 1; pp. 38–49. (In Polish) [Google Scholar]

- Available online: https://bezel.com.pl/2016/11/24/michal-doliwo-dobrowolski/ (accessed on 5 January 2023).

- Available online: https://en.wikipedia.org/wiki/Mikhail_Dolivo-Dobrovolsky (accessed on 5 January 2023).

- Klug, W. Die Elektrische Kraftűbertragungsanlage Eichdorf—Grünberg in Schl.; Elektrotechnische Zeitsdrift (ETZ): Berlin, Germany, 1896; H. 45; pp. 686–689. [Google Scholar]

- Bird, B.; Marsh, J.; McLellan, P. Harmonic reduction in multiple converters by triple-frequency current injection. IEEE Proc. 1969, 116, 1730–1734. [Google Scholar]

- Gyugi, L.; Strycula, E. Active ac Power Filters. In Proceedings of the IEEE IAS Annual Meeting, Chicago, IL, USA, 11–14 October 1976; pp. 529–535. [Google Scholar]

- Mohan, N.; Peterson, H.; Long, W.; Dreifuerst, G.; Vithaythil, J. Active Filters for AC Harmonic Suppression. In Proceedings of the IEEE/PES Winter Meeting, New York, NY, USA, 30 January–4 February 1977. [Google Scholar]

- Uceda, J.; Aldana, F.; Martinez, P. Active filters for static power converters. IEEE Proc. B 1983, 130, 347–354. [Google Scholar]

- Kawahira, H.; Nakamura, T.; Nakazawa, S.; Nomura, M. Active Power Filter. In Proceedings of the International Power Electronics Conference, Tokyo, Japan, 27–31 March 1983; pp. 981–992. [Google Scholar]

- Akagi, H.; Kanazawa, Y.; Nabae, A. Generalized Theory of the Instantaneous Reactive Power in Three-Phase Circuits. In Proceedings of the International Power Electronics Conference, Tokyo, Japan, 27–31 March 1983; pp. 1375–1386. [Google Scholar]

- Akagi, H.; Tsukamoto, Y.; Nabae, A. Analysis and design of an active power filter using quad-series voltage-source PWM converters. IEEE Trans. Ind. Appl. 1990, 26, 93–98. [Google Scholar] [CrossRef]

- Peng, F.; Akagi, H.; Nabae, A. A study of active power filters using quad-series voltage-source PWM converters for harmonic compensation. IEEE Trans. Power Electron. 1990, 5, 9–15. [Google Scholar] [CrossRef]

- Moran, S. A Line Voltage Regulator/Conditioner for Harmonic Sensitive Load Isolation. In Proceedings of the IEEE/IAS Annual Meeting, San Diego, CA, USA, 1–5 October 1989; pp. 947–951. [Google Scholar]

- Akagi, H. Trends in active power line conditioners. IEEE Trans. Power Electron. 1994, 9, 263–268. [Google Scholar] [CrossRef]

- Akagi, H. New Trends in Active Filters. In Proceedings of the International Conference on Power Electronics, Drives and Energy Systems for Industrial Growth, New Delhi, India, 8–11 January 1996; pp. 17–26. [Google Scholar]

- Akagi, H. New Trends in Active Filters for Power Conditioning. IEEE Trans. Ind. Appl. 1996, 32, 1312–1322. [Google Scholar] [CrossRef]

- Singh, B.; Al-Haddad, K.; Chandra, A. A review of active filters for power quality improvement. IEEE Trans. Ind. Electron. 1999, 46, 960–971. [Google Scholar] [CrossRef]

- Peng, F.Z. Harmonic sources and filtering approaches. IEEE Ind. Appl. Mag. 2001, 7, 18–25. [Google Scholar] [CrossRef]

- Akagi, H. Active harmonic filters. Proc. IEEE 2005, 93, 2128–2141. [Google Scholar] [CrossRef]

- Akagi, H.; Watanabe, E.H.; Aredes, M. Instantaneous Power Theory and Applications to Power Conditioning; Wiley-IEEE Press: Hoboken, NJ, USA, 2007. [Google Scholar]

- Benysek, G.; Pasko, M. (Eds.) Power Theories for Improved Power Quality; Springer: London, UK, 2012. [Google Scholar]

- Afonso, J.L.; Tanta, M.; Pinto, J.G.O.; Monteiro, L.F.C.; Machado, L.; Sousa, T.J.C.; Monteiro, V. A Review on Power Electronics Technologies for Power Quality Improvement. Energies 2021, 14, 8585. [Google Scholar] [CrossRef]

- Buła, D.; Grabowski, D.; Maciążek, M. A Review on Optimization of Active Power Filter Placement and Sizing Methods. Energies 2022, 15, 1175. [Google Scholar] [CrossRef]

- Das, S.R.; Ray, P.K.; Sahoo, A.K.; Ramasubbareddy, S.; Babu, T.S.; Kumar, N.M.; Elavarasan, R.M.; Mihet-Popa, L. A Com-prehensive Survey on Different Control Strategies and Applications of Active Power Filters for Power Quality Improvement. Energies 2021, 14, 4589. [Google Scholar] [CrossRef]

- Asiminoaei, L.; Blaabjerg, F.; Hansen, S. Detection is key—harmonic detection methods for active power filter applications. IEEE Ind. Appl. Mag. 2007, 13, 22–33. [Google Scholar] [CrossRef]

- Sozanski, K. Digital Signal Processing in Power Electronics Control Circuits, 2nd ed.; Springer: London, UK, 2017. [Google Scholar]

- Jacobsen, E.; Lyons, R. The sliding DFT. IEEE Signal Process. Mag. 2003, 20, 74–80. [Google Scholar]

- Jacobsen, E.; Lyons, R. An update to the sliding DFT. IEEE Signal Process. Mag. 2004, 21, 110–111. [Google Scholar] [CrossRef]

- Jacobsen, E. Understanding and Implementing the Sliding DFT, dsprelated.com. The Related Media Group. Available online: https://www.dsprelated.com/ (accessed on 5 January 2023).

- Sherlock, B.G.; Monro, D.M. Moving discrete Fourier transform. IEE Proc. Radar Signal Process. 1992, 139, 279–282. [Google Scholar] [CrossRef]

- Brown, A. Running Fourier Transforms; Electronics World: Maidstone, UK, 1998; p. 959. [Google Scholar]

- Assous, S.; Linnett, L. High resolution time delay estimation using sliding discrete Fourier transform. Digit. Signal Process. 2012, 22, 820–827. [Google Scholar] [CrossRef]

- Lyons, R. Understanding Digital Signal Processing, 3rd ed.; Prentice Hall: Upper Saddle River, NJ, USA, 2011; pp. 479–498. [Google Scholar]

- Douglas, S.; Soh, J. A Numerically Stable Sliding-Window Estimator and Its Application to Adaptive Filters. In Proceedings of the 31st Asilomar Conference on Signals, Systems, and Computers, Pacific Grove, CA, USA, 31 October–2 November 1997; Volume 1, pp. 111–115. [Google Scholar]

- Gufovskiy, D.; Chu, L. An accurate and stable sliding DFT computed by a modified CIC filter. IEEE Signal Process. Mag. 2017, 34, 89–93. [Google Scholar] [CrossRef]

- Lyons, R. Streamlining Digital Signal Processing: A Tricks of the Trade Guide-Book; Wiley: Hoboken, NJ, USA, 2012. [Google Scholar]

- Sozanski, K.; Jarnut, M. Three-Phase Active Power Filter Using the Sliding DFT Control Algorithm. In Proceedings of the 11th European Conference on Power Electronics and Applications, Dresden, Germany, 11–14 September 2005. [Google Scholar]

- Sozanski, K. Harmonic Compensation Using the Sliding DFT Algorithm. In Proceedings of the IEEE 35th Annual Power Electronics Specialists Conference —PESC ’04, Aachen, Germany, 20–25 June 2004. [Google Scholar]

- Lyons, R.; Howard, C. Improvements to the Sliding Discrete Fourier Transform Algorithm. IEEE Signal Process. Mag. 2021, 38, 119–127. [Google Scholar] [CrossRef]

- Duda, K. Accurate, guaranteed stable, sliding discrete Fourier transform. IEEE Signal Process. Mag. 2010, 27, 124–127. [Google Scholar]

- Park, C.S. Fast, accurate, and guaranteed stable sliding discrete Fourier transform. IEEE Signal Process. Mag. 2015, 32, 145–156. [Google Scholar] [CrossRef]

- Li, K.; Nai, W. Rapid Extraction of the Fundamental Components for Non-Ideal Three-Phase Grid Based on an Improved Sliding Discrete Fourier Transform. Electronics 2022, 11, 1915. [Google Scholar] [CrossRef]

- Tan, G.; Fu, Q.; Xia, T.; Zhang, X. Development of Frequency Fixed Sliding Discrete Fourier Transform Filter Based Single-Phase Phase-Locked Loop. IEEE Access 2021, 9, 110573–110581. [Google Scholar] [CrossRef]

- Orallo, C.M.; Carugati, I. Single Bin Sliding Discrete Fourier Transform. In Fourier Transforms—High-Tech Application and Current Trends; Nikolic, G.S., Cakic, M.D., Cvetkovic, D.J., Eds.; IntechOpen: London, UK, 2017. [Google Scholar] [CrossRef]

- Kulshreshtha, T.; Dhar, A.S. Improved VLSI architecture for triangular windowed sliding DFT based on CORDIC algorithm. IET Circuits Devices Syst. 2019, 13, 251–258. [Google Scholar] [CrossRef]

- Kollar, Z.; Plesznik, F.; Trumpf, S. Observer-Based Recursive Sliding Discrete Fourier Transform [Tips & Tricks]. IEEE Signal Process. Mag. 2018, 35, 100–106. [Google Scholar] [CrossRef]

- Juang, W.H.; Lai, S.C.; Luo, C.H.; Lee, S.Y. VLSI Architecture for Novel Hopping Discrete Fourier Transform Computation. IEEE Access 2018, 6, 30491–30500. [Google Scholar] [CrossRef]

- Safapourhajari, S.; Kokkeler, A.B.J. On the Low Complexity Implementation of the DFT-Based BFSK Demodulator for Ultra-Narrowband Communications. IEEE Access 2020, 8, 146666–146682. [Google Scholar] [CrossRef]

- TMS320F2837xD Dual-Core Microcontrollers, Data Sheet, Texas Instruments, SPRS880O, FEBRUARY 2021. Available online: https://www.ti.com/lit/ds/sprs880m/sprs880m.pdf (accessed on 5 January 2023).

- LAUNCHXL-F28379D Overview, User’s Guide (Rev. C); SPRUI77C; Texas Instruments: Dallas, TX, USA, 2019.

- ACS770xCB, Data Sheet; ACS770-Datasheet; Allegro MicroSystems: Manchester, NH, USA, 2021.

- AMC1311x High-Impedance, 2-V Input, Reinforced Isolated Amplifiers, Data Sheet; SBAS786C; Texas Instruments: Dallas, TX, USA, 2022.

- Swiss Grid. Available online: https://www.swissgrid.ch/en/home/operation/regulation/frequency.html#grid-time-deviation (accessed on 18 November 2022).

- Sozanski, K.; Sozanska, A. Multirate Shunt Active Power Filter with Improved Dynamic Parameters. In Proceedings of the Signal Processing, Algorithms, Architectures, Arrangements and Applications, Poznan, Poland, 20–22 September 2017; pp. 137–142. [Google Scholar]

- Sozanski, K. Video of APF with SSDFT. Available online: https://staff.uz.zgora.pl/ksozansk/files/My%20APF/APF_with_SSDFT.mp4 (accessed on 15 January 2023).

| Symbol | Value |

|---|---|

| C1, C2 | 4.4 mF/450 V |

| LC1, LC2, LC3 | 2.4 mH/50 A |

| CC1, CC2, CC3 | 3 µF/1200 V |

| RC1, RC2, RC3 | 10 Ω/10 W |

| fc | 25,600 Hz |

| fs | 25,600 Hz |

| iC1max, iC2max, iC3max, | 50 A |

| uDC1, uDC2 | 400 V |

| Q1…Q6 | IGBT FF100R12RT4 |

| MCU | TMS320F28379D, 100 MHz |

| Sampling Cycle | ADC Channel A | ADC Channel B | ADC Channel C | ADC Channel D |

|---|---|---|---|---|

| 1 | iL1(t) | iL2(t) | iL3(t) | uDC1(t) |

| 2 | iC1(t) | iC2(t) | iC3(t) | uDC2(t) |

| 3 | iL1(t) | iL2(t) | iL3(t) | temp(t) |

| State Number | Line Period | SDFT1 | SDFT2 |

|---|---|---|---|

| 1 | 1 | IL -> S | 0 |

| 2 | 1 | IL -> S | IL |

| 3 | 1 | 0 | IL -> S |

| 4 | 1 | IL | IL -> S |

| State Number | The Number of Line Period | SDFT1 | SDFT2 | SDFT3 | SDFT4 |

|---|---|---|---|---|---|

| 1 | 8 | IL1 -> S1 | IL2 -> S2 | IL3 -> S3 | 0 |

| 2 | 1 | IL1 -> S1 | IL2 -> S2 | IL3 -> S3 | IL1 |

| 3 | 8 | 0 | IL2 -> S2 | IL3 -> S3 | IL1 -> S1 |

| 4 | 1 | IL1 | IL2 -> S2 | IL3 -> S3 | IL1 -> S1 |

| 5 | 8 | IL1 -> S1 | IL2 -> S2 | IL3 -> S3 | 0 |

| 6 | 1 | IL1 -> S1 | IL2 -> S2 | IL3 -> S3 | IL2 |

| 7 | 8 | IL1 -> S1 | 0 | IL3 -> S3 | IL2 -> S2 |

| 8 | 1 | IL1 -> S1 | IL2 | IL3 -> S3 | IL2 -> S2 |

| 9 | 8 | IL1 -> S1 | IL2 -> S2 | IL3 -> S3 | 0 |

| 10 | 1 | IL1 -> S1 | IL2 -> S2 | IL3 -> S3 | IL3 |

| 11 | 8 | IL1 -> S1 | IL2 -> S2 | 0 | IL3 -> S3 |

| 12 | 1 | IL1 -> S1 | IL2 -> S2 | IL3 | IL3 -> S3 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Sozanski, K.; Szczesniak, P. Advanced Control Algorithm for Three-Phase Shunt Active Power Filter Using Sliding DFT. Energies 2023, 16, 1453. https://doi.org/10.3390/en16031453

Sozanski K, Szczesniak P. Advanced Control Algorithm for Three-Phase Shunt Active Power Filter Using Sliding DFT. Energies. 2023; 16(3):1453. https://doi.org/10.3390/en16031453

Chicago/Turabian StyleSozanski, Krzysztof, and Pawel Szczesniak. 2023. "Advanced Control Algorithm for Three-Phase Shunt Active Power Filter Using Sliding DFT" Energies 16, no. 3: 1453. https://doi.org/10.3390/en16031453

APA StyleSozanski, K., & Szczesniak, P. (2023). Advanced Control Algorithm for Three-Phase Shunt Active Power Filter Using Sliding DFT. Energies, 16(3), 1453. https://doi.org/10.3390/en16031453