Single-Phase Grid-Forming Strategy with Power Decoupling Implementation for Electrolytic-Capacitor-Free EV Smart Battery Charger

Abstract

1. Introduction

1.1. Motivation

1.2. Literature Review

1.3. Contributions

- Unlike typical GFM studies, where inverters using electrolytic capacitors on the DC Link with high capacitance values and small DC-link ripple are considered, this article proposes a novel approach to implement a GFM control strategy in an isolated single-phase DC-AC converter considering a high DC-link ripple and smaller DC-link capacitance values, intended for electrolytic-capacitor-free EV SBCs. The proposed GFM control strategy provides voltage and frequency support in grid-connected operation (V2G mode) and stand-alone operation to supply energy to islanded loads (V2H mode), obtaining high-quality power in both terminals (grid and battery), even in the presence of high DC-link ripple.

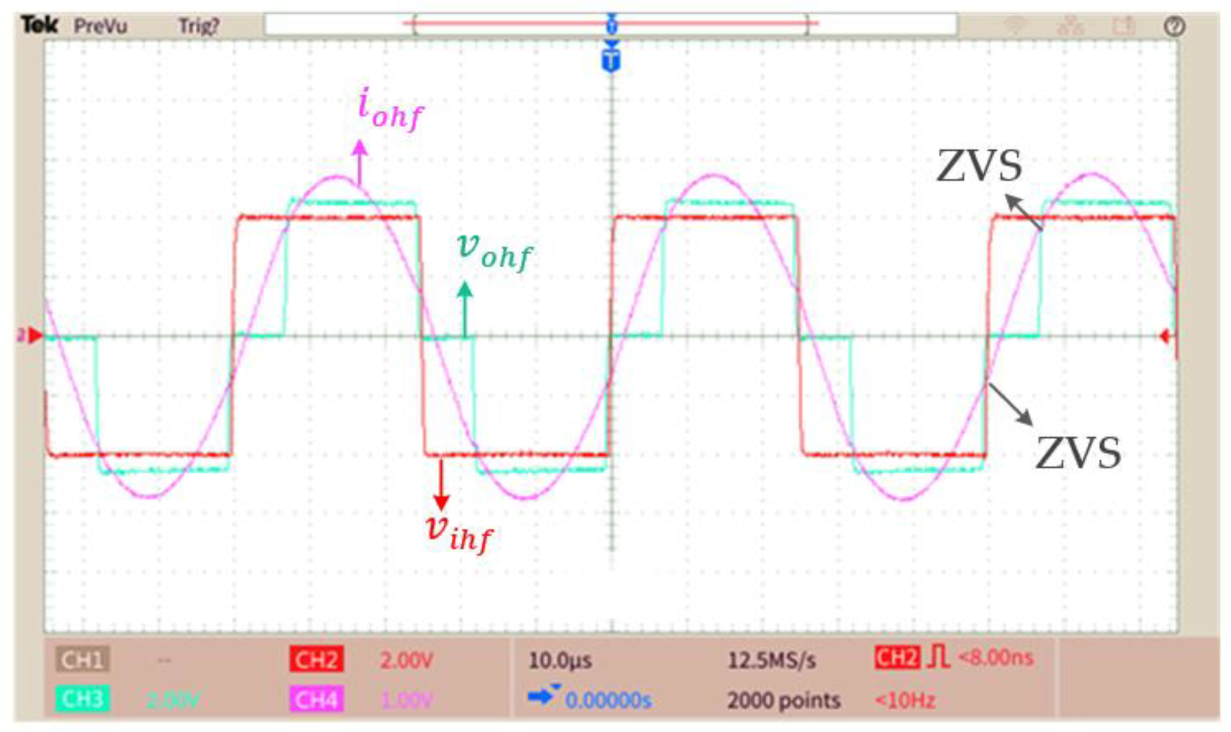

- A novel power decoupling for a DABSR DC-DC converter is introduced. In the proposed strategy the phase-shift angle controls the average DC-link voltage while the duty-ratio angle compensates for the high DC-link ripple. The proposed power decoupling mitigates the LFR on the DC current. The proposed modulation obtains minimal HF current and ZVS mode in the DABSR DC-DC converter. Therefore, high efficiency can be obtained.

1.4. Organization

2. Converter Structure

2.1. Voltage Source Inverter Stage

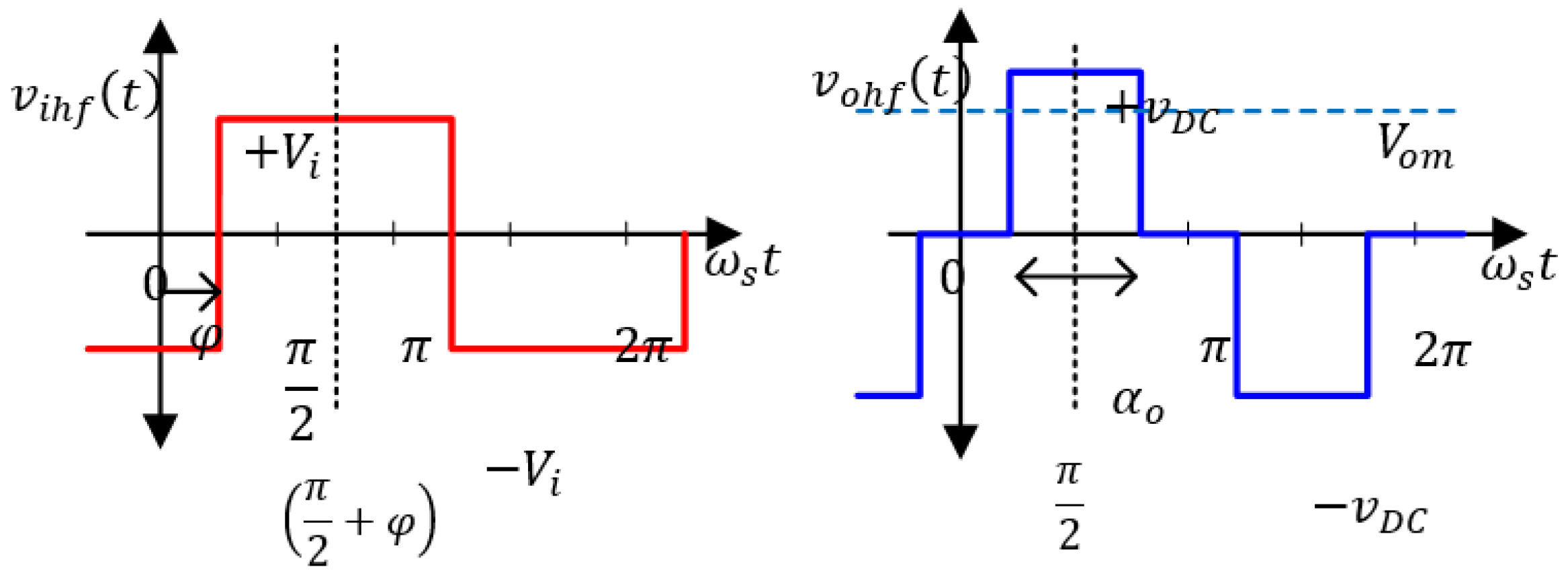

2.2. Dual-Active Bridge Series-Resonant Stage

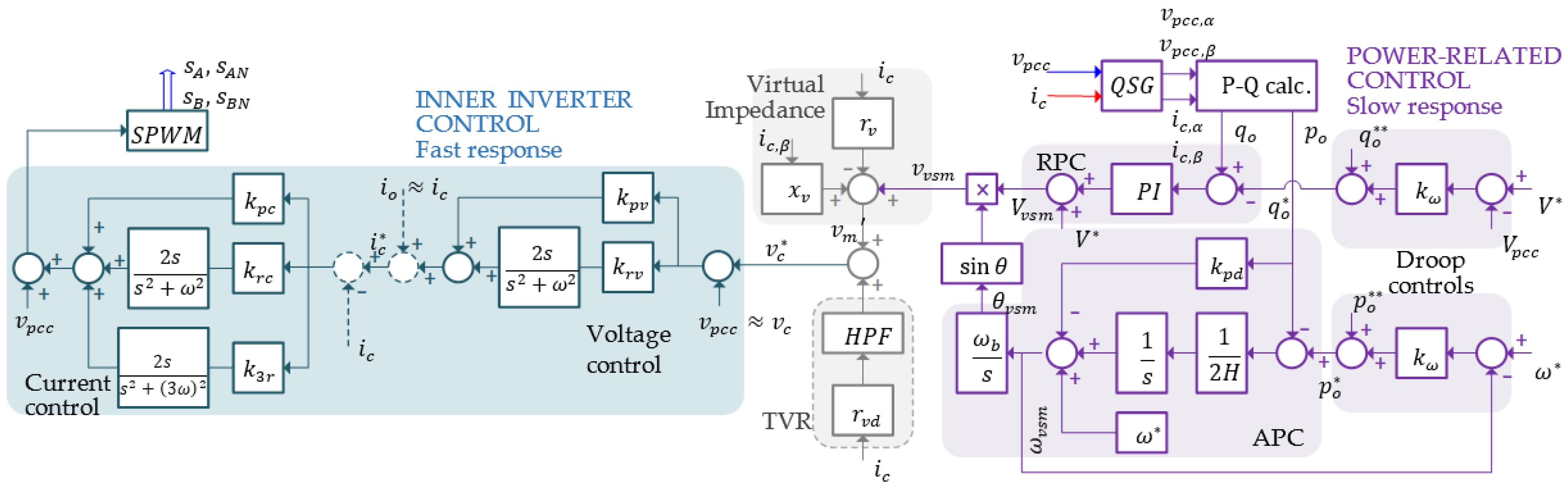

3. DC-AC Control: Single-Phase GFM with Improved Stability

3.1. Power-Related Control

3.1.1. Droop Control

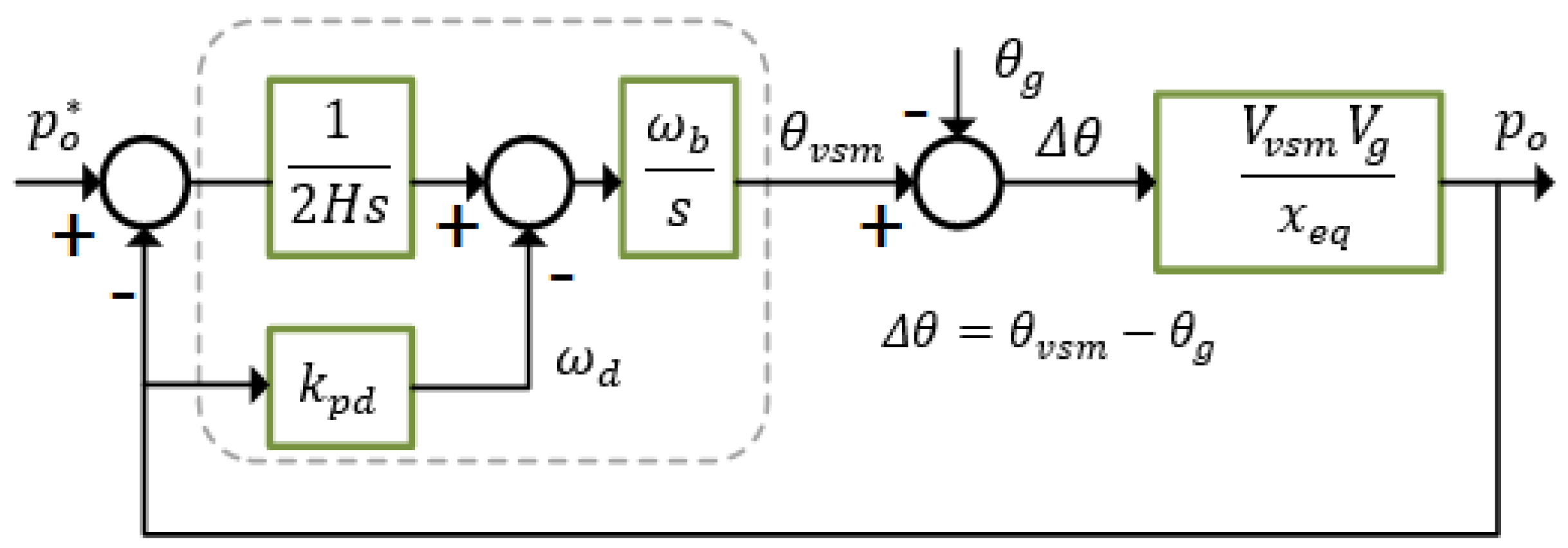

3.1.2. Active Power Control

3.1.3. Reactive Power Control

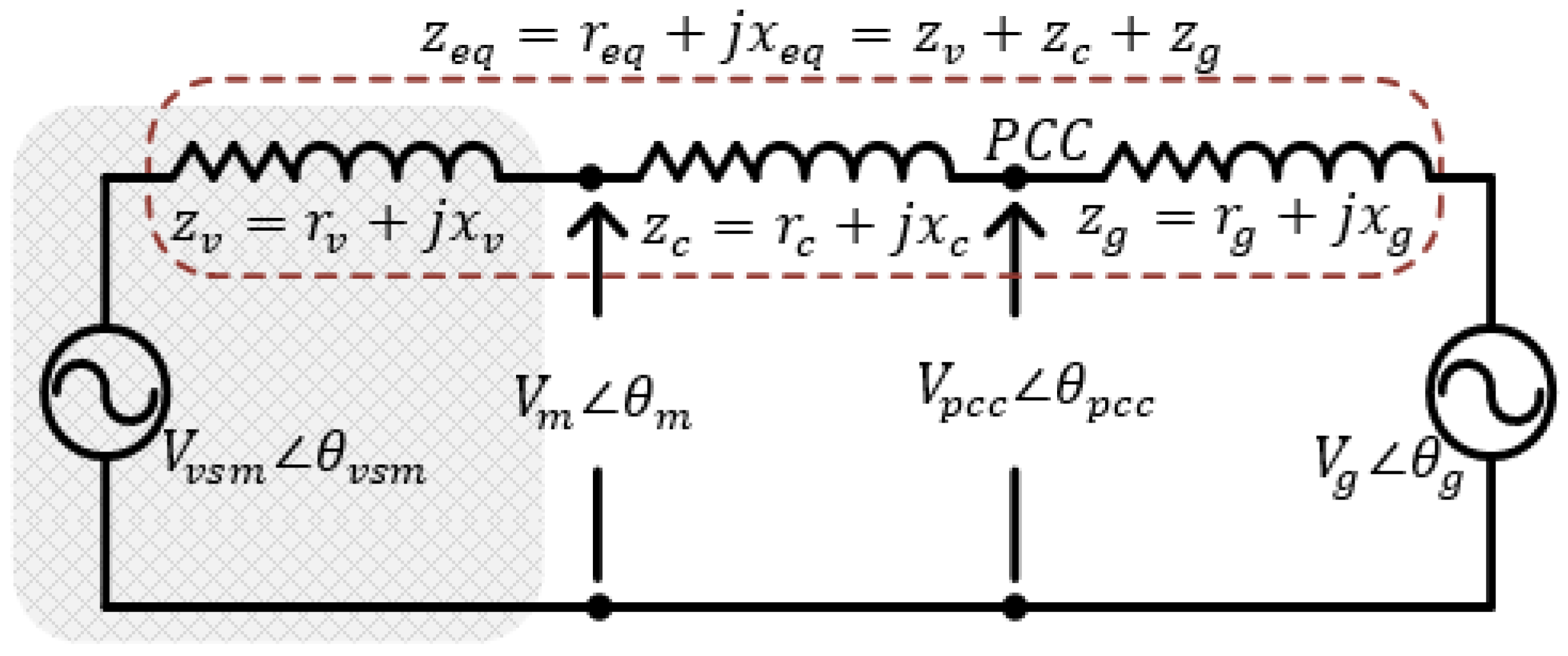

3.2. Virtual Impedance and Stability Improvement

Stability Improvement Using Transitory Virtual Resistance

3.3. Inner Inverter Control

4. DC-DC Control: DC-Link Control and Active Power Decoupling

4.1. Active Power Decoupling Based on DR Modulation

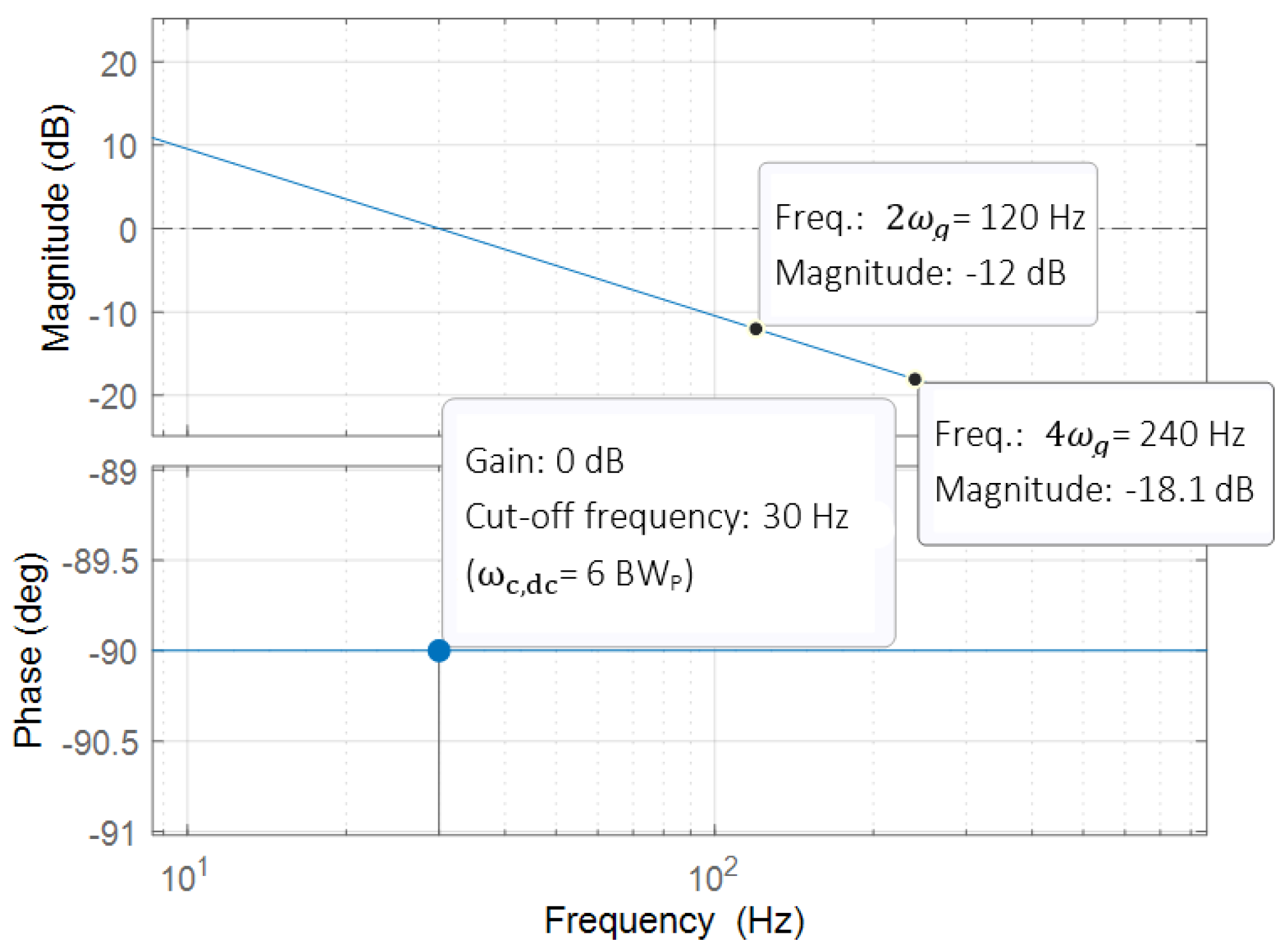

4.2. DC-Link Voltage Control

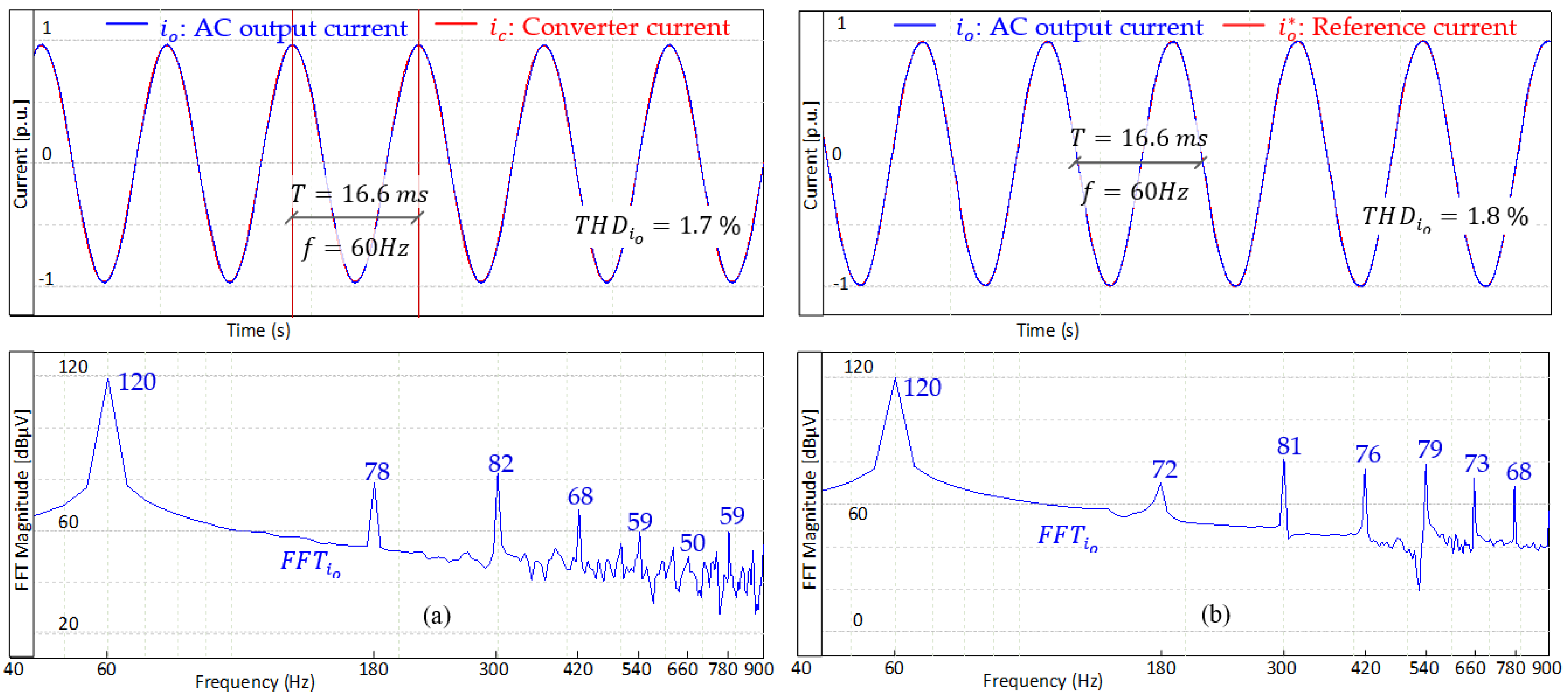

5. Experimental Results Using Hardware-in-the-Loop

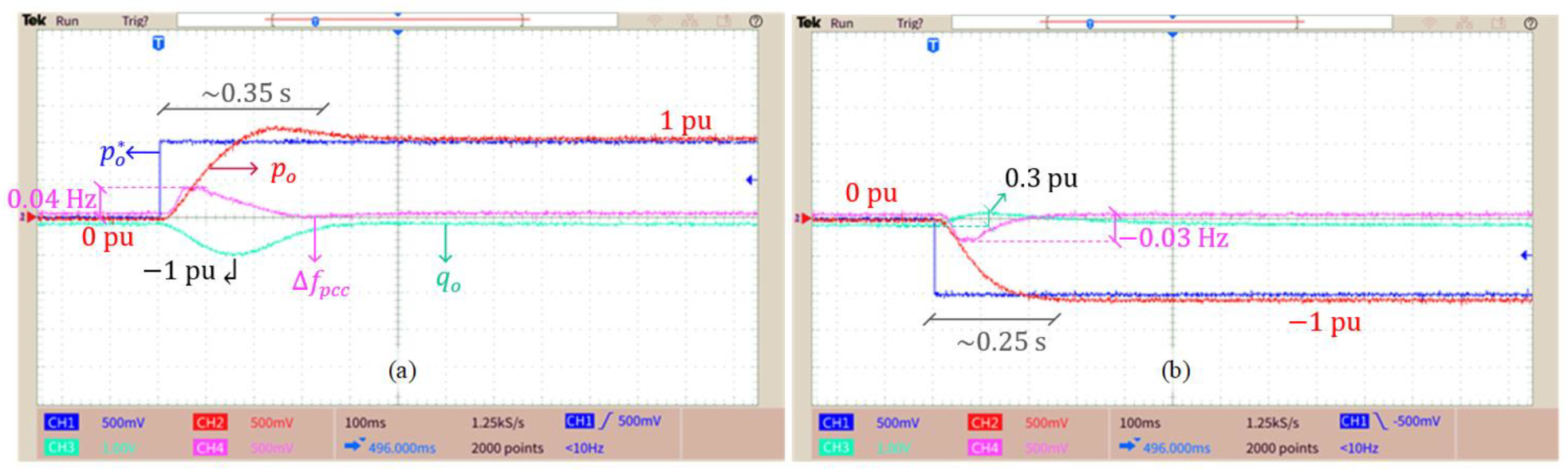

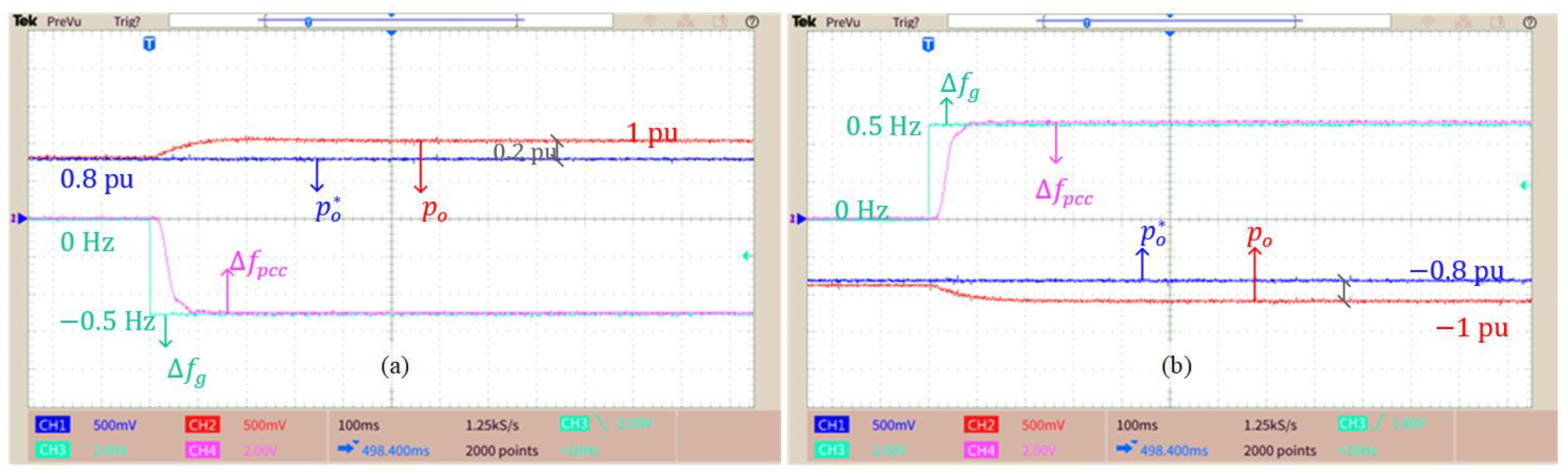

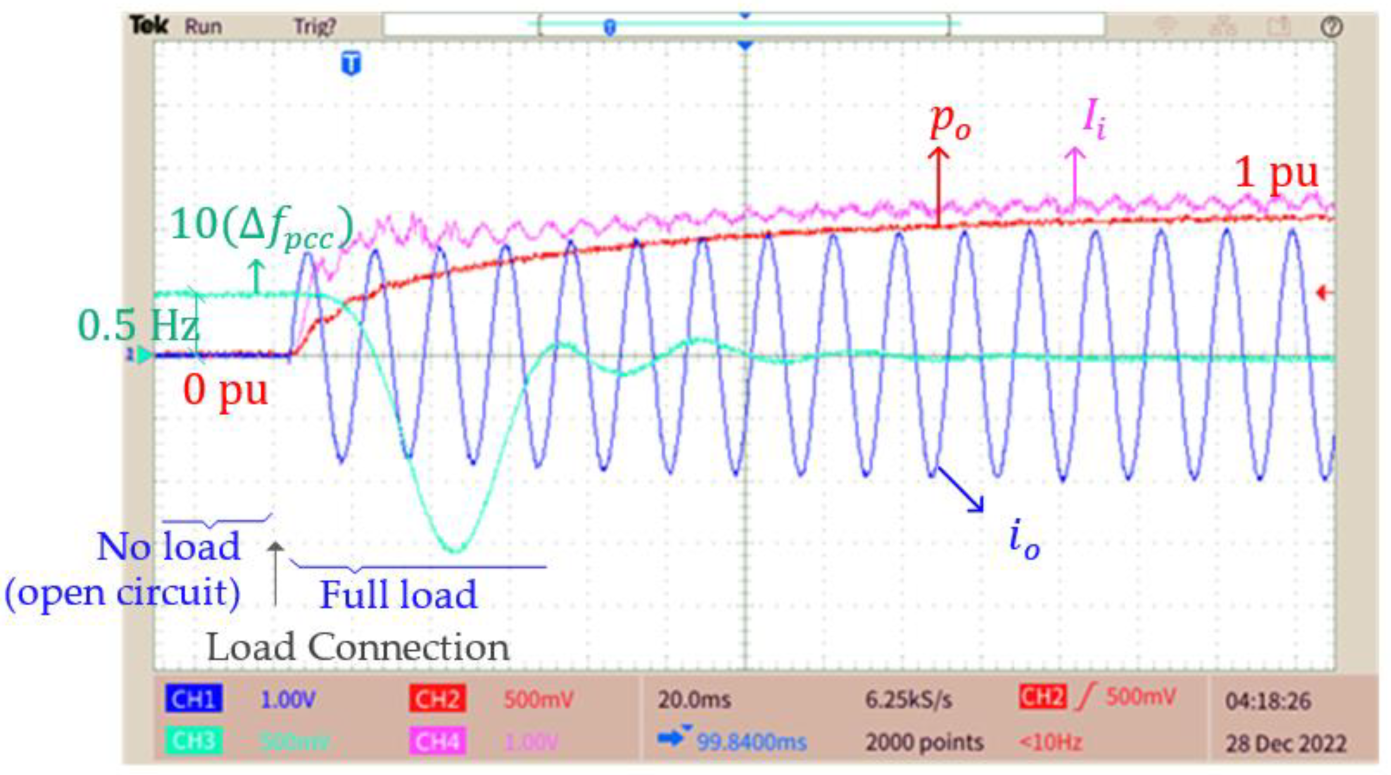

5.1. Dynamic Response to Frequency Events

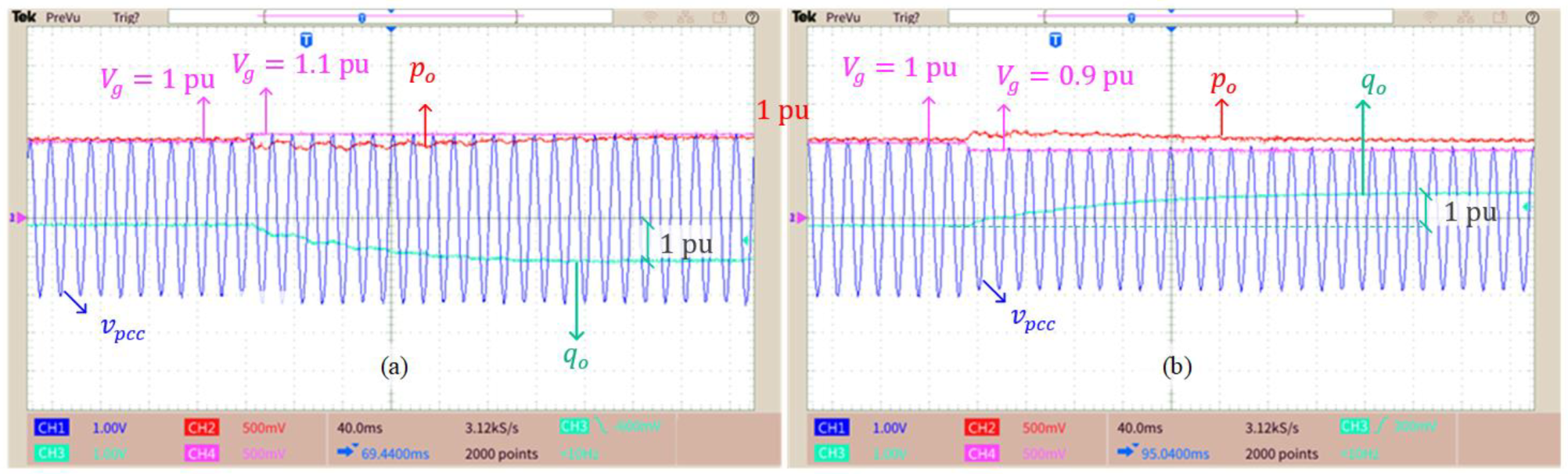

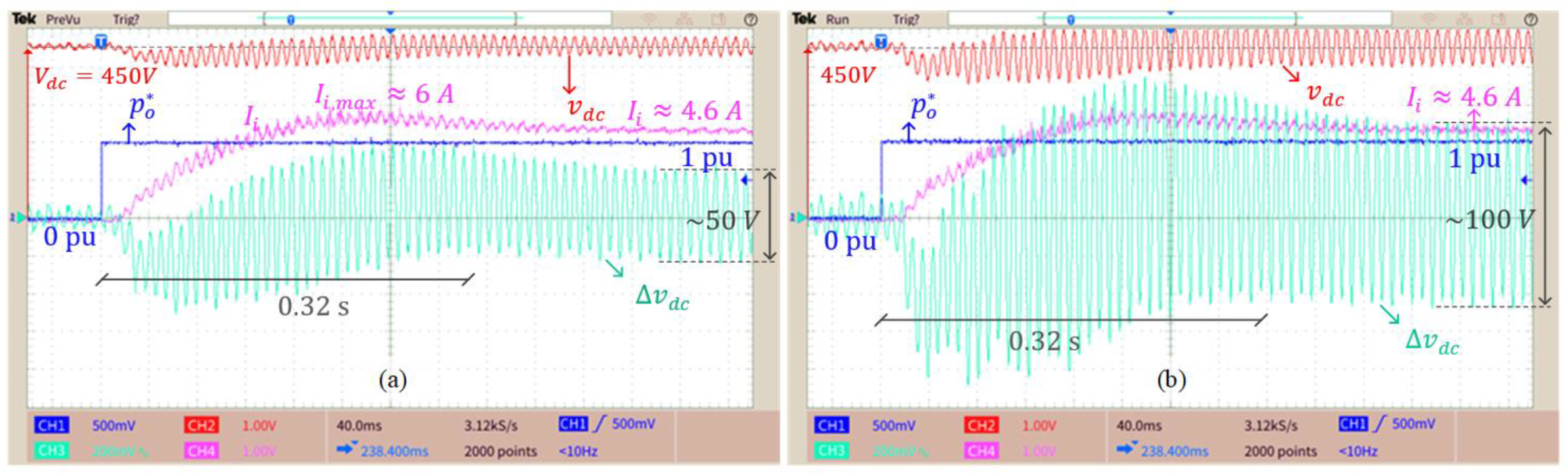

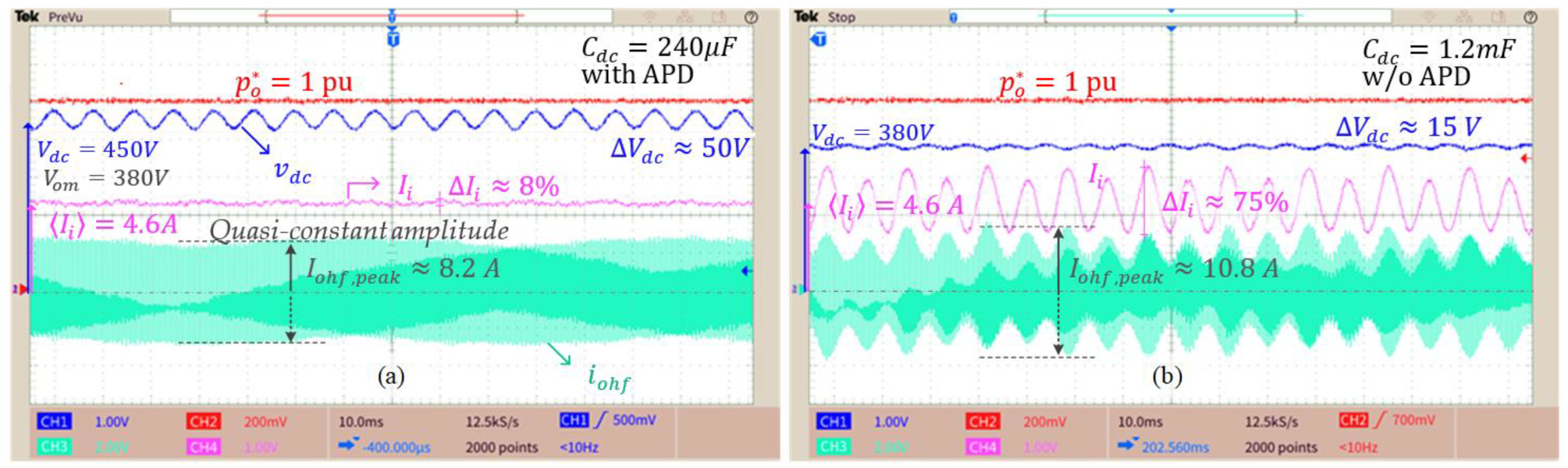

5.2. Power Decoupling Capability

6. Comparison with Previous Works

7. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Hu, Q.; Bu, S.; Terzija, V. A Distributed P and Q Provision-Based Voltage Regulation Scheme by Incentivized EV Fleet Charging for Resistive Distribution Networks. IEEE Trans. Transp. Electrif. 2021, 7, 2376–2389. [Google Scholar] [CrossRef]

- Restrepo, M.; Morris, J.; Kazerani, M.; Cañizares, C.A. Modeling and Testing of a Bidirectional Smart Charger for Distribution System EV Integration. IEEE Trans. Smart Grid 2018, 9, 152–162. [Google Scholar] [CrossRef]

- Monteiro, V.; Pinto, J.G.; Afonso, J.L. Operation Modes for the Electric Vehicle in Smart Grids and Smart Homes: Present and Proposed Modes. IEEE Trans. Veh. Technol. 2016, 65, 1007–1020. [Google Scholar] [CrossRef]

- Monteiro, V.; Exposto, B.; Ferreira, J.C.; Afonso, J.L. Improved Vehicle-to-Home (iV2H) Operation Mode: Experimental Analysis of the Electric Vehicle as Off-Line UPS. IEEE Trans. Smart Grid 2017, 8, 2702–2711. [Google Scholar] [CrossRef]

- Sfakianakis, G.E.; Everts, J.; Lomonova, E.A. Overview of the requirements and implementations of bidirectional isolated AC-DC converters for automotive battery charging applications. In Proceedings of the Ecological Vehicles and Renewable Energies (EVER) Conference, Monte Carlo, Monaco, 31 March–2 April 2015. [Google Scholar]

- Zhang, Y.; Fang, J.; Gao, F.; Gao, S.; Rogers, D.J.; Zhu, X. Integrated High- and Low-Frequency Current Ripple Suppressions in a Single-Phase Onboard Charger for EVs. IEEE Trans. Power Electron. 2021, 36, 1717–1729. [Google Scholar] [CrossRef]

- Iyer, V.M.; Gulur, S.; Bhattacharya, S. Small-Signal Stability Assessment and Active Stabilization of a Bidirectional Battery Charger. IEEE Trans. Ind. Appl. 2019, 55, 563–574. [Google Scholar] [CrossRef]

- Gautam, A.R.; Fulwani, D.M.; Makinen, R.R.; Rathore, A.K.; Singh, D. Control Strategies and Power Decoupling Topologies to Mitigate 2ω-Ripple in Single Phase Inverters: A Review and Open Challenges. J. IEEE Access 2020, 8, 147533–147559. [Google Scholar] [CrossRef]

- Sun, Y.; Liu, Y.; Su, M.; Xiong, W.; Yang, J. Review of Active Power Decoupling Topologies in Single-Phase System. IEEE Trans. Power Electron. 2016, 31, 4778–4794. [Google Scholar] [CrossRef]

- Liu, Y.; Zhang, W.; Sun, Y.; Su, M.; Xu, G.; Dan, H. Review and Comparison of Control Strategies in Active Power Decoupling. IEEE Trans. Power Electron. 2021, 36, 14436–14455. [Google Scholar] [CrossRef]

- Wang, H.; Wang, H.; Zhu, G.; Blaabjerg, F. An Overview of Capacitive DC-Links-Topology Derivation and Scalability Analysis. IEEE Trans. Power Electron. 2020, 35, 1805–1829. [Google Scholar] [CrossRef]

- Kisacikoglu, M.C.; Kesler, M.; Tolbert, L.M. Single-Phase On-Board Bidirectional PEV Charger for V2G Reactive Power Operation. IEEE Trans. Smart Grid 2015, 6, 767–775. [Google Scholar] [CrossRef]

- De Melo, H.N.; Trovao, J.P.F.; Pereirinha, P.G.; Jorge, H.M.; Antunes, C.H. A Controllable Bidirectional Battery Charger for Electric Vehicles with Vehicle-to-Grid Capability. IEEE Trans. Veh. Technol. 2018, 67, 114–123. [Google Scholar] [CrossRef]

- Kazemtarghi, A.; Dey, S.; Mallik, A. Optimal Utilization of Bidirectional EVs For Grid Frequency Support in Power Systems. IEEE Trans. Power Deliv. 2022, 1–13. [Google Scholar] [CrossRef]

- Zhang, Z.; Liu, B.; Song, S. Power Decoupling Control for V2G/G2V/PV2G Operation Modes in Single-Phase PV/Battery Hybrid Energy System with Low DC Link Capacitance. J. IEEE Access 2021, 9, 160975–160986. [Google Scholar] [CrossRef]

- Xu, J.; Soeiro, T.B.; Gao, F.; Tang, H.; Bauer, P. Minimum Switching Losses Discontinuous PWM Strategy for Bidirectional Single-Phase AC–DC Converter with Active Power Decoupling. IEEE Trans. Power Electron. 2021, 36, 6118–6132. [Google Scholar] [CrossRef]

- Sal y Rosas, D.; Frey, D.; Schanen, J.-L.; Ferrieux, J.-P. Isolated Single Stage Bidirectional AC-DC Converter with Power Decoupling and Reactive Power Control to Interface Battery with the Single-Phase Grid. In Proceedings of the 2018 IEEE Applied Power Electronics Conference and Exposition (APEC), San Antonio, TX, USA, 4–8 March 2018; 2018; pp. 631–636. [Google Scholar] [CrossRef]

- Patil, D.; Agarwal, V. Compact Onboard Single-Phase EV Battery Charger with Novel Low-Frequency Ripple Compensator and Optimum Filter Design. IEEE Trans. Veh. Technol. 2016, 65, 1948–1956. [Google Scholar] [CrossRef]

- Nguyen, H.V.; To, D.-D.; Lee, D.-C. Onboard Battery Chargers for Plugin Electric Vehicles with Dual Functional Circuit for Voltage Battery Charging and Active Power Decoupling. J. IEEE Access 2018, 6, 70212–70222. [Google Scholar] [CrossRef]

- Pantaleon, E.; y Rosas, D.S.; Espinoza, R. Modulation and Control Strategy for an isolated and bidirectional two-stage DC-AC converter with high ripple on the DC-Link to interface battery with the single-phase grid. In Proceedings of the PEDG Conference, Chicago, IL, USA, 28 June–1 July 2021. [Google Scholar]

- Liu, B.; Li, G.; He, D.; Chen, Y. DC and AC Power Quality Control for Single-Phase Grid-Tied PEMFC Systems with Low DC-Link Capacitance by Solution-Space-Reduced MPC. IEEE Trans. Ind. Electron. 2022, 69, 5625–5636. [Google Scholar] [CrossRef]

- Liu, X.; Li, H. An Electrolytic-Capacitor-Free Single-Phase High-Power Fuel Cell Converter with Direct Double-Frequency Ripple Current Control. IEEE Tran. Ind. Appl. 2015, 51, 297–308. [Google Scholar] [CrossRef]

- Meng, L.; Shu, Z.; Lei, Y.; Yan, H.; Li, Z.; Ma, L.; Yin, X.; He, X. Optimal Input and Output Power Quality Control of Single-Phase AC–DC–DC Converter with Significant DC-Link Voltage Ripple. IEEE Trans. Ind. Electron. 2020, 67, 10366–10376. [Google Scholar] [CrossRef]

- Lasseter, R.H.; Chen, Z.; Pattabiraman, D. Grid-Forming Inverters: A Critical Asset for the Power Grid. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 925–935. [Google Scholar] [CrossRef]

- Zhang, H.; Xiang, W.; Lin, W.; Wen, J. Grid Forming Converters in Renewable Energy Sources Dominated Power Grid: Control Strategy, Stability, Application, and Challenges. J. Mod. Power Syst. Clean Energy 2021, 9, 1239–1256. [Google Scholar] [CrossRef]

- Rathnayake, D.B.; Akrami, M.; Phurailatpam, C.; Me, S.P.; Hadavi, S.; Jayasinghe, G.; Zabihi, S.; Bahrani, B. Grid Forming Inverter Modeling, Control, and Applications. J. IEEE Access 2021, 9, 114781–114807. [Google Scholar] [CrossRef]

- Rosso, R.; Wang, X.; Liserre, M.; Lu, X.; Engelken, S. Grid Forming Converters: Control Approaches, Grid-Synchronisation and future Trends-A Review. IEEE Open J. Ind. Appl. 2021, 2, 93–109. [Google Scholar] [CrossRef]

- Kwon, M.; Park, S.; Oh, C.-y.; Lee, J.; Choi, S. Unified Control Scheme of Grid-Connected Inverters for Autonomous and Smooth Transfer to Stand-Alone Mode. IEEE Trans. Power Electron. 2022, 37, 416–425. [Google Scholar] [CrossRef]

- Liu, J.; Miura, Y.; Bevrani, H.; Ise, T. A Unified Modeling Method of Virtual Synchronous Generator for Multi-Operation-Mode Analyses. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 9, 2394–2409. [Google Scholar] [CrossRef]

- Deng, H.; Fang, J.; Qi, Y.; Tang, Y.; Debusschere, V. A Generic Voltage Control for Grid-Forming Converters with Improved Power Loop Dynamics. IEEE Trans. Ind. Electron. 2022, 1–13. [Google Scholar] [CrossRef]

- Suul, J.A.; D’Arco, S.; Guidi, G. Virtual Synchronous Machine-Based Control of a Single-Phase Bi-Directional Battery Charger for Providing Vehicle-to-Grid Services. IEEE Trans. Ind. Appl. 2016, 52, 3234–3244. [Google Scholar] [CrossRef]

- Ashtiani, N.A.; Khajehoddin, S.A.; Karimi-Ghartemani, M. Modeling and Stability Analysis of Single-Phase Microgrids Controlled in Stationary Frame. IEEE Trans. Power Electron. 2022, 37, 7759–7774. [Google Scholar] [CrossRef]

- Karimi-Ghartemani, M.; Sharma, R.; Zakerian, A.; Khajehoddin, S.A. A Single-phase Enhanced Grid-forming Controller with Converter Current Limiting. In Proceedings of the ECCE Conference, Vancouver, BC, Canada, 10–14 October 2021. [Google Scholar]

- Zarate, A.; Peña, J.C.U.; y Rosas, D.S. Isolated and Bidirectional two-stage DC/AC converter with grid-forming virtual inertia and high ripple on the DC bus for Single-Phase Grid applications. In Proceedings of the PEDG 2021, Chicago, IL, USA, 28 June–1 July 2021. [Google Scholar]

- Qoria, T.; Rokrok, E.; Bruyere, A.; Francoi, B.; Guillaud, X. A PLL-Free Grid-Forming Control with Decoupled Functionalities for High-Power Transmission System Applications. IEEE Access J. 2020, 8, 197363–197378. [Google Scholar] [CrossRef]

- Ruan, X.; Wang, X.; Pan, D.; Yang, D.; Li, W.; Bao, C. Control Techniques for LCL-Type Grid-Connected Inverters; CPSS Power Electronics Series; Springer: Singapore, 2018. [Google Scholar] [CrossRef]

- IEEE Standards Coordinating Committee. In IEEE Standard for Interconnection and Interoperability of Distributed Energy Resources with Associated Electric Power Systems Interfaces; IEEE: Piscataway, NJ, USA, 2018. [CrossRef]

- Li, X.; Bhat, A.K.S. Analysis and Design of High-Frequency Isolated Dual-Bridge Series Resonant DC/DC Converter. IEEE Trans. Power Electron. 2010, 25, 850–862. [Google Scholar] [CrossRef]

- Kundur, P. Power System Stability and Control; Balu, N.J., Ed.; McGraw-Hill: New York, NY, USA, 1994. [Google Scholar]

- Dokus, M.; Mertens, A. On the Coupling of Power-Related and Inner Inverter Control Loops of Grid-Forming Converter Systems. IEEE Access 2021, 9, 16173–16192. [Google Scholar] [CrossRef]

- Laaksonen, H.; Saari, P.; Komulainen, R. Voltage and Frequency Control of Inverter Based Weak LV Network Microgrid. In Proceedings of the 2005 International Conference on Future Power Systems, Amsterdam, The Netherlands, 18 November 2005; p. 6. [Google Scholar] [CrossRef]

- Taul, M.G.; Wang, X.; Davari, P.; Blaabjerg, F. Current Limiting Control with Enhanced Dynamics of Grid-Forming Converters During Fault Conditions. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 1062–1073. [Google Scholar] [CrossRef]

- Matas, J.; Castilla, M.; de Vicuna, L.G.; Miret, J.; Vasquez, J.C. Virtual Impedance Loop for Droop-Controlled Single-Phase Parallel Inverters Using a Second-Order General-Integrator Scheme. IEEE Trans. Power Electron. 2010, 25, 2993–3002. [Google Scholar] [CrossRef]

- Rodriguez, P.; Candela, I.; Citro, C.; Rocabert, J.; Luna, A. Control of Grid-Connected Power Converters Based on a Virtual Admittance Control Loop. In 2013 15th European Conference on Power Electronics and Applications (EPE); Lille, France, 2–6 September 2013, 2013. [Google Scholar] [CrossRef]

- Qoria, T. Grid-Forming Control to Achieve a 100% Power Electronics Interfaced Power Transmission Systems. Ph.D. Thesis, HESAM Université, Paris, France, 2020. [Google Scholar]

- Pereira, L.F.A.; Flores, J.V.; Bonan, G.; Coutinho, D.F.; da Silva, J.M.G. Multiple Resonant Controllers for Uninterruptible Power Supplies—A Systematic Robust Control Design Approach. IEEE Trans. Ind. Electron. 2014, 61, 1528–1538. [Google Scholar] [CrossRef]

- Zmood, D.N.; Holmes, D.G.; Bode, G.H. Frequency-Domain Analysis of Three-Phase Linear Current Regulators. IEEE Trans. Ind. Appl. 2001, 37, 601–610. [Google Scholar] [CrossRef]

- Teodorescu, R.; Blaabjerg, F.; Liserre, M.; Loh, P.C. Proportional-Resonant Controllers and Filters for Grid-Connected Voltage-Source Converters. IEE Proc.-Electr. Power Appl. 2006, 153, 750–762. [Google Scholar] [CrossRef]

- Yang, Z.; Zeng, J.; Yu, D.; Zhang, Q.; Zhang, Z. Two-Stage Power Decoupling for a Single-Phase Photovoltaic Inverter by Controlling the DC-Link Voltage Ripple in the DQ Frame. In Proceedings of the 2020 IEEE Applied Power Electronics Conference and Exposition (APEC), New Orleans, LA, USA, 15–19 March 2020. [Google Scholar] [CrossRef]

- Fang, J.; Li, H.; Tang, Y.; Blaabjerg, F. On the Inertia of Future More-Electronics Power Systems. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 7, 2130–2146. [Google Scholar] [CrossRef]

| Parameter | DC Link Capacitance Value | Capacitor Technology |

|---|---|---|

| Electrolytic | ||

| Filmic |

| Symbol | Parameter Description | Value |

|---|---|---|

| Nominal apparent power | ||

| Nominal RMS voltage | ||

| Nominal grid angular frequency | ||

| VSI and DAB switching frequency | ||

| LCL filter elements values | ||

| Grid infinite bus model inductance | ||

| DC-link film capacitance | ||

| Peak-to-peak DC-link voltage ripple | ||

| Average DC-link voltage | ||

| Minimum DC-link voltage | ||

| Series-resonant circuit quality factor | ||

| Series-resonant circuit elements values | ||

| HF transformer turns-ratio | ||

| Battery filter | ||

| Battery voltage |

| Symbol | Quantity | Value |

|---|---|---|

| PRR current controller gains | .2 | |

| PR voltage controller gains | ||

| Virtual resistance and reactance | ||

| TVR and cut-off frequency | ||

| Frequency and amplitude droop gains | ||

| Inertia constant and damping factor | ||

| Reactive power controller gains | ||

| DC-link voltage controller gains | ||

| APC bandwidth | rad/s | |

| DC-link voltage control bandwidth | rad/s |

| Symbol | Value |

|---|---|

| 1 p.u./V | |

| 0.1 Hz/V | |

| 100 V/V | |

| 100 V/V | |

| 3 A/V | |

| 2 A/V | |

| 3.2141 A/V |

| Parameters | Proposed Converter | Non-Isolated DC-AC [2] | Isolated DC-AC [7] | Isolated DC-AC [20] | Isolated DC-AC [22] |

|---|---|---|---|---|---|

| Structure | DC-DC DABSR + VSI | Bidirectional Boost + VSI | DC-DC DAB + VSI | DC-DC DABSR + VSI | DC-DC Three-phase DAB + VSI |

| DC-Link Capacitor | Film | Electrolytic | Electrolytic | Film | Film |

| DC-Link Ripple | High (10%) | Low (3%) | Low (3%) | High (10%) | High (10%) |

| Galvanic Isolation | Yes | Non | Yes | Yes | Yes |

| Durability | High | Low | Low | High | High |

| Control Strategy | V2G and Stand-Alone V2H in Unified GFM strategy | V2G (GFO), Stand-Alone AC Voltage Control (V2H) | Only active power V2G Reported (GFO) | Only active power V2G Reported (GFO) | Only stand-alone AC voltage control reported |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Sal y Rosas, D.; Zarate, A. Single-Phase Grid-Forming Strategy with Power Decoupling Implementation for Electrolytic-Capacitor-Free EV Smart Battery Charger. Energies 2023, 16, 894. https://doi.org/10.3390/en16020894

Sal y Rosas D, Zarate A. Single-Phase Grid-Forming Strategy with Power Decoupling Implementation for Electrolytic-Capacitor-Free EV Smart Battery Charger. Energies. 2023; 16(2):894. https://doi.org/10.3390/en16020894

Chicago/Turabian StyleSal y Rosas, Damián, and Alvaro Zarate. 2023. "Single-Phase Grid-Forming Strategy with Power Decoupling Implementation for Electrolytic-Capacitor-Free EV Smart Battery Charger" Energies 16, no. 2: 894. https://doi.org/10.3390/en16020894

APA StyleSal y Rosas, D., & Zarate, A. (2023). Single-Phase Grid-Forming Strategy with Power Decoupling Implementation for Electrolytic-Capacitor-Free EV Smart Battery Charger. Energies, 16(2), 894. https://doi.org/10.3390/en16020894