Operation of the System of Coupled Low-Voltage Feeders during Short-Circuit Faults †

Abstract

:1. Introduction

- two MV lines fed from the same transformer make a loop arrangement;

- two MV lines fed from different transformers of a substation make a loop arrangement; and

- two MV lines fed from different transformers of two substations make a loop arrangement.

- possibility of coupling more than two LVFs (which is not possible using the previous two approaches unless by adding more switches or converters),

- automatic power exchange capability among the coupled LVFs (which is not possible in the non-automatic normally-open switch approach)

- less imposed costs and losses to the system (compared to the back-to-back connection approach), and

- possibility of circulating the surplus generated power by the PV systems in one phase to the other phases(s) of any of the LVFs through the DSTATCOM.

- to investigate the desired operation of the system of coupled LVFs under fault conditions,

- to develop the proper protection approach for the system of coupled LVFs, and

- to evaluate the dynamic effectiveness of the proposed protection scheme.

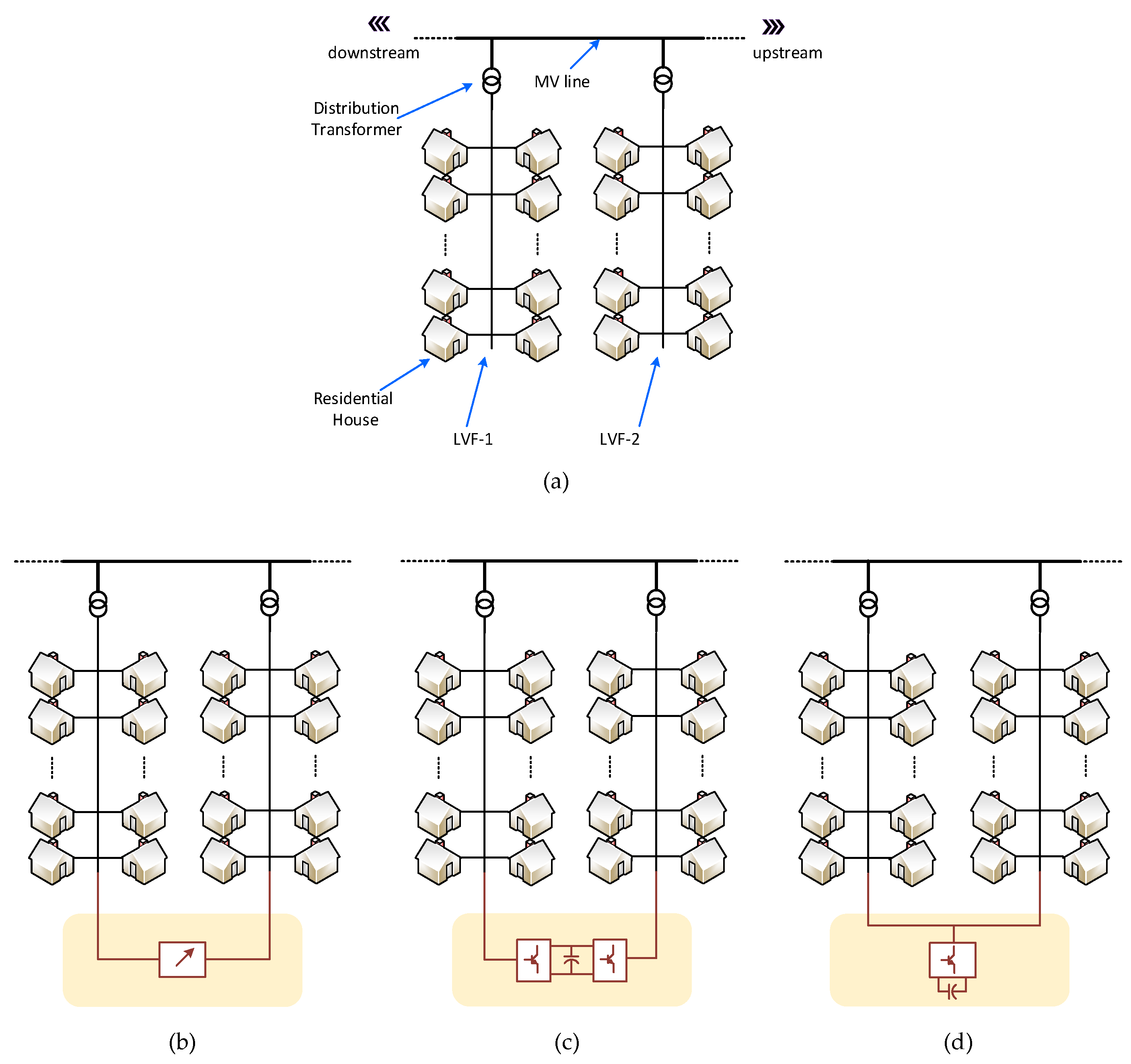

2. System under Consideration

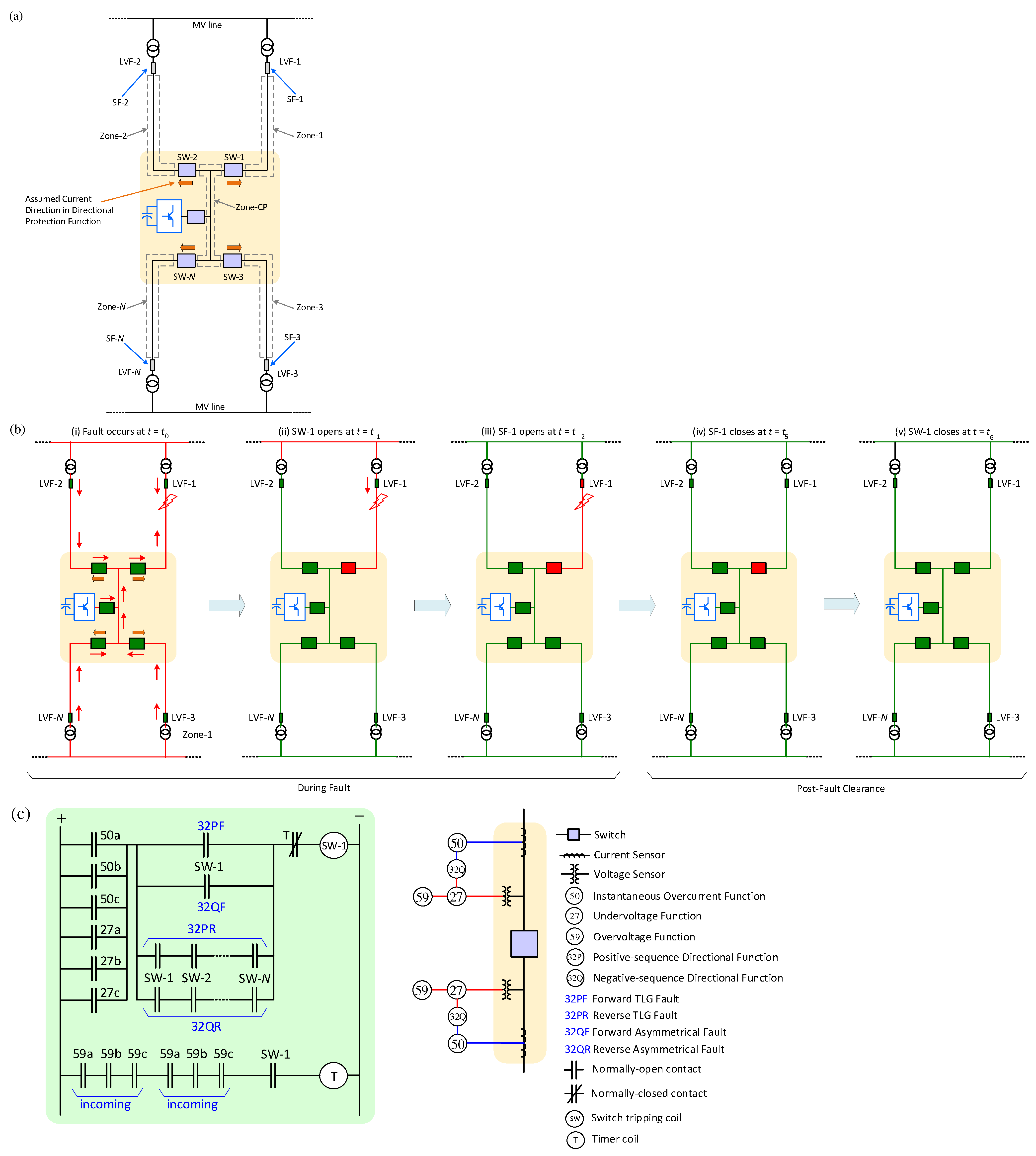

3. Desired Operation of the System of Coupled LVFs under Fault Conditions

- Fault occurs at t = t0;

- Action-1: The switch at the coupling point of the LVFs trips at t = t1 (based on the command of the overcurrent and/or undervoltage functions);

- Action-2: The SF at the secondary side of the distribution transformer of the faulted LVF (i.e., SF-1) trips at t = t2;

- Action-3: The SF at the secondary side of the distribution transformer of the non-faulted LVF (i.e., SF-2) trips at t = t2′ as backup protection when action-1 fails;

- Action-4: The cut-out fuse at the primary side of the distribution transformer of the faulted LVF trips at t = t3 as a backup protection when action-2 fails;

- Action-5: The cut-out fuse at the primary side of the distribution transformer of the non-faulted LVF trips at t = t3′ as a backup protection when action-3 fails;

- Action-6: The first protective device in the MV line trips at t = t4 when either action 4 or 5 fails;

4. Operation of the System of Coupled LVFs in the Presence of a DSTATCOM

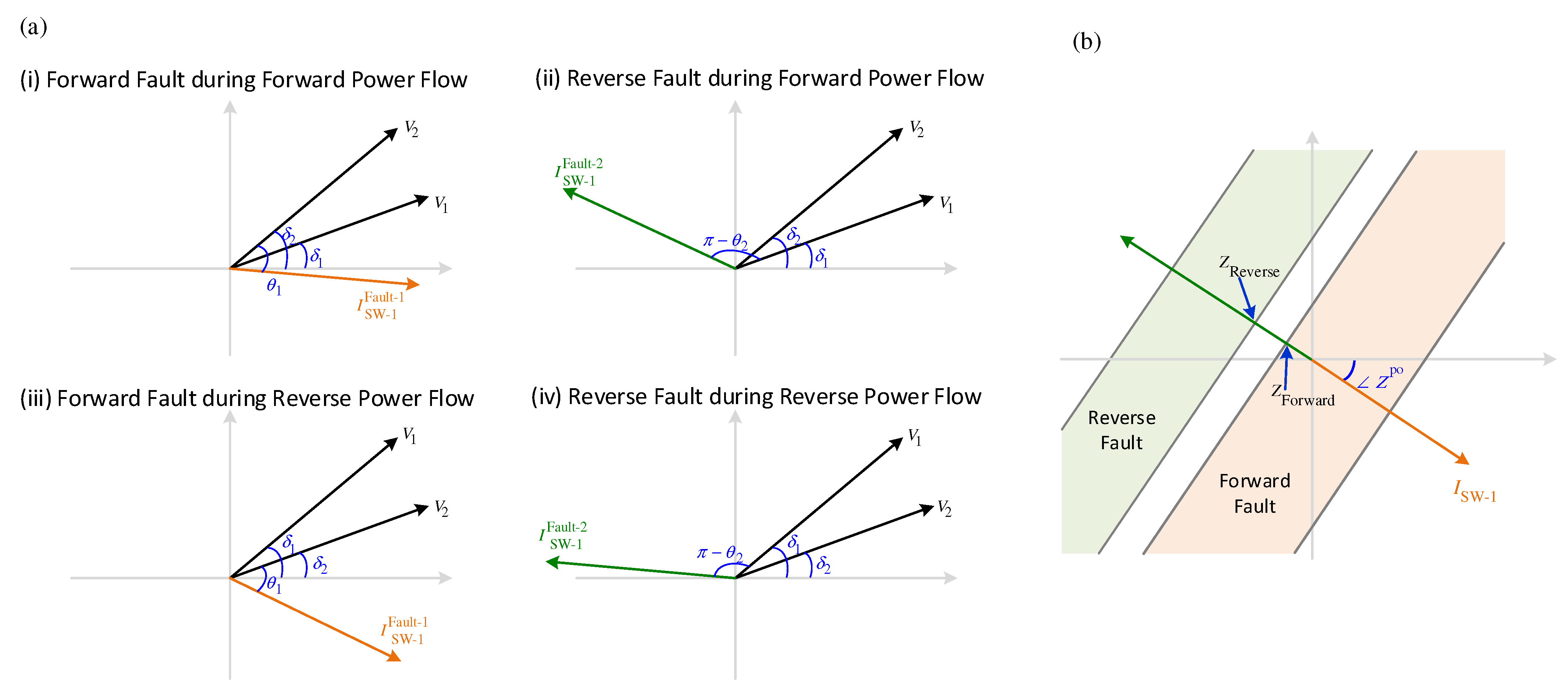

- For both forward and reverse asymmetrical faults, is always negative;

- For a forward asymmetrical fault for switch-m, lags the driving voltage by the characteristic angle of the line and is considered positive;

- For a reverse asymmetrical fault for switch-m, is in the reverse direction (180° phase shift) of the forward fault; and

- For a forward asymmetrical fault, is always negative and for a reverse asymmetrical fault, is always positive.

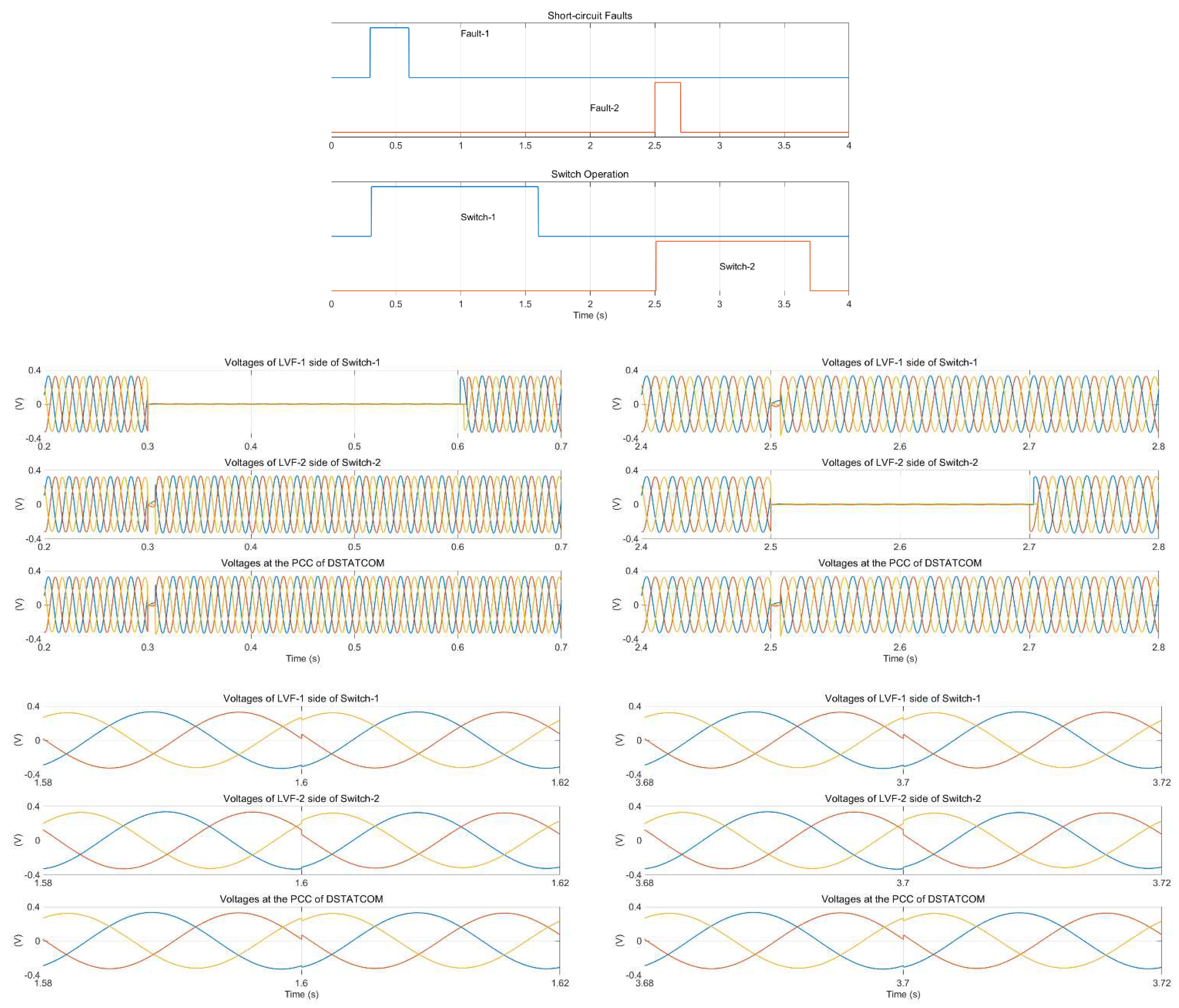

5. Case Studies and Simulation Results

6. Conclusions

Funding

Data Availability Statement

Conflicts of Interest

Appendix A. Structure and Control of the DSTATCOM

Appendix B. Structure of the Coupling Point Switch

Appendix C. Short-Circuit Studies for the System of Coupled LVFs without a DSTATCOM

Appendix C.1. Triple Line to Ground (TLG) Short-Circuit Faults

Appendix C.2. Single Line to Ground (SLG) Short-Circuit Faults

Appendix C.3. Line to Line (LL) Short-Circuit Faults

Appendix C.4. Double Line to Ground (DLG) Short-Circuit Faults

Appendix D. Short-Circuit Studies for the System of Coupled LVFs in the Presence of a DSTATCOM

Appendix E. Directional Protection Function and Its Settings

Appendix F. Technical Data of Network under Studies

| Distribution Transformer | Voltage and frequency: 11 kV/415 V, 50 Hz Rating: 200 kVA Connection: Δ/Y-grounded Impedance: = 5% |

| LVF | Conductor number and size: 3 × 70 + 35 mm2 Conductor Type: AAC bare overhead conductor Length: 400 m Impedance: [Ω/km] Number of poles: 10 poles (nodes) with a distance of 40 m from each other. |

| MV line | Conductor number and size: 3 × 50 mm2 Conductor Type: ACSR bare overhead conductor Length: 2 km Impedance: [Ω/km] |

| Load | Number and type in each LVF: 30 single-phase houses Demand: 1–5 kW Power Factor: 0.95 lagging Impedance: [Ω for 1 kW]. |

| PVs | Number and type in each LVF: 15 single-phase Power Factor: 1 Inverter coupling impedance: 5 mH |

References

- Short, T.A. Electric Power Distribution Handbook; CRC Press: Boca Raton, FL, USA, 2004. [Google Scholar]

- Kazemi, S.; Sanaye-Pasand, M.; Lehtonen, M.; Fotuhi-Firuzabad, M. Impacts of automatic control systems of loop restoration scheme on the distribution system reliability. IET Gener. Transm. Distrib. 2009, 3, 891–902. [Google Scholar] [CrossRef]

- Venkatesh, B.; Rakesh, R.; Gooi, H. Optimal reconfiguration of radial distribution systems to maximize loadability. IEEE Trans. Power Syst. 2004, 19, 260–266. [Google Scholar] [CrossRef]

- Chen, T.H.; Huang, W.T.; Gu, J.C.; Pu, G.C.; Hsu, Y.F.; Guo, T.Y. Feasibility study of upgrading primary feeders from radial and open-loop to normally closed-loop arrangement. IEEE Trans. Power Syst. 2004, 19, 1308–1316. [Google Scholar] [CrossRef]

- Chen, C.-S.; Tsai, C.-T.; Lin, C.-H.; Hsieh, W.-L.; Ku, T.-T. Loading Balance of Distribution Feeders with Loop Power Controllers Considering Photovoltaic Generation. IEEE Trans. Power Syst. 2011, 26, 1762–1768. [Google Scholar] [CrossRef]

- Okada, N. Verification of Control Method for a Loop Distribution System using Loop Power Flow Controller. In Proceedings of the 2006 IEEE PES Power Systems Conference and Exposition, Atlanta, GA, USA, 29 October–1 November 2006; pp. 2116–2123. [Google Scholar] [CrossRef]

- Okada, N.; Takasaki, M.; Sakai, H.; Katoh, S. Development of a 6.6 kV 1MVA transformerless loop balance controller. In Proceedings of the IEEE Power Electronics Specialists Conference, Orlando, FL, USA, 17–21 June 2007; pp. 1087–1091. [Google Scholar]

- Jindal, A.K.; Ghosh, A.; Joshi, A. Interline Unified Power Quality Conditioner. IEEE Trans. Power Deliv. 2007, 22, 364–372. [Google Scholar] [CrossRef]

- Jindal, A.; Ghosh, A.; Joshi, A. Power quality improvement using interline voltage controller. IET Gener. Transm. Distrib. 2007, 1, 287–293. [Google Scholar] [CrossRef]

- Wijekoon, H.; Vilathgamuwa, D.; Choi, S. Interline dynamic voltage restorer: An economical way to improve interline power quality. IEE Proc. Gener. Transm. Distrib. 2003, 150, 513. [Google Scholar] [CrossRef]

- Sayed, M.A.; Takeshita, T. All nodes voltage regulation and line loss minimization in loop distribution systems using UPFC. IEEE Trans. Power Electron. 2011, 26, 1694–1703. [Google Scholar] [CrossRef]

- IEEE Recommended Practice for Monitoring. Electric Power Quality; IEEE Standard: Piscataway, NJ, USA, 1995; Volume 1159. [Google Scholar]

- IEC 61000-2-2; IEC Standard Voltages, Electromagnetic Compatibility, Part 2: Environment-Compatibility Levels for Low-Frequency Conducted Disturbances and Signaling In Public Low-Voltage Power Supply Systems. IEC: Geneva, Switzerland, 2002.

- EN 50160; Voltage Characteristics of Electricity Supplied by Public Distribution Systems. Copper Development Association: Hemel Hempstead, UK, 1999.

- AS60038; Australian Standard Voltage. Standards Australia International Ltd.: Strathfield, NSW, Australia, 2000.

- Eltawil, M.A.; Zhao, Z. Grid-connected photovoltaic power systems: Technical and potential problems—A review. Renew. Sustain. Energy Rev. 2010, 14, 112–129. [Google Scholar] [CrossRef]

- Noone, B. PV Integration on Australian Distribution Networks: Literature Review; Australian PV Association: Redfern, NSW, Australia, 2013. [Google Scholar]

- Energex/Ergon Energy Connection Standard on Small Scale Parallel Inverter Energy Systems up to 30 kVA; Ergon Energy Corporation Ltd.: Townsville, QLD, Australia, 2014.

- Demirok, E.; González, P.C.; Frederiksen, K.H.B.; Sera, D.; Rodriguez, P.; Teodorescu, R. Local Reactive Power Control Methods for Overvoltage Prevention of Distributed Solar Inverters in Low-Voltage Grids. IEEE J. Photovolt. 2011, 1, 174–182. [Google Scholar] [CrossRef]

- Ku, T.-T.; Lin, C.-H.; Chen, C.-S.; Hsu, C.-T.; Hsieh, W.-L.; Hsieh, S.-C. Coordination of PV Inverters to Mitigate Voltage Violation for Load Transfer Between Distribution Feeders with High Penetration of PV Installation. IEEE Trans. Ind. Appl. 2015, 52, 1. [Google Scholar] [CrossRef]

- Shahnia, F.; Majumder, R.; Ghosh, A.; Ledwich, G.; Zare, F. Voltage imbalance analysis in residential low voltage distribution networks with rooftop PVs. Electr. Power Syst. Res. 2011, 81, 1805–1814. [Google Scholar] [CrossRef]

- Samadi, A.; Eriksson, R.; Soder, L.; Rawn, B.G.; Boemer, J.C. Coordinated Active Power-Dependent Voltage Regulation in Distribution Grids with PV Systems. IEEE Trans. Power Deliv. 2014, 29, 1454–1464. [Google Scholar] [CrossRef]

- Tonkoski, R.; Lopes, L.A.C.; El-Fouly, T.H.M. Coordinated Active Power Curtailment of Grid Connected PV Inverters for Overvoltage Prevention. IEEE Trans. Sustain. Energy 2011, 2, 139–147. [Google Scholar] [CrossRef]

- Von Appen, J.; Stetz, T.; Braun, M.; Schmiegel, A. Local voltage control strategies for PV storage systems in distribution grids. IEEE Trans. Smart Grid 2014, 5, 1002–1009. [Google Scholar] [CrossRef]

- Marra, F.; Yang, G.; Traeholt, C.; Ostergaard, J.; Larsen, E. A Decentralized Storage Strategy for Residential Feeders with Photovoltaics. IEEE Trans. Smart Grid 2014, 5, 974–981. [Google Scholar] [CrossRef]

- Shahnia, F.; Ghosh, A. Decentralized voltage support in a Low Voltage feeder by droop based voltage controlled PVs. In Proceedings of the 23rd Australasian Universities Power Engineering Conference, Hobart, TAS, Australia, 29 September–3 October 2013; pp. 1–6. [Google Scholar] [CrossRef]

- Mouli, G.R.C.; Bauer, P.; Wijekoon, T.; Panosyan, A.; Barthlein, E.-M. Design of a Power-Electronic-Assisted OLTC for Grid Voltage Regulation. IEEE Trans. Power Deliv. 2015, 30, 1086–1095. [Google Scholar] [CrossRef]

- Kabiri, R.; Holmes, D.G.; McGrath, B.P. Voltage regulation of LV feeders with high penetration of PV distributed generation using electronic tap changing transformers. In Proceedings of the 24th Australasian Universities Power Engineering Conference, Perth, WA, Australia, 28 September–1 October 2014; pp. 1–6. [Google Scholar] [CrossRef]

- Shahnia, F.; Ami, S.M.; Ghosh, A. Circulating the reverse flowing surplus power generated by single-phase DERs among the three phases of the distribution lines. Int. J. Electr. Power Energy Syst. 2016, 76, 90–106. [Google Scholar] [CrossRef]

- Shahnia, F.; Ghosh, A.; Ledwich, G.; Zare, F. Voltage unbalance improvement in low voltage residential feeders with rooftop PVs using custom power devices. Int. J. Electr. Power Energy Syst. 2014, 55, 362–377. [Google Scholar] [CrossRef]

- Shahnia, F.; Rajakaruna, S.; Ghosh, A. Static Compensators in Power Systems; Springer: Berlin/Heidelberg, Germany, 2014. [Google Scholar]

- Efkarpidis, N.; Wijnhoven, T.; Gonzalez, C.; De Rybel, T.; Driesen, J. Coordinated voltage control scheme for Flemish LV distribution grids utilizing OLTC transformers and D-STATCOM’s. In Proceedings of the 12th IET International Conference on Developments in Power System Protection (DPSP 2014), Copenhagen, Denmark, 31 March–3 April 2014; pp. 1–6. [Google Scholar]

- Shahnia, F.; Ghosh, A. Coupling of neighbouring low voltage residential distribution feeders for voltage profile improvement using power electronics converters. IET Gener. Transm. Distrib. 2015, 10, 535–547. [Google Scholar] [CrossRef]

- Coffele, F.; Booth, C.; Dysko, A. An Adaptive Overcurrent Protection Scheme for Distribution Networks. IEEE Trans. Power Deliv. 2015, 30, 561–568. [Google Scholar] [CrossRef]

- Mahat, P.; Chen, Z.; Bak-Jensen, B.; Bak, C.L. A Simple Adaptive Overcurrent Protection of Distribution Systems with Distributed Generation. IEEE Trans. Smart Grid 2011, 2, 428–437. [Google Scholar] [CrossRef]

- Lin, W.-M.; Lin, C.-H.; Sun, Z.-C. Adaptive Multiple Fault Detection and Alarm Processing for Loop System with Probabilistic Network. IEEE Trans. Power Deliv. 2004, 19, 64–69. [Google Scholar] [CrossRef]

- Sharon, Y.; Montenegro, A.; Gardner, A.; Ennis, M.G. New directional protection for distribution networks. In Proceedings of the 2015 IEEE Power & Energy Society General Meeting, Denver, CO, USA, 26–30 July 2015; pp. 1–5. [Google Scholar] [CrossRef]

- Capasso, A.; Catone, R.; Lama, R.; Lauria, S.; Santopaolo, A. Ground fault protection in ENEL Distribuzione’s experimental MV loop line. In Proceedings of the 12th IET International Conference on Developments in Power System Protection (DPSP 2014), Copenhagen, Denmark, 31 March–3 April 2014; pp. 1–6. [Google Scholar]

- Shen, K.-Y.; Gu, J.-C. Protection coordination analysis of closed-loop distribution system. In Proceedings of the International Conference on Power System Technology, Kunming, China, 13–17 October 2002; pp. 702–706. [Google Scholar] [CrossRef]

- Monadi, M.; Gavriluta, C.; Candela, J.I.; Rodriguez, P. A communication-assisted protection for MVDC distribution systems with distributed generation. In Proceedings of the 2015 IEEE Power & Energy Society General Meeting, Denver, CO, USA, 26–30 July 2015. [Google Scholar] [CrossRef]

- Shih, M.Y.; Salazar, C.A.C.; Enríquez, A.C. Adaptive directional overcurrent relay coordination using ant colony optimisation. IET Gener. Transm. Distrib. 2015, 9, 2040–2049. [Google Scholar] [CrossRef]

- El-Khattam, W.; Sidhu, T. Resolving the impact of distributed renewable generation on directional overcurrent relay coordination: A case study. IET Renew. Power Gener. 2009, 3, 415–425. [Google Scholar] [CrossRef]

- Albasri, F.A.; Alroomi, A.R.; Talaq, J.H. Optimal coordination of directional overcurrent relays using biogeography-based optimization algo-rithms. IEEE Trans. Power Deliv. 2015, 30, 1810–1820. [Google Scholar] [CrossRef]

- Saleh, K.; Zeineldin, H.; Al-Hinai, A.; El-Saadany, E. Optimal coordination of directional overcurrent relays using a new time-current-voltage characteristic. IEEE Trans. Power Deliv. 2015, 30, 537–544. [Google Scholar] [CrossRef]

- Amraee, T. Coordination of Directional Overcurrent Relays Using Seeker Algorithm. IEEE Trans. Power Deliv. 2012, 27, 1415–1422. [Google Scholar] [CrossRef]

- Loos, M.; Werben, S.; Maun, J.C. Circulating currents in closed loop structure, a new problematic in distribution networks. In Proceedings of the 2012 IEEE Power and Energy Society General Meeting, San Diego, CA, USA, 22–26 July 2012. [Google Scholar]

- Premalata, J.; Pradhan, A.K. Network Protection Systems Considering the Presence of STATCOMs. In Static Compensators in Power Systems; Shahnia, F., Rajakaruna, S., Ghosh, A., Eds.; Springer: Singapore, 2014. [Google Scholar]

- Kazemi, A.; Jamali, S.; Shateri, H. Effects of DSTATCOM on measured impedance at source node of distribution feeder. In Proceedings of the CIRED Seminar 2008: SmartGrids for Distribution, Frankfurt, Germany, 23–24 June 2008. [Google Scholar] [CrossRef]

- Raman, S.; Gokaraju, R.; Jain, A. An adaptive fuzzy mho relay for phase backup protection with infeed from STATCOM. IEEE Trans. Power Deliv. 2013, 28, 120–128. [Google Scholar] [CrossRef]

- Part 6: Low voltage overhead. In Distribution Construction Standards Handbook; WesternPower: Perth, WA, Australia, 2007.

- Technical Specification for 24kV Padmounted Substations; Specification ETS02-02-02, Version-10; Ergon Energy Corporation Ltd.: Townsville, QLD, Australia, 2012.

- Oza, B.; Chander, M. Power System Protection and Switchgear; McGraw-Hill: New York, NY, USA, 2010. [Google Scholar]

- Fleming, B. Negative-sequence impedance directional element. In Proceedings of the 10th Annual ProTest User Group Meeting, Pasadena, CA, USA, 24–26 February 1998; pp. 1–11. [Google Scholar]

- Roberts, J.; Guzman, A. Directional element design and evaluation. In Proceedings of the 21st Annual Western Protective Relay Conference, Spokane, WA, USA, 19–21 October 1994; pp. 1–27. [Google Scholar]

- Glover, J.D.; Sarma, M.S.; Overbye, T. Power System Analysis and Design, 5th ed.; Cengage Learning Inc.: Boston, MA, USA, 2011. [Google Scholar]

- Pradhan, A.K.; Routray, A.; Gudipalli, S.M. Fault Direction Estimation in Radial Distribution System Using Phase Change in Sequence Current. IEEE Trans. Power Deliv. 2007, 22, 2065–2071. [Google Scholar] [CrossRef]

- Hashemi, S.M.; Hagh, M.T.; Seyedi, H. Transmission-Line Protection: A Directional Comparison Scheme Using the Average of Superimposed Components. IEEE Trans. Power Deliv. 2013, 28, 955–964. [Google Scholar] [CrossRef]

- Jalilian, A.; Hagh, M.T.; Hashemi, S.M. An Innovative Directional Relaying Scheme Based on Postfault Current. IEEE Trans. Power Deliv. 2014, 29, 2640–2647. [Google Scholar] [CrossRef]

- Ukil, A.; Deck, B.; Shah, V.H. Current-only directional overcurrent relay. IEEE Sens. J. 2011, 11, 1403–1404. [Google Scholar] [CrossRef]

- Shahnia, F. Protection considerations of using a DSTATCOM when coupling neighboring low voltage feeders. In Proceedings of the IEEE International Conference on Industrial Technology (ICIT), Taipei, Taiwan, 14–17 March 2016; pp. 529–534. [Google Scholar] [CrossRef]

- Shahnia, F. Application and control of a DSTATCOM to couple neighboring low voltage feeders. In Proceedings of the IEEE International Conference on Industrial Technology (ICIT), Taipei, Taiwan, 14–17 March 2016; pp. 476–481. [Google Scholar] [CrossRef]

- Mishra, M.K.; Karthikeyan, K. A Fast-Acting DC-Link Voltage Controller for Three-Phase DSTATCOM to Compensate AC and DC Loads. IEEE Trans. Power Deliv. 2009, 24, 2291–2299. [Google Scholar] [CrossRef]

- Tewari, A. Modern Control Design with MATLAB and Simulink; Wiley: Hoboken, NJ, USA, 2002. [Google Scholar]

- Kumar, C.; Mishra, M.K. Dual-functional DSTATCOM with flexible mode transfer for power quality improvement. In Proceedings of the IEEE Power and Energy Society General Meeting, National Harbor, MD, USA, 27–31 July 2014; pp. 1–5. [Google Scholar] [CrossRef]

- ABB Switch Disconnectors Data. 2015. Available online: https://new.abb.com/low-voltage/products/switches/manual-operated-switch-disconnectors (accessed on 1 July 2023).

- Rashid, M.H. Power Electronics: Circuits, Devices and Applications, 4th ed.; Pearson: London, UK, 2013. [Google Scholar]

- Schweitzer, E.O.; Zocholl, S.E. Introduction to symmetrical components. In Proceedings of the 30th Annual Western Protective Relay Conference, Spokane, WA, USA, 21–23 October 2003; pp. 1–15. [Google Scholar]

- Kersting, W.H. Distribution System Modelling and Analysis; CRC Press: Boca Raton, FL, USA, 2012. [Google Scholar]

- Horak, J. Zero sequence impedance of overhead transmission lines. In Proceedings of the 59th Annual Conference for Protective Relay Engineers, College Station, TX, USA, 4–6 April 2006; pp. 1–11. [Google Scholar]

- Ziegler, G. Numerical Distance Protection: Principles and Applications, 4th ed.; Wiley: Hoboken, NJ, USA, 2011. [Google Scholar]

- REF550 Feeder Protection Relay, ABB. 2015. Available online: http://new.abb.com/medium-voltage/distribution-automation/numerical-relays/feeder-protection-and-control/other-series/ref550---advanced-feeder-protection (accessed on 1 July 2023).

- SEL-351 Protection System, Schweitzer Engineering Laboratories. 2015. Available online: https://selinc.com/products/351/ (accessed on 1 July 2023).

- MiCOM P14D Agile Directional Feeder Management IEDs, ALSTOM. 2015. Available online: https://www.gegridsolutions.com/multilin/catalog/p14n-p14d-p94v.htm (accessed on 1 July 2023).

- Zimmerman, K.; Costello, D. Fundamentals and improvements for directional relays. In Proceedings of the 2010 63rd Annual Conference for Protective Relay Engineers, College Station, TX, USA, 29 March–1 April 2010; pp. 1–12. [Google Scholar] [CrossRef]

- SEL 321 Instruction Manual. Schweitzer Engineering Laboratories. Available online: https://selinc.com/products/321/ (accessed on 1 July 2023).

- Ituzaro, F.A.; Douglin, R.H.; Butler-Purry, K.L. Zonal overcurrent protection for smart radial distribution systems with distributed generation. In Proceedings of the IEEE PES Innovative Smart Grid Technologies Conference (ISGT), Washington, DC, USA, 24–27 February 2013; pp. 1–6. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Shahnia, F. Operation of the System of Coupled Low-Voltage Feeders during Short-Circuit Faults. Energies 2023, 16, 6009. https://doi.org/10.3390/en16166009

Shahnia F. Operation of the System of Coupled Low-Voltage Feeders during Short-Circuit Faults. Energies. 2023; 16(16):6009. https://doi.org/10.3390/en16166009

Chicago/Turabian StyleShahnia, Farhad. 2023. "Operation of the System of Coupled Low-Voltage Feeders during Short-Circuit Faults" Energies 16, no. 16: 6009. https://doi.org/10.3390/en16166009

APA StyleShahnia, F. (2023). Operation of the System of Coupled Low-Voltage Feeders during Short-Circuit Faults. Energies, 16(16), 6009. https://doi.org/10.3390/en16166009