Compensation-Voltage-Injection-Based Neutral-Point Voltage Fluctuation Suppression Method for NPC Converters †

Abstract

1. Introduction

2. Analysis and Modeling of Neutral-Point Voltage Fluctuation

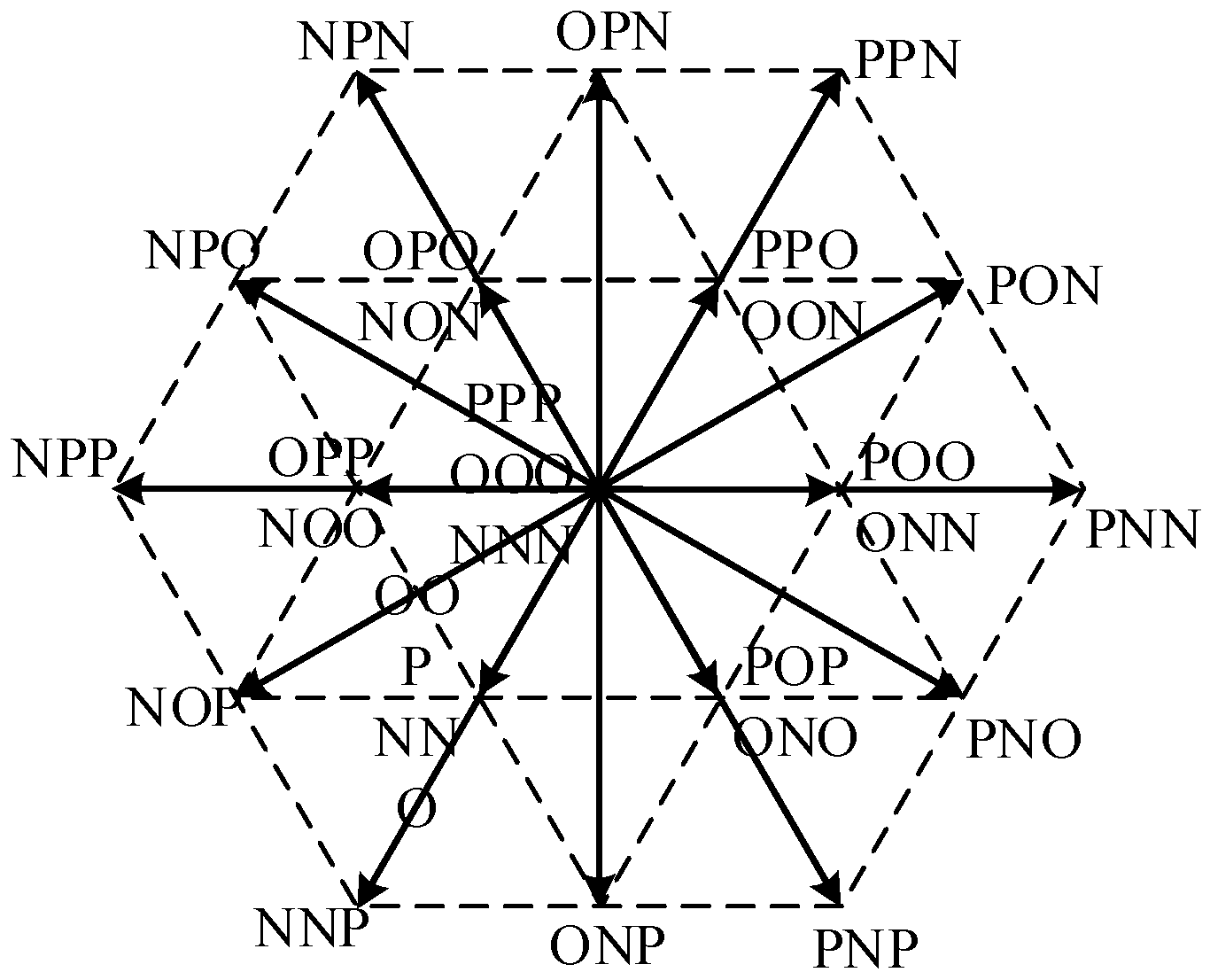

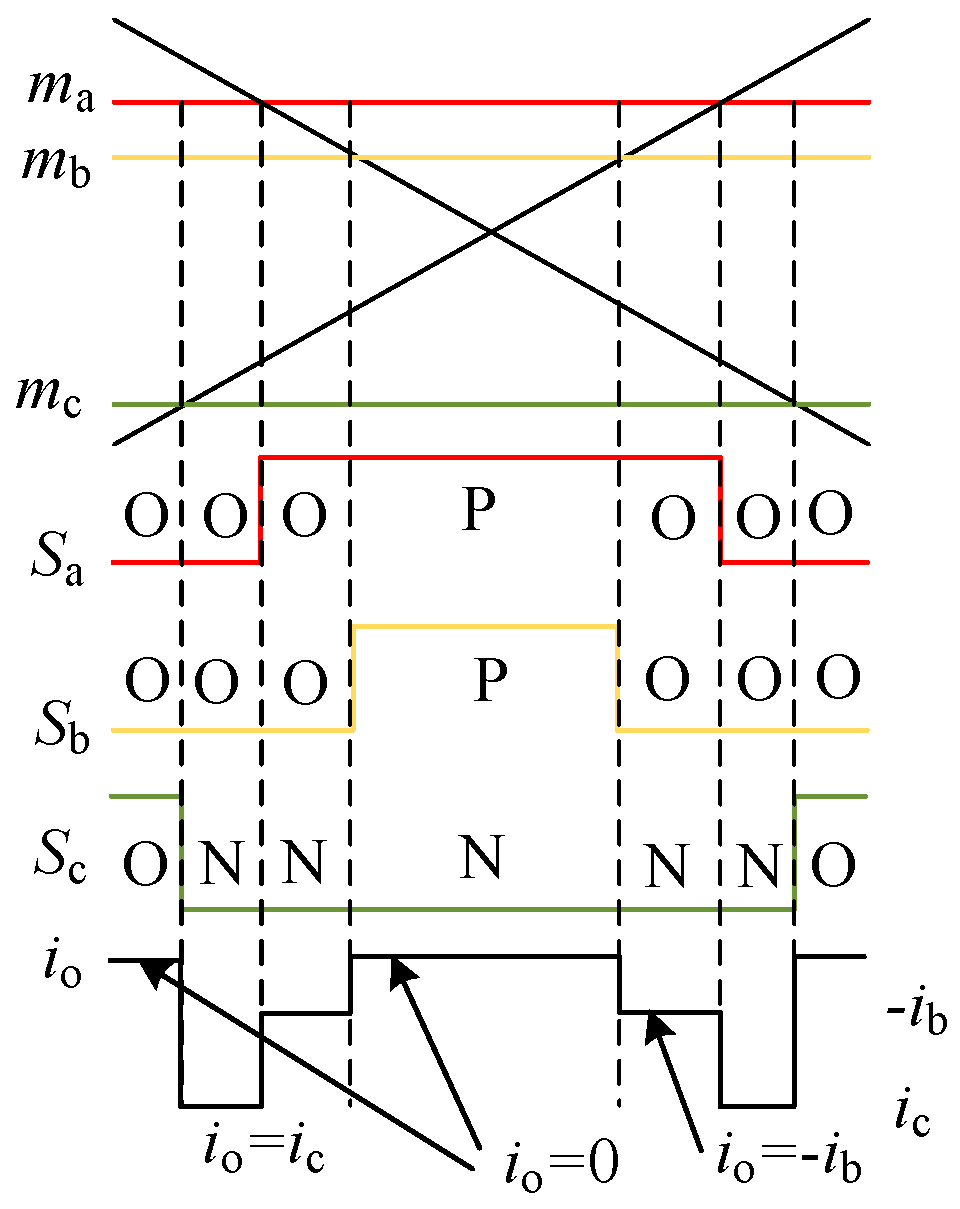

2.1. Principle of Modulation Strategy for NPC Inverter

2.2. Modeling of Neutral-Point Voltage Fluctuation

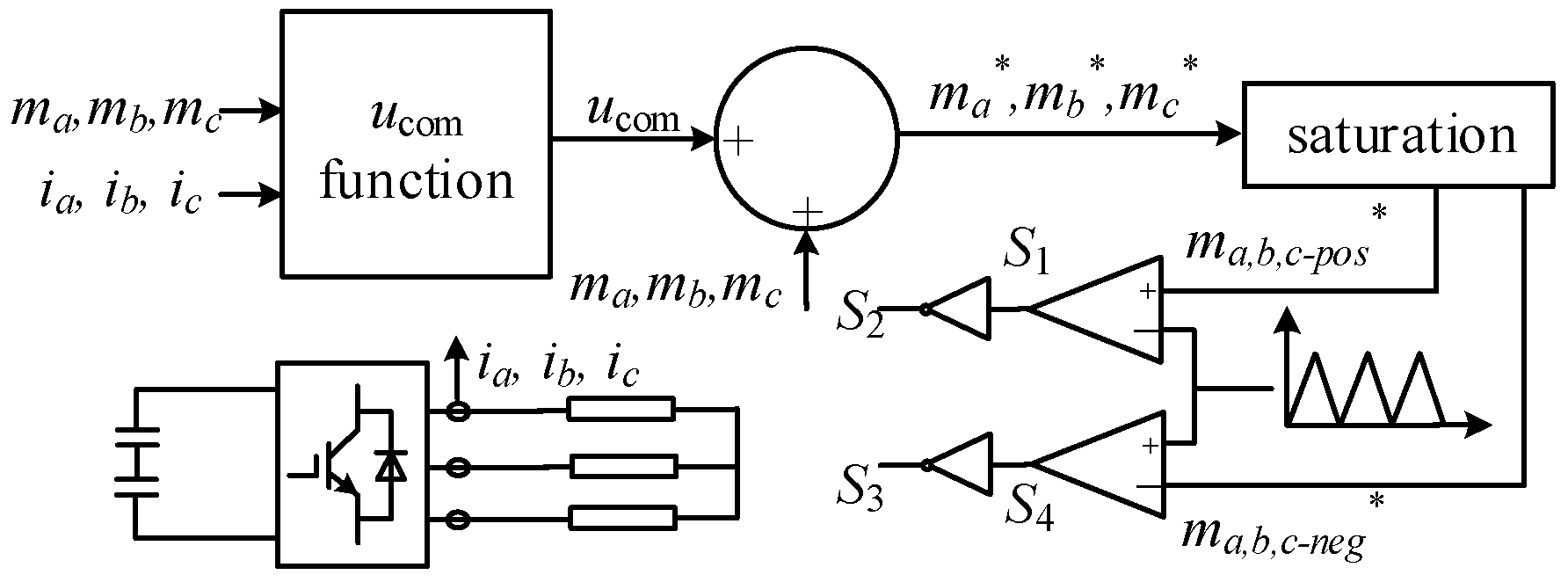

3. Proposed Voltage Fluctuation Suppression Method

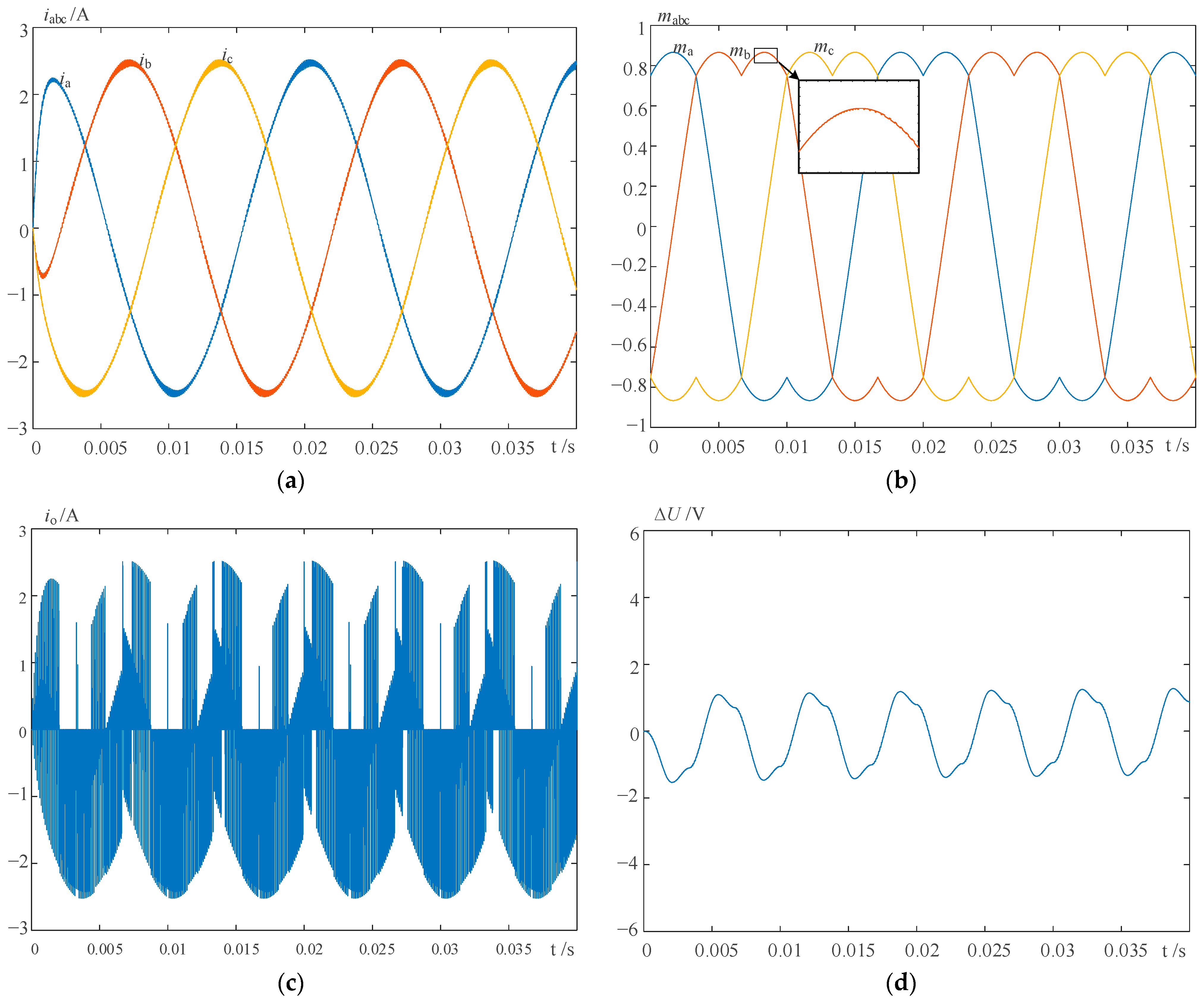

3.1. Switching-Cycle-Based Compensation Voltage Injection Method

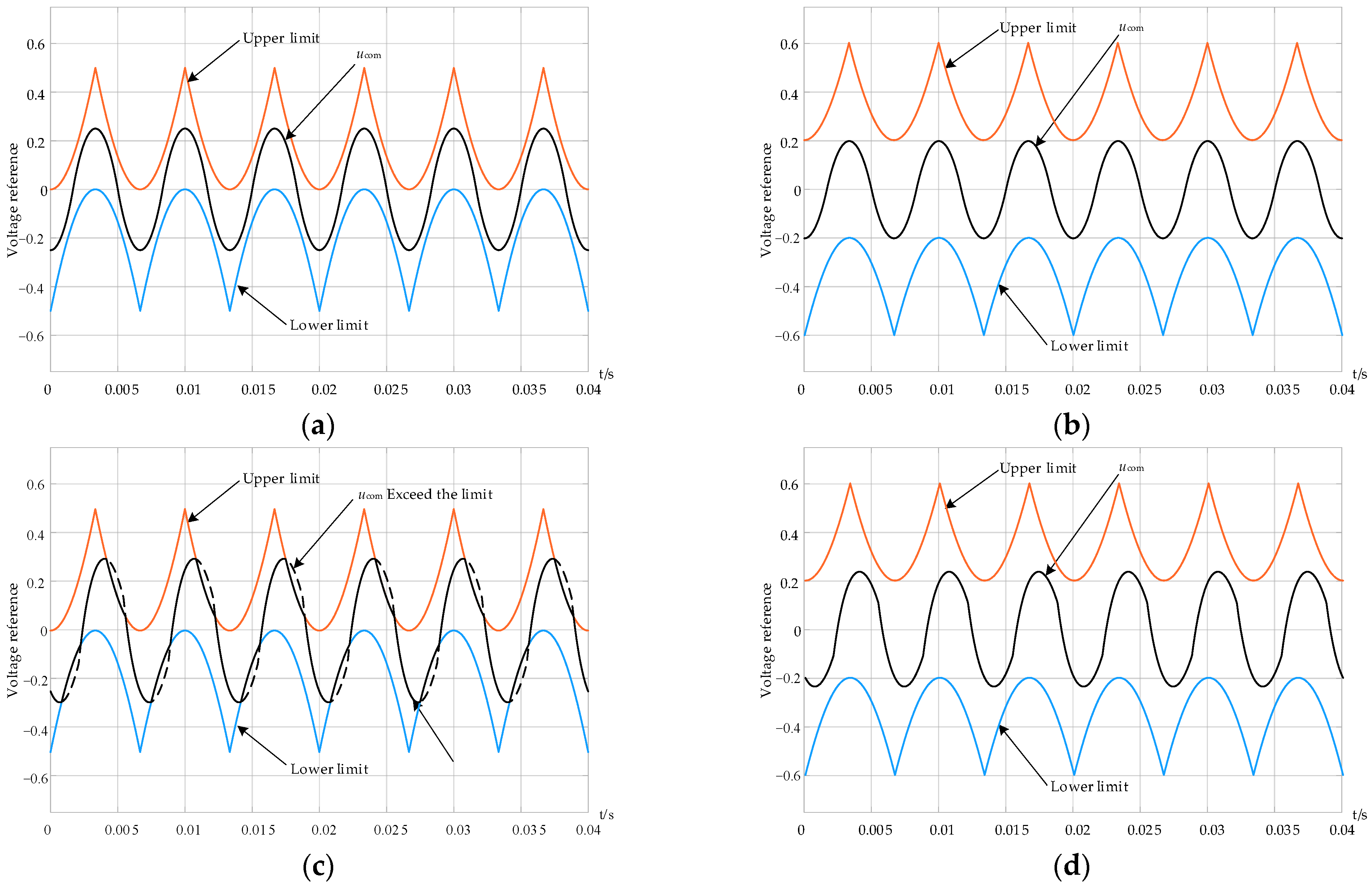

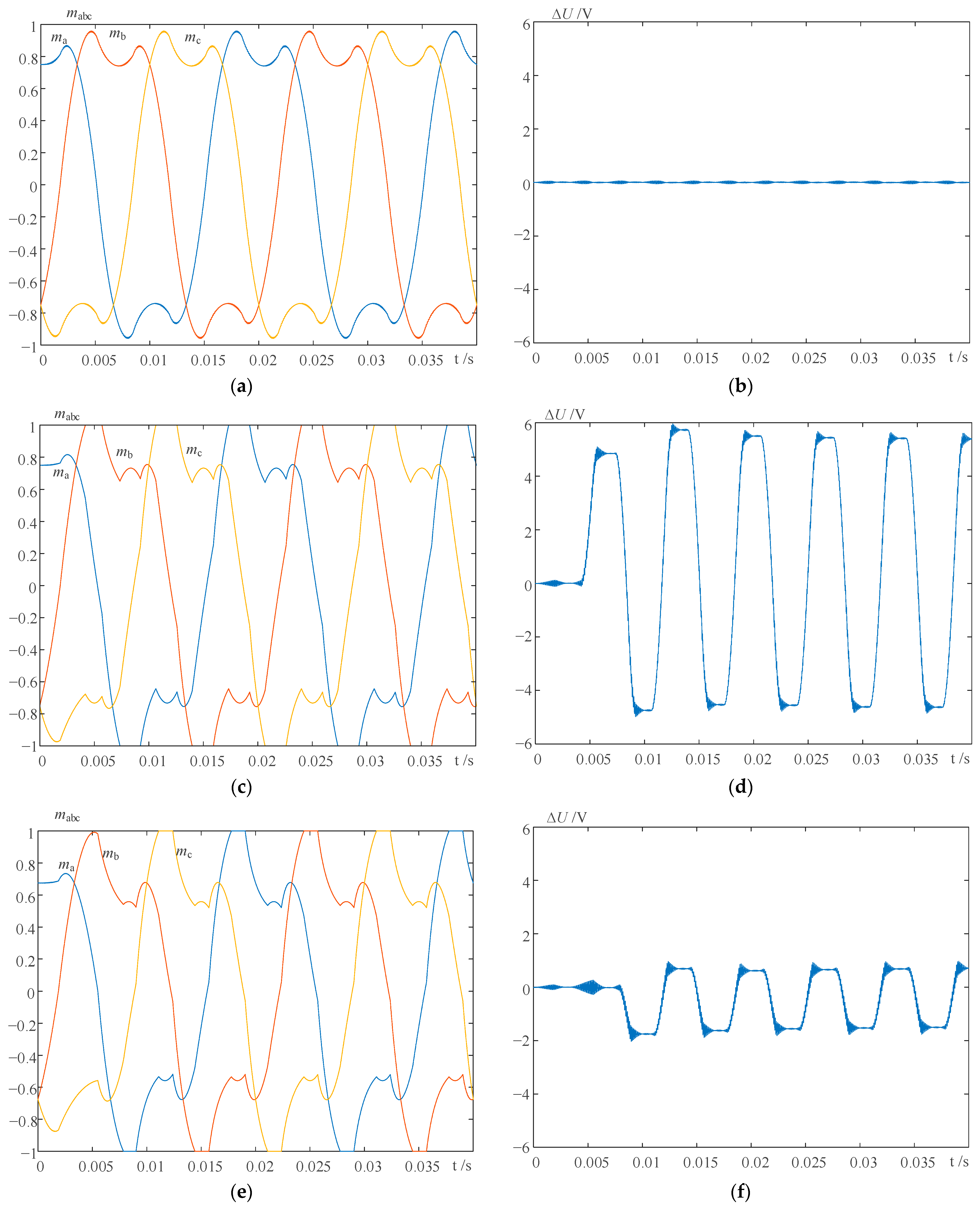

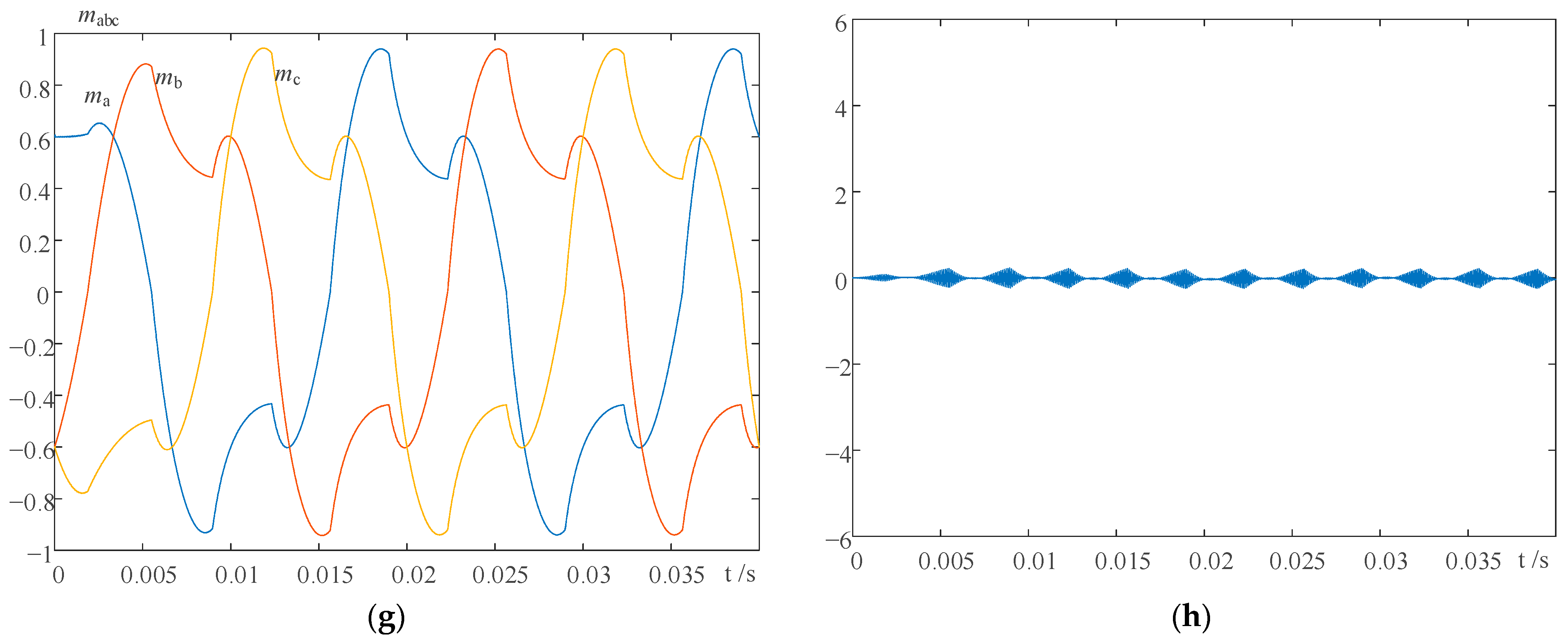

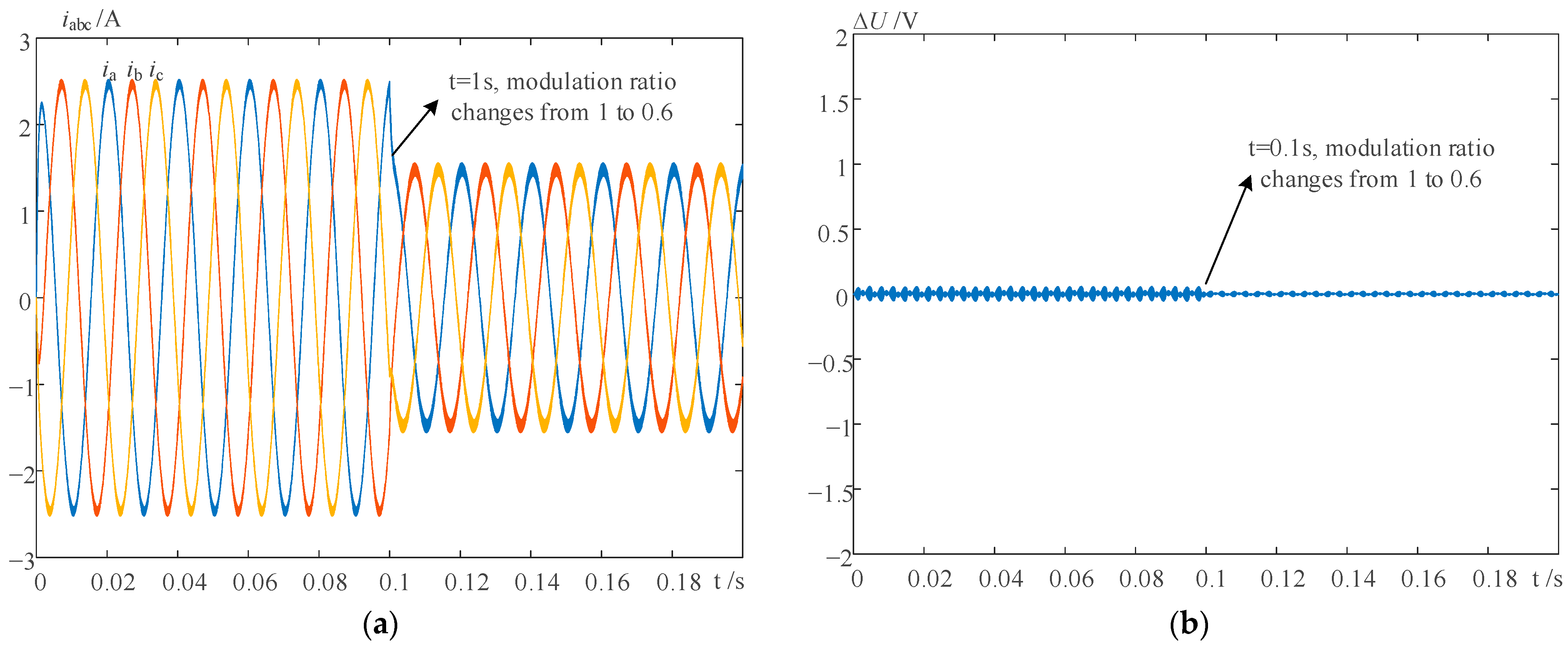

3.2. Influence of Modulation Rate and Power Factor

4. Simulation and Experimental Results

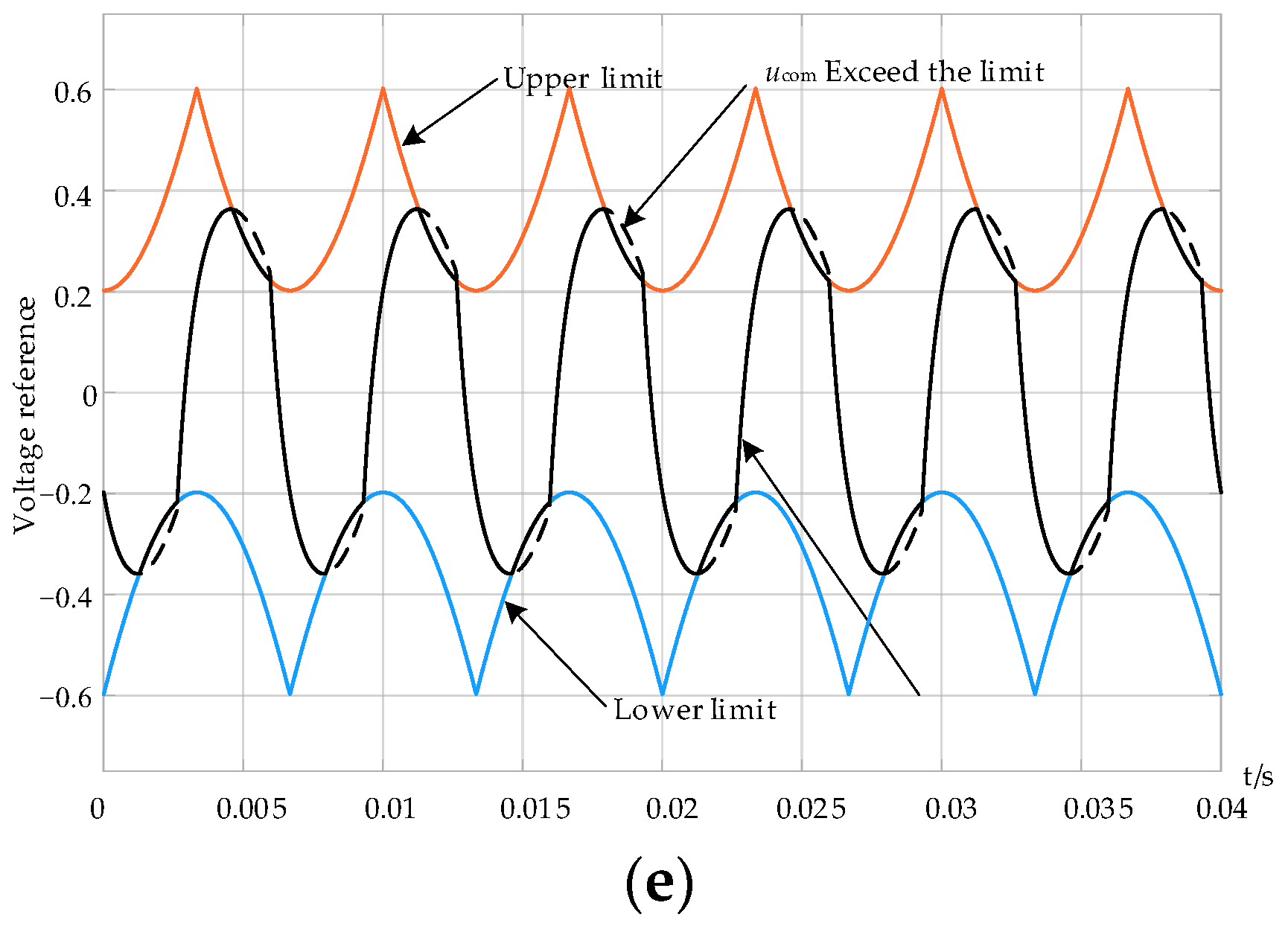

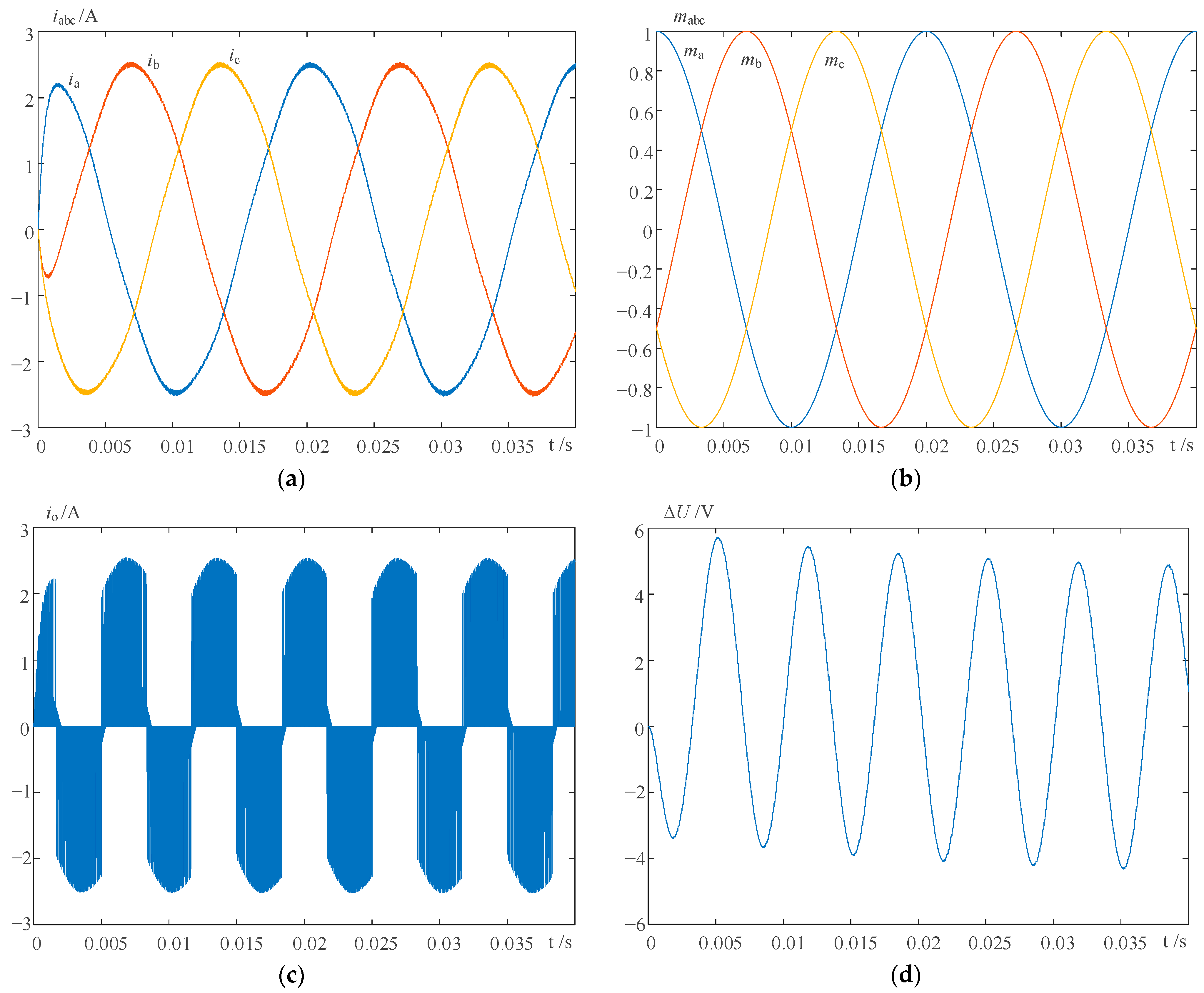

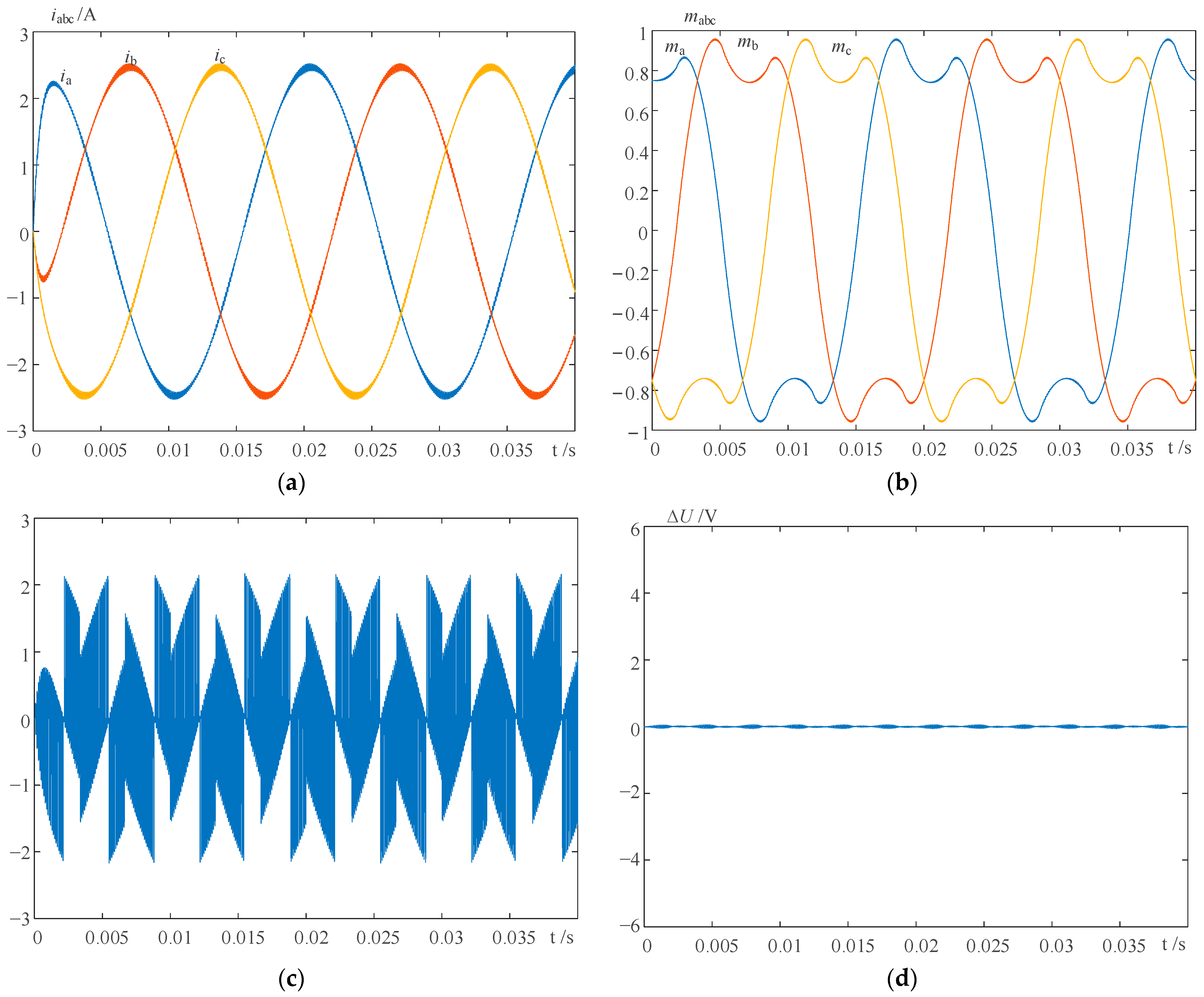

4.1. Simulation Results

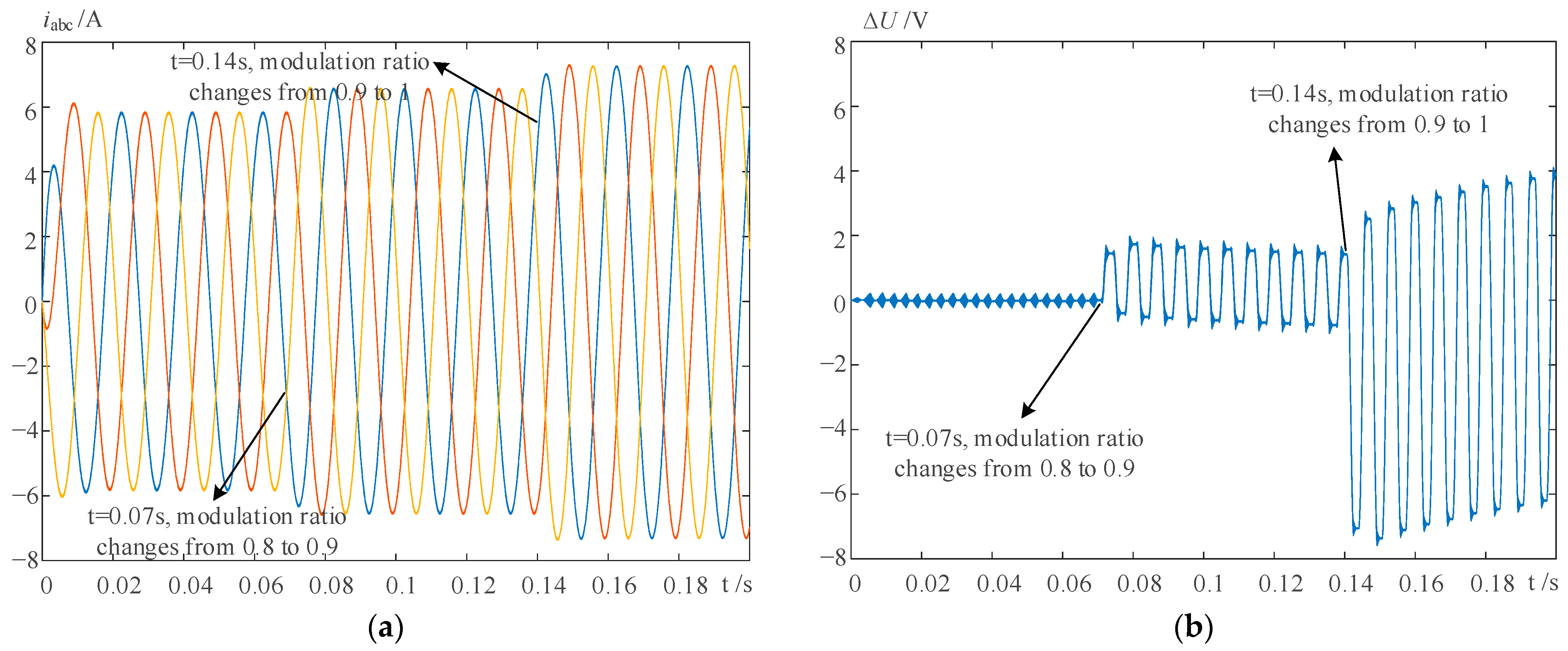

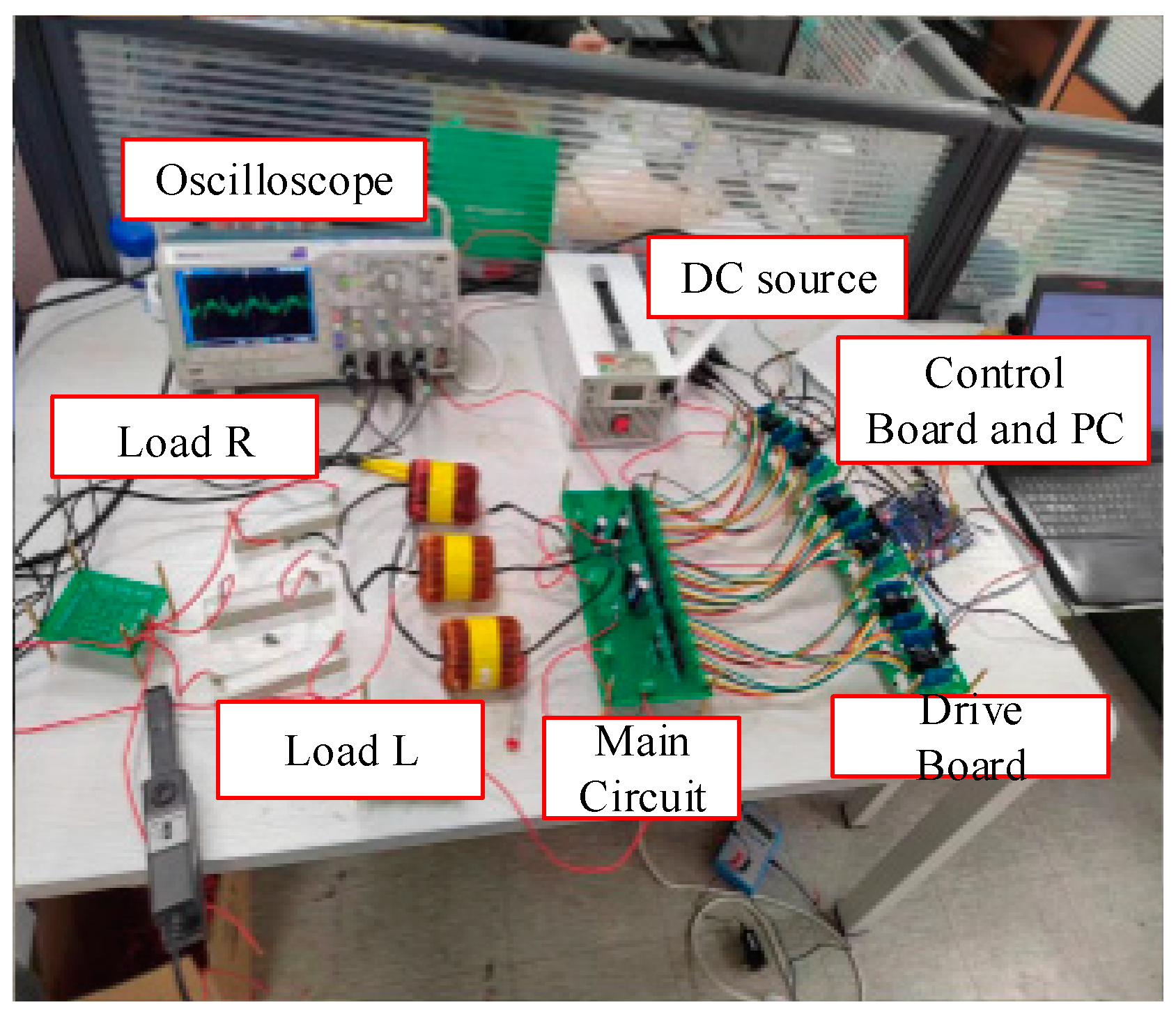

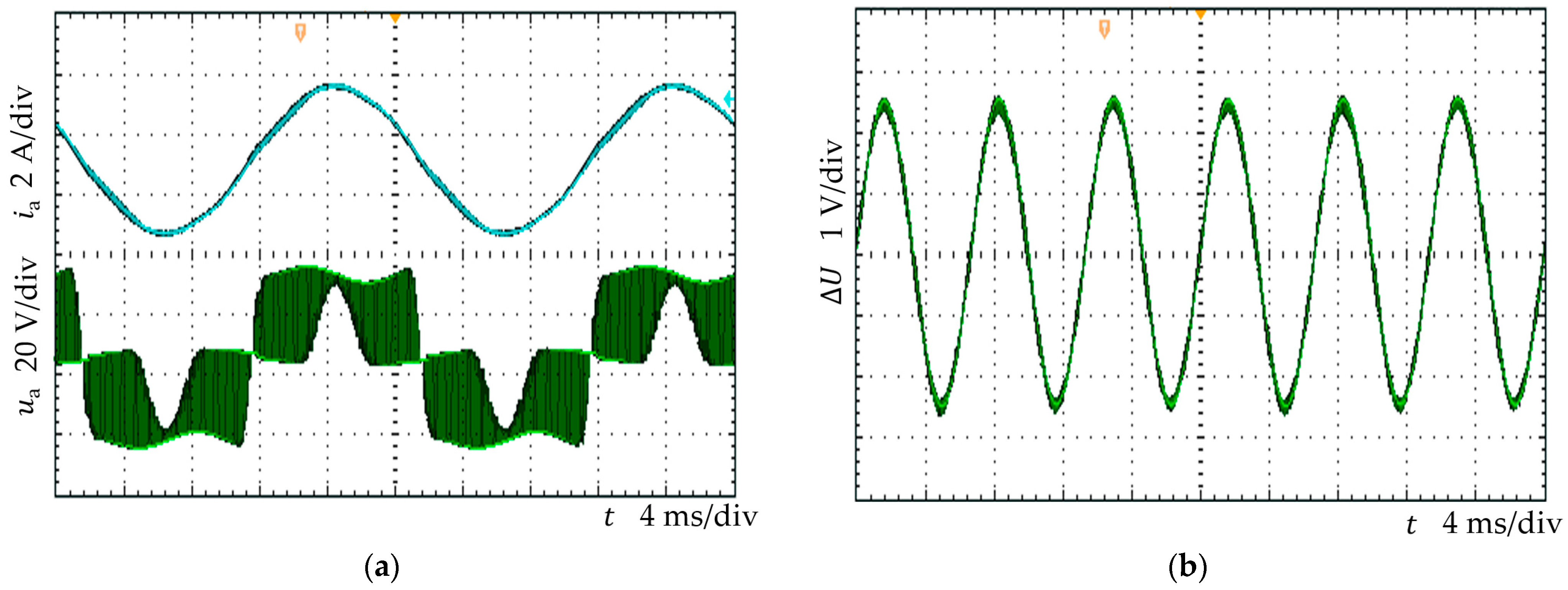

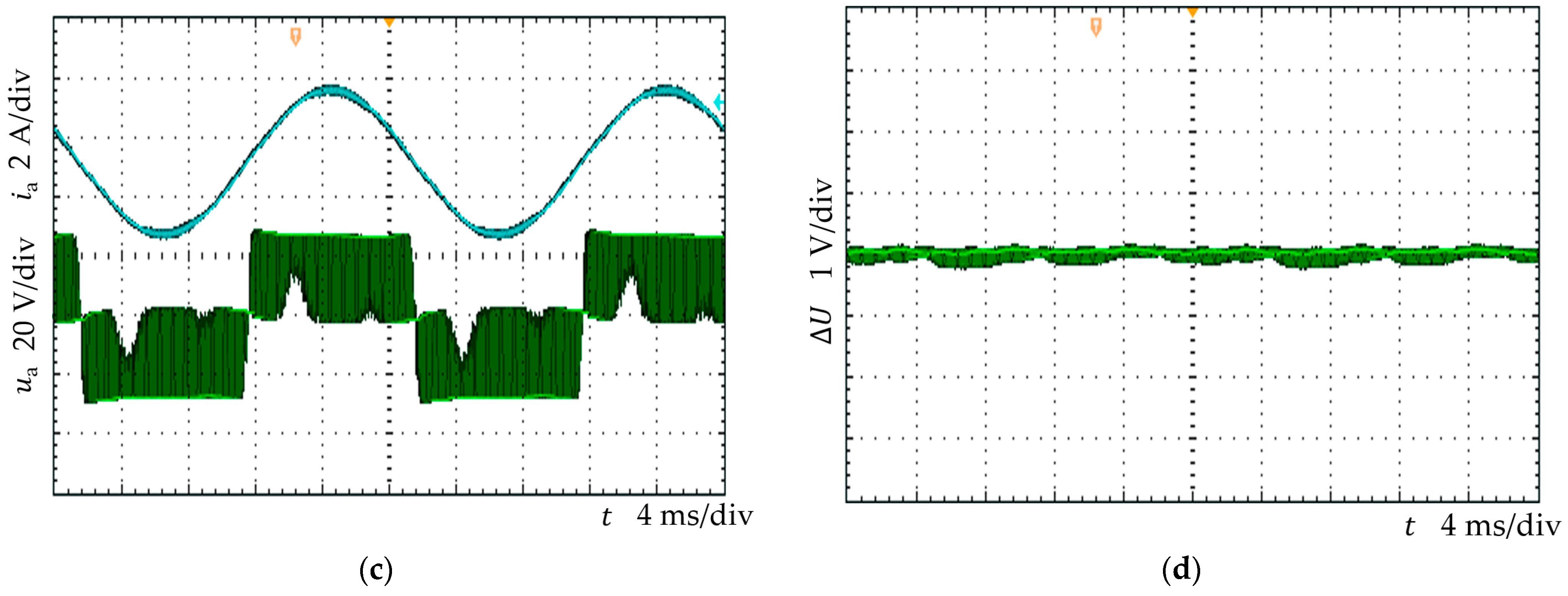

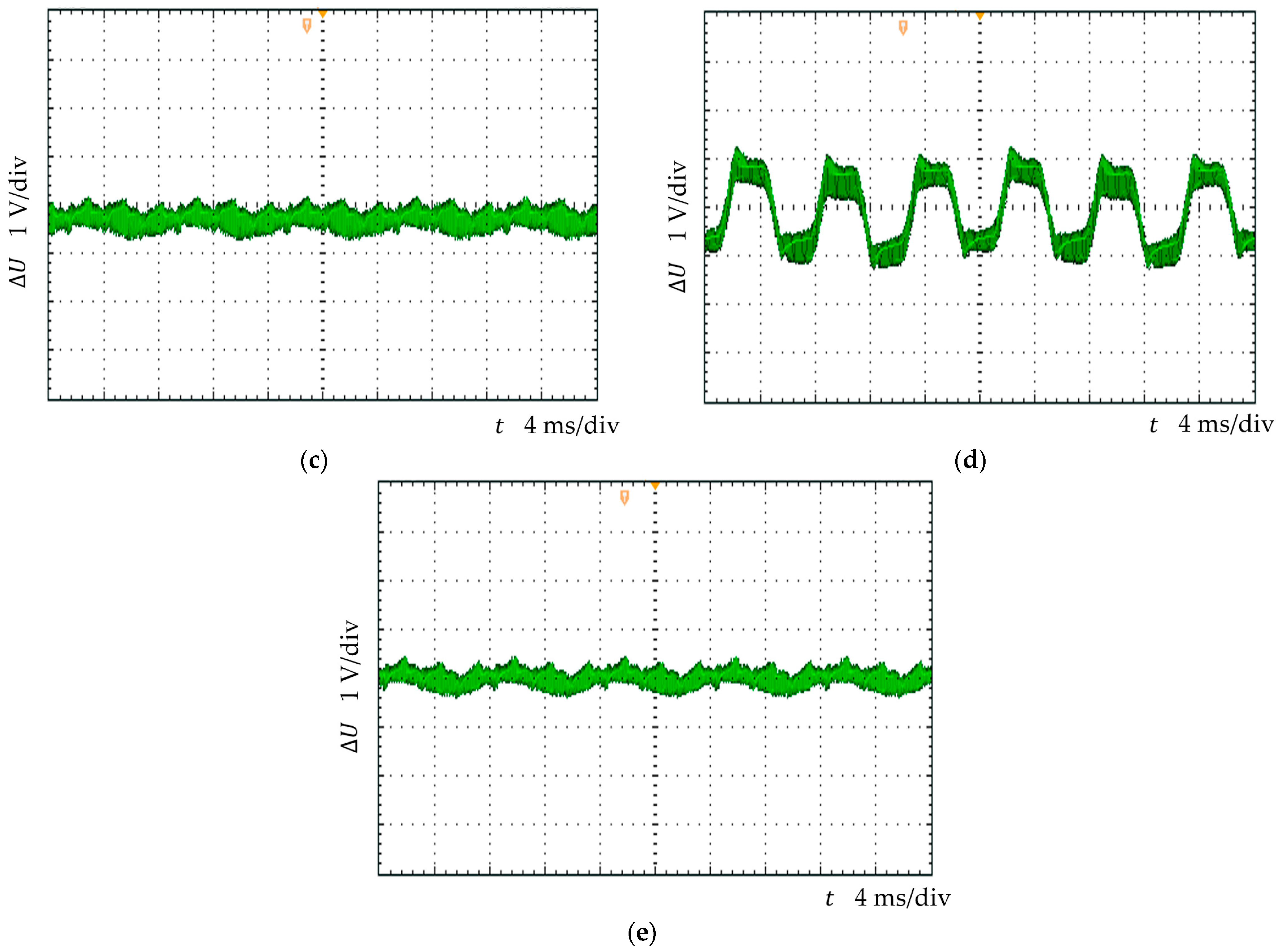

4.2. Experimental Results

5. Conclusions

- (1)

- The proposed average model can accurately calculate the voltage fluctuation of the neutral point. There are only very few discretization errors.

- (2)

- The proposed method can effectively suppress the voltage fluctuation of the neutral point. In the condition of high-power factor and low-modulation ratio, the voltage variation in each switching cycle can be self-balanced. The amplitude of the voltage fluctuation of the neutral point is much lower than that without compensation.

- (3)

- The power factor and modulation ratio have a great influence on the suppression ability of the proposed method. Usually, the higher the power factor and the lower the modulation ratio, the better the suppression effect. However, even the proposed method cannot achieve completed compensation in the condition of low-power factor and high-modulation ratio. The amplitude of the neutral-point voltage fluctuation is still much lower than without compensation.

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Nabae, A.; Takahashi, I.; Akagi, H. A New Neutral-Point-Clamped PWM Inverter. IEEE Trans. Ind. Appl. 1981, 17, 518–523. [Google Scholar] [CrossRef]

- Chen, G.; Gong, C.; Bao, J.; Zhu, L.; Wang, Z. Compensation Voltage Injection Based Neutral Point Voltage Fluctuation Suppression for NPC Converter. In Proceedings of the 2022 Asia Power and Electrical Technology Conference (APET), Shanghai, China, 13 November 2022; pp. 203–208. [Google Scholar]

- Liu, P.; Duan, S.; Yao, C.; Chen, C. A Double Modulation Wave CBPWM Strategy Providing Neutral-Point Voltage Oscillation Elimination and CMV Reduction for Three-Level NPC Inverters. IEEE Trans. Ind. Electron. 2018, 65, 16–26. [Google Scholar] [CrossRef]

- Oghorada, O.; Li, Z.; Esan, A.; Egbune, D.; Uwagboe, J. Inter-cluster Voltage Balancing Control of Modular Multilevel Cascaded Converter Under Unbalanced Grid Voltage. Prot. Control. Mod. Power Syst. 2022, 6, 289–299. [Google Scholar] [CrossRef]

- Wang, Z.; Cui, F.; Zhang, G.; Shi, T.; Xia, C. Novel Carrier-Based PWM Strategy with Zero-sequence Voltage Injected for Three-Level NPC Inverter. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 1442–1451. [Google Scholar] [CrossRef]

- Xia, C.; Zhang, G.; Yan, Y.; Xin, G.; Shi, T.; He, X. Discontinuous Space Vector PWM Strategy of Neutral-Point-Clamped Three-Level Inverters for Output Current Ripple Reduction. IEEE Trans. Power Electron. 2017, 32, 5109–5121. [Google Scholar] [CrossRef]

- Tsai, M.J.; Chen, H.C.; Tsai, M.R.; Wang, Y.B.; Cheng, P.T. Evaluation of Carrier-based Modulation Techniques with Common-Mode Voltage Reduction for Neutral Point Clamped Converter. IEEE Trans. Power Electron. 2017, 33, 3268–3275. [Google Scholar] [CrossRef]

- Jiang, W.; Wang, P.; Ma, M.; Wang, J.; Li, J.; Li, L.; Chen, K. A Novel Virtual Space Vector Modulation With Reduced Common-Mode Voltage and Eliminated Neutral Point Voltage Oscillation for Neutral Point Clamped Three-Level Inverter. IEEE Trans. Ind. Electron. 2020, 67, 884–894. [Google Scholar] [CrossRef]

- Jayakumar, V.; Chokkalingam, B.; Munda, J. A Comprehensive Review on Space Vector Modulation Techniques for Neutral Point Clamped Multi-Level Inverters. IEEE Access 2021, 9, 112104–112144. [Google Scholar] [CrossRef]

- Li, F.; He, F.; Ye, Z.; Fernando, T.; Wang, X.; Zhang, X. A Simplified PWM Strategy for Three-Level Converters on Three-Phase Four-Wire Active Power Filter. IEEE Trans. Power Electron. 2017, 33, 4396–4406. [Google Scholar] [CrossRef]

- Giri, S.K.; Chakrabarti, S.; Banerjee, S.; Chakraborty, C. A Carrier-Based PWM Scheme for Neutral Point Voltage Balancing in Three-Level Inverter Extending to Full Power Factor Range. IEEE Trans. Ind. Electron. 2017, 64, 1873–1883. [Google Scholar] [CrossRef]

- Ding, W.; Qiu, H.; Duan, B.; Xing, X.; Cui, N.; Zhang, C. A Novel Segmented Component Injection Scheme to Minimize the Oscillation of DC-Link Voltage Under Balanced and Unbalanced Conditions for Vienna Rectifier. IEEE Trans. Power Electron. 2019, 34, 9536–9551. [Google Scholar] [CrossRef]

- Jiang, W.D.; Du, S.W.; Shi, X.F.; Bao, X.H. Hybrid PWM Strategy of SVPWM and VSVPWM for Neutral Point-clamped Three-level Voltage Source Inverter. Proc. CSEE 2009, 29, 47–53. [Google Scholar]

- Xia, C.; Shao, H.; Zhang, Y.; He, X. Adjustable Proportional Hybrid SVPWM Strategy for Neutral-Point-Clamped Three-Level Inverters. IEEE Trans. Ind. Electron. 2013, 60, 4234–4242. [Google Scholar] [CrossRef]

- Bendre, A.; Venkataramanan, G.; Rosene, D.; Srinivasan, V. Modeling and design of a neutral-point voltage regulator for a three-level diode-clamped inverter using multiple-carrier modulation. IEEE Trans. Ind. Electron. 2006, 53, 718–726. [Google Scholar] [CrossRef]

- Chaturvedi, P.; Jain, S.; Agarwal, P. Carrier-Based Neutral Point Potential Regulator With Reduced Switching Losses for Three-Level Diode-Clamped Inverter. IEEE Trans. Ind. Electron. 2014, 61, 613–624. [Google Scholar] [CrossRef]

- Pou, J.; Zaragoza, J.; Ceballos, S.; Saeedifard, M.; Boroyevich, D. A Carrier-Based PWM Strategy With Zero-Sequence Voltage Injection for a Three-Level Neutral-Point-Clamped Converter. IEEE Trans. Power Electron. 2012, 27, 642–651. [Google Scholar] [CrossRef]

- Xiong, W.; Zhu, X.; Lin, J.; Xie, S.; Sun, Y.; Liu, Y.; Su, M. An Algebraic Modulation Strategy for 3L-NPC Converters With Inherent Neutral-Point Voltage Balance Capability. IEEE Trans. Power Electron. 2022, 37, 7533–7539. [Google Scholar] [CrossRef]

- Yu, T.; Wan, W.; Duan, S. A Modulation Method to Eliminate Leakage Current and Balance Neutral-Point Voltage for Three-Level Inverters in Photovoltaic Systems. IEEE Trans. Ind. Electron. 2023, 70, 1635–1645. [Google Scholar] [CrossRef]

- Kang, K.P.; Cho, Y.; Ryu, M.H.; Baek, J.W. A Harmonic Voltage Injection Based DC-Link Imbalance Compensation Technique for Single-Phase Three-Level Neutral-Point-Clamped (NPC) Inverters. Energies 2018, 11, 1886. [Google Scholar] [CrossRef]

- Hammami, M.; Rizzoli, G.; Mandrioli, R.; Grandi, G. Capacitors Voltage Switching Ripple in Three-Phase Three-Level Neutral Point Clamped Inverters with Self-Balancing Carrier-Based Modulation. Energies 2018, 11, 3244. [Google Scholar] [CrossRef]

- Odeh, C.; Kondratenko, D.; Lewicki, A.; Jąderko, A. Modified SPWM Technique with Zero-Sequence Voltage Injection for a Five-Phase, Three-Level NPC Inverter. Energies 2021, 14, 1198. [Google Scholar] [CrossRef]

| /2 | ON | ON | OFF | OFF | 1 |

| 0 | OFF | ON | ON | OFF | 0 |

| /2 | OFF | OFF | ON | ON | −1 |

| Vector | Vector | Vector | |||

|---|---|---|---|---|---|

| ONN | POO | ONP | |||

| POP | ONO | PON | |||

| NNO | OOP | PNO | |||

| OPP | NOO | OPN | |||

| NON | OPO | NOP | |||

| PPO | OON | NPO |

| Parameters | Value |

|---|---|

| DC voltage /V | 50 |

| Switching frequency/kHz | 10 |

| DC capacitor /μF | 300 |

| DC capacitor /μF | 300 |

| Inductor L/mH | 5 |

| Resistor R/Ω | 10 |

| Inductor L/mH | 7 |

| Resistor R/Ω | 2.5 |

| THD of iabc under Different Cases | THD, Amp of 2nd, Amp of 5th |

|---|---|

| Case1: m = 1, (SPWM without compensation) Case2: m = 1, | 1.90%, 0.32%, 1.60% 1.32%, 0%, 0.007% |

| Case3: m = 1, | 0.69%, 0.12%, 0.49% |

| Case4: m = 0.9, | 0.45%, 0.16%, 0.12% |

| Case5: m = 0.8, | 0.45%, 0.01%, 0% |

| Parameters | Value |

|---|---|

| DC voltage /V | 50 |

| Switching frequency/kHz | 10 |

| DC capacitor /μF | 300 |

| DC capacitor /μF | 300 |

| Inductor L/mH | 5 |

| Resistor R/Ω | 10 |

| Inductor L/mH | 7 |

| Resistor R/Ω | 2.5 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chen, G.; Gong, C.; Bao, J.; Zhu, L.; Wang, Z. Compensation-Voltage-Injection-Based Neutral-Point Voltage Fluctuation Suppression Method for NPC Converters. Energies 2023, 16, 4409. https://doi.org/10.3390/en16114409

Chen G, Gong C, Bao J, Zhu L, Wang Z. Compensation-Voltage-Injection-Based Neutral-Point Voltage Fluctuation Suppression Method for NPC Converters. Energies. 2023; 16(11):4409. https://doi.org/10.3390/en16114409

Chicago/Turabian StyleChen, Guo, Chunyang Gong, Jun Bao, Lihua Zhu, and Zhixin Wang. 2023. "Compensation-Voltage-Injection-Based Neutral-Point Voltage Fluctuation Suppression Method for NPC Converters" Energies 16, no. 11: 4409. https://doi.org/10.3390/en16114409

APA StyleChen, G., Gong, C., Bao, J., Zhu, L., & Wang, Z. (2023). Compensation-Voltage-Injection-Based Neutral-Point Voltage Fluctuation Suppression Method for NPC Converters. Energies, 16(11), 4409. https://doi.org/10.3390/en16114409