Commutation Behavior and Stray Inductance Analysis of a FC-3L-BDC Phase-Leg PEBB

Abstract

:1. Introduction

- The selection procedure of IGBT devices regarding isolation and blocking voltages.

- Step-by-step analysis of how the stray inductance is presented in the commutation paths of FC-3L-BDC and the influences of stray inductance on the switching behavior of IGBT devices.

- Design guidelines of an FC-3L-BDC phase-leg PEBB with an extremely low commutation stray inductance and high isolation voltage.

- The accurate stray inductance measurement of a capacitor and single IGBT in a half-bridge package and stray inductance estimation and verification of the FC-3L-BDC phase-leg PEBB.

- Checking for the turn-off and coupling overvoltage of IGBTs over the entire current range, and snappy reverse recovery of FWDs at one-tenth of the nominal current of IGBT devices.

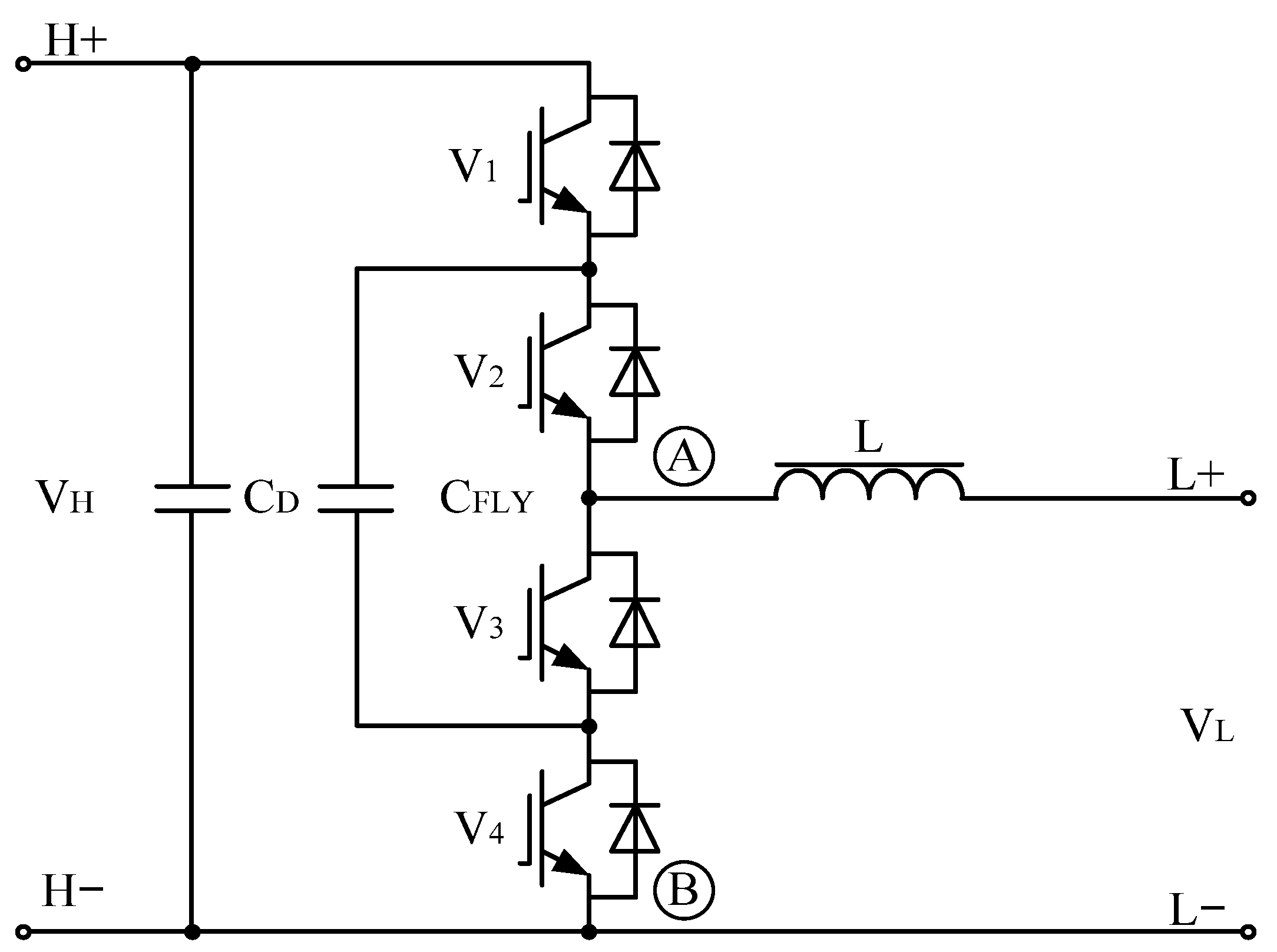

2. Operation Principle of FC-3L-BDC

3. Analysis of Commutation Paths of FC-3L-BDC

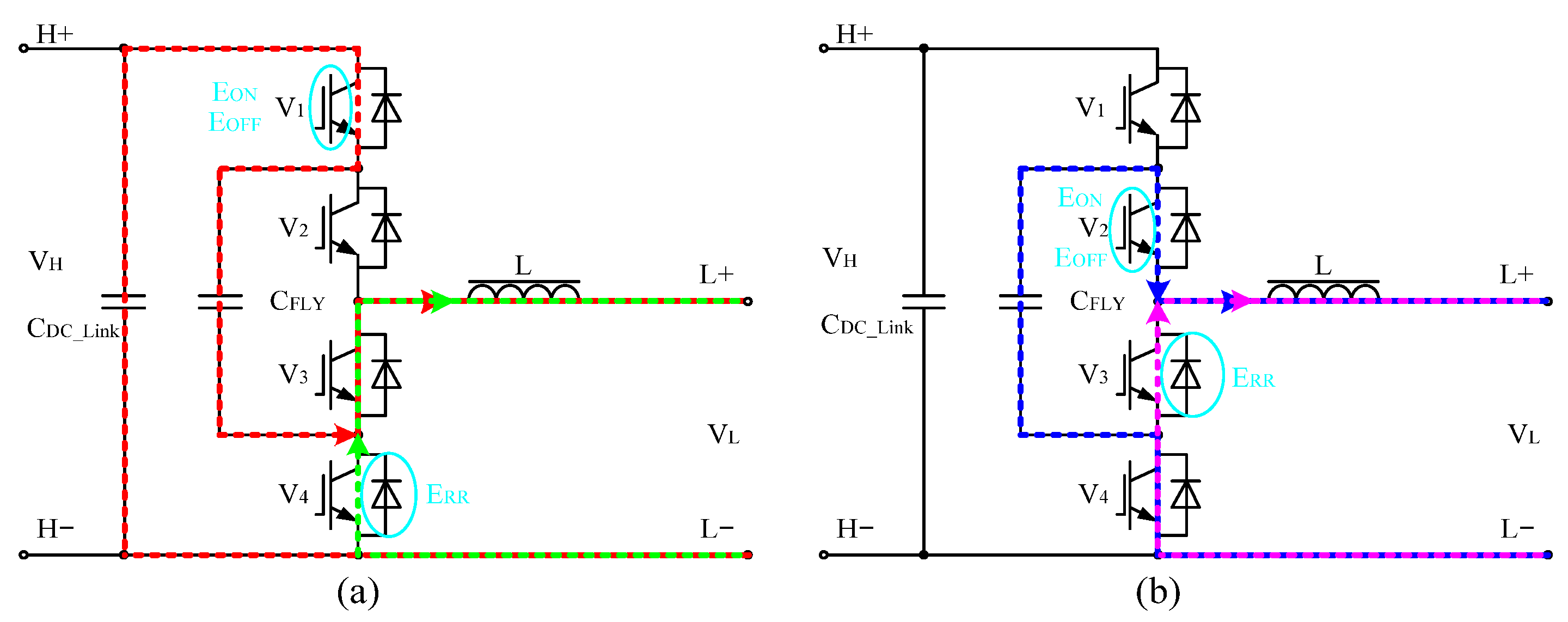

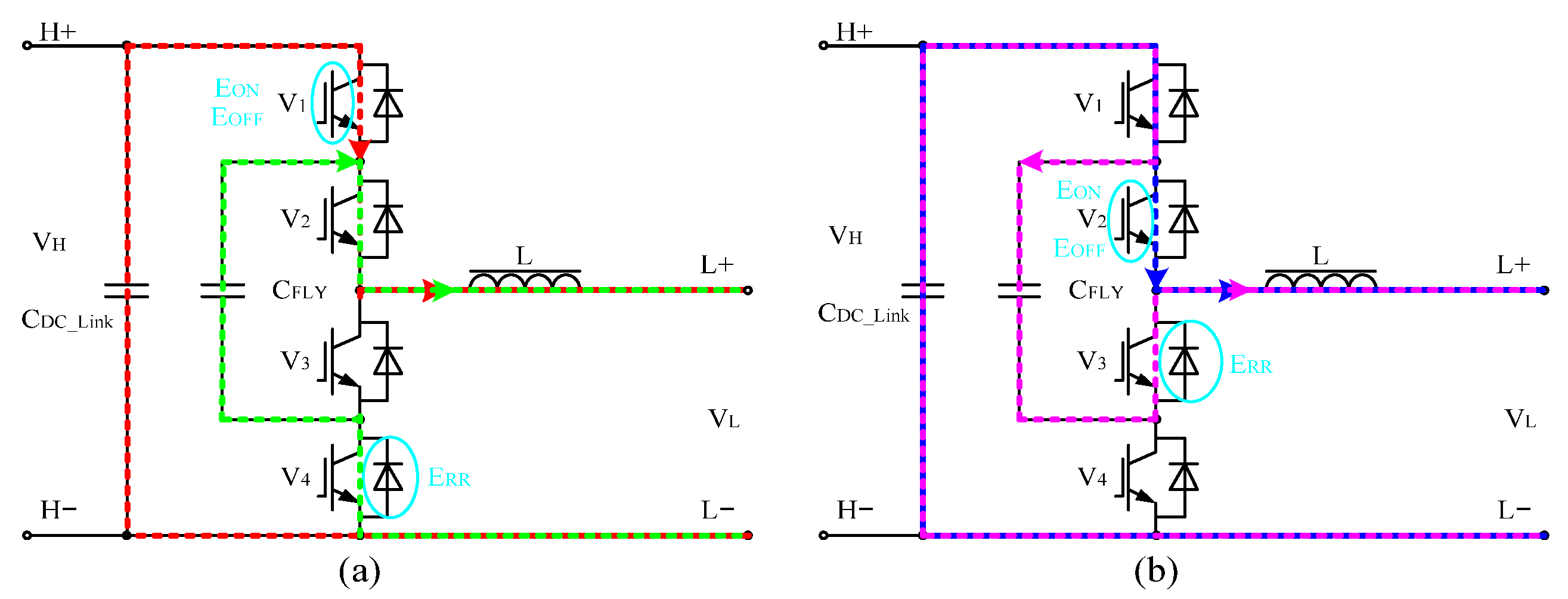

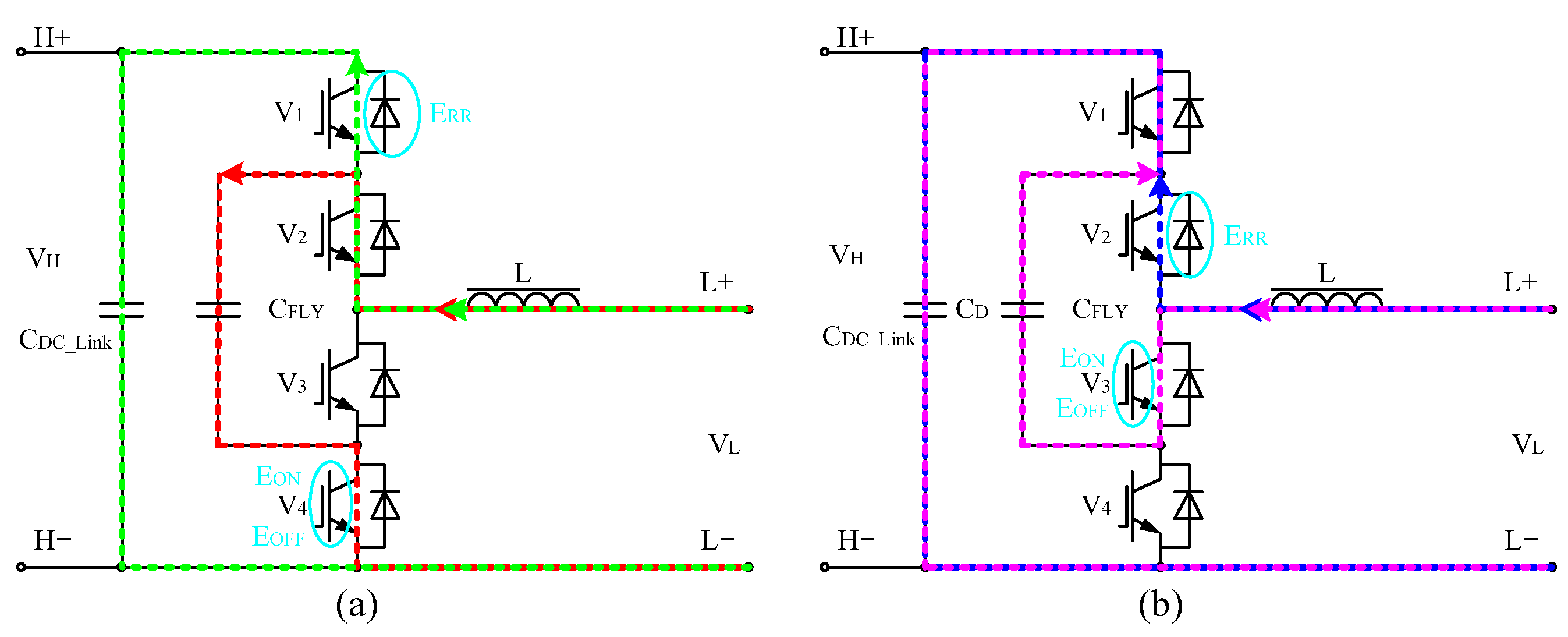

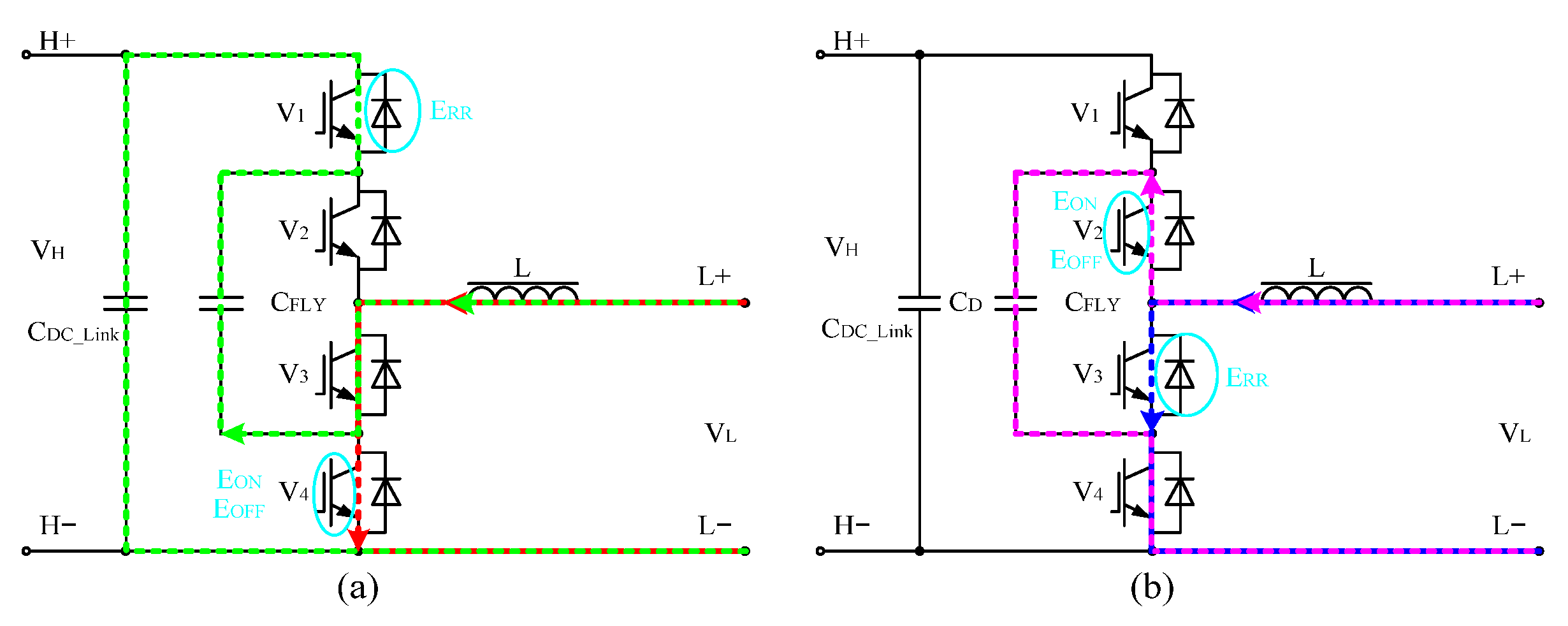

3.1. Commutation Paths

3.2. The Influences of Commutation Path Stray Inductance

4. The Design of FC-3L-BDC Phase-Leg PEBB

4.1. Selection of IGBT Devices

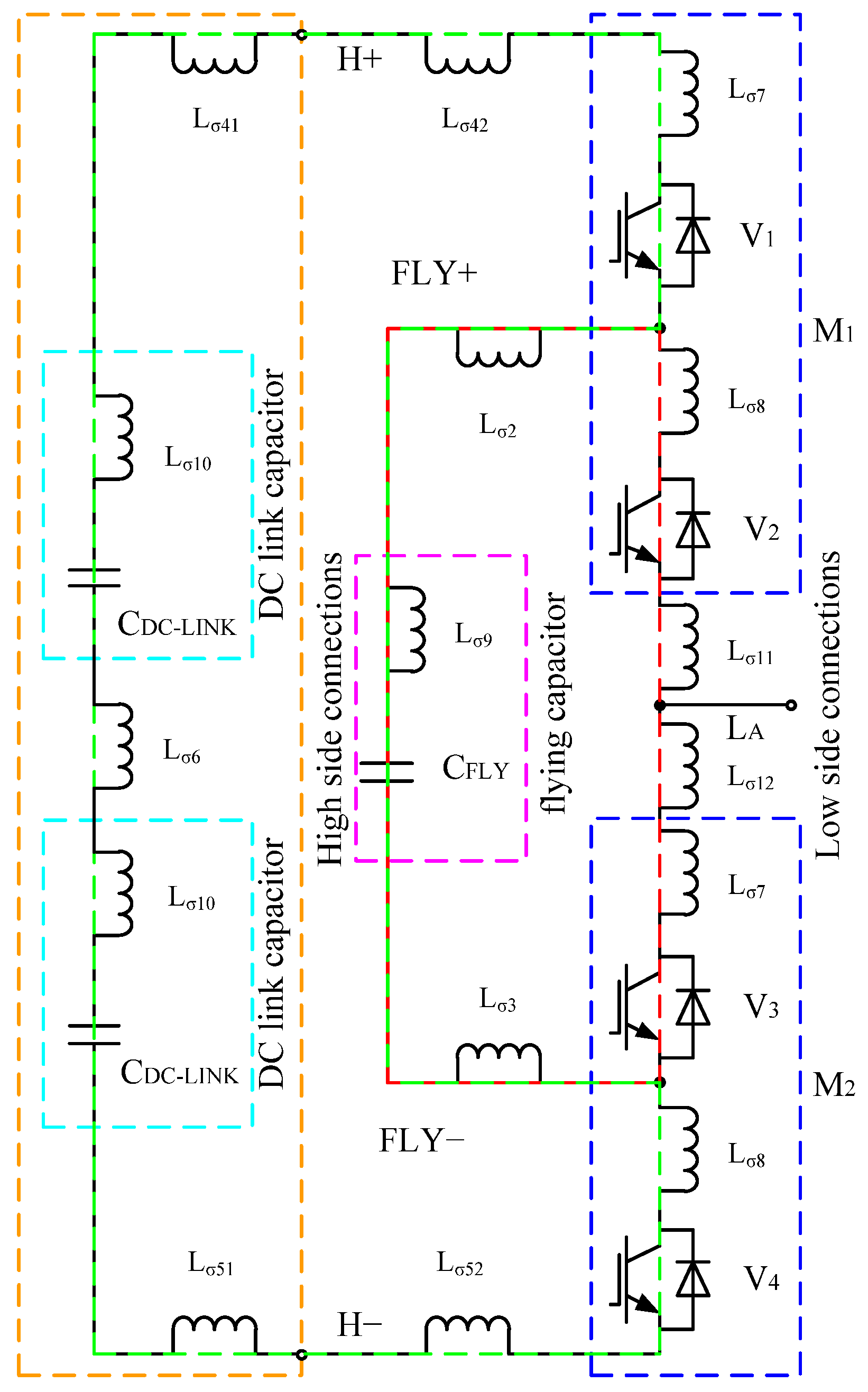

4.2. Description of PEBB

- Cost effectiveness, by using industry-standardized IGBT devices and metal film capacitors.

- Production efficiency, by using a laminated bus bar.

- Maintainability, by using force-air cooling and a single phase-leg configuration. Only the flying capacitors are integrated in the PEBB. The high-voltage-side DC-link capacitors are installed in the converter cabinet. In this approach, the weight of the PEBB can be minimized.

- A symmetrical layout should be adopted. Actually, if the placement direction of IGBT devices is consistent and aligned, the symmetry of the layout can be guaranteed.

- Reduce the difference in stray inductance between the outer and inner commutation paths. Reduce Lσ_O as much as possible.

- Completely overlap the copper planar sheets in each layer.

- Since the commutation current directions of “H−” and “H+” layers are opposite, the two layers should be arranged next to each other.

- Since the commutation current directions of “FLY+”, “FLY−”, and “LA” layers are opposite, the three layers should be arranged next to each other.

4.3. Clearance and Creepage Distances

5. Stray Inductance Estimation

5.1. Lumped Stray Inductance Model of PEBB with Mutual Coupling Consideration

5.2. Estimation of Stray Inductance of Laminated Bus Bars

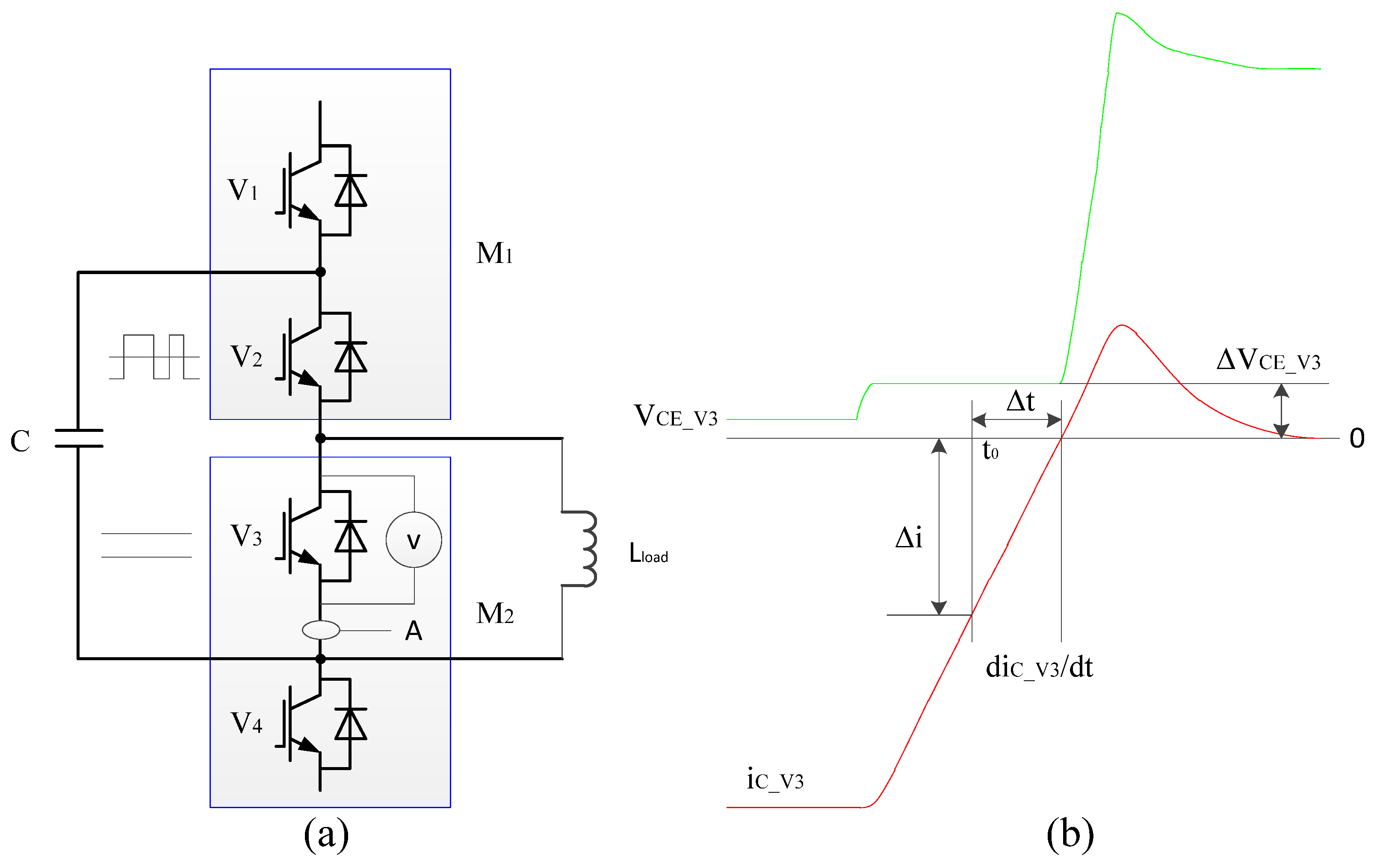

5.3. Stray Inductance of IGBT

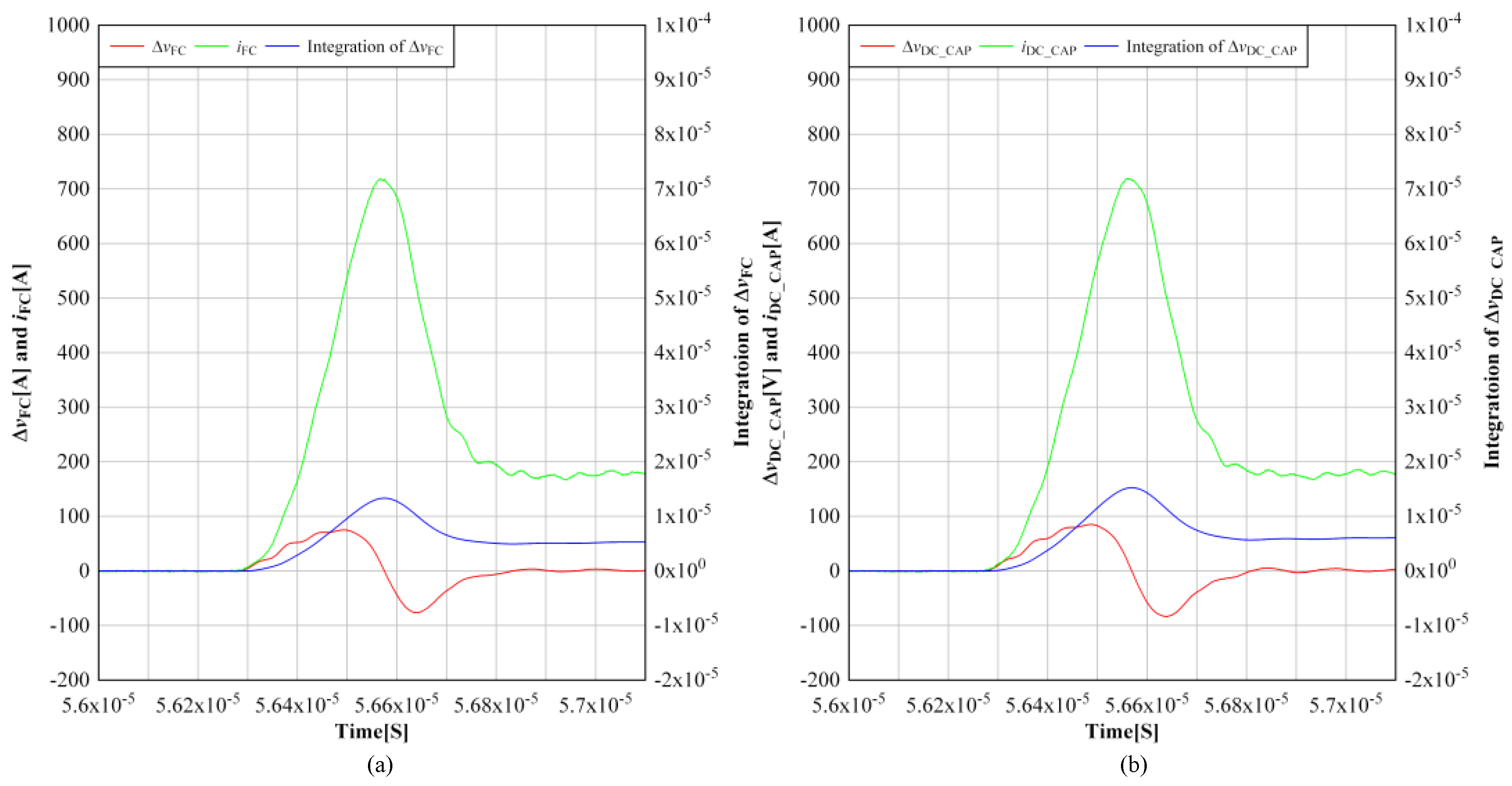

5.4. Stray Inductance of Flying Capacitor and DC-Link Capacitor

5.5. Effective Stray Inductance of Commutation Loop

6. Experimental Results

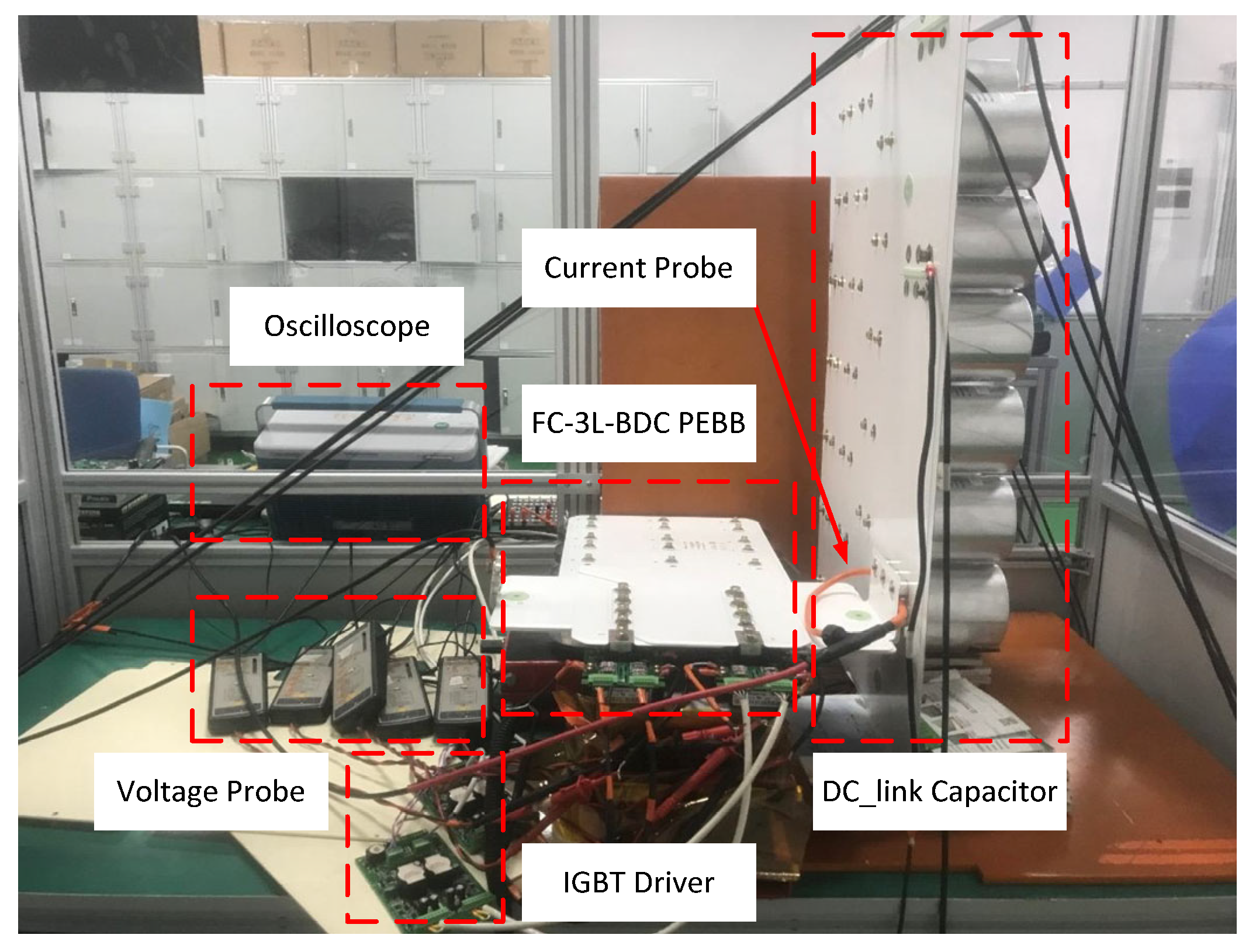

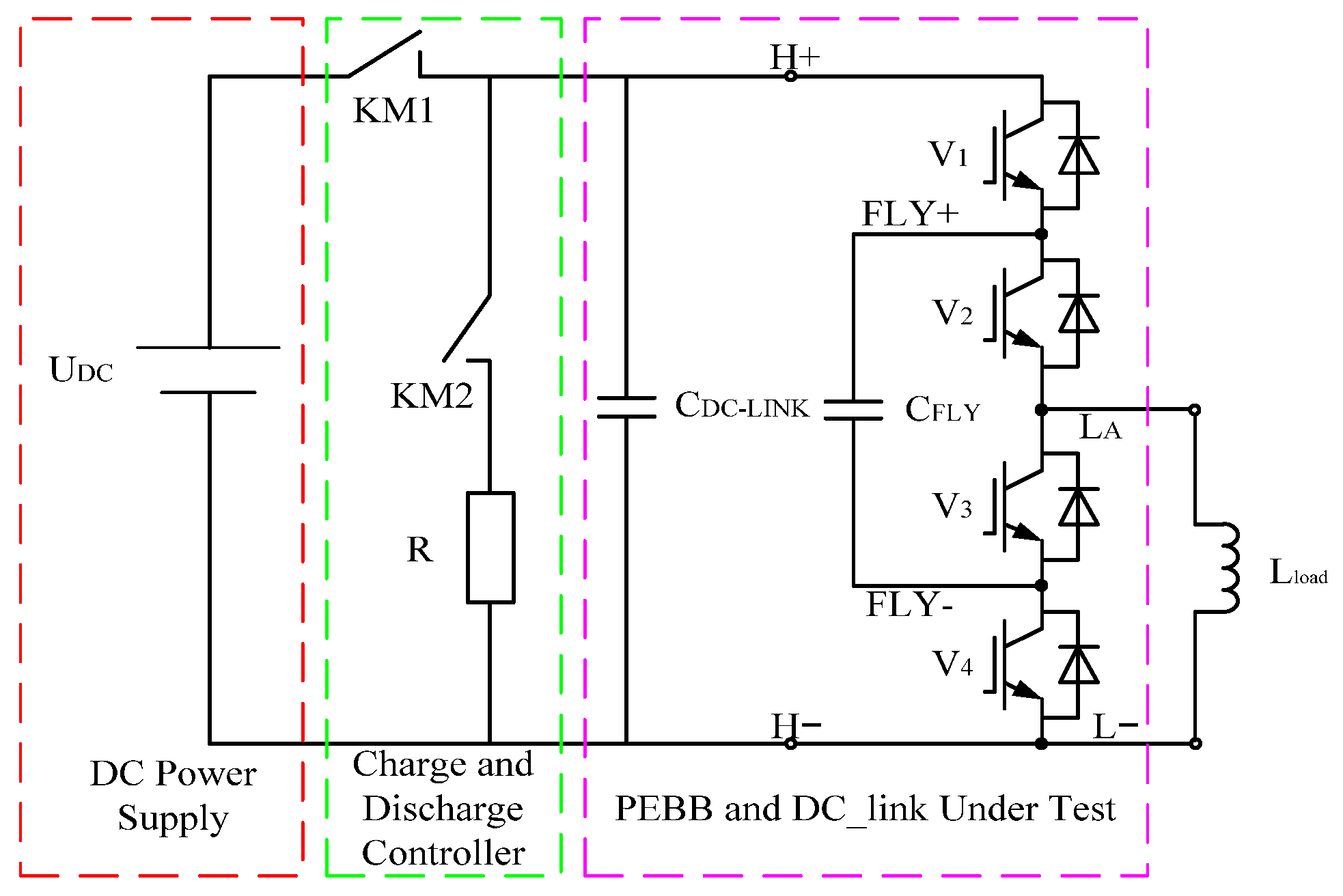

6.1. Test Bench Description

6.2. Double-Pulse Test for the FC-3L-BDC Phase-Leg PEBB

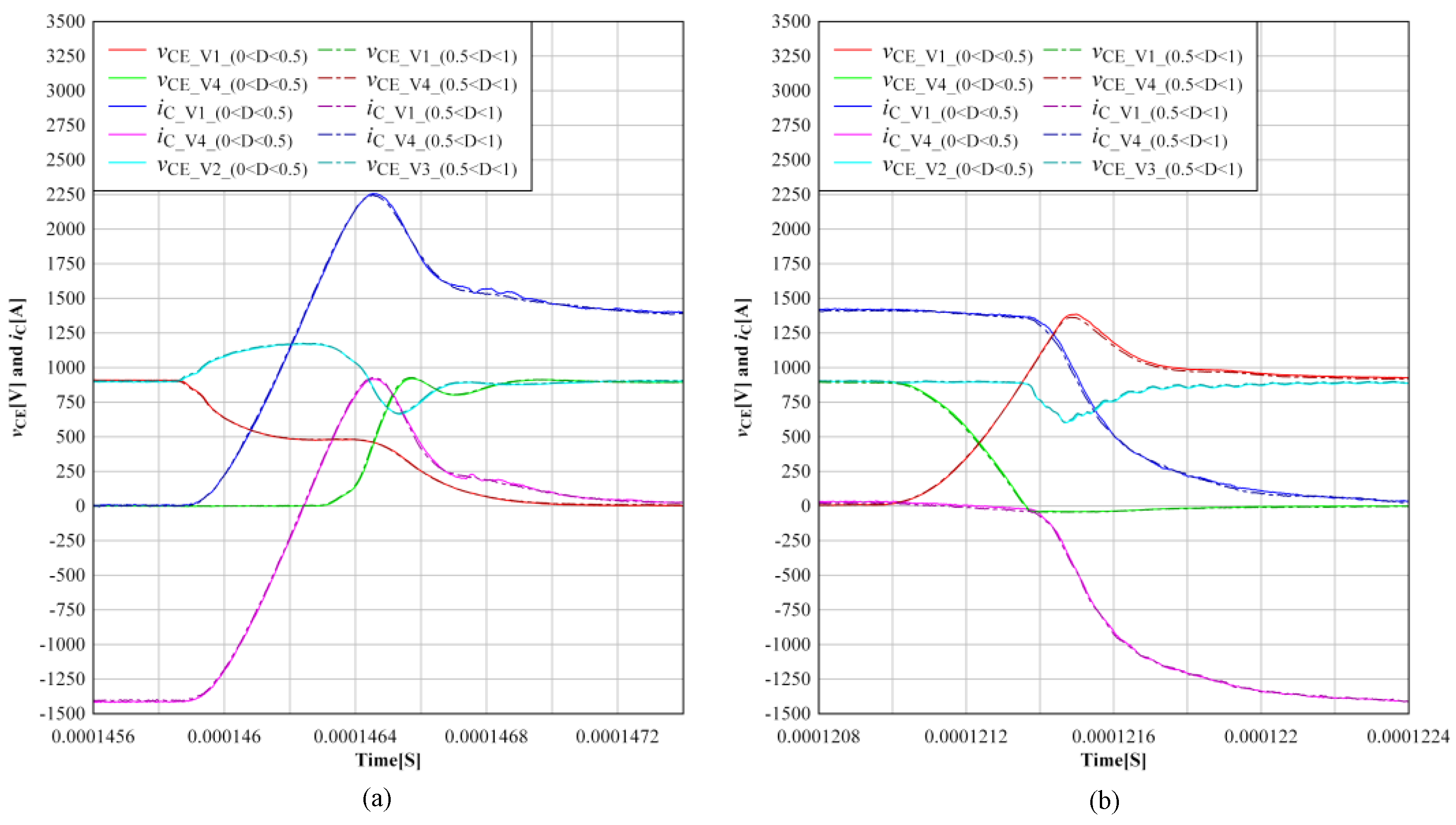

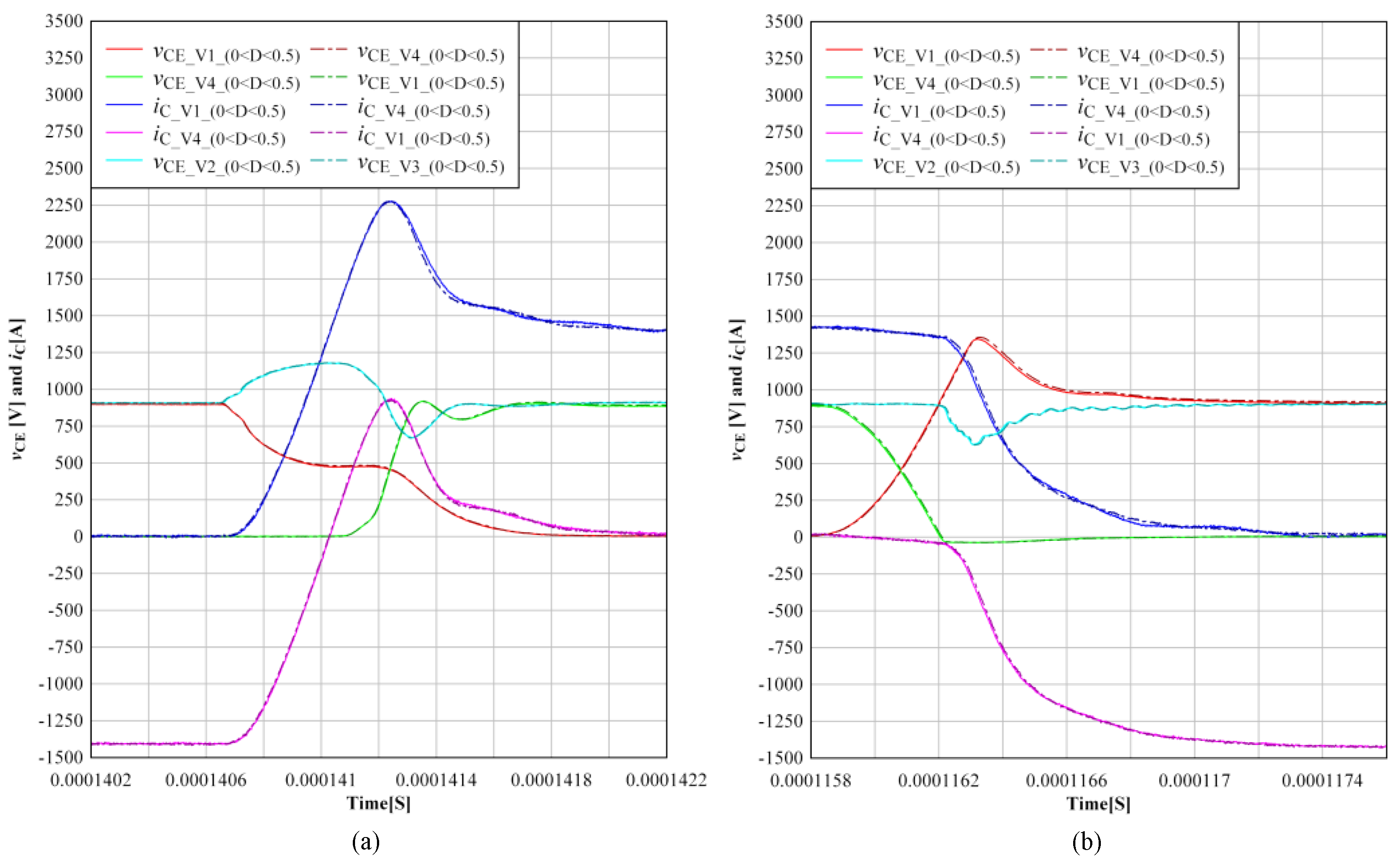

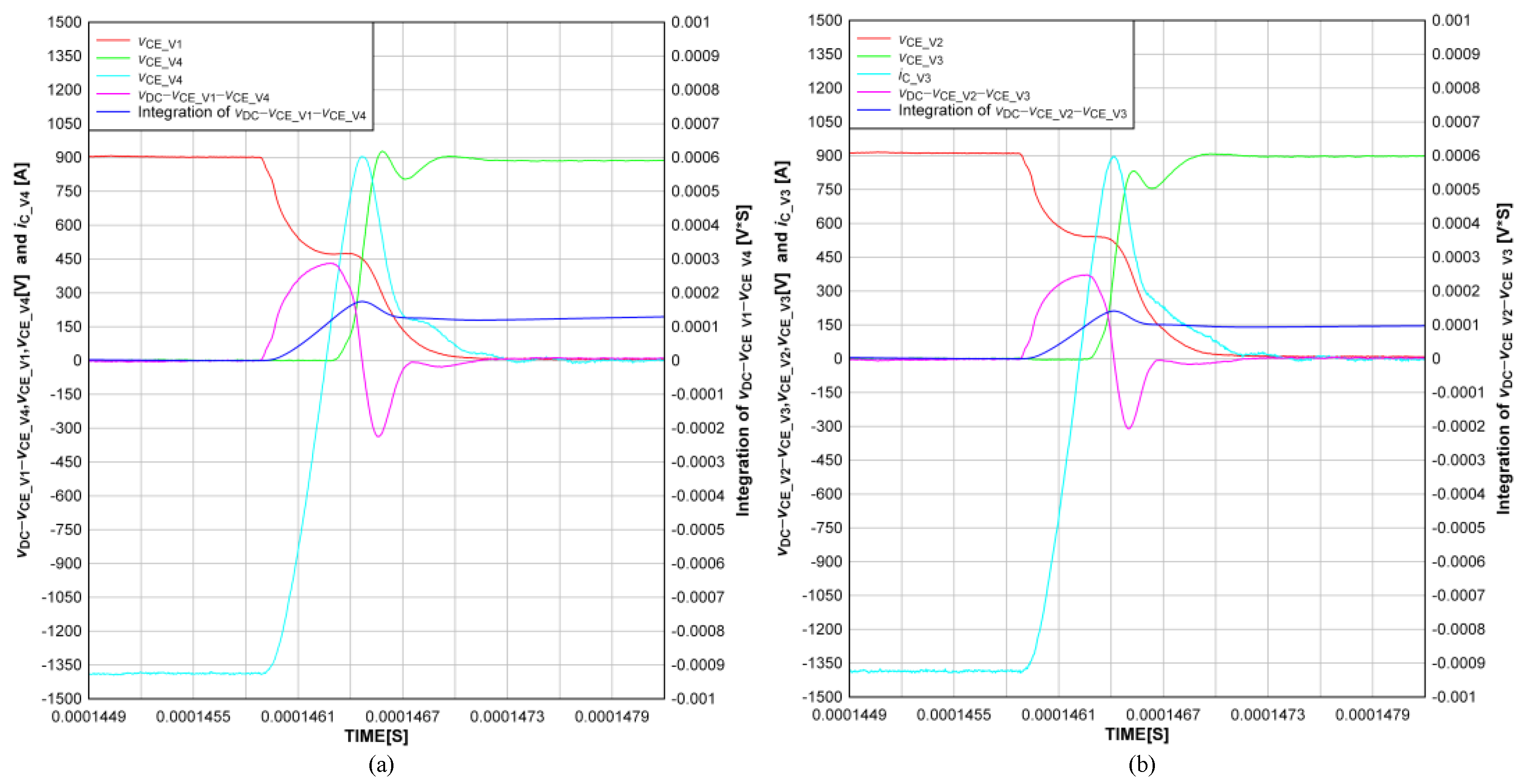

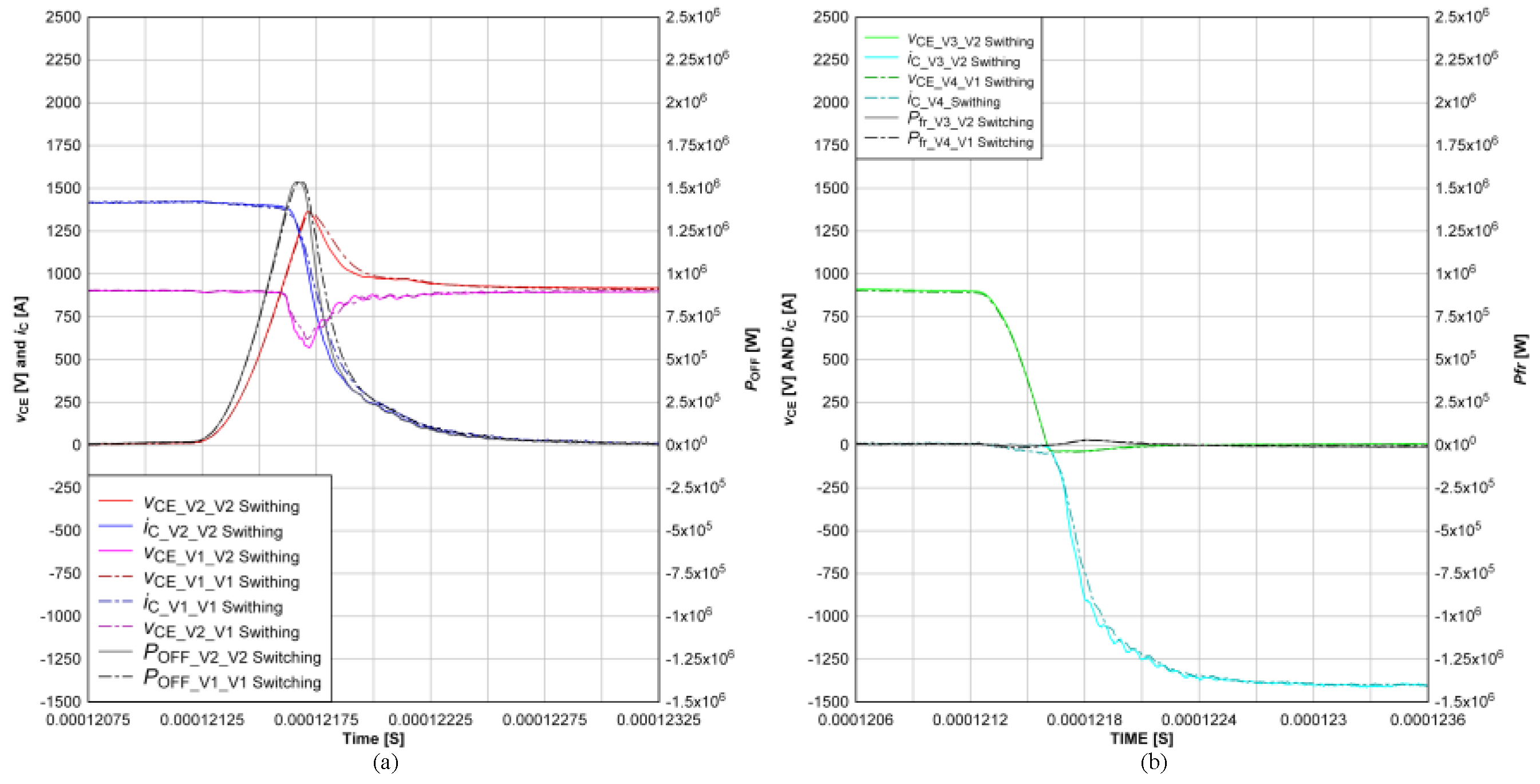

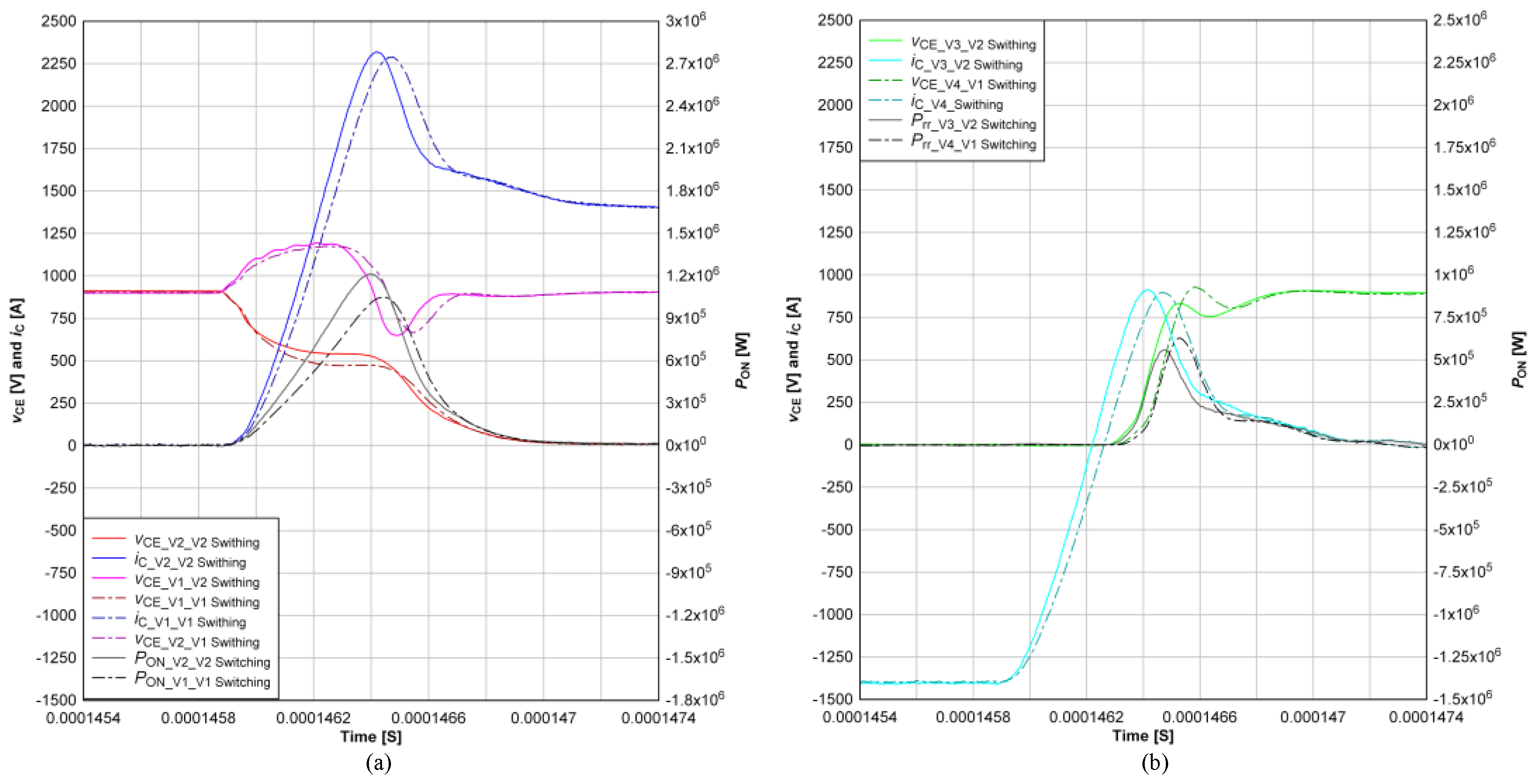

6.3. The Influence of Current Paths on IGBT Switching Characteristics

6.4. The Influence of IGBT Position on IGBT Switching Characteristics

6.5. Stray Inductance Measurements

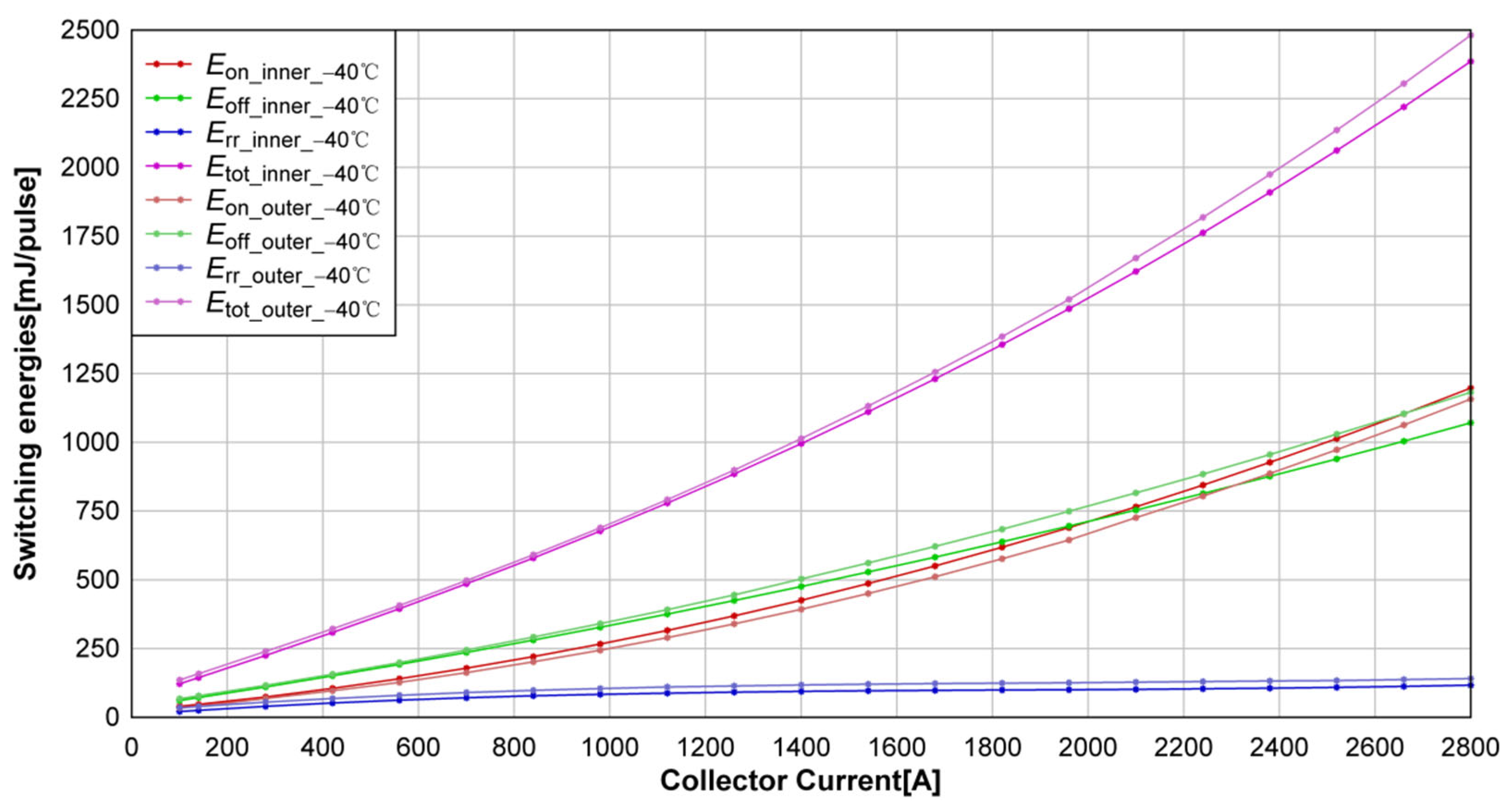

6.6. Comparison of Outer and Inner Commutation Paths

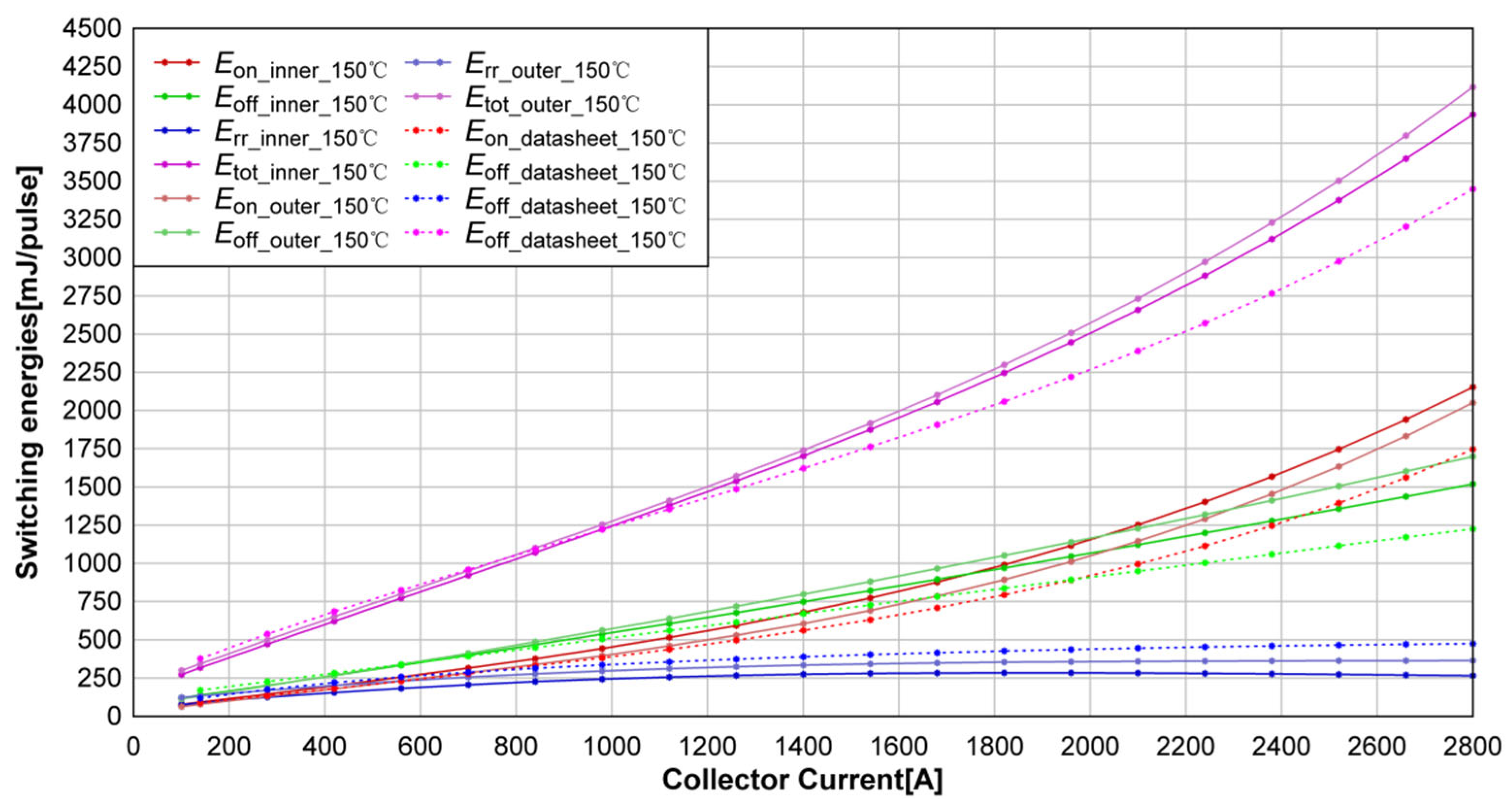

6.7. Switching Energy Loss Measurements

6.8. Verification of Snappy Reverse Recovery in the FWD

7. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- IPCC. 2021: Summary for Policymakers. In Climate Change 2021: The Physical Science Basis. Contribution of Working Group I to the Sixth Assessment Report of the Intergovernmental Panel on Climate Change; Masson-Delmotte, V., Zhai, P., Pirani, A., Connors, S.L., Péan, C., Berger, S., Caud, N., Chen, Y., Goldfarb, L., Gomis, M.I., Eds.; Cambridge University Press: Cambridge, UK; New York, NY, USA, 2021; pp. 3–32. [Google Scholar] [CrossRef]

- IPCC. 2022: Summary for Policymakers. In Climate Change 2022: Mitigation of Climate Change. Contribution of Working Group III to the Sixth Assessment Report of the Intergovernmental Panel on Climate Change; Shukla, P.R., Skea, J., Slade, R., Al Khourdajie, A., van Diemen, R., McCollum, D., Pathak, M., Some, S., Vyas, P., Fradera, R., Eds.; Cambridge University Press: Cambridge, UK; New York, NY, USA, 2021. [Google Scholar] [CrossRef]

- Bi, K.; Lv, H.; Chen, L.; Li, J.; Zhu, Y.; Huang, W.; Fan, Q. A Model Predictive Controlled Bidirectional Four Quadrant Flying Capacitor DC/DC Converter Applied in Energy Storage System. IEEE Trans. Power Electron. 2022, 37, 7705–7717. [Google Scholar] [CrossRef]

- Yagoub, M.A.; Tao, Z. Modelling analysis and simulation of a micro-grid using photovoltaic (PV) & battery based power generation. In Proceedings of the 16th IET International Conference on AC and DC Power Transmission (ACDC 2020), Online, 2–3 July 2020; pp. 1514–1521. [Google Scholar] [CrossRef]

- Jayan, V.; Ghias, A.M.Y.M. A Single-Objective Modulated Model Predictive Control for a Multilevel Flying Capacitor Converter in a DC Microgrid. IEEE Trans. Power Electron. 2022, 37, 1560–1569. [Google Scholar] [CrossRef]

- Jin, K.; Ruan, X.; Yang, M.; Xu, M. A Hybrid Fuel Cell Power System. IEEE Trans. Ind. Electron. 2008, 56, 1212–1222. [Google Scholar] [CrossRef]

- Hasimi, N.; Hinz, H.; Schofield, N. Comparative Analysis of Bidirectional DC-DC Converters for Fuel Cell Hybrid Vehicles. In Proceedings of the 10th International Conference on Power Electronics, Machines and Drives (PEMD 2020), Online, 15–17 December 2020; pp. 68–74. [Google Scholar] [CrossRef]

- Qu, X.; Tian, L.; Li, J.; Lou, C.; Jiang, T. Research on Charging and discharging Strategies of Regenerative Braking Energy Recovery System for Metro Flywheel. In Proceedings of the 2021 3rd Asia Energy and Electrical Engineering Symposium (AEEES), Chengdu, China, 26–29 March 2021; pp. 1087–1095. [Google Scholar] [CrossRef]

- Lu, Y.; Zhao, Y.; Zhao, X.; Li, G.; Zhang, C. Status analysis of regenerative braking energy utilization equipments in urban rail transit. In Proceedings of the 2017 IEEE Transportation Electrification Conference and Expo, Asia-Pacific (ITEC Asia-Pacific), Harbin, China, 7–10 August 2017; pp. 1–6. [Google Scholar] [CrossRef]

- Chen, L.; Huang, K.; Lv, W.; Zhang, D.; Huang, S. Control Strategy of Modularized Ultra-capacitor Energy Storage System for Regenerative Braking Energy in Metro-Transit Systems. In Proceedings of the 2019 22nd International Conference on Electrical Machines and Systems (ICEMS), Harbin, China, 11–14 August 2019; pp. 1–5. [Google Scholar] [CrossRef]

- Calderaro, V.; Galdi, V.; Graber, G.; Piccolo, A. Siting and sizing of stationary Super Capacitors in a Metro Network. In Proceedings of the AEIT Annual Conference 2013 (AEIT), Mondello, Palermo, Italy, 3–5 October 2013; pp. 1–5. [Google Scholar] [CrossRef]

- Flynn, M.; Mcmullen, P.; Solis, O. Saving energy using flywheels. IEEE Ind. Appl. Mag. 2008, 14, 69–76. [Google Scholar] [CrossRef]

- Liang, H.; Dong, L.; Hu, J.; Chen, Y. Energy Management Strategy Based on Dynamic Threshold for Energy Recovery System in Rail Transit. In Proceedings of the 2019 IEEE Vehicle Power and Propulsion Conference (VPPC), Hanoi, Vietnam, 14–17 October 2019; pp. 1–6. [Google Scholar] [CrossRef]

- Bhanderi, M.D.; Chavda, J.K. Ultra-capacitor based three level bi-directional isolated DC-DC converter for the regenerative breaking energy recovery system. In Proceedings of the 2017 International Conference on Information, Communication, Instrumentation and Control (ICICIC), Indore, India, 17–19 August 2017; pp. 1–6. [Google Scholar] [CrossRef]

- Grbovic, P.J.; Delarue, P.; Le Moigne, P. Interface converters for ultra-capacitor applications in power conversion systems. In Proceedings of the 2012 15th International Power Electronics and Motion Control Conference (EPE/PEMC), Novi Sad, Serbia, 4–6 September 2012; pp. LS7d.1-1–LS7d.1-7. [Google Scholar] [CrossRef]

- Ruan, X.; Wei, J.; Xue, Y. Three-level converters with the input and output sharing the ground. In Proceedings of the IEEE 34th Annual Conference on Power Electronics Specialist, 2003. PESC ‘03, Acapulco, Mexico, 15–19 June 2003; Volume 4, pp. 1919–1923. [Google Scholar] [CrossRef]

- Jin, K.; Yang, M.; Ruan, X. Three-Level Bi-Directional Converter—A Novel DC-DC Converter Suitable for Fuel Cell Power System. In Proceedings of the 2006 37th IEEE Power Electronics Specialists Conference, Jeju, Korea, 18–22 June 2006; pp. 1–6. [Google Scholar] [CrossRef]

- Chen, H.-C.; Lu, C.-Y.; Lien, W.-H. Active capacitor voltage balancing control for three-level flying capacitor boost converter. In Proceedings of the 2018 IEEE Applied Power Electronics Conference and Exposition (APEC), San Antonio, TX, USA, 4–8 March 2018; pp. 127–132. [Google Scholar] [CrossRef]

- Kan, Z.; Li, P.; Yuan, R.; Zhang, C. Interleaved three-level bi-directional DC-DC converter and power flow control. In Proceedings of the 2018 3rd International Conference on Intelligent Green Building and Smart Grid (IGBSG), Yilan, Taiwan, 22–25 April 2018; pp. 1–4. [Google Scholar] [CrossRef]

- Zhang, D.; Chen, C.; Ou, Y.; Zheng, T.; Tang, W. Model predictive control of three-level bidirectional DC-DC converter based on super capacitor energy storage system. In Proceedings of the 2020 International Conference on Electrical Engineering (ICEE), Bandung, Indonesia, 23–24 September 2020; pp. 1–5. [Google Scholar] [CrossRef]

- Mahmoudi, M.A.H.; Ahmadi, R. Modulated model predictive control of three level flying capacitor buck converter. In Proceedings of the 2017 IEEE Power and Energy Conference at Illinois (PECI), Champaign, IL, USA, 23–24 February 2017; pp. 1–5. [Google Scholar] [CrossRef]

- Putera, P.; Klumpner, C.; Wheeler, P. A bidirectional three-level interleaved DC-DC converter for an electric vehicle charging station operating in a wide range of battery currents and voltages. In Proceedings of the 11th International Conference on Power Electronics, Machines and Drives (PEMD 2022), Newcastle, UK, 21–23 June 2022; pp. 439–445. [Google Scholar] [CrossRef]

- Ying, Z.; Liang, Z.; Weichao, L.; Xiangming, Z.; Bing, L. Commutation behaviour analysis of a 3L-ANPC-VSC phase-leg PEBB using 4.5kV and 3kA press-pack IGBT. In Proceedings of the 16th IET International Conference on AC and DC Power Transmission (ACDC 2020), Online, 2–3 July 2020; pp. 1837–1842. [Google Scholar] [CrossRef]

- Volke, A.; Hornkamp, M. IGBT Modules; Technologies, Driver and Application; Infineon Technol. AG: Neubiberg, Germany, 2012. [Google Scholar]

- Wintrich, A.; Nicolai, U.; Tursky, W.; Reimann, T. Application Manual Power Semiconductors; Semikron Int. GmbH: Nuremberg, Germany, 2015. [Google Scholar]

- Jin, K.; Yang, M.; Ruan, X.; Xu, M. Three-Level Bidirectional Converter for Fuel-Cell/Battery Hybrid Power System. IEEE Trans. Ind. Electron. 2009, 57, 1976–1986. [Google Scholar] [CrossRef]

- Infineon. Properties of a New PrimePACK™ IGBT Module Concept for Optimized Electrical and Thermal Interconnection to a Modern Converter Environment. 2015. Available online: https://www.infineon.com/dgdl/Infineon-PCIM_2005_Properties_of_a_New_PrimePACK-ED-v1.0-en.pdf?fileId=db3a304412b407950112b40edb6112a9&da=t (accessed on 18 April 2022).

- IEC 61287-1:2014; Railway Applications—Power Converters Installed on Board Rolling Stock—Part 1: Characteristics and Test Methods. International Electrotechnical Commission: Geneva, Switzerland, 2014.

- Mayor, A.; Rizo, M.; Monter, A.R.; Bueno, E.J. Commutation Behavior Analysis of a Dual 3L-ANPC-VSC Phase-Leg PEBB Using 4.5-kV and 1.5-kA HV-IGBT Modules. IEEE Trans. Power Electron. 2018, 34, 1125–1141. [Google Scholar] [CrossRef]

- Skibinski, G.L.; Divan, D.M. Design methodology and modeling of low inductance planar bus structures. In Proceedings of the 1993 Fifth European Conference on Power Electronics and Applications, Brighton, UK, 13–16 September 1993; Volume 3, pp. 98–105. [Google Scholar]

- IEC 62497-1:2010+AMD1:2013; Railway Applications—Insulation Coordination—Part 1: Basic Requirements—Clearances and Creepage Distances for All Electrical and Electronic Equipment. International Electrotechnical Commission: Geneva, Switzerland, 2013.

- Engelmann, G.; Quabeck, S.; Gottschlich, J.; De Doncker, R.W. Experimental and simulative investigations on stray capacitances and stray inductances of power modules. In Proceedings of the 2017 19th European Conference on Power Electronics and Applications (EPE’17 ECCE Europe), Warsaw, Poland, 11–14 September 2017; pp. P.1–P.10. [Google Scholar] [CrossRef]

- IEC 61071:2017; Capacitors for Power Electronics. International Electrotechnical Commission: Geneva, Switzerland, 2017.

- KEYSIGHT. Impedance Measurement Handbook. 2016. Available online: https://www.keysight.com/us/en/assets/7018-06840/application-notes/5950-3000.pdf (accessed on 18 April 2022).

- IEC 60747-2:2016; Semiconductor Devices—Part 2: Discrete Devices—Rectifier Diodes. International Electrotechnical Commission: Geneva, Switzerland, 2016.

- IEC 60747-9:2019; Semiconductor Devices—Part 9: Discrete Devices—Insulated-Gate Bipolar Transistors (IGBTs). International Electrotechnical Commission: Geneva, Switzerland, 2019.

- Tektronix. THDP0100/0200 & TMDP0200 High Voltage Differential Probes Instruction Manual. Available online: https://download.tek.com/manual/THDP0100-0200-TMDP0200-High-Voltage-Differential-Probe-Instruction-Manual-ZH-CN-077054301.pdf (accessed on 18 April 2022).

- PEM. Available online: http://www.pemuk.com/Userfiles/CWT/cwt_0318.pdf (accessed on 18 April 2022).

| Energy Transmit Direction | Relationship of High-Voltage Side and Low-Voltage Side | Working Mode |

|---|---|---|

| High-Voltage Side to Low-Voltage Side | VL < VH/2 | Buck, 0 < D < 0.5 |

| High-Voltage Side to Low-Voltage Side | VL > VH/2 | Buck, 0.5 < D < 1 |

| Low-Voltage Side to High-Voltage Side | VL < VH/2 | Boost, 0.5 < D < 1 |

| Low-Voltage Side to High-Voltage Side | VL > VH/2 | Boost, 0 < D < 0.5 |

| Working Mode | Active IGBT | Reverse Recovery FWD | Commutation Paths |

|---|---|---|---|

| BUCK, 0 < D < 0.5 | V1 | V4 | CDC_LINK-V1-CFLY-V4 |

| V2 | V3 | CFLY-V2-V3 | |

| BUCK, 0.5 < D < 1 | V1 | V4 | CDC_LINK-V1-CFLY-V4 |

| V2 | V3 | CFLY-V2-V3 | |

| BOOST, 0 < D < 0.5 | V4 | V1 | CDC_LINK-V1-CFLY-V4 |

| V3 | V2 | CFLY-V2-V3 | |

| BOOST, 0.5 < D < 1 | V4 | V1 | CDC_LINK-V1-CFLY-V4 |

| V3 | V2 | CFLY-V2-V3 |

| LA | FLY+ | FLY− | |

| LA | 19.00 nH | −2.29 nH | −9.78 nH |

| FLY+ | −2.29 nH | 46.17 nH | −29.95 nH |

| FLY− | −9.78 nH | −29.95 nH | 42.73 nH |

| FLY+ | FLY− | H+ | CC | H− | |

| FLY+ | 44.57 nH | −29.13 nH | −4.86 nH | −0.07 nH | −3.78 nH |

| FLY− | −29.13 nH | 42.82 nH | 7.11 nH | 0.04 nH | −10.58 nH |

| H+ | −4.86 nH | 7.11 nH | 83.89 nH | −0.09 nH | −79.38 nH |

| CC | −0.07 nH | 0.04 nH | −0.09 nH | 2.32 nH | −1.54 nH |

| H− | −3.78 nH | −10.58 nH | −79.38 nH | −1.54 nH | 108.64 nH |

| Capacitor | Double-Pulse Test Method | Impedance Analysis at 1.22 MHz | Resonance Method |

|---|---|---|---|

| Flying capacitor | 19.33 nH | 20.3 nH | 42.8 nH |

| DC-link capacitor | 22.24 nH | 23.22 nH | 54.8 nH |

| Active Switch | Gate Signal of V1 | Gate Signal of V2 | Gate Signal of V3 | Gate Signal of V4 |

|---|---|---|---|---|

| FC charge | On | Off | Off | On |

| V1 | Double pulse | Off | Off | Off |

| V2 | Off | Double pulse | Off | Of |

| V3 | Off | Off | Double pulse | Off |

| V4 | Off | Off | Off | Double pulse |

| Device under Test | Ppk_on (kW) | Eon (mJ) | Ppk_off (kW) | Eoff (mJ) | Ppk_rr (kW) | Err (mJ) |

|---|---|---|---|---|---|---|

| V1 (D < 0.5) | 1052 | 455 | 1540 | 592 | 628 | 189 |

| V1 (0.5 < D < 1) | 1050 | 457 | 1537 | 591 | 631 | 191 |

| V2 (D < 0.5) | 1215 | 487 | 1537 | 560 | 560 | 151 |

| V2 (0.5 < D < 1) | 1210 | 492 | 1543 | 567 | 566 | 157 |

| Device under Test | Ppk_on (kW) | Eon (mJ) | Ppk_off (kW) | Eoff (mJ) | Ppk_rr (kW) | Err (mJ) |

|---|---|---|---|---|---|---|

| V1 (D < 0.5) | 1052 | 455 | 1540 | 592 | 628 | 189 |

| V2 (D < 0.5) | 1215 | 487 | 1537 | 560 | 560 | 151 |

| V3 (D < 0.5) | 1219 | 483 | 1529 | 558 | 556 | 147 |

| V4 (D < 0.5) | 1048 | 458 | 1537 | 590 | 631 | 191 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Liu, H.; Xie, S.; Dou, Z.; Qi, Y.; Liu, F.; Tan, Y. Commutation Behavior and Stray Inductance Analysis of a FC-3L-BDC Phase-Leg PEBB. Energies 2022, 15, 9651. https://doi.org/10.3390/en15249651

Liu H, Xie S, Dou Z, Qi Y, Liu F, Tan Y. Commutation Behavior and Stray Inductance Analysis of a FC-3L-BDC Phase-Leg PEBB. Energies. 2022; 15(24):9651. https://doi.org/10.3390/en15249651

Chicago/Turabian StyleLiu, Haitao, Shunmeng Xie, Zechun Dou, Yu Qi, Feng Liu, and Yifan Tan. 2022. "Commutation Behavior and Stray Inductance Analysis of a FC-3L-BDC Phase-Leg PEBB" Energies 15, no. 24: 9651. https://doi.org/10.3390/en15249651

APA StyleLiu, H., Xie, S., Dou, Z., Qi, Y., Liu, F., & Tan, Y. (2022). Commutation Behavior and Stray Inductance Analysis of a FC-3L-BDC Phase-Leg PEBB. Energies, 15(24), 9651. https://doi.org/10.3390/en15249651