Temporal Verification of Relay-Based Railway Traffic Control Systems Using the Integrated Model of Distributed Systems

Abstract

1. Introduction

- The graphic formalism for modeling, having the same semantics as the algebraic model for verification, so there is no need to translate from the description of the system to the verification language [9];

- A limited set of examined features, but verified automatically, without specifying temporal formulas; these are deadlocks and termination;

- Finding partial deadlocks and termination concerning parts of the system or even its individual elements; while the rest of the system may not experience the effects of partial deadlocks/termination, most verifiers find only total deadlocks/termination, and the user has to ask for partial properties by formulating appropriate temporal formulas;

- Fairness of verification is a little-known feature among non-specialists; however, most verifiers are unfair or weakly fair, which can lead to the detection of non-existent deadlocks [10].

2. Related Work

- Specification in languages specific for the verifier rather than a graphical form convenient for the designer;

- Strong fairness of verification (weak fairness or no fairness leads to the possibility of finding false deadlocks [10]).

3. The Study

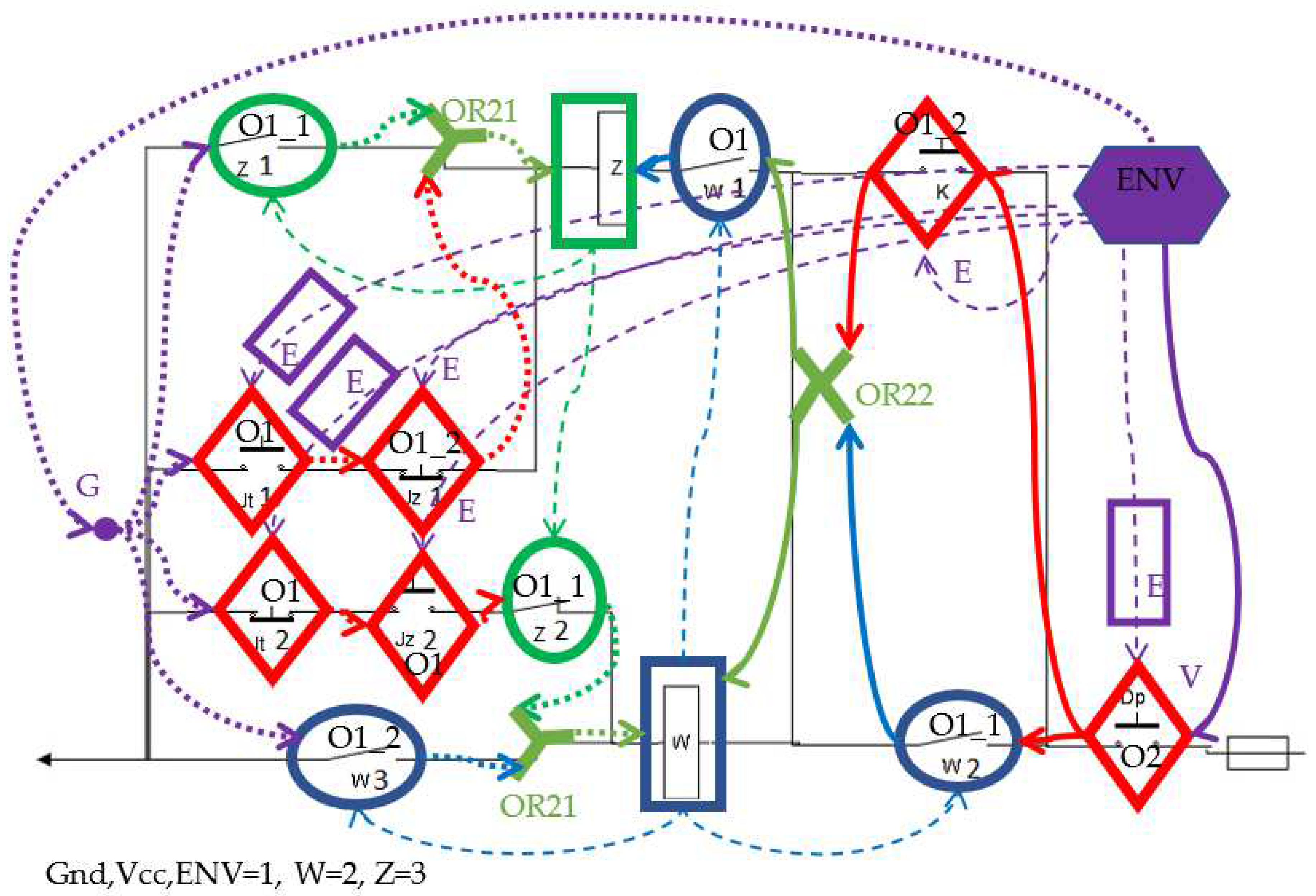

3.1. Line Block Eap

3.2. The Checked Fragment of the System

4. Temporal Verification

4.1. Verification Tools: IMDS/Dedan

- Testing correct operation and the correct sequence of input signals: will the system inevitably reach the predicted final state, going through all the required states beforehand?

- The introduction of damage and the correct sequence of input signals: whether the system does not reach the final state, but also does not pass through dangerous states?

- Checking the correct system and the incorrect sequence of input signals, does the system not reach the final state, but also does not go through dangerous states?

- Of course, the required and unsafe states must also be defined, which will be discussed later.

4.2. IMDS Formalism

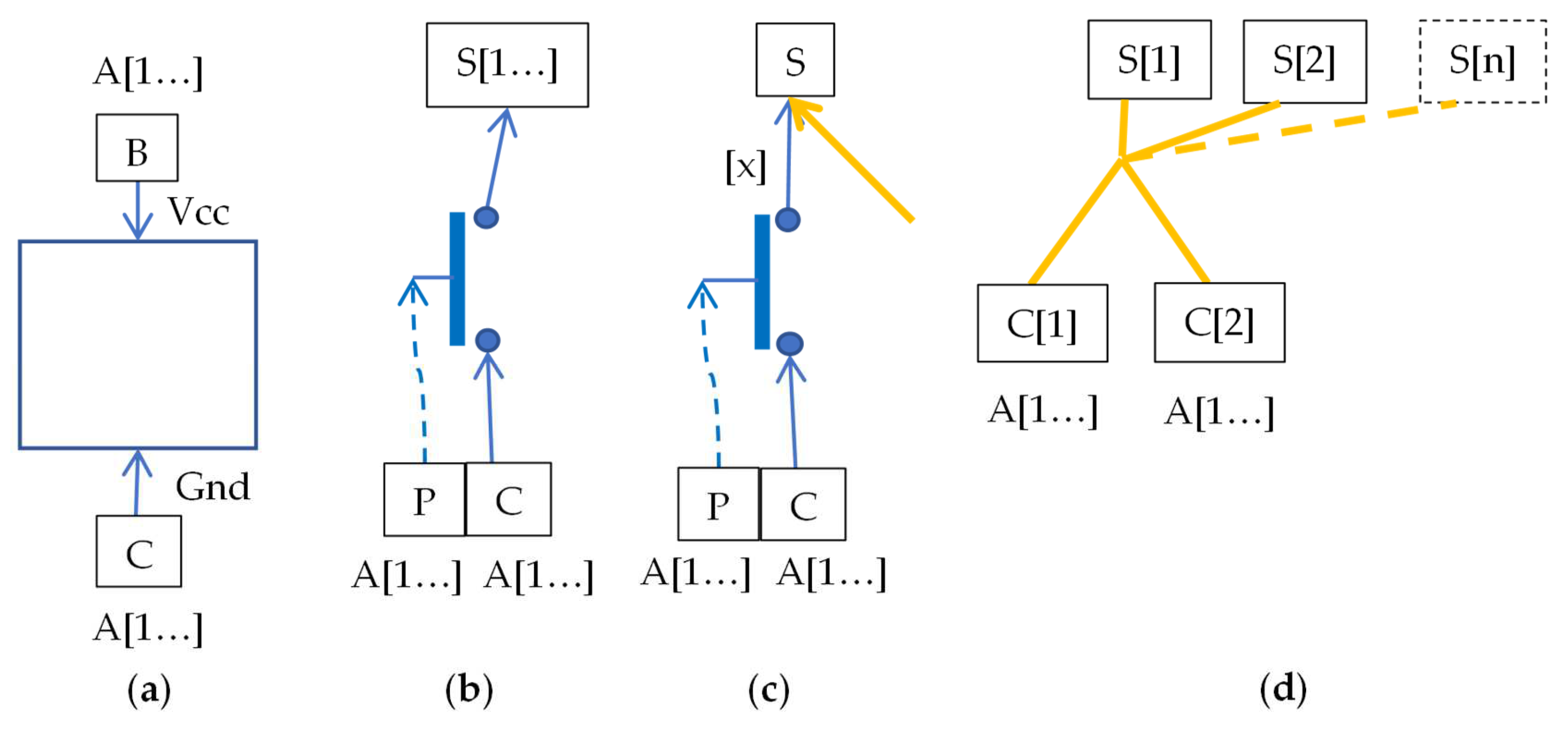

4.3. DA3 Graphical Notation

5. Verification

- DT(s), s∈S — for a server s, the formula is true in every configuration T, for which there is a message of some agent and directed to server s, i.e., ∃p∈P,p = (a,s′,r) p∈T ∧ s = s′,

- ET(s), s∈S — for a server s, the formula is true in every configuration T, for which at least one action is enabled on the server s, i.e., ∃λ∈Λ,λ = (((a,s′,r),(s′,v)),((a,s″,r″),(s′,v′))) (a,s′,r)∈T ∧ (s′,v)∈T ∧ s = s′.

- DT(a), a∈A—for an agent a, the formula is true in every configuration T, in which a message of the agent a is present, i.e., ∃p∈P,p = (a′,s,r) p∈T ∧ a = a′, that is, the agent did not terminate.

- ET(a), a∈A — for an agent a, the formula is true in every configuration T, in which at least one action is enabled with the participation of the agent a, i.e., ∃λ∈Λ,λ = (((a′,s,r),(s,v)),((a′,s′,r′),(s,v′))) (a′,s,r)∈T ∧ (s,v)∈T ∧ a = a′.

- FT(a), a∈A—for an agent a, the formula is true in every configuration T in which no message of the agent a is present, i.e., ∀m∈T,m = (a′,s,r) a ≠ a′.

5.1. Modeling System Elements

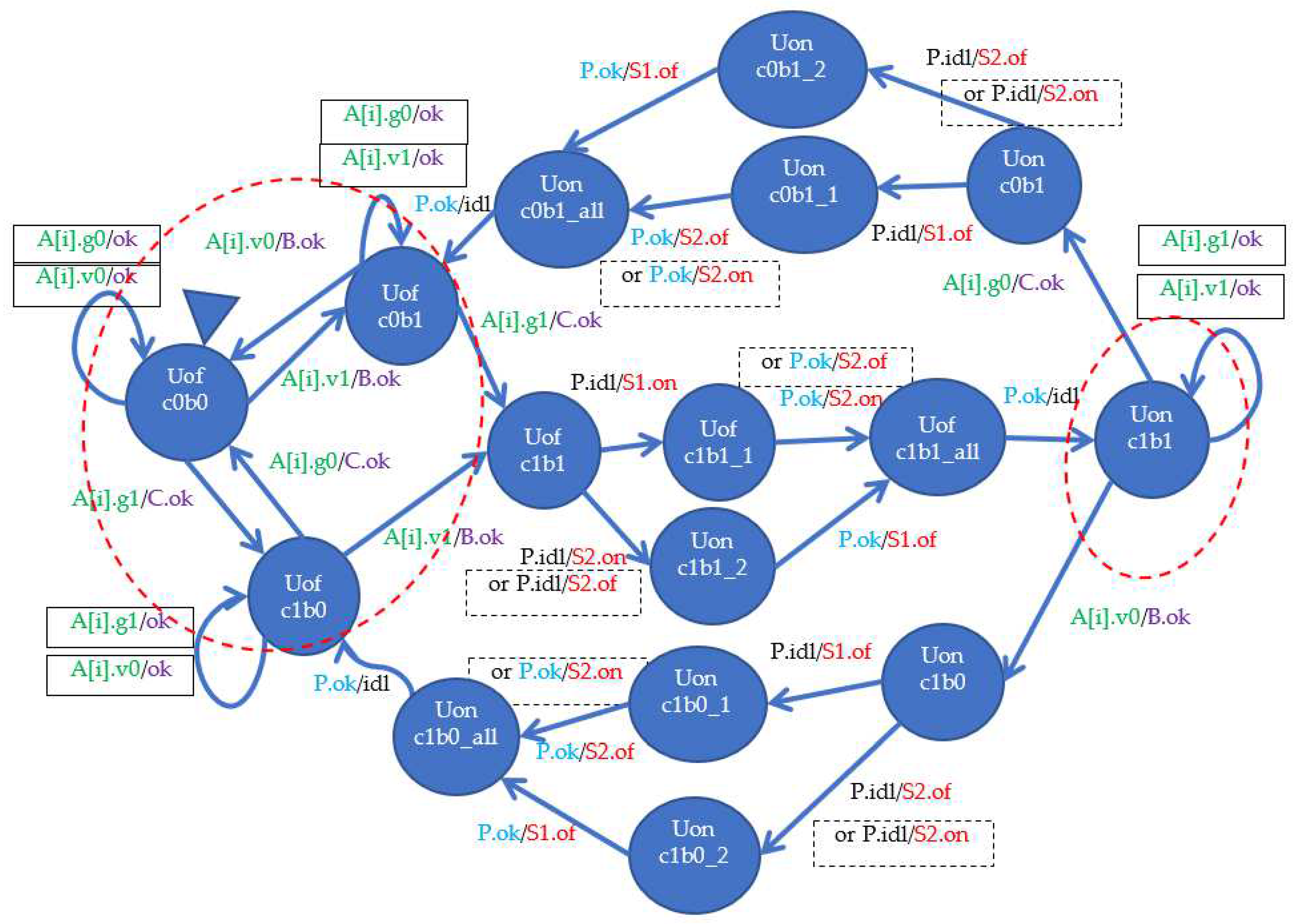

5.2. The Course of the Verification

5.2.1. Basic Checking

5.2.2. Unexpected Error

5.2.3. Correct Sequence

5.2.4. Element Failure—Short Circuit between Input and Output

5.2.5. Damage to the Element—Permanent Opening

5.2.6. Incorrect Sequence of Actions Controlled from the Environment

6. Conclusions and Further Work

- Specification of circuit elements using a graphical form of distributed automata DA3. In a case of safety checking in the occurrence of faults, specification of faulty elements in the same fashion.

- Specification of observer agents that investigate the required/unwanted changes of states of individual elements.

- The proving of the correctness of the system is done by the inevitability of reaching their termination by the specified agents. This feature is checked automatically. Termination is partial in this case (which is also a rare feature among verifiers) because other agents may be in a “technical” deadlock state.

- Checking inevitable termination in the case of correct termination (required property), or possible termination in the case of safety checking of a faulty circuit or faulty input sequence (unwanted property). Finding partial deadlocks, causing the lack of termination, discovers malfunctioning elements or subsystems while the rest of the circuit can work properly.

- Graphical modeling of systems is rare. Among the works on relay systems, only [12,14] use UML state diagrams, and [16] schematic diagrams. Both of these approaches, however, require translation into a Kripke structure, which may subtly influence the semantics of the model. The remaining works cited use little readable switch tables [15] or text input in the form of complex formulas or a domain-specific language or B method [17]. In our approach, the design of element models takes place directly in the intuitive form of graphical distributed automata, fully compatible with the algebraic model subject to verification. The semantics of both specification methods (graphical and algebraic) are identical, so the specification does not require translation into the verifier’s input data. The same applies to the approaches based on the Uppaal specification [7,18].

- The investigated properties of systems are typically specified using temporal formulas (or ProB verifier formulas [17]). As industrial practice shows, for the vast majority of designers, this is an entry threshold that is (subjectively) difficult to overcome. And it is rarely possible to invite a researcher familiar with temporal logic to permanent cooperation in the checking of systems. Some of the cited works replace temporal formulas with typical, predefined properties that are internally replaced by sentences in temporal logic [15,16]. Instead of temporal formulas examining individual characteristics, we introduce observer automata, which can be easily designed by the user. These automata report that the system has achieved certain states, as shown in this article. A similar approach using Uppaal observers is only shown in [18]. The observer automaton achieves the “deliberate” deadlock state in the event of a system malfunction (primarily in the case of security testing).

- Our original idea is to introduce damaged elements to the library of models. Replacing an element (or several elements) with a damaged one, and subjecting the system to an incorrect sequence of external events, allows for checking whether the system will behave safely in such circumstances. The system should not reach a supported end state in such a situation, but should protect the managed system from a catastrophe, for example, by letting two trains onto the same track. If the system does not behave safely, then again, the possibility of simulating a counterexample on component automata would make it possible to find the reason for this behavior. Demonstrating the safety of the system even in the event of damage may be necessary in the process of its certification.

- A feature that is automatically detected by all verifiers is a total deadlock. Some verifiers detect partial deadlocks, but this requires a specific structure of the system under investigation, or the user specifies an appropriate temporal formula. Our verification method is specific in that it automatically detects partial deadlocks where some components are stuck while others are still working correctly. This allows a broader class of errors to be detected.

- The fairness aspect of the verifier is significant but often overlooked. Most of the verifiers available do not provide fairness at all, or only weak fairness. Among the verifiers used in the cited articles, Spin and Uppaal do not provide strong fairness. NuSMV ensures fairness as long as the user specifies special formulas for each expected fair divergence in the operation of individual automata. The work [10] shows how the lack of strong justice (compassion) can lead to the detection of a non-existent deadlock. The verification algorithm we use as well as the one used in ProB [17] provide strong fairness.

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Eap. Jednoodstępowa (półsamoczynna) Blokada Liniowa Typu Eap-94 [Single-section (semi-automatic) Line Block Type Eap-94]. 2016. Available online: http://www.pphu-mgrot.pl/download/pdf/DTREap-94.pdf (accessed on 28 September 2022). (In Polish).

- IEC62425:2007; Railway Applications—Communication, Signalling and Processing Systems—Safety Related Electronic Systems for Signalling. International Electrotechnical Commission: Geneva, Switzerland, 2007. Available online: https://webstore.iec.ch/publication/7001 (accessed on 28 September 2022).

- EN50129:2018; Railway Applications—Communication, Signalling and Processing Systems—Safety-Related Electronic Systems for Signalling. The European Committee for Standardization (CEN): Brussels, Belgium, 2018. Available online: https://standards.iteh.ai/catalog/standards/clc/f6548cc3-5885-43aa-8654-9e71383b892e/en-50129-2018 (accessed on 28 September 2022).

- EN50126-1:2017; Railway Applications—The Specification and Demonstration of Reliability, Availability, Maintainability and Safety (RAMS)—Part 1: Generic RAMS Process. The European Committee for Standardization (CEN): Brussels, Belgium, 2017. Available online: https://standards.iteh.ai/catalog/standards/clc/e5456892-eb2c-437e-8c4b-91c08007f0b4/en-50126-1-2017 (accessed on 28 September 2022).

- EN50126-2:2017; Railway Applications—The Specification and Demonstration of Reliability, Availability, Maintainability and Safety (RAMS)—Part 2: Systems Approach to Safety. The European Committee for Standardization (CEN): Brussels, Belgium, 2017. Available online: https://standards.iteh.ai/catalog/standards/clc/67bf2fa9-46a2-4460-a907-91b2ac91d7fc/en-50126-2-2017 (accessed on 28 September 2022).

- Li, J. SIL Implementation on Safety Functions in Mass Transit System. Int. J. Math. Eng. Manag. Sci. 2018, 3, 258–270. [Google Scholar] [CrossRef]

- Daskaya, I.; Huhn, M.; Milius, S. Formal Safety Analysis in Industrial Practice. In FMICS 2011: Formal Methods for Industrial Critical Systems; Salaün, G., Schätz, B., Eds.; Springer: Berlin/Heidelberg, Germany, 2011; pp. 68–84. [Google Scholar] [CrossRef]

- Daszczuk, W.B. Specification and Verification in Integrated Model of Distributed Systems (IMDS). Computers 2018, 7, 65. [Google Scholar] [CrossRef]

- Daszczuk, W.B. Graphic modeling in Distributed Autonomous and Asynchronous Automata (DA3). Softw. Syst. Model. 2021, 20, 363–398. [Google Scholar] [CrossRef]

- Daszczuk, W.B. Fairness in Temporal Verification of Distributed Systems. In DepCoS-RELCOMEX 2018: Contemporary Complex Systems and Their Dependability; Zamojski, W., Mazurkiewicz, J., Sugier, J., Walkowiak, T., Kacprzyk, J., Eds.; Springer International Publishing: Cham, Switzerland, 2019; Volume 761, pp. 135–150. [Google Scholar] [CrossRef]

- Ferrari, A.; Magnani, G.; Grasso, D.; Fantechi, A. Model Checking Interlocking Control Tables. In FORMS/FORMAT 2010; Schnieder, E., Tarnai, G., Eds.; Springer: Berlin/Heidelberg, Germany, 2011; pp. 107–115. [Google Scholar] [CrossRef]

- Fantechi, A. Distributing the Challenge of Model Checking Interlocking Control Tables. In ISoLA 2012: Leveraging Applications of Formal Methods, Verification and Validation. Applications and Case Studies; Margaria, T., Steffen, B., Eds.; Springer: Berlin/Heidelberg, Germany, 2012; pp. 276–289. [Google Scholar] [CrossRef]

- Haxthausen, A.E.; Le Bliguet, M.; Kjær, A.A. Modelling and Verification of Relay Interlocking Systems. In Monterey Workshop 2008: Foundations of Computer Software. Future Trends and Techniques for Development; Choppy, C., Sokolsky, O., Eds.; Springer: Berlin/Heidelberg, Germany, 2010; pp. 141–153. [Google Scholar] [CrossRef]

- Haxthausen, A.E.; Peleska, J.; Pinger, R. Applied Bounded Model Checking for Interlocking System Designs. In SEFM 2013: Software Engineering and Formal Methods; Counsell, S., Núñez, M., Eds.; Springer International Publishing: Cham, Switzerland, 2014; Volume 8368, pp. 205–220. [Google Scholar] [CrossRef]

- Haxthausen, A.E.; Østergaard, P.H. On the Use of Static Checking in the Verification of Interlocking Systems. In ISoLA 2016: Leveraging Applications of Formal Methods, Verification and Validation: Discussion, Dissemination, Applications; Margaria, T., Steffen, B., Eds.; Springer International Publishing: Cham, Switzerland, 2016; pp. 266–278. [Google Scholar] [CrossRef]

- Amendola, A.; Becchi, A.; Cavada, R.; Cimatti, A.; Ferrando, A.; Pilati, L.; Scaglione, G.; Tacchella, A.; Zamboni, M. NORMA: A tool for the analysis of Relay-based Railway Interlocking Systems. In TACAS 2022: Tools and Algorithms for the Construction and Analysis of Systems; Fisman, D., Rosu, G., Eds.; Springer: Cham, Switzerland, 2022; pp. 125–142. [Google Scholar] [CrossRef]

- de Almeida Pereira, D.I.; Deharbe, D.; Perin, M.; Bon, P. B-Specification of Relay-Based Railway Interlocking Systems Based on the Propositional Logic of the System State Evolution. In RSSRail 2019: Reliability, Safety, and Security of Railway Systems. Modelling, Analysis, Verification, and Certification; Collart-Dutilleul, S., Lecomte, T., Romanovsky, A., Eds.; Springer: Cham, Switzerland, 2019; pp. 242–258. [Google Scholar] [CrossRef]

- Lahtine, J. Model Checking Timed Safety Instrumented Systems; Helsinki University of Technology, Department of Information and Computer Science: Helsinki, Finland, 2008; Available online: https://aaltodoc.aalto.fi/handle/123456789/874 (accessed on 28 September 2022).

- Behrmann, G.; David, A.; Larsen, K.G.; Pettersson, P.; Yi, W. Developing UPPAAL over 15 years. Softw. Pract. Exp. 2011, 41, 133–142. [Google Scholar] [CrossRef]

- Sabatier, D. Using Formal Proof and B Method at System Level for Industrial Projects. In RSSRail 2016: Reliability, Safety, and Security of Railway Systems. Modelling, Analysis, Verification, and Certification; Lecomte, T., Pinger, R., Romanovsky, A., Eds.; Springer: Cham, Switzerland, 2016; Volume 9707, pp. 20–31. [Google Scholar] [CrossRef]

- Comptier, M.; Deharbe, D.; Perez, J.M.; Mussat, L.; Pierre, T.; Sabatier, D. Safety Analysis of a CBTC System: A Rigorous Approach with Event-B. In RSSRail 2017: Reliability, Safety, and Security of Railway Systems. Modelling, Analysis, Verification, and Certification; Fantechi, A., Lecomte, T., Romanovsky, A., Eds.; Springer: Cham, Switzerland, 2017; Volume 10598, pp. 148–159. [Google Scholar] [CrossRef]

- James, P.; Moller, F.; Nguyen, H.N.; Roggenbach, M.; Schneider, S.; Treharne, H. Techniques for modelling and verifying railway interlockings. Int. J. Softw. Tools Technol. Transf. 2014, 16, 685–711. [Google Scholar] [CrossRef]

- Idani, A.; Ledru, Y.; Ait Wakrime, A.; Ben Ayed, R.; Bon, P. Towards a Tool-Based Domain Specific Approach for Railway Systems Modeling and Validation. In RSSRail 2019: Reliability, Safety, and Security of Railway Systems. Modelling, Analysis, Verification, and Certification; Collart-Dutilleul, S., Lecomte, T., Romanovsky, A., Eds.; Springer: Cham, Switzerland, 2019; Volume 11495, pp. 23–40. [Google Scholar] [CrossRef]

- Fantechi, A.; Gori, G.; Haxthausen, A.E.; Limbrée, C. Compositional Verification of Railway Interlockings: Comparison of Two Methods. In RSSRail 2022: Reliability, Safety, and Security of Railway Systems. Modelling, Analysis, Verification, and Certification; Collart-Dutilleul, S., Haxthausen, A.E., Lecomte, T., Eds.; Springer: Cham, Switzerland, 2022; Volume 13294, pp. 3–19. [Google Scholar] [CrossRef]

- Iliasov, A.; Laibinis, L.; Taylor, D.; Lopatkin, I.; Romanovsky, A. Safety Invariant Verification that Meets Engineers’ Expectations. In RSSRail 2022: Reliability, Safety, and Security of Railway Systems. Modelling, Analysis, Verification, and Certification; Collart-Dutilleul, S., Haxthausen, A.E., Lecomte, T., Eds.; Springer: Cham, Switzerland, 2022; Volume 13294, pp. 20–31. [Google Scholar] [CrossRef]

- Kamburjan, E.; Hähnle, R. Deductive Verification of Railway Operations. In RSSRail 2017: Reliability, Safety, and Security of Railway Systems. Modelling, Analysis, Verification, and Certification; Fantechi, A., Lecomte, T., Romanovsky, A., Eds.; Springer: Cham, Switzerland, 2017; Volume 10598, pp. 131–147. [Google Scholar] [CrossRef]

- Sun, P.; Collart-dutilleul, S.; Bon, P. A model pattern of railway interlocking system by Petri nets. In Proceedings of the 2015 International Conference on Models and Technologies for Intelligent Transportation Systems (MT-ITS), Budapest, Hungary, 3–5 June 2015; pp. 442–449. [Google Scholar] [CrossRef]

- Carrasquel, J.C.; Morales, A.; Villapol, M.E. Prosega/CPN: An extension of CPN Tools for Automata-based Analysis and System Verification. Proc. Inst. Syst. Program. RAS 2018, 30, 107–128. [Google Scholar] [CrossRef] [PubMed]

- Parillaud, C.; Fonteneau, Y.; Belmonte, F. Interlocking Formal Verification at Alstom Signalling. In RSSRail 2019: Reliability, Safety, and Security of Railway Systems. Modelling, Analysis, Verification, and Certification; Collart-Dutilleul, S., Lecomte, T., Romanovsky, A., Eds.; Springer: Cham, Switzerland, 2019; Volume 11495, pp. 215–225. [Google Scholar] [CrossRef]

- Han, X.; Tang, T.; Lv, J.; Wang, H. Failure Analysis of Chinese Train Control System Level 3 Based on Model Checking. In RSSRail 2016: Reliability, Safety, and Security of Railway Systems. Modelling, Analysis, Verification, and Certification; Lecomte, T., Pinge, R., Romanovsky, A., Eds.; Springer: Cham, Switzerland, 2016; Volume 9707, pp. 95–105. [Google Scholar] [CrossRef]

- Limbrée, C.; Cappart, Q.; Pecheur, C.; Tonetta, S. Verification of Railway Interlocking—Compositional Approach with OCRA. In RSSRail 2016: Reliability, Safety, and Security of Railway Systems. Modelling, Analysis, Verification, and Certification; Lecomte, T., Pinger, R., Romanovsky, A., Eds.; Springer: Cham, Switzerland, 2016; Volume 9707, pp. 134–149. [Google Scholar] [CrossRef]

- Halchin, A.; Feliachi, A.; Singh, N.K.; Ait-Ameur, Y.; Ordioni, J. B-PERFect. Applying the PERF Approach to B Based System Developments. In RSSRail 2017: Reliability, Safety, and Security of Railway Systems. Modelling, Analysis, Verification, and Certification; Fantechi, A., Lecomte, T., Romanovsky, A., Eds.; Springer: Cham, Switzerland, 2017; Volume 10598, pp. 160–172. [Google Scholar] [CrossRef]

- Theeg, G.; Vlasenko, S. Railway Signalling & Interlocking: International Compendium, 3rd ed.; PMC Media House: Bingen am Rhein, Germany, 2019; ISBN 3962451692.

- Daszczuk, W.B. Asynchronous Specification of Production Cell Benchmark in Integrated Model of Distributed Systems. In Intelligent Methods and Big Data in Industrial Applications; Bembenik, R., Skonieczny, L., Protaziuk, G., Kryszkiewicz, M., Rybinski, H., Eds.; Springer International Publishing: Cham, Switzerland, 2019; Volume 40, pp. 115–129. [Google Scholar] [CrossRef]

- Daszczuk, W.B. 2-Vagabonds: Non-exhaustive verification algorithm. In Integrated Model of Distributed Systems (Studies in Computational Intelligence); Springer Nature: Cham, Switzerland, 2020; Volume 817, p. 256. [Google Scholar] [CrossRef]

- Baier, C.; Katoen, J.-P. Principles of Model Checking; MIT Press: Cambridge, MA, USA, 2008; ISBN 9780262026499. [Google Scholar]

- Daszczuk, W.B. Evaluation of temporal formulas based on “Checking By Spheres”. In Proceedings of the Proceedings Euromicro Symposium on Digital Systems Design, Warsaw, Poland, 4–6 September 2001; pp. 158–164. [Google Scholar] [CrossRef]

- EN50205:2002; Relays with Forcibly Guided (Mechanically Linked) Contacts. The European Committee for Standardization (CEN): Brussels, Belgium, 2002. Available online: https://standards.iteh.ai/catalog/standards/clc/f50401a3-3a46-4da5-8d81-3770892193d6/en-50205-2002 (accessed on 28 September 2022).

- UIC736:4ED-2004; Signalling Relays. International Union of Railways: Paris, France, 2004. Available online: https://www.normadoc.com/english/uic-736-2004-06.html (accessed on 28 September 2022).

- IEC62912:2015; Railway Applications—Direct Current Signalling Monostable Relays of Type N and Type C. International Electrotechnical Commission: Geneva, Switzerland, 2015. Available online: https://standards.iteh.ai/catalog/standards/iec/001b4732-c217-40bb-8798-530774bf50f5/iec-62912-2015 (accessed on 28 September 2022).

- IEC62912-2:2019; Railway Applications—Direct Current Signalling Monostable Relays—Part 2: Spring Type Relays. International Electrotechnical Commission: Geneva, Switzerland, 2019. Available online: https://standards.iteh.ai/catalog/standards/iec/7f8df920-e205-4bc4-8c49-d069fb31b4ad/iec-62912-2-2019 (accessed on 28 September 2022).

- Manna, Z.; Pnueli, A. The Temporal Logic of Reactive and Concurrent Systems; Springer: New York, NY, USA, 1992. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Karolak, J.; Daszczuk, W.B.; Grabski, W.; Kochan, A. Temporal Verification of Relay-Based Railway Traffic Control Systems Using the Integrated Model of Distributed Systems. Energies 2022, 15, 9041. https://doi.org/10.3390/en15239041

Karolak J, Daszczuk WB, Grabski W, Kochan A. Temporal Verification of Relay-Based Railway Traffic Control Systems Using the Integrated Model of Distributed Systems. Energies. 2022; 15(23):9041. https://doi.org/10.3390/en15239041

Chicago/Turabian StyleKarolak, Juliusz, Wiktor B. Daszczuk, Waldemar Grabski, and Andrzej Kochan. 2022. "Temporal Verification of Relay-Based Railway Traffic Control Systems Using the Integrated Model of Distributed Systems" Energies 15, no. 23: 9041. https://doi.org/10.3390/en15239041

APA StyleKarolak, J., Daszczuk, W. B., Grabski, W., & Kochan, A. (2022). Temporal Verification of Relay-Based Railway Traffic Control Systems Using the Integrated Model of Distributed Systems. Energies, 15(23), 9041. https://doi.org/10.3390/en15239041