Hysteresis Based Quasi Fixed Frequency Current Control of Single Phase Full Bridge Grid Integrated Voltage Source Inverter

Abstract

1. Introduction

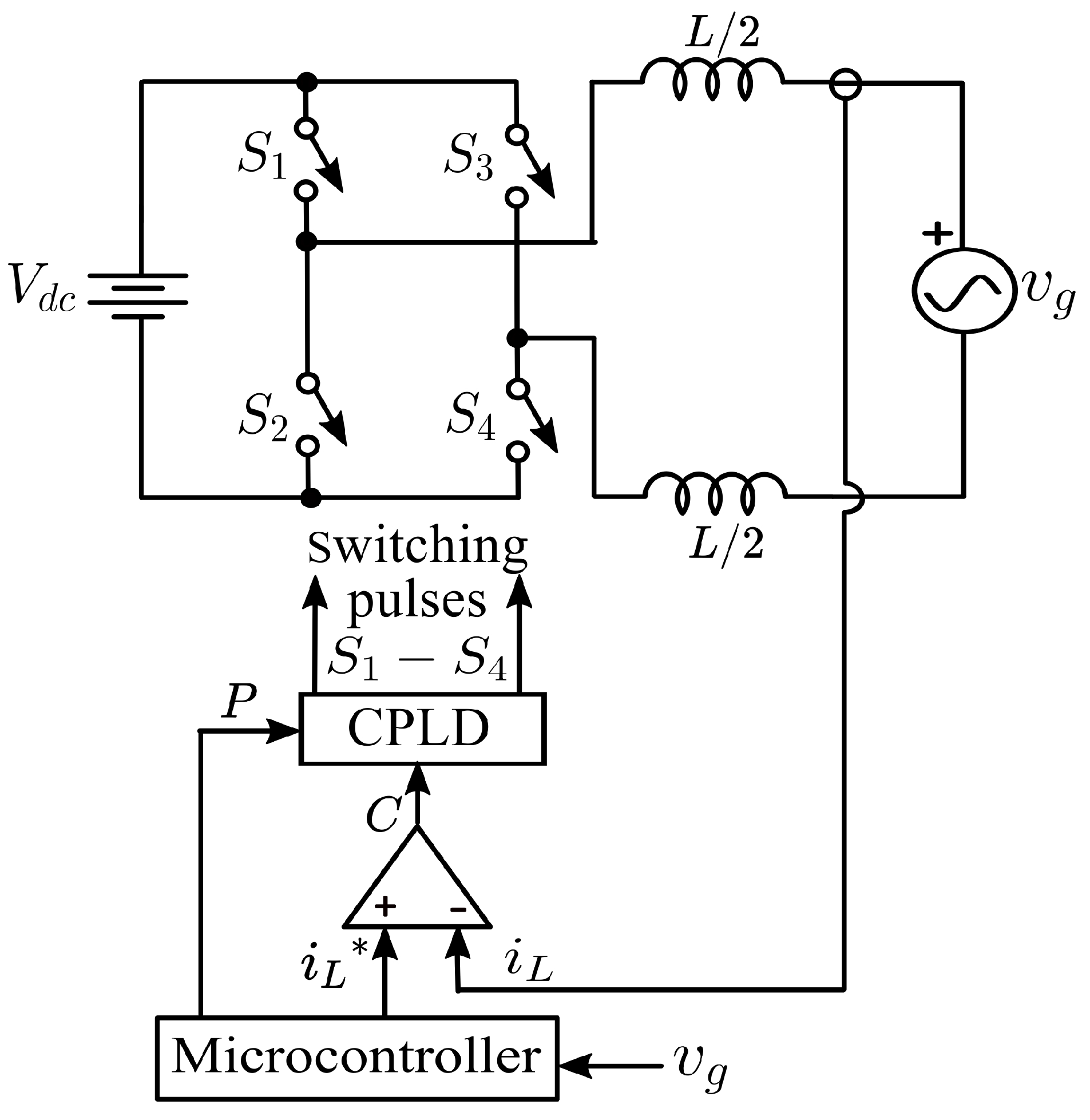

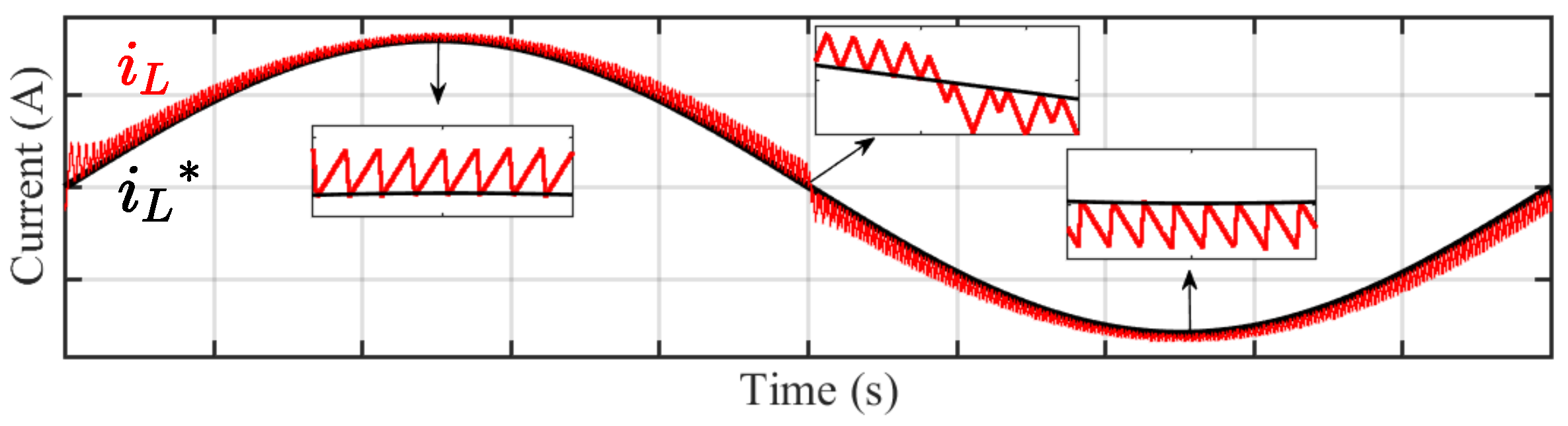

2. Principle of Operation

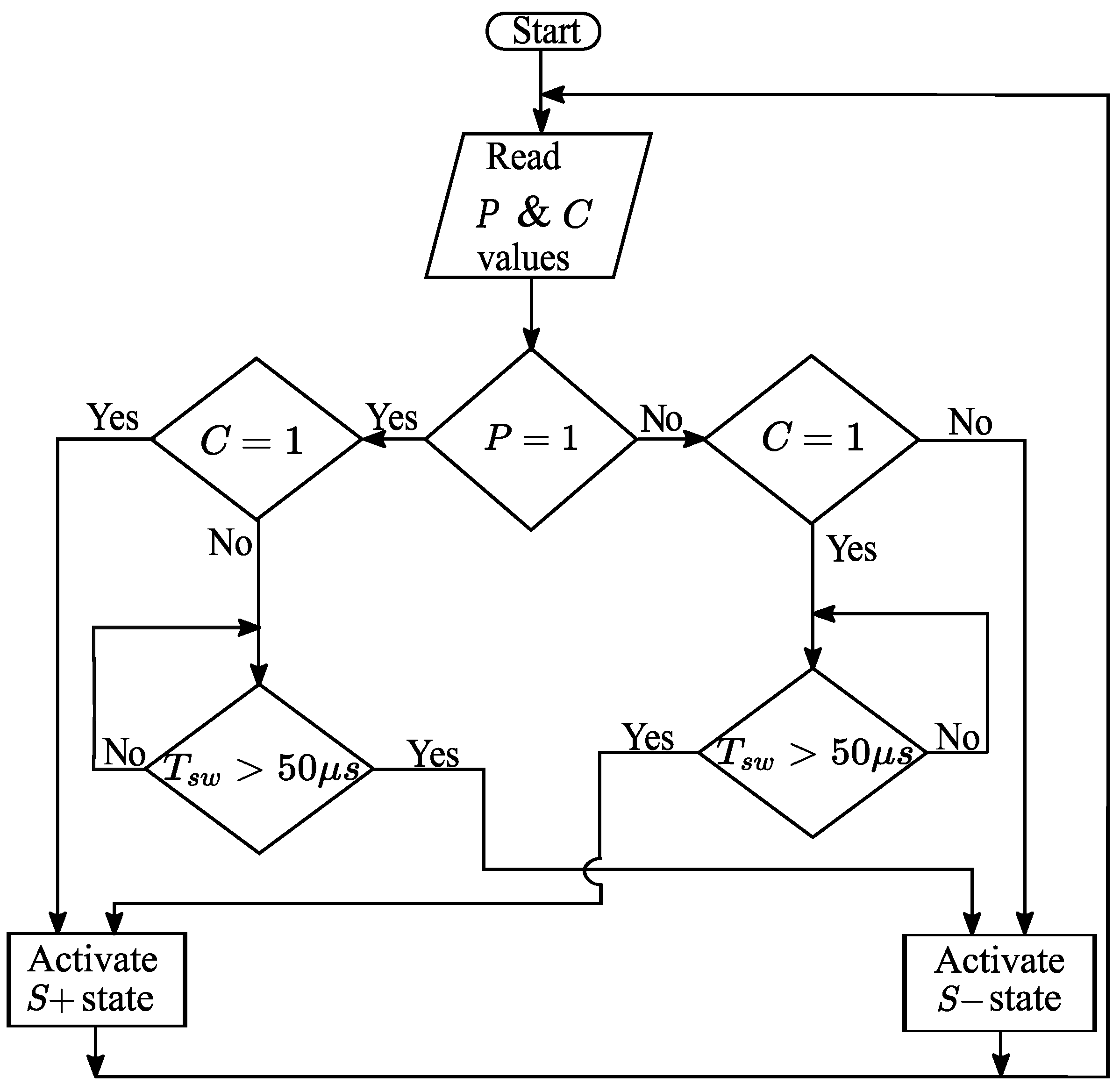

2.1. Switching Logic

2.1.1. Positive Half Cycle

2.1.2. Negative Half Cycle

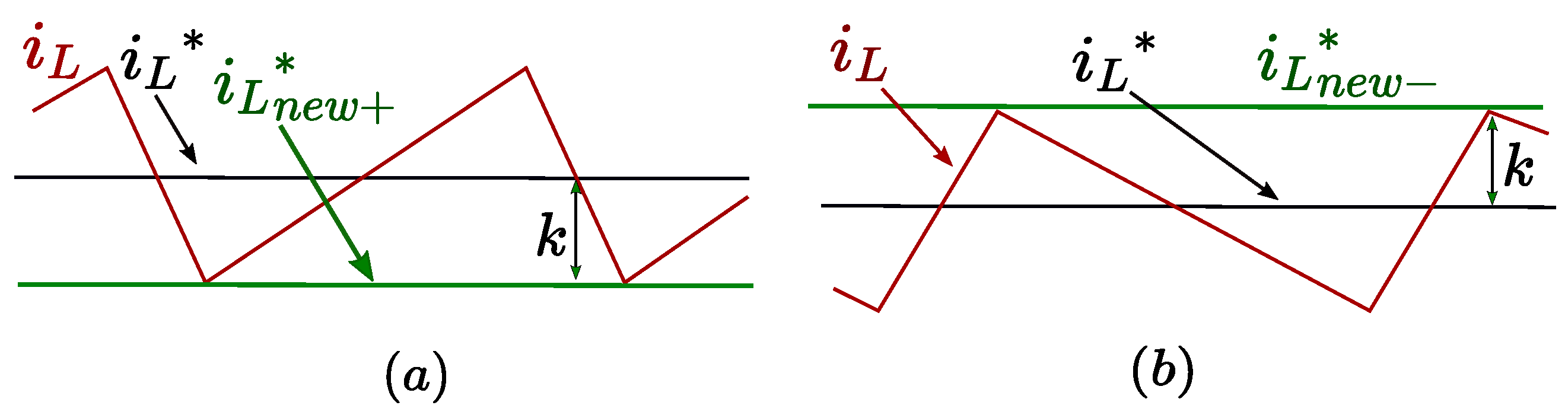

2.2. Reference Correction

3. Simulation Results

3.1. Methods to Correct the DC Offset and Curb the THD

3.1.1. Modifying the Reference Current

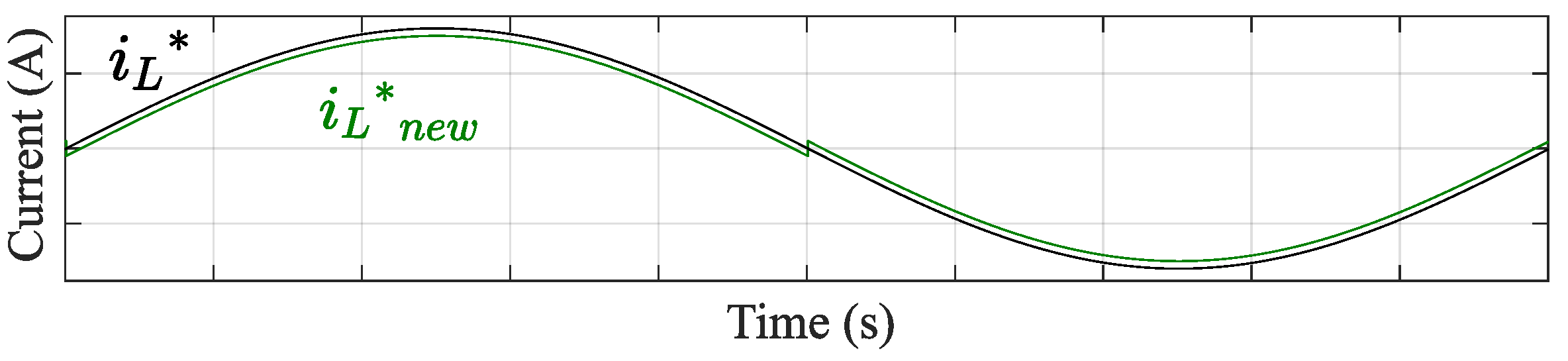

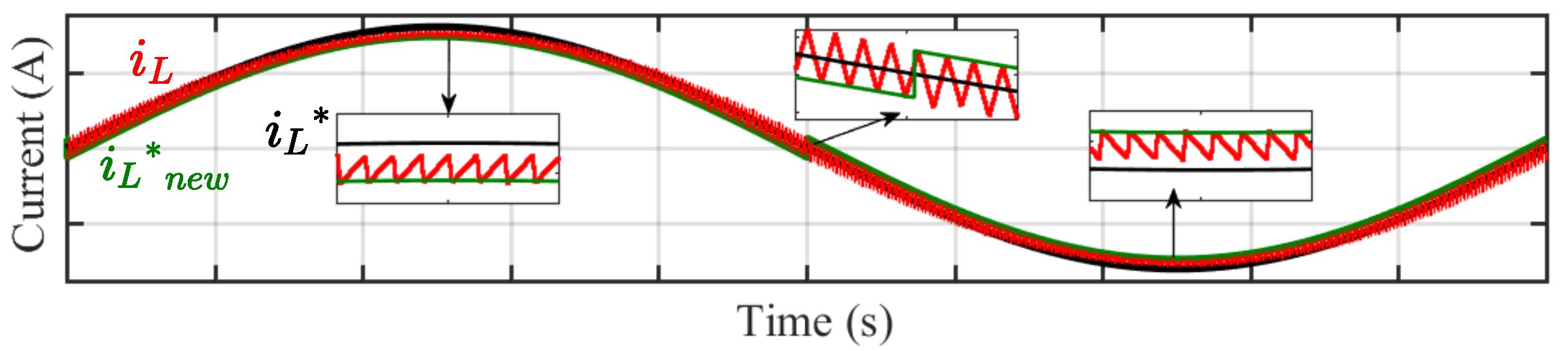

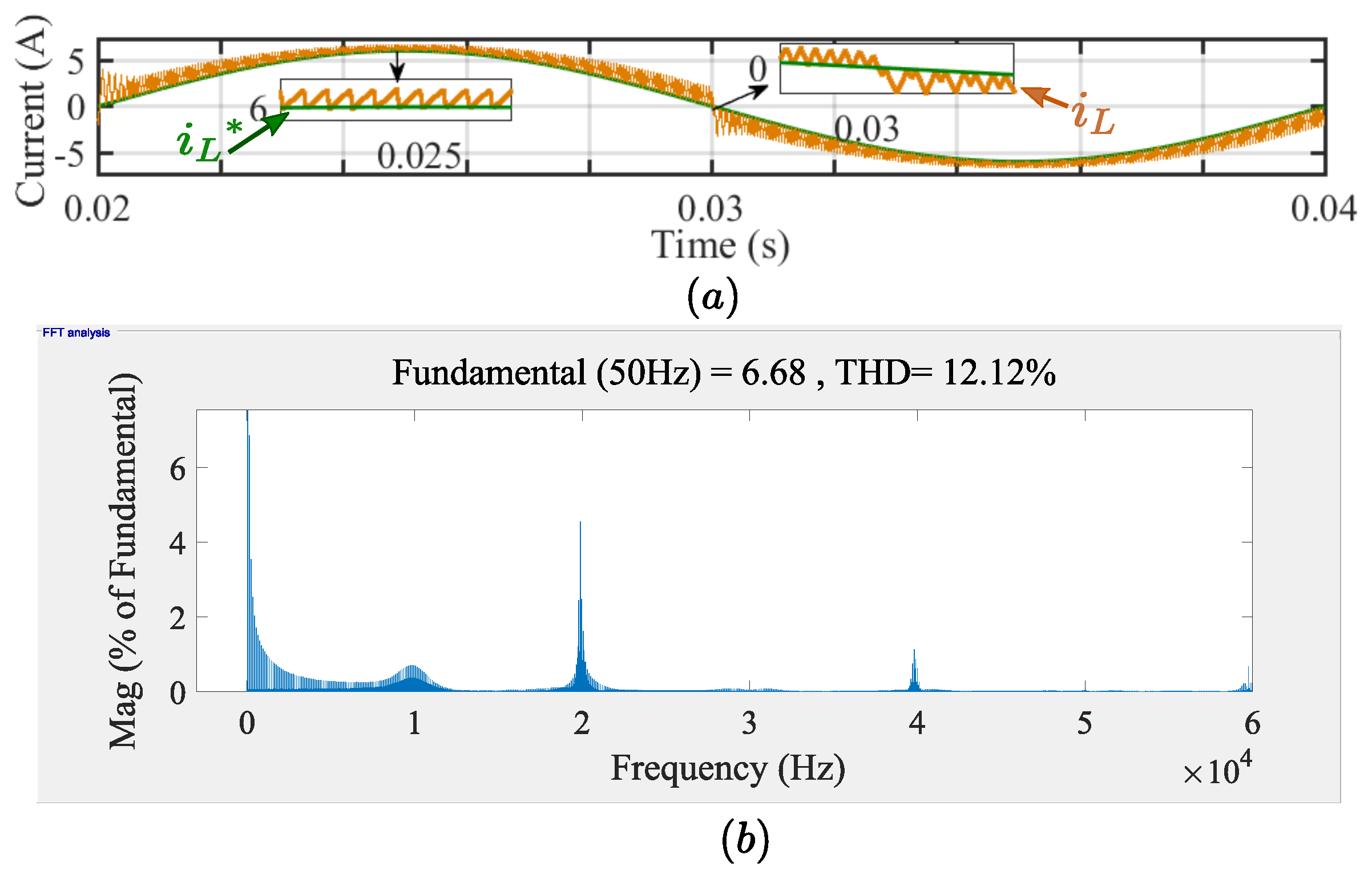

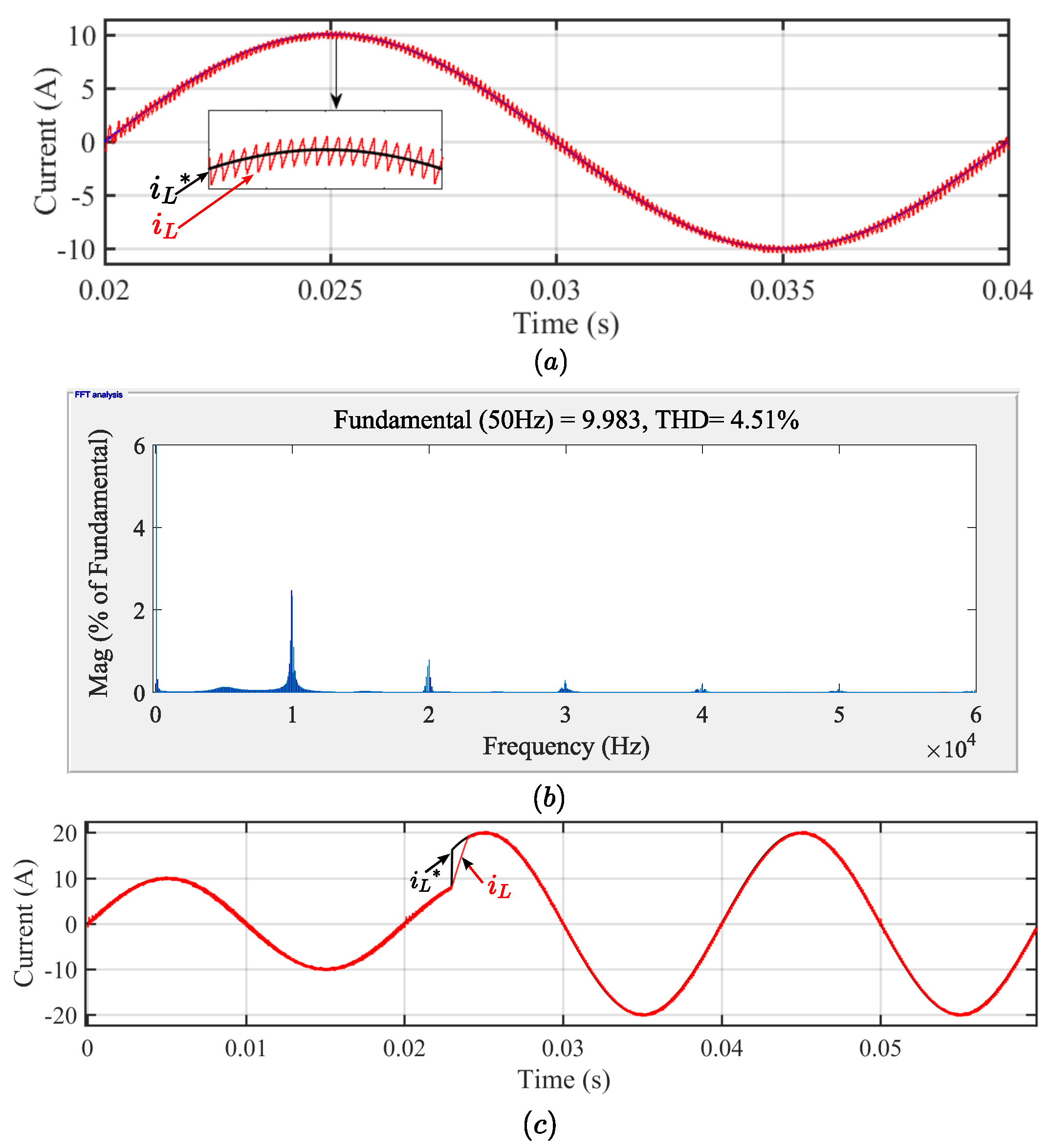

- Fixed offsetThe is modified by the k, equivalent to half the maximum amplitude of inductor current ripple given by (11) and the resulting waveform is in Figure 14a. Here the distortion at the zero-crossing is corrected completely, while the rest of the quarter-wave is over-corrected as observed in the zoomed view of the positive peak shown in Figure 14a. The THD is within the limit as shown in Figure 14b. To remove the DC offset error completely, a variable offset correction is suggested.

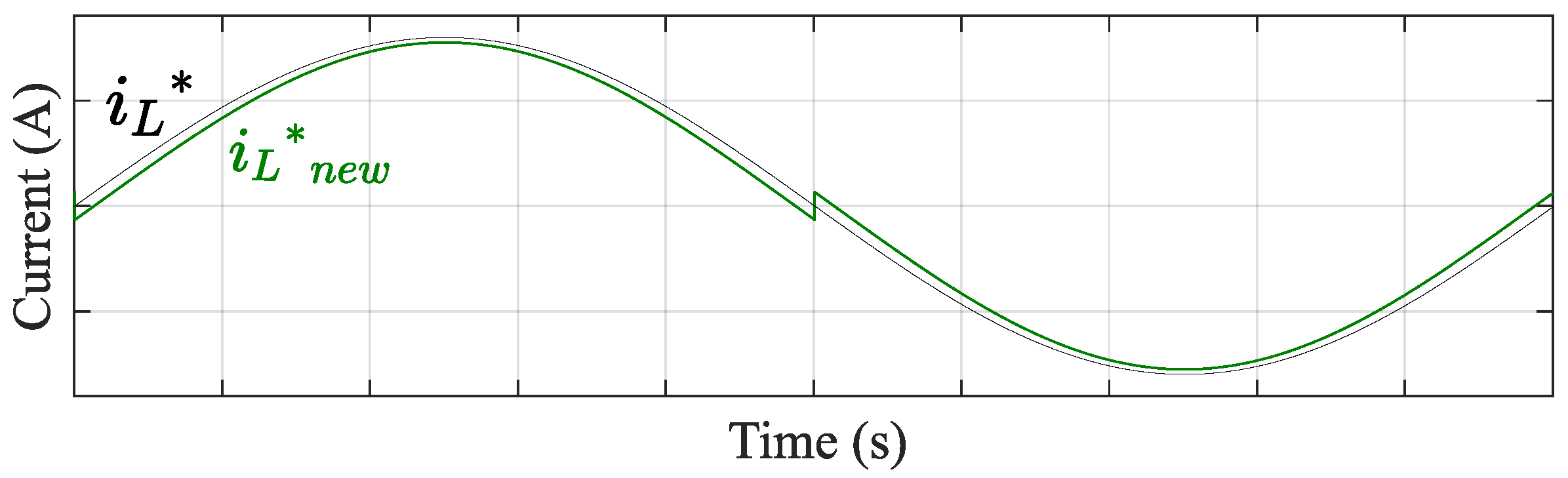

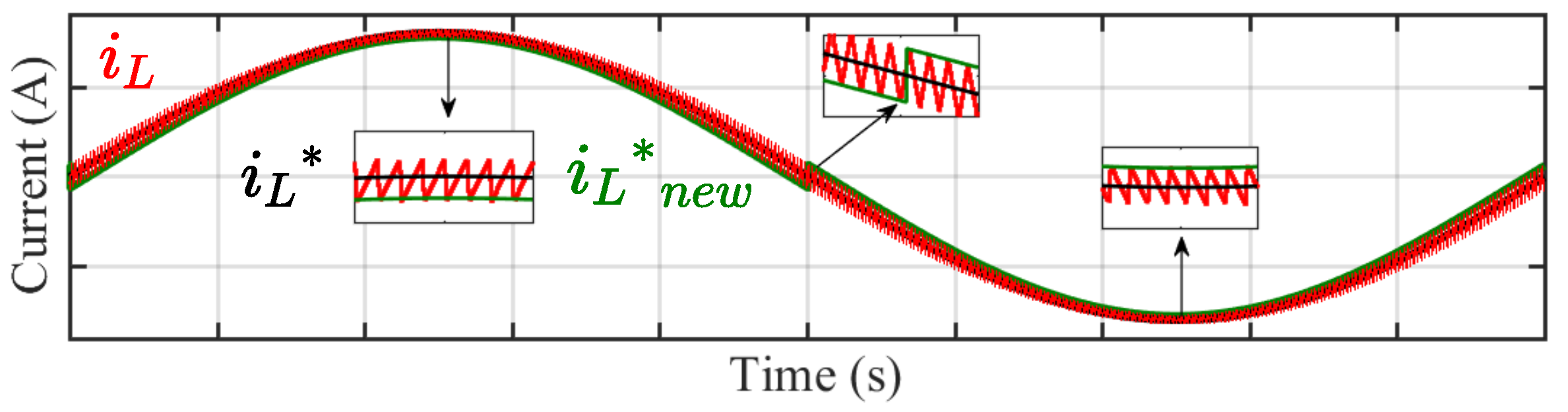

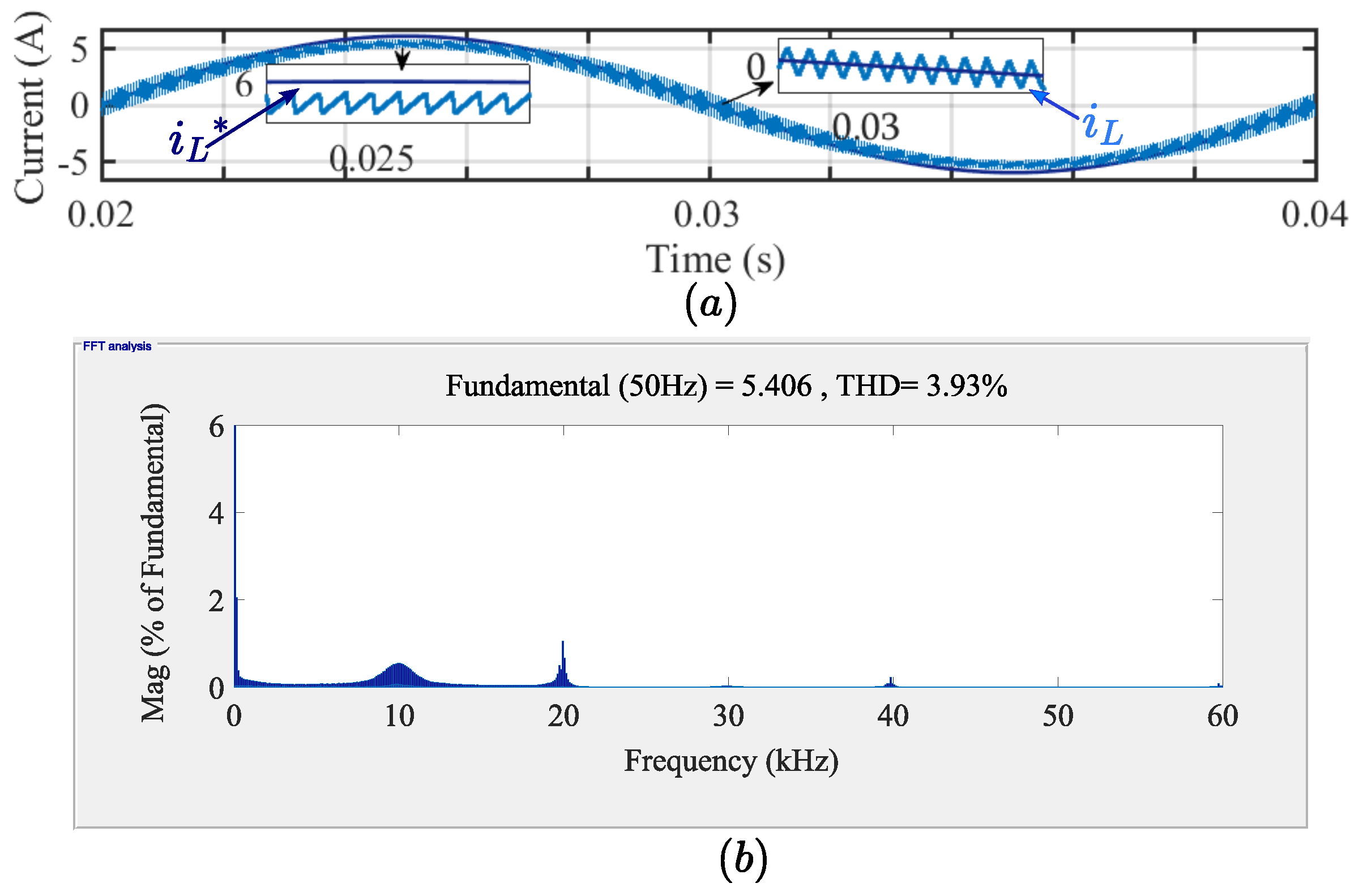

- Variable OffsetFor a given condition, the in (7) varies with the instantaneous values of while the other parameters are kept constant. Hence, the k needed to correct the offset also varies and is half the current ripple at any instant (k = ). Figure 15a shows the waveform corrected by the variable offset, and its frequency spectrum is given in Figure 15b. It shows that the DC offset error is corrected completely and the THD is improved even further.

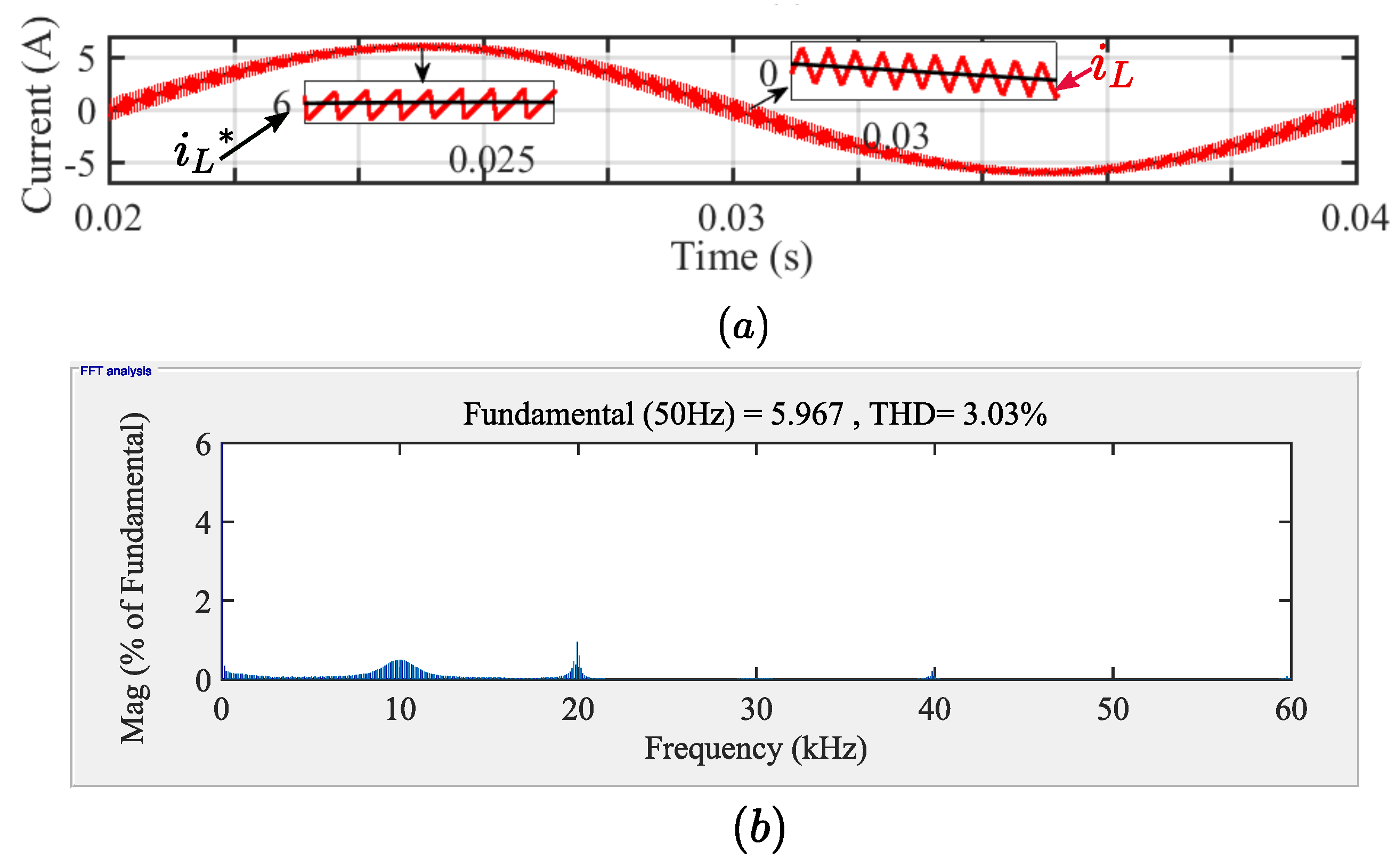

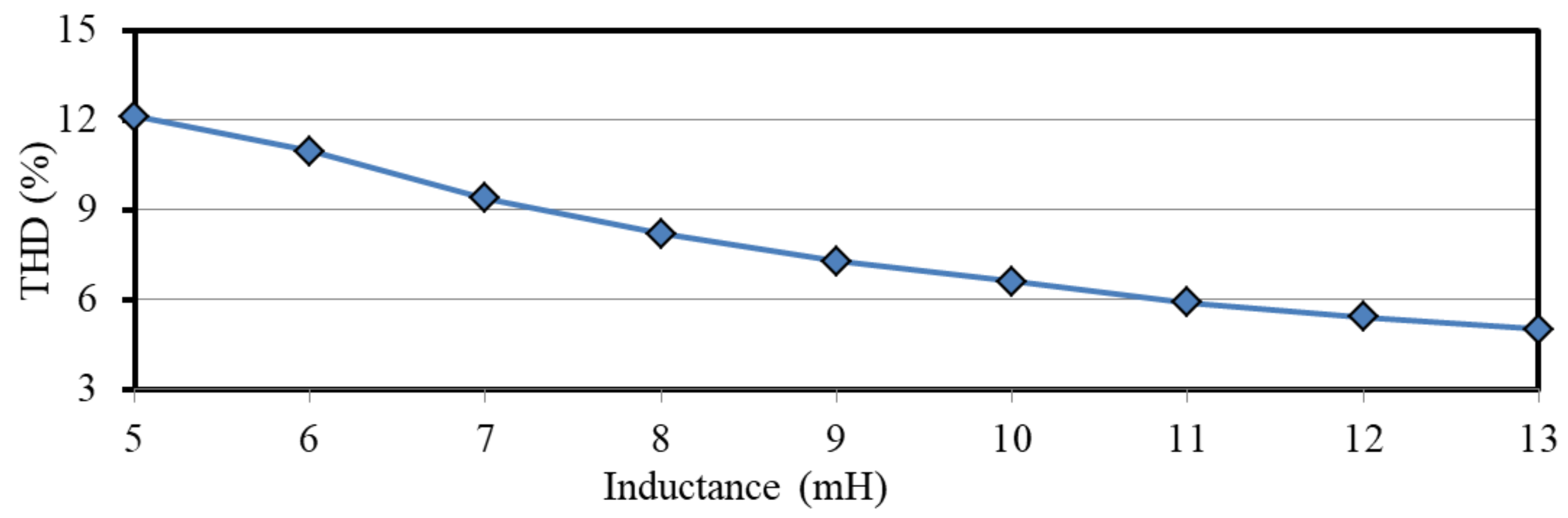

3.1.2. Increasing the Inductance

3.2. Sensitivity Analysis

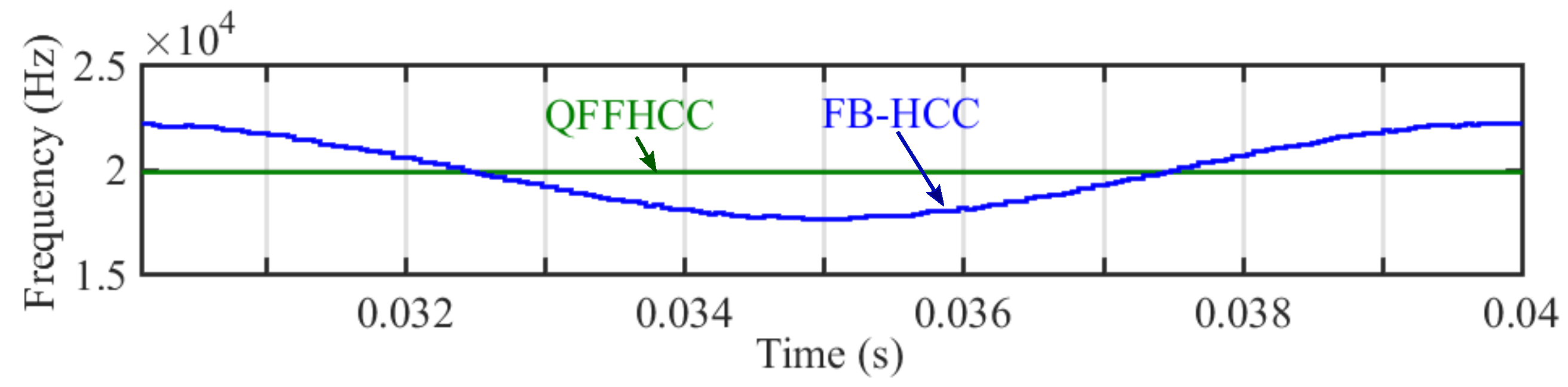

3.3. Switching Frequency Analysis

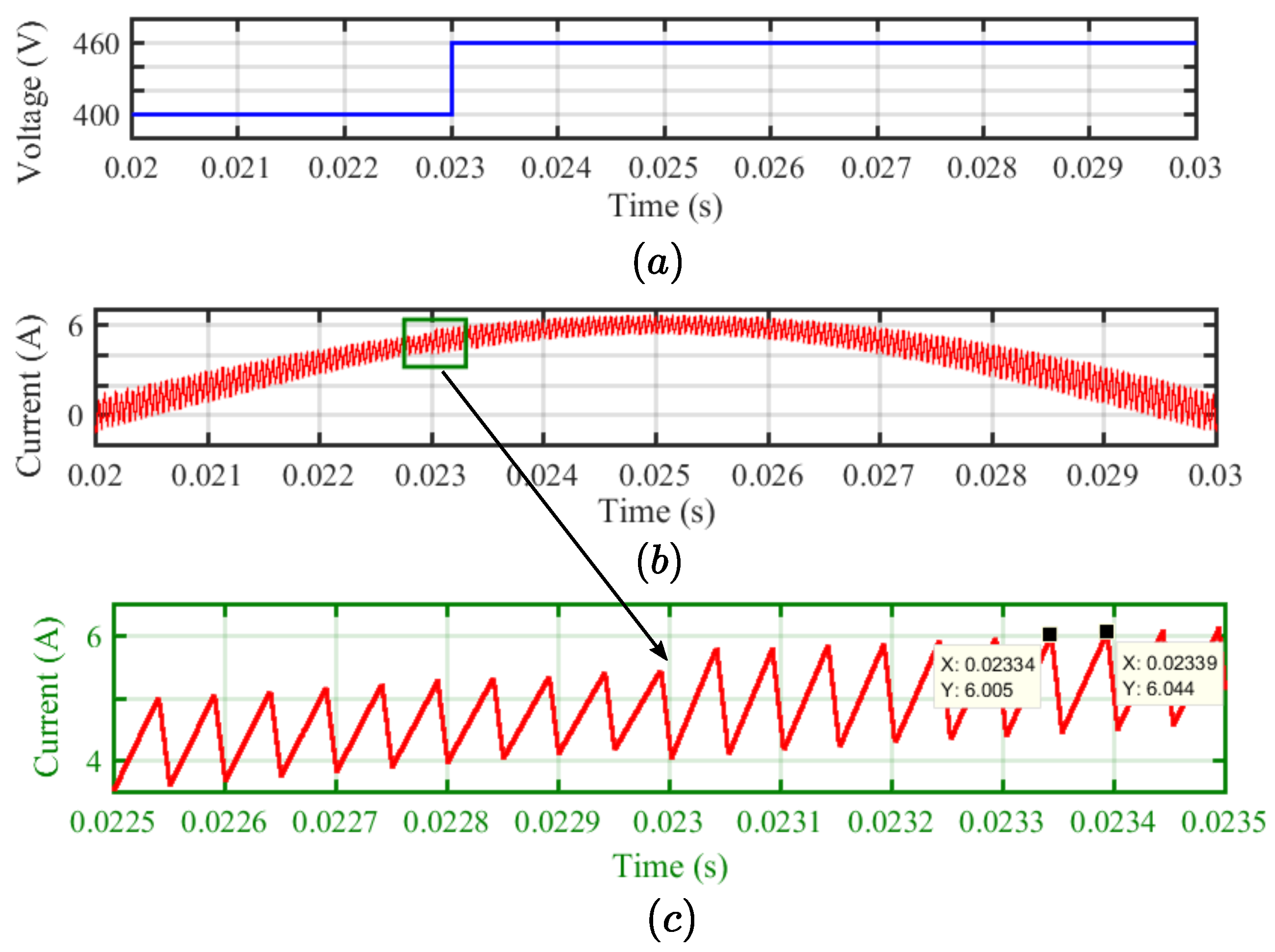

3.4. Transient Behavior

3.5. Comparison with a Similar Control Scheme

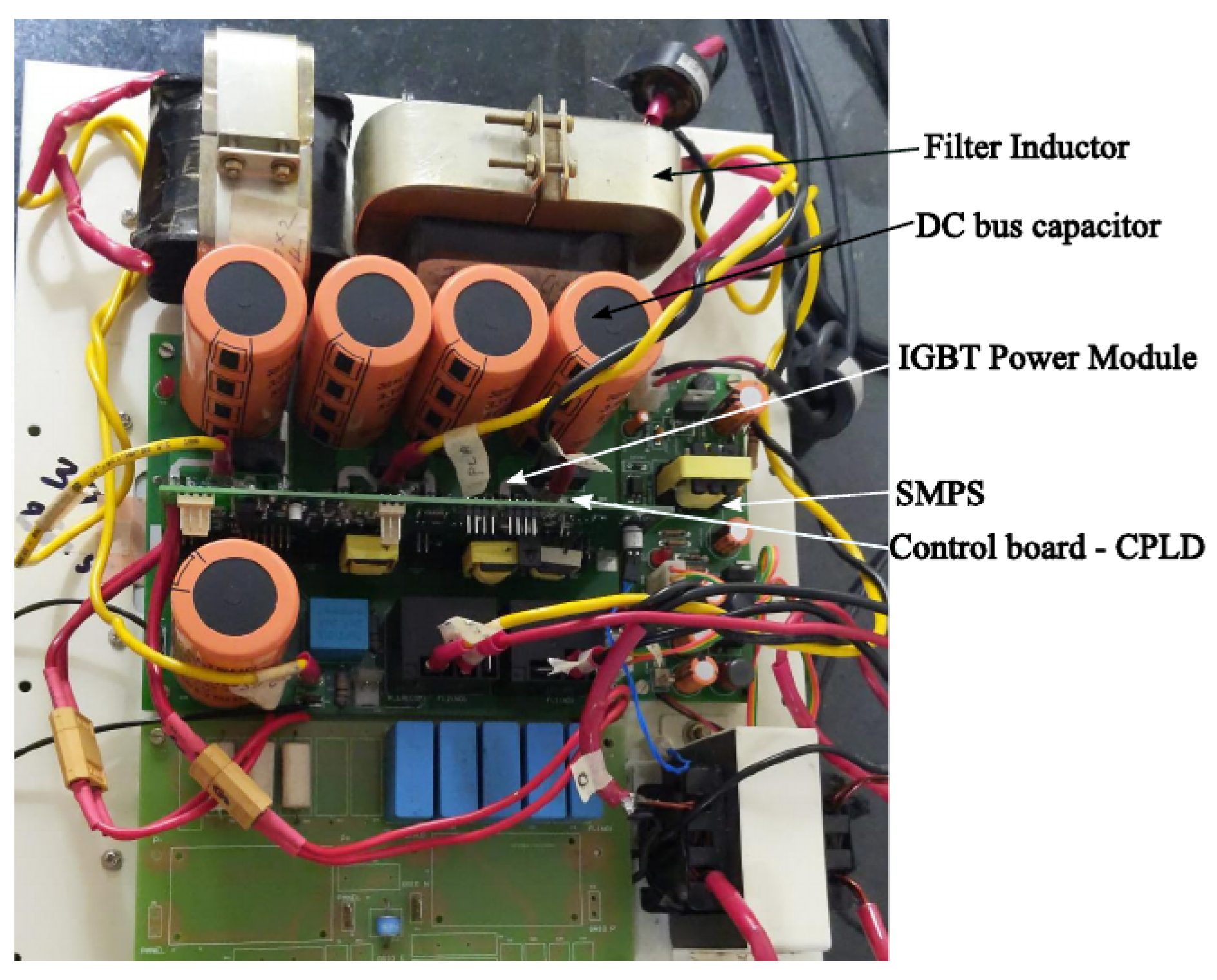

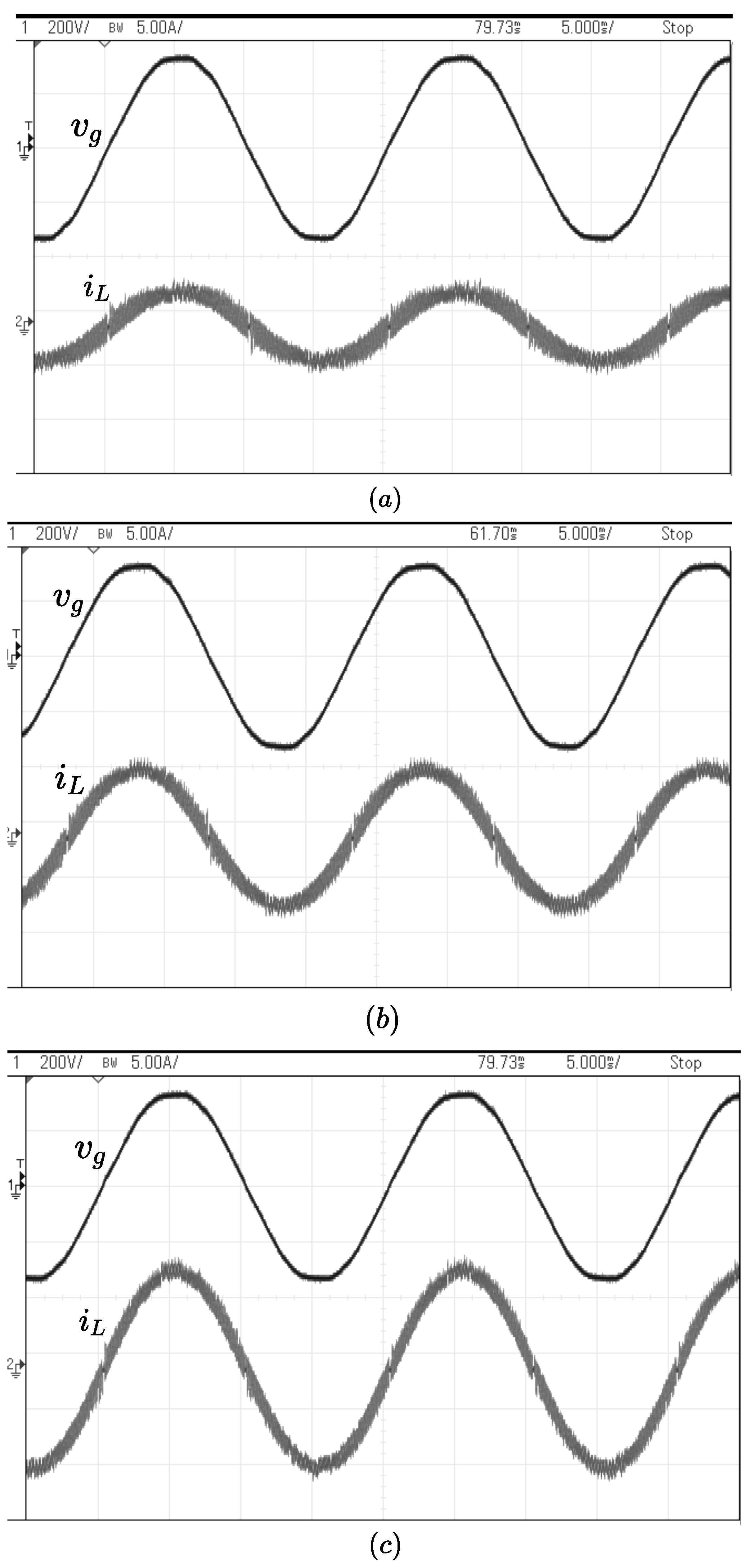

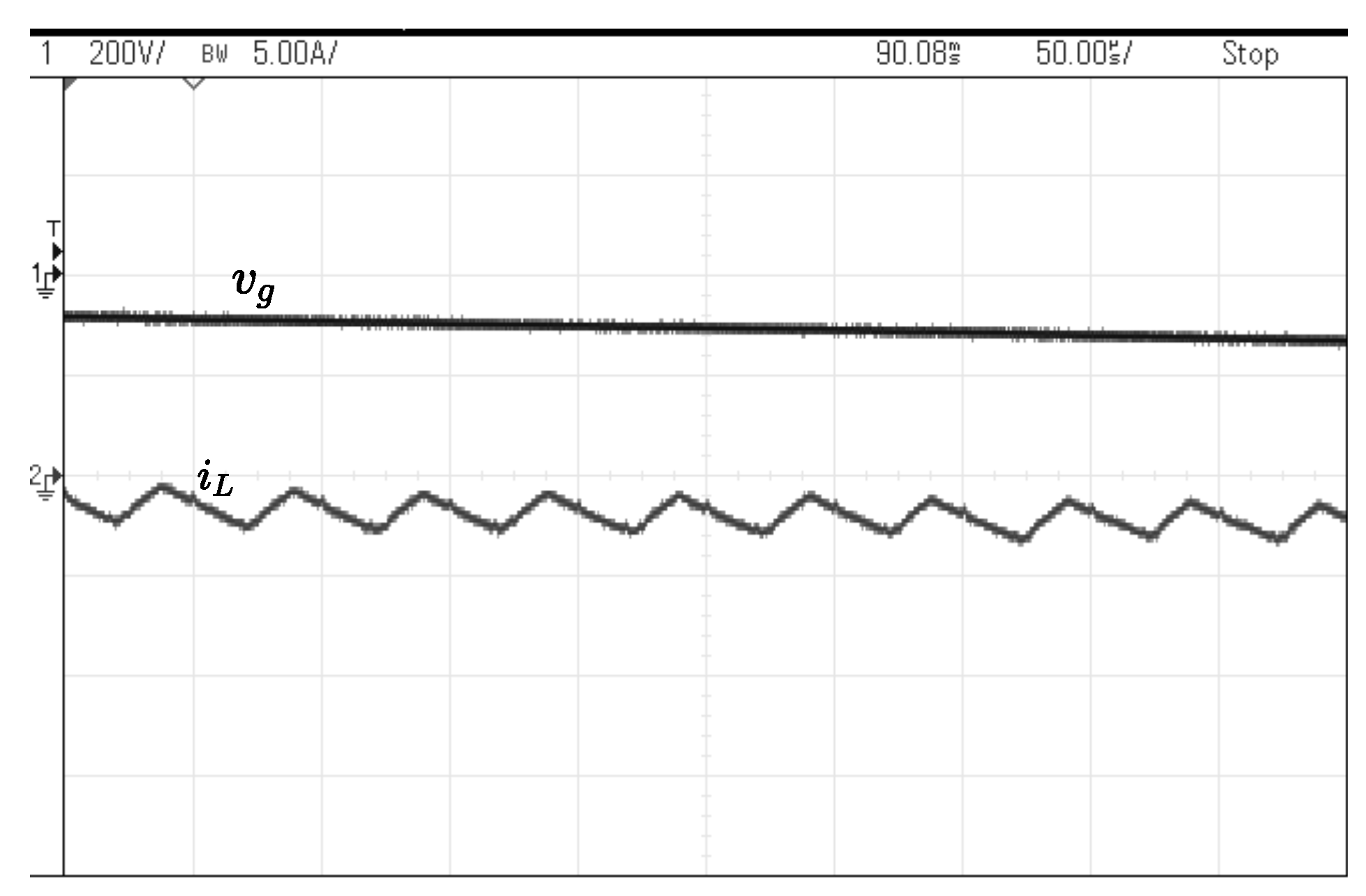

4. Experimental Verification

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Newell, R.; Raimi, D.; Villanueva, S.; Prest, B.; Prest, B. Global energy outlook 2021: Pathways from Paris. Resources for the Future. 2021. Available online: https://media.rff.org/documents/RFF_GEO_2021_Report_1.pdf (accessed on 1 September 2022).

- Eltawil, M.A.; Zhao, Z. Grid-connected photovoltaic power systems: Technical and potential problems—A review. Renew. Sustain. Energy Rev. 2010, 14, 112–129. [Google Scholar] [CrossRef]

- Ali Khan, M.Y.; Liu, H.; Yang, Z.; Yuan, X. A comprehensive review on grid connected photovoltaic inverters, their modulation techniques, and control strategies. Energies 2020, 13, 4185. [Google Scholar] [CrossRef]

- Bose, B.K.; Bose, B.K. Power Electronics and Variable Frequency Drives: Technology and Applications; IEEE Press: Piscataway, NJ, USA, 1997; Volume 996. [Google Scholar]

- Carrasco, J.M.; Franquelo, L.G.; Bialasiewicz, J.T.; Galván, E.; PortilloGuisado, R.C.; Prats, M.M.; León, J.I.; Moreno-Alfonso, N. Power-electronic systems for the grid integration of renewable energy sources: A survey. IEEE Trans. Ind. Electron. 2006, 53, 1002–1016. [Google Scholar] [CrossRef]

- Kazmierkowski, M.; Dzieniakowski, M. Review of current regulation methods for VS-PWM inverters. In Proceedings of the ISIE’93-Budapest: IEEE International Symposium on Industrial Electronics Conference Proceedings, Budapest, Hungary, 1–3 June 1993; IEEE: Piscataway, NJ, USA, 1993; pp. 448–456. [Google Scholar]

- Timbus, A.; Liserre, M.; Teodorescu, R.; Rodriguez, P.; Blaabjerg, F. Evaluation of current controllers for distributed power generation systems. IEEE Trans. Power Electron. 2009, 24, 654–664. [Google Scholar] [CrossRef]

- Kazmierkowski, M.P.; Malesani, L. Current control techniques for three-phase voltage-source PWM converters: A survey. IEEE Trans. Ind. Electron. 1998, 45, 691–703. [Google Scholar] [CrossRef]

- Komurcugil, H.; Ozdemir, S.; Sefa, I.; Altin, N.; Kukrer, O. Sliding-Mode Control for Single-Phase Grid-Connected LCL-Filtered VSI With Double-Band Hysteresis Scheme. IEEE Trans. Ind. Electron. 2015, 63, 864–873. [Google Scholar] [CrossRef]

- Kumar, N.; Saha, T.K.; Dey, J. Design and analysis of a double band hysteresis SMC for cascaded inverter-based PV system. In Proceedings of the 2016 IEEE Region 10 Conference (TENCON), Singapore, 22–25 November 2016; IEEE: Piscataway, NJ, USA, 2016; pp. 898–902. [Google Scholar]

- Repecho, V.; Biel, D.; Olm, J.M. A Simple Switching-Frequency-Regulated Sliding-Mode Controller for a VSI With a Full Digital Implementation. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 9, 569–579. [Google Scholar] [CrossRef]

- Camacho, E.F.; Alba, C.B. Model Predictive Control; Springer Science & Business Media: Berlin/Heidelberg, Germany, 2013. [Google Scholar]

- Kouro, S.; Perez, M.A.; Rodriguez, J.; Llor, A.M.; Young, H.A. Model Predictive Control: MPC’s Role in the Evolution of Power Electronics. IEEE Ind. Electron. Mag. 2015, 9, 8–21. [Google Scholar] [CrossRef]

- Xia, C.; Liu, T.; Shi, T.; Song, Z. A Simplified Finite-Control-Set Model-Predictive Control for Power Converters. IEEE Trans. Ind. Inform. 2014, 10, 991–1002. [Google Scholar] [CrossRef]

- Le-Huy, H.; Dessaint, L.A. An adaptive current controller for PWM inverters. In Proceedings of the 1986 17th Annual IEEE Power Electronics Specialists Conference, Vancouver, BC, Canada, 23–27 June 1986; IEEE: Piscataway, NJ, USA, 1986; pp. 610–616. [Google Scholar]

- Rahman, K.; Khan, M.R.; Choudhury, M.; Rahman, M. Variable-band hysteresis current controllers for PWM voltage-source inverters. IEEE Trans. Power Electron. 1997, 12, 964–970. [Google Scholar] [CrossRef]

- Parvez, M.; Elias, M.; Rahim, N.; Osman, N. Current control techniques for three-phase grid interconnection of renewable power generation systems: A review. Sol. Energy 2016, 135, 29–42. [Google Scholar] [CrossRef]

- Buso, S.; Fasolo, S.; Malesani, L.; Mattavelli, P. A dead-beat adaptive hysteresis current control. IEEE Trans. Ind. Appl. 2000, 36, 1174–1180. [Google Scholar] [CrossRef]

- Li, Y.; Zhao, H. A Space Vector Switching Pattern Hysteresis Control Strategy in VIENNA Rectifier. IEEE Access 2020, 8, 60142–60151. [Google Scholar] [CrossRef]

- Bose, B.K. An adaptive hysteresis-band current control technique of a voltage-fed PWM inverter for machine drive system. IEEE Trans. Ind. Electron. 1990, 37, 402–408. [Google Scholar] [CrossRef]

- Malesani, L.; Tenti, P. A novel hysteresis control method for current-controlled voltage-source PWM inverters with constant modulation frequency. IEEE Trans. Ind. Appl. 1990, 26, 88–92. [Google Scholar] [CrossRef]

- Tripathi, A.; Sen, P.C. Comparative analysis of fixed and sinusoidal band hysteresis current controllers for voltage source inverters. IEEE Trans. Ind. Electron. 1992, 39, 63–73. [Google Scholar] [CrossRef]

- Malesani, L.; Mattavelli, P.; Tomasin, P. Improved constant-frequency hysteresis current control of VSI inverters with simple feedforward bandwidth prediction. IEEE Trans. Ind. Appl. 1997, 33, 1194–1202. [Google Scholar] [CrossRef]

- Tekwani, P.; Kanchan, R.; Gopakumar, K. Novel current error space phasor based hysteresis controller using parabolic bands for control of switching frequency variations. IEEE Trans. Ind. Electron. 2007, 54, 2648–2656. [Google Scholar] [CrossRef]

- Ho, C.N.M.; Cheung, V.S.; Chung, H.S.H. Constant-frequency hysteresis current control of grid-connected VSI without bandwidth control. IEEE Trans. Power Electron. 2009, 24, 2484–2495. [Google Scholar] [CrossRef]

- Buccella, C.; Cecati, C.; Latafat, H. Digital control of power converters—A survey. IEEE Trans. Ind. Inform. 2012, 8, 437–447. [Google Scholar] [CrossRef]

- Nguyen-Van, T.; Abe, R.; Tanaka, K. A digital hysteresis current control for half-bridge inverters with constrained switching frequency. Energies 2017, 10, 1610. [Google Scholar] [CrossRef]

- Wu, F.; Feng, F.; Luo, L.; Duan, J.; Sun, L. Sampling period online adjusting-based hysteresis current control without band with constant switching frequency. IEEE Trans. Ind. Electron. 2014, 62, 270–277. [Google Scholar] [CrossRef]

- Blaabjerg, F.; Teodorescu, R.; Liserre, M.; Timbus, A.V. Overview of control and grid synchronization for distributed power generation systems. IEEE Trans. Ind. Electron. 2006, 53, 1398–1409. [Google Scholar] [CrossRef]

- Chettibi, N.; Mellit, A. FPGA-based real time simulation and control of grid-connected photovoltaic systems. Simul. Model. Pract. Theory 2014, 43, 34–53. [Google Scholar] [CrossRef]

- Buso, S.; Caldognetto, T. A nonlinear wide-bandwidth digital current controller for DC–DC and DC–AC converters. IEEE Trans. Ind. Electron. 2015, 62, 7687–7695. [Google Scholar] [CrossRef]

- Kumar, M.; Gupta, R. Sampled-time-domain analysis of a digitally implemented current controlled inverter. IEEE Trans. Ind. Electron. 2016, 64, 217–227. [Google Scholar] [CrossRef]

- Al-Safi, A.; Al-Khayyat, A.; Manati, A.M.; Alhafadhi, L. Advances in fpga based pwm generation for power electronics applications: Literature review. In Proceedings of the 2020 11th IEEE Annual Information Technology, Electronics and Mobile Communication Conference (IEMCON), Online, 4–7 November 2020; IEEE: Piscataway, NJ, USA, 2020; pp. 252–259. [Google Scholar]

- Sankar, D.; Syamala, L.; Chembathu Ayyappan, B.; Kallarackal, M. FPGA-Based Cost-Effective and Resource Optimized Solution of Predictive Direct Current Control for Power Converters. Energies 2021, 14, 7669. [Google Scholar] [CrossRef]

- Nguyen, V.T.; Dam, M.T.; So, J.; Lee, J.G. Immunity Characterization of FPGA I/Os for Fault-Tolerant Circuit Designs against EMI. Adv. Electr. Comput. Eng. 2019, 19, 37–44. [Google Scholar] [CrossRef]

- Dartawan, K.; Najafabadi, A.M. Case study: Applying IEEE Std. 519-2014 for harmonic distortion analysis of a 180 MW solar farm. In Proceedings of the 2017 IEEE Power & Energy Society General Meeting, Chicago, IL, USA, 16–20 July 2017; IEEE: Piscataway, NJ, USA, 2017; pp. 1–5. [Google Scholar]

- Photovoltaics, D.G.; Storage, E. IEEE 1547–2018—IEEE Standard for Interconnection and Interoperability of Distributed Energy Resources with Associated Electric Power Systems Interfaces—Redline. 2018. Available online: https://ieeexplore.ieee.org/document/8365917547–2018 (accessed on 1 September 2022).

- International Electrotechnical Commission. IEC 61727-2004 Photovoltaic (PV) Systems: Characteristics of the U-tility Interface. 2007. Available online: https://global.ihs.com/doc_detail.cfm?item_s_key=00285429#referenced-documents (accessed on 1 September 2022).

- Arranz-Gimon, A.; Zorita-Lamadrid, A.; Morinigo-Sotelo, D.; Duque-Perez, O. A review of total harmonic distortion factors for the measurement of harmonic and interharmonic pollution in modern power systems. Energies 2021, 14, 6467. [Google Scholar] [CrossRef]

| MPC | SMC | QFFHCC |

|---|---|---|

| (1) Non-linear controller (2) No modulation needed (3) Handle system constraints in an intuitive way (4) Can include non-conventional control objectives | (1) Robustness to parameter variations (2) Fast transient response (3) Reduction in system order | (1) Non-linear controller (2) Easy to implement (3) No modulators are used (4) Very fast transient response (5) Robust (6) Offers fixed switching frequency (7) Works well with advanced controllers like FPGA/CPLD |

| (1) Variable switching frequency (2) High computational burden | (1) Chattering effect (2) Variable switching frequency | (1) Performance depends on the controller used (2) Current feedback is needed |

| Parameter | Value |

|---|---|

| 400 V | |

| 50 Hz | |

| 230 V | |

| 20 kHz | |

| L | 5 mH |

| 6 A |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Syamala, L.; Sankar, D.; Makkar, S.E.; Jos, B.M.; Kallarackal, M. Hysteresis Based Quasi Fixed Frequency Current Control of Single Phase Full Bridge Grid Integrated Voltage Source Inverter. Energies 2022, 15, 8112. https://doi.org/10.3390/en15218112

Syamala L, Sankar D, Makkar SE, Jos BM, Kallarackal M. Hysteresis Based Quasi Fixed Frequency Current Control of Single Phase Full Bridge Grid Integrated Voltage Source Inverter. Energies. 2022; 15(21):8112. https://doi.org/10.3390/en15218112

Chicago/Turabian StyleSyamala, Lakshmi, Deepa Sankar, Suhara Ekkarakkudy Makkar, Bos Mathew Jos, and Mathew Kallarackal. 2022. "Hysteresis Based Quasi Fixed Frequency Current Control of Single Phase Full Bridge Grid Integrated Voltage Source Inverter" Energies 15, no. 21: 8112. https://doi.org/10.3390/en15218112

APA StyleSyamala, L., Sankar, D., Makkar, S. E., Jos, B. M., & Kallarackal, M. (2022). Hysteresis Based Quasi Fixed Frequency Current Control of Single Phase Full Bridge Grid Integrated Voltage Source Inverter. Energies, 15(21), 8112. https://doi.org/10.3390/en15218112