Impedance Compensation Method Considering Unbalanced Ground Fault with SFCL in a Power Distribution System

Abstract

1. Introduction

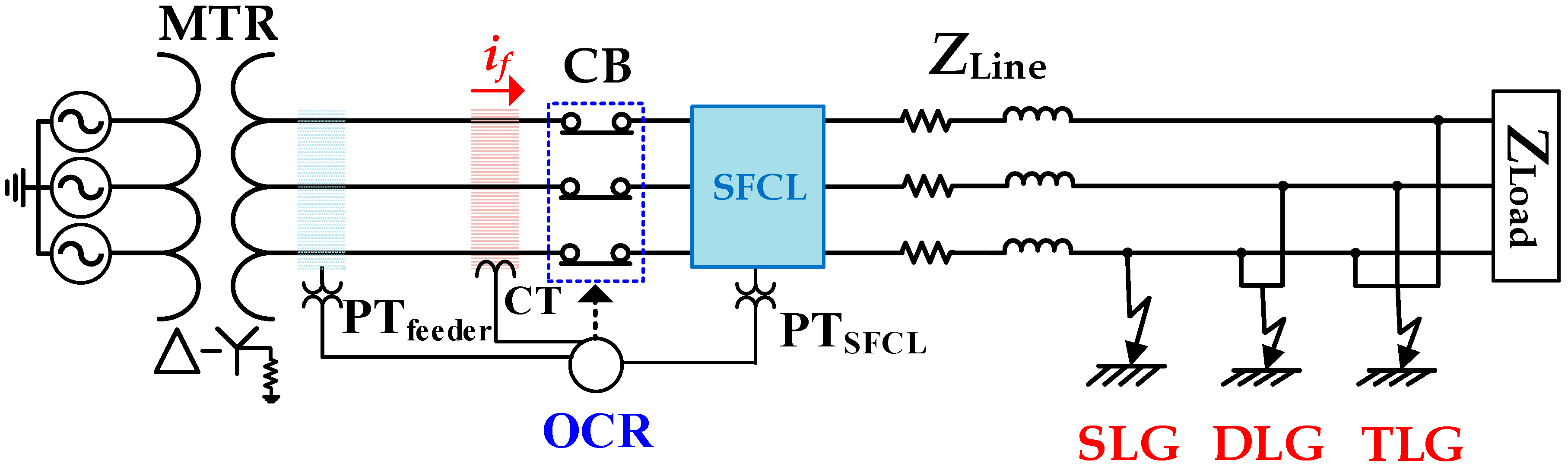

2. Configuration of Power Distribution System with SFCL

2.1. Structure of Power Distribution System

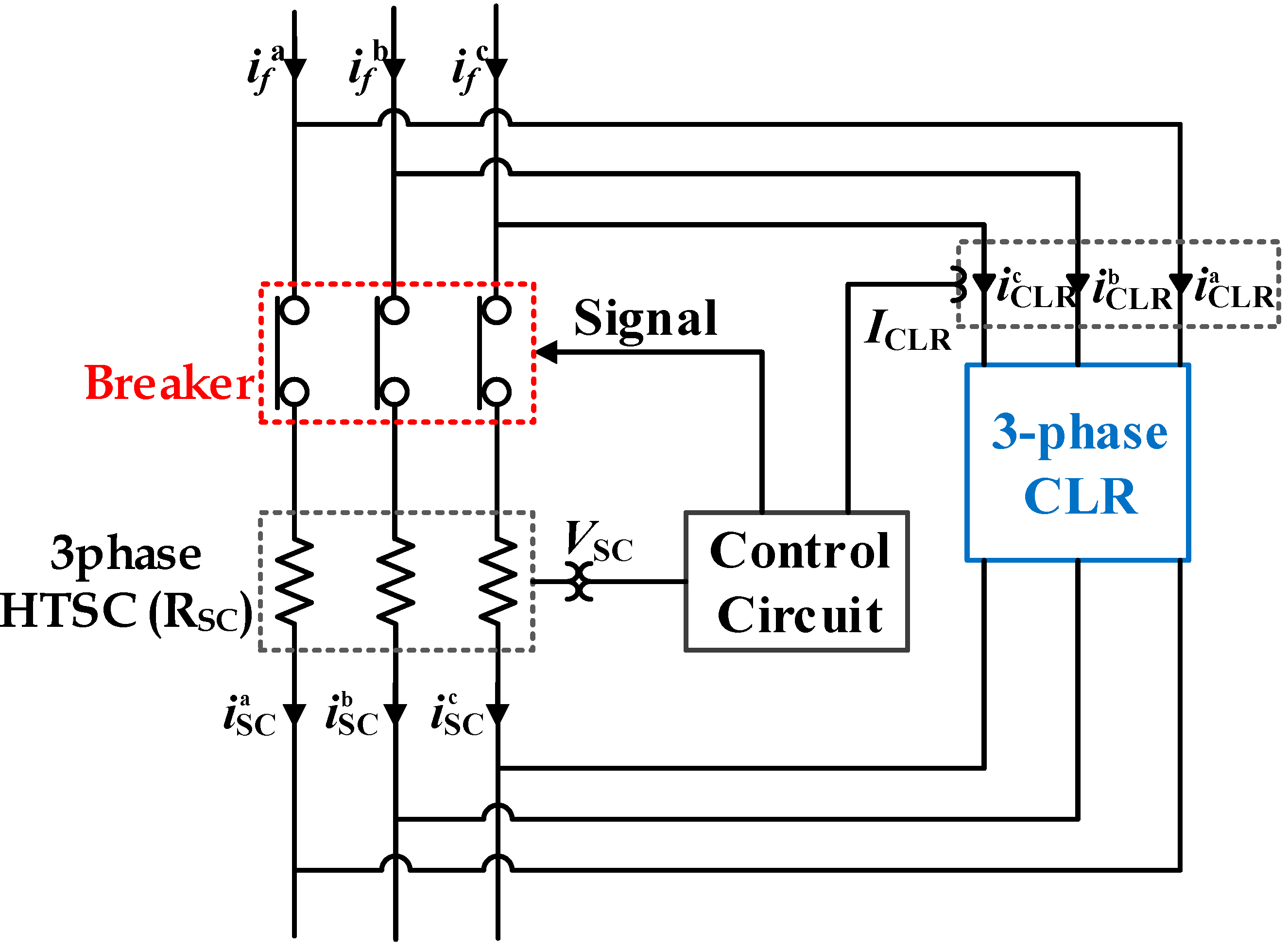

2.2. Trigger Type SFCL Modeling

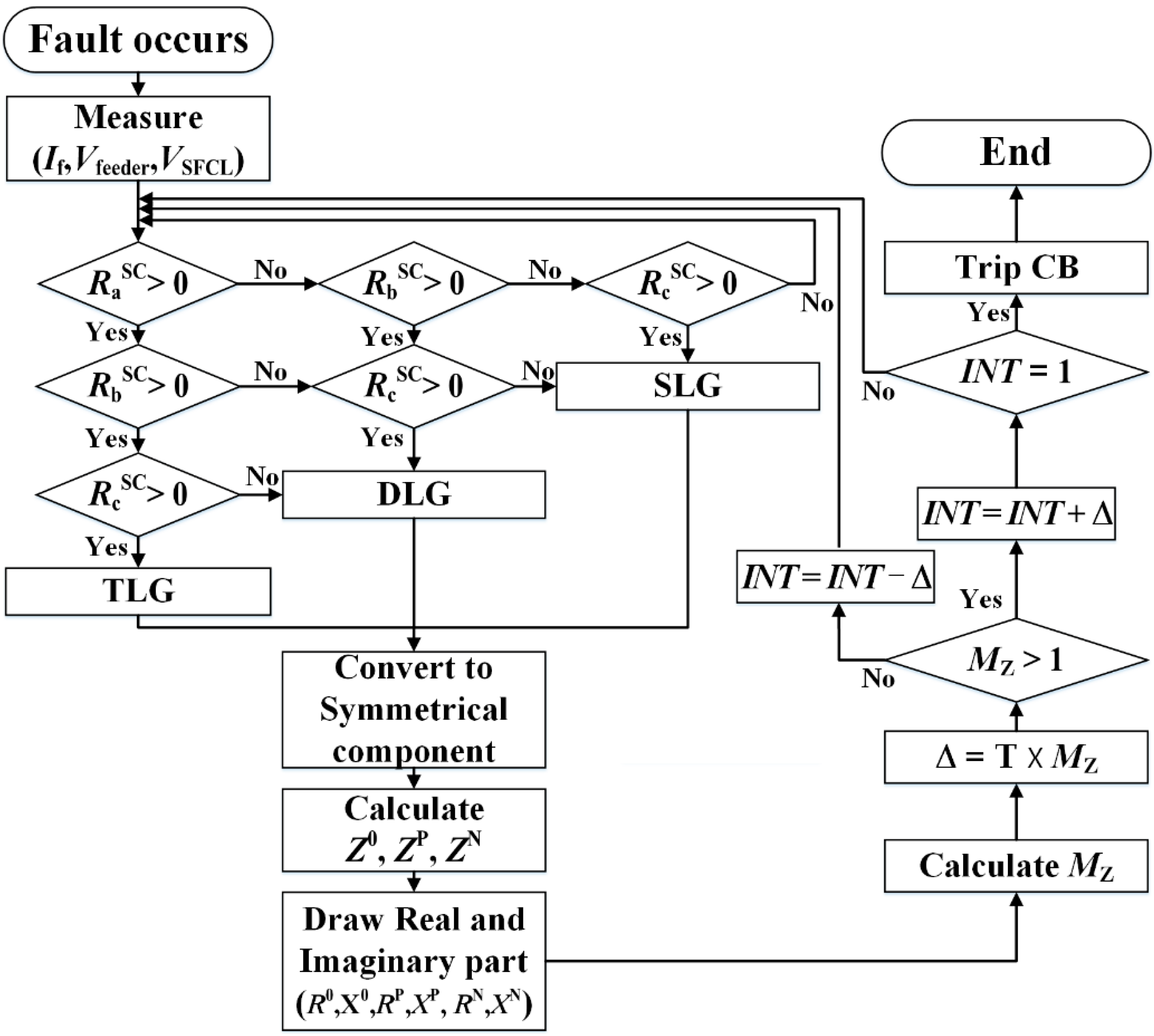

3. Operational Characteristic of over Current Relay

3.1. Equivalent Impedance of Power Distribution System

- Case 1: Single-line ground fault (SLG)

- Case 2: Double-line ground fault (DLG)

- Case 3: Triple-line ground fault (TLG)

3.2. Over Current Relay’s Characteristic Modeling

4. Results and Discussion

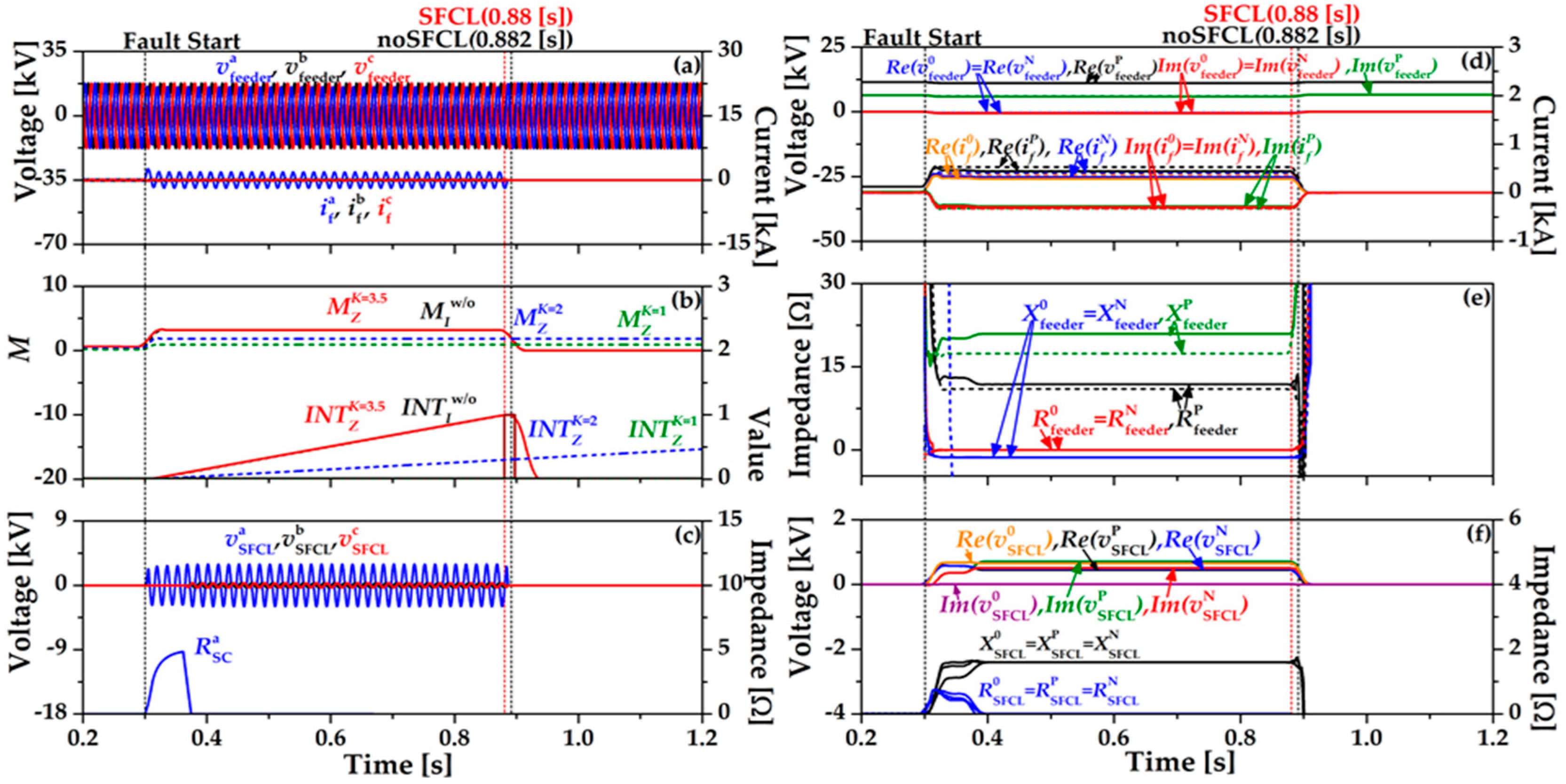

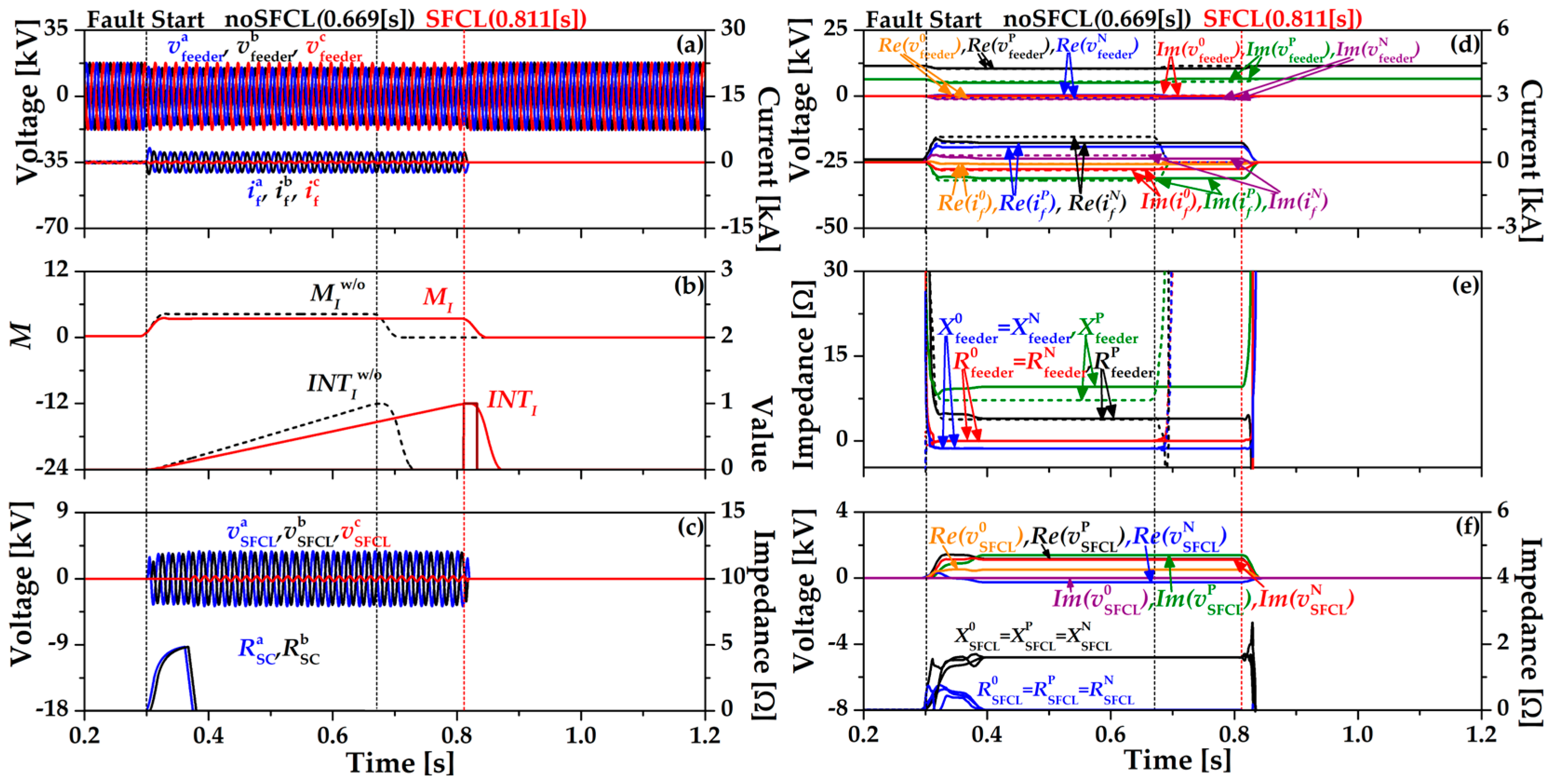

4.1. Single-Line Ground Fault

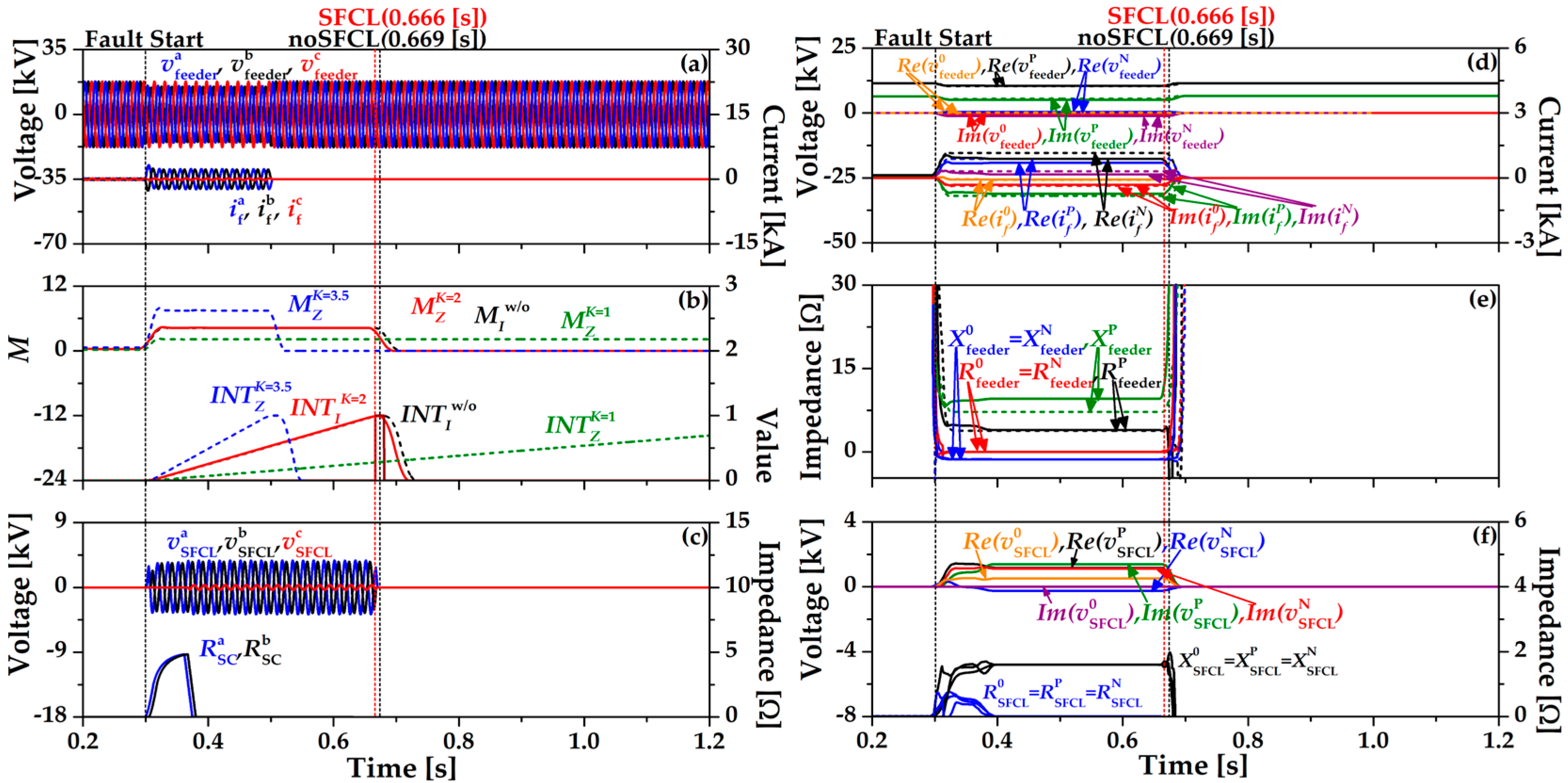

4.2. Double-Line Ground Fault

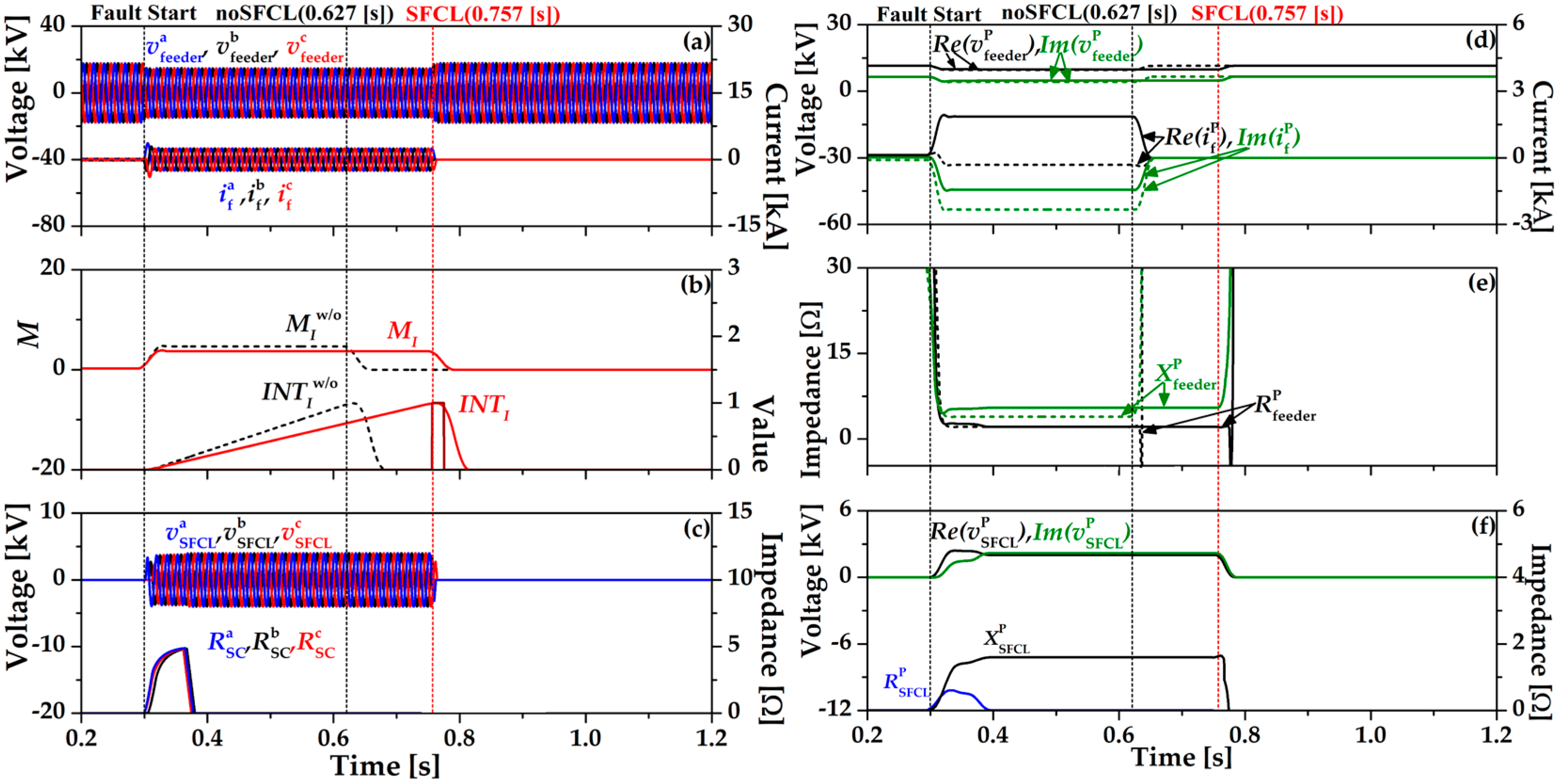

4.3. Triple-Line Ground Fault

5. Discussion

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Kim, H.J.; Yoon, T.A. Study on application of a high-speed trigger-type SFCL (TSFCL) for interconnection of power systems with different reliabilities. IEEE Trans. Appl. Supercond. 2010, 20, 1194–1198. [Google Scholar] [CrossRef]

- Song, M.; Tang, Y.; Zhou, Y.; Ren, L.; Chen, L.; Cheng, S. Electromagnetic Characteristics Analysis of Air-Core Transformer Used in Voltage Compensation Type Active SFCL. IEEE Trans. Appl. Supercond. 2010, 20, 1194–1198. [Google Scholar] [CrossRef]

- Zou, Z.-C.; Chen, X.-Y.; Li, C.-S.; Xiao, X.Y.; Zhang, Y. Conceptual Design and Evaluation of a Resistive-Type SFCL for Efficient Fault Ride through in a DFIG. IEEE Trans. Appl. Supercond. 2016, 26, 7. [Google Scholar] [CrossRef]

- Lim, S.H.; Han, T.H.; Cho, Y.S.; Choi, H.S.; Han, B.S.; Lee, S.W. Quench characteristics of HTSC elements in integrated three-phase flux-lock type SFCL according to ground-fault types. Phys. C Supercond. Appl. 2007, 463, 1198–1203. [Google Scholar] [CrossRef]

- Hyun, O.-B.; Park, K.-B.; Sim, J.; Kim, H.-R.; Yim, S.-W.; Oh, I.-S. Introduction of a Hybrid SFCL in KEPCO Grid and Local Points at Issue. IEEE Trans. Appl. Supercond. 2009, 19, 1946–1949. [Google Scholar] [CrossRef]

- Shirai, Y.; Noda, S.; Yamabe, K.; Hattori, K.; Baba, J.; Nishihara, T.; Nitta, T.; Kobayashi, S.; Sato, K. Current Limiting Performance of Three-Phase Concentric Transformer Type SFCL at Unbalanced Fault Conditions. IEEE Trans. Appl. Supercond. 2012, 23, 5601905. [Google Scholar] [CrossRef][Green Version]

- Kim, W.-S.; Hyun, O.-B.; Park, C.-R.; Yim, S.-W.; Yu, S.-D.; Yang, S.-E.; Kim, H.-S.; Kim, H.R. Dynamic Characteristics of a 22.9 kV Hybrid SFCL for Short-Circuit Test Considering a Simple Coordination of Protection System in Distribution Networks. IEEE Trans. Appl. Supercond. 2012, 22, 3. [Google Scholar]

- Sung, B.C.; Park, D.K.; Park, J.W.; Ko, T.K. Study on a Series Resistive SFCL to Improve Power System Transient Stability: Modeling, Simulation, and Experimental Verification. IEEE Trans. Ind. Electron. 2009, 56, 2412–2419. [Google Scholar] [CrossRef]

- Shen, B.; Chen, Y.; Li, C.; Wang, S.; Chen, X. Superconducting fault current limiter (SFCL): Experiment and the simulation from finite-element method (FEM) to power/energy system software. Energies 2021, 234, 1. [Google Scholar] [CrossRef]

- Huh, J.-S.; Shin, H.-S.; Moon, W.-S.; Kang, B.-W.; Kim, J.-C. Study on Voltage Unbalance Improvement Using SFCL in Power Feed Network with Electric Railway System. IEEE Trans. Appl. Supercond. 2013, 23, 3601004. [Google Scholar]

- Choi, H.-Y.; Cho, Y.-S.; Jung, B.-I.; Chung, D.-C.; Fathy, A. Comparison of the Unbalanced Faults in Three-Phase Resistive and Matrix-Type SFCLs. IEEE Trans. Appl. Supercond. 2010, 20, 1215–1218. [Google Scholar] [CrossRef]

- Lim, S.-H.; Lim, S.-T. Current Limiting and Recovery Characteristics of a Trigger-Type SFCL Using Double Quench. IEEE Trans. Appl. Supercond. 2018, 28, 17572499. [Google Scholar] [CrossRef]

- Martini, L.; Bocchi, M.; Angeli, G.; Ascade, M.; Rossi, V.; Valzasina, A.; Ravetta, C.; Fratti, S.; Martino, E. Live grid field-testing final results of the first Italian superconducting fault current limiter and severe 3-phase fault experience. IEEE. Trans. Appl. Supercond. 2015, 25, 3. [Google Scholar] [CrossRef]

- Shin, J.W.; Kim, J.C.; Lee, H.; Yoon, K.H.; Chai, H.S.; Kim, J.S. Impact of SFCL according to Voltage Sags Based Reliability. IEEE Trans. Appl. Supercond. 2021, 31, 5. [Google Scholar] [CrossRef]

- Lim, S.T.; Lim, S.H. Analysis on operational improvement of OCR using voltage component in a power distribution system for application of SFCL. J. Electr. Eng. Technol. 2019, 14, 1027–1033. [Google Scholar] [CrossRef]

- Park, M.-K.; Lim, S.-H. Impedance Compensation Method of Protective Relay for SFCL’s Application in a Power Distribution System. IEEE Trans. Appl. Supercond. 2021, 31, 20463141. [Google Scholar] [CrossRef]

- Park, M.-K.; Lim, S.-H. Analysis on Protection Coordination of OCRs Using Voltage Components for the Application of SFCL in a Power Distribution System with DG. IEEE Trans. Appl. Supercond. 2021, 31, 20994711. [Google Scholar]

- Moon, J.; Lim, S.; Kim, J.; Yun, S. Assessment of the Impact of SFCL on Voltage Sags in Power Distribution System. IEEE Trans. Appl. Supercond. 2011, 21, 2161–2164. [Google Scholar] [CrossRef]

- Lim, S.T.; Lim, S.H. Analysis on protective coordination between over-current relays with voltage component in a power distribution system with SFCL. IEEE Trans. Appl. Supercond. 2020, 30, 4. [Google Scholar] [CrossRef]

- Choi, S.-J.; Lim, S.H. Enhancement on the Fault Ride through Capability of Power Distribution Systems Linked by Distributed Generation due to the Impedance of Superconducting Fault Current Limiters. Energies 2019, 12, 4810. [Google Scholar] [CrossRef]

- Lim, S.T.; Lim, S.H. Study on improvement of overcurrent relay (OCR)’s operation due to application of superconducting fault current limiter (SFCL) in power distribution system with a dispersed generation. Trans. Korean Inst. Electr. Eng. 2017, 66, 300–304. [Google Scholar] [CrossRef]

- Mangunkusumo, K.G.H.; Kusuma, A.A.; Munir, B.S. A Case Study of Mutual Impedance Effect in Parallel Transmission Lines Under Maintenance Condition. In Proceedings of the 2018 10th International Conference on Information Technology and Electrical Engineering (ICITEE), Bali, Indonesia, 24–26 July 2018; pp. 192–195. [Google Scholar]

- Koirala, A.; D’hulst, R.; van Hertem, D. Impedance modelling for European style Distribution Feeder. In Proceedings of the 2019 International Conference on Smart Energy Systems and Technologies (SEST), Porto, Portugal, 11 September 2019. [Google Scholar]

- Wen, B.; Burgos, R.; Boroyevich, D.; Mattavelli, P.; Shen, Z. AC Stability Analysis and dq Frame Impedance Specifications in Power-Electronics-Based Distributed Power Systems. IEEE J. Emerg. Sel. Top. Power Electron. 2017, 5, 1455–1465. [Google Scholar] [CrossRef]

- Saadat, H. Power System Analysis; Milwaukee School of Engineering: Milwaukee, WI, USA, 1999. [Google Scholar]

- Sravya, A.S.L.; Yoshita, L.N.; Reddy, B.D.D.; Sailaja, V.; Manitha, P.V.; Deepa, K. Impedance Bus Matrix Formation using Bus Building Algorithm for Power System Analysis. In Proceedings of the 2020 IEEE International Women in Engineering (WIE) Conference on Electrical and Computer Engineering (WIECON-ECE), Bhubaneswar, India, 26–27 December 2020; pp. 200–205. [Google Scholar]

- Paz, M.C.R.; Ferraz, R.G.; Bretas, A.S.; Leborgne, R.C. System unbalance and fault impedance effect on faulted distribution networks. Comput. Math. Appl. 2010, 60, 1105–1114. [Google Scholar]

- Korea Electric Power Corporation. Distribution Practical III; Korea Electric Power Corporation: Seoul, Korea, 2006. [Google Scholar]

| Experimental Circuit | Value | Unit |

|---|---|---|

| Source | 154 | [kV] |

| 100 | [MVA] | |

| MTR | 154/22.9 | [kV] |

| 60 | [MVA] | |

| Line Impedance | ZP = ZN = 0.182 + j0.391 | [Ω/km] |

| Z0 = 0.518 + j1.189 | [Ω/km] | |

| Feeder Length | 10 | [km] |

| Load | 5 | [MW] |

| PF = 0.95 |

| Parameters | Value | Unit |

|---|---|---|

| VSet | 1 | [kV] |

| ISet | 0.5 | [kA] |

| HTSC | Convergence resistance (Rn) = 5 Critical current (IC) = 1 | [Ω] [kA] |

| CLR | j1.6 | [Ω] |

| Parameters | Data |

|---|---|

| TD | 0.1 |

| A | 39.85 |

| B | 1.084 |

| p | 1.95 |

| [kV] | 10.56 |

| [kA] | 0.504 |

| Fault Type | K | Existing OCR Algorithm [s] | Impedance Compensation Method [s] |

|---|---|---|---|

| SLG | 3.5 | 0.882 | 0.88 |

| DLG | 2 | 0.669 | 0.666 |

| TLG | 1 | 0.627 | 0.626 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Cho, Y.-J.; Lim, S.-H. Impedance Compensation Method Considering Unbalanced Ground Fault with SFCL in a Power Distribution System. Energies 2022, 15, 7405. https://doi.org/10.3390/en15197405

Cho Y-J, Lim S-H. Impedance Compensation Method Considering Unbalanced Ground Fault with SFCL in a Power Distribution System. Energies. 2022; 15(19):7405. https://doi.org/10.3390/en15197405

Chicago/Turabian StyleCho, Yoo-Jung, and Sung-Hun Lim. 2022. "Impedance Compensation Method Considering Unbalanced Ground Fault with SFCL in a Power Distribution System" Energies 15, no. 19: 7405. https://doi.org/10.3390/en15197405

APA StyleCho, Y.-J., & Lim, S.-H. (2022). Impedance Compensation Method Considering Unbalanced Ground Fault with SFCL in a Power Distribution System. Energies, 15(19), 7405. https://doi.org/10.3390/en15197405