UTC Synchronized Signal Generation for Synchrophasors and Sampled Values Measurements

Abstract

:1. Introduction

2. Related Works and Standards

3. Sampling Clock Generation

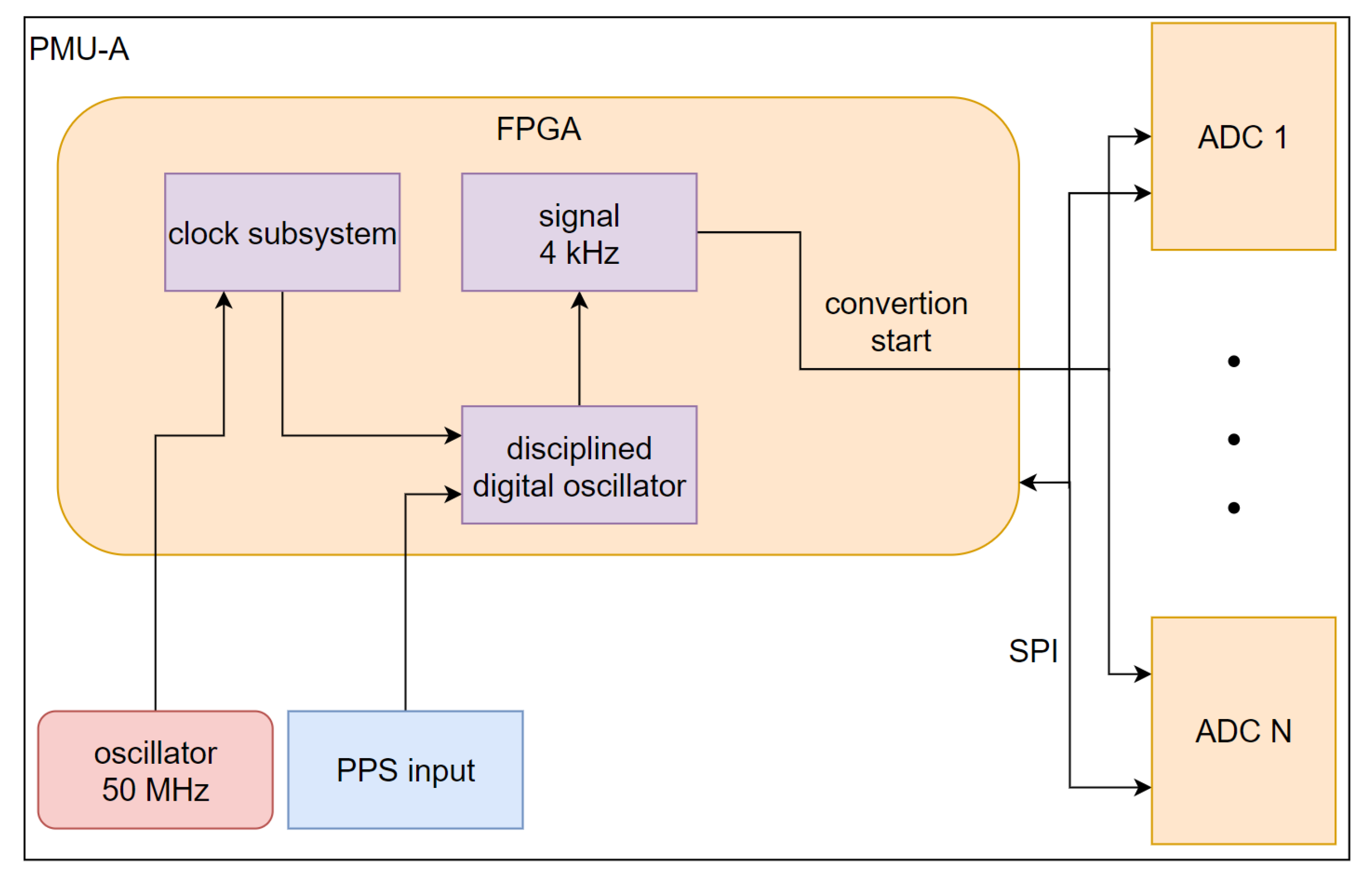

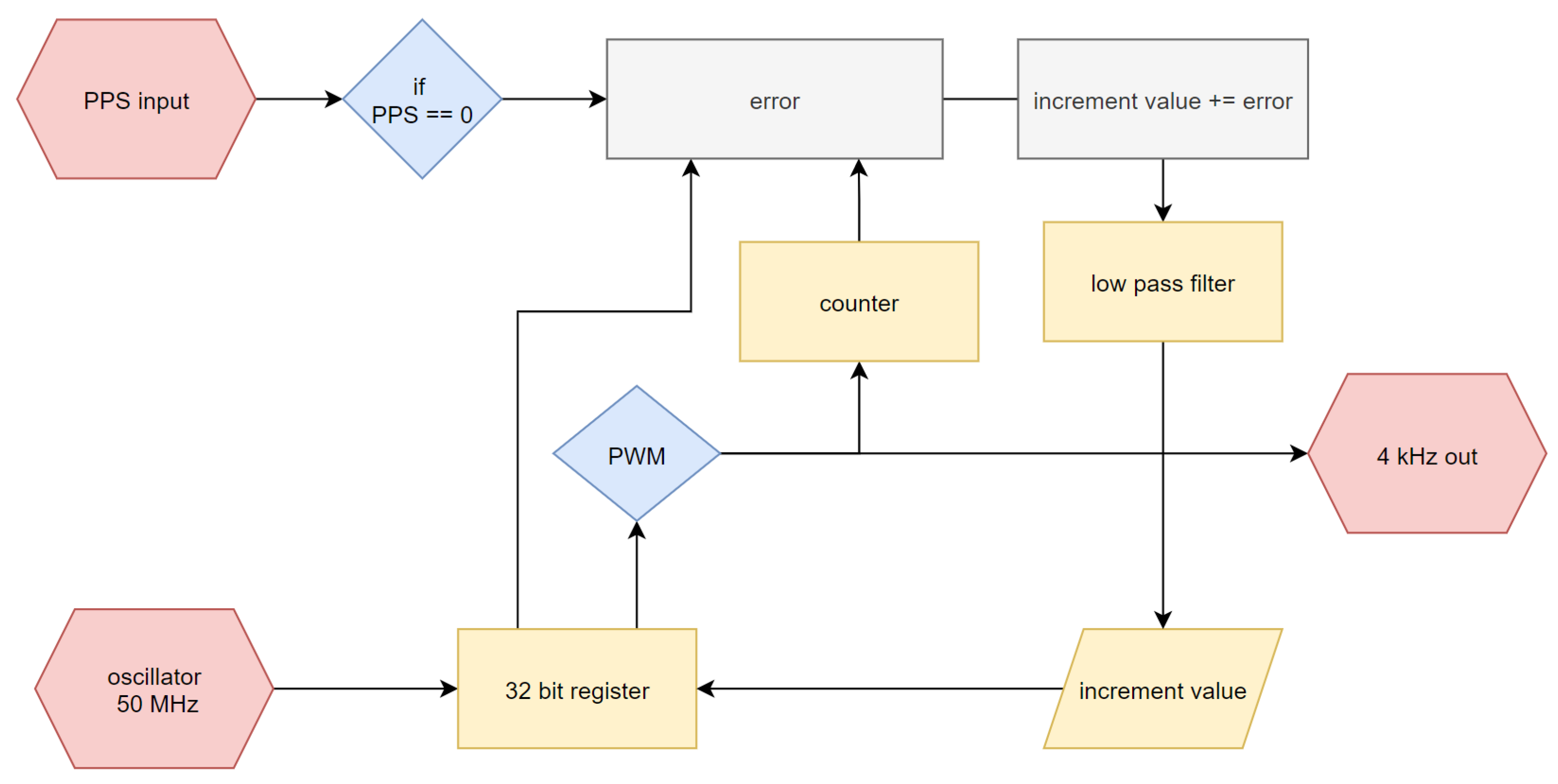

3.1. PMU-A

3.2. PMU-B

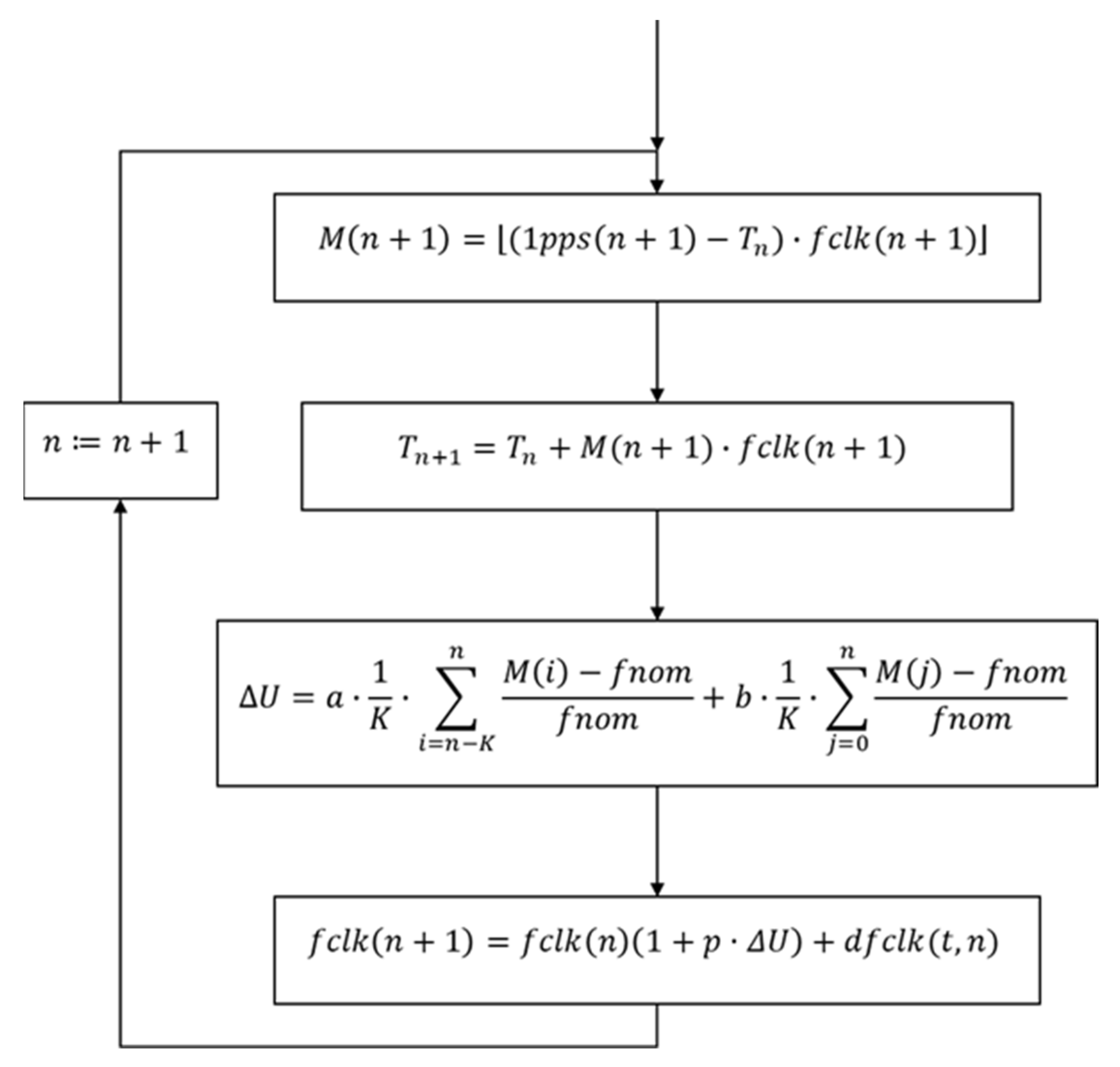

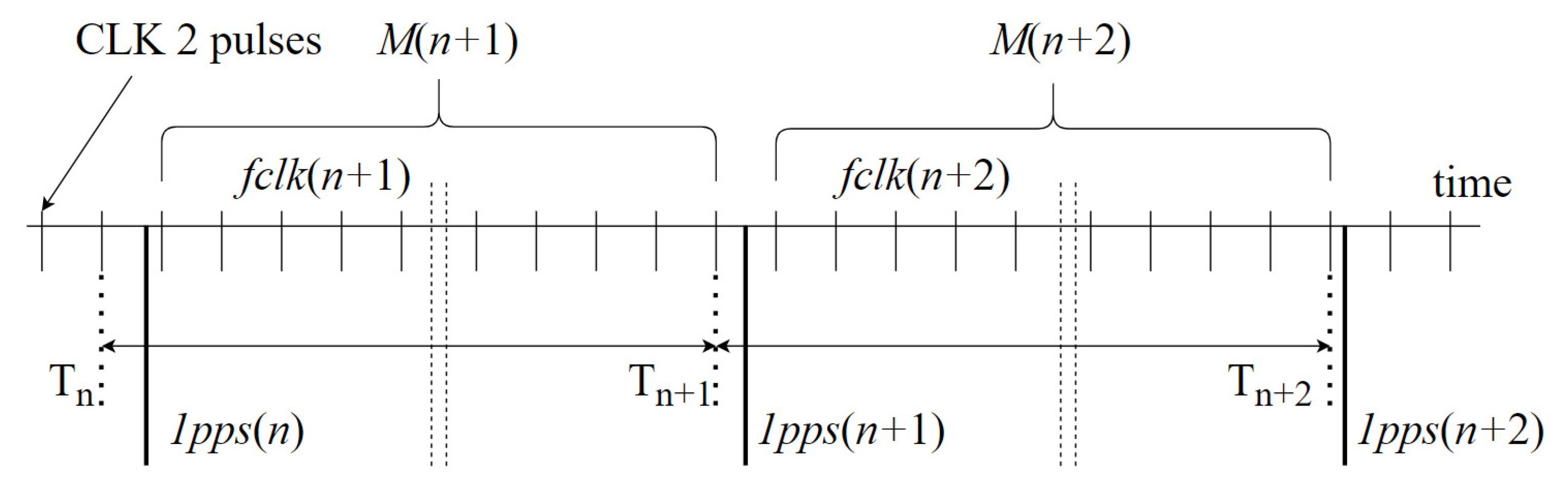

3.2.1. Synchronization Algorithm

- M(n) is the number of CLK 2 pulses counted by TIM2 between consecutive PPS pulses (└┘ denotes an integer part of a number);

- fclk(n) is the frequency of CLK 2 signal between consecutive PPS pulses;

- fnom is the nominal value of CLK 2 signal, equal to 107.520 MHz;

- 1pps(n) is the arrival time of PPS pulse at n-epoch;

- Tn is the moment in time of the last pulse of CLK 2 signal counted before the arrival of PPS pulse;

- K is the frequency averaging time interval length (in seconds);

- ΔU is the increment of TCVCXO tuning voltage computed at each pass of the loop of the synchronization algorithm;

- a and b are the coefficients that ensure proper dynamical characteristics of the synchronization procedure;

- dfclk(t,n) is a term expressing the TCVCXO frequency temperature and aging dependence.

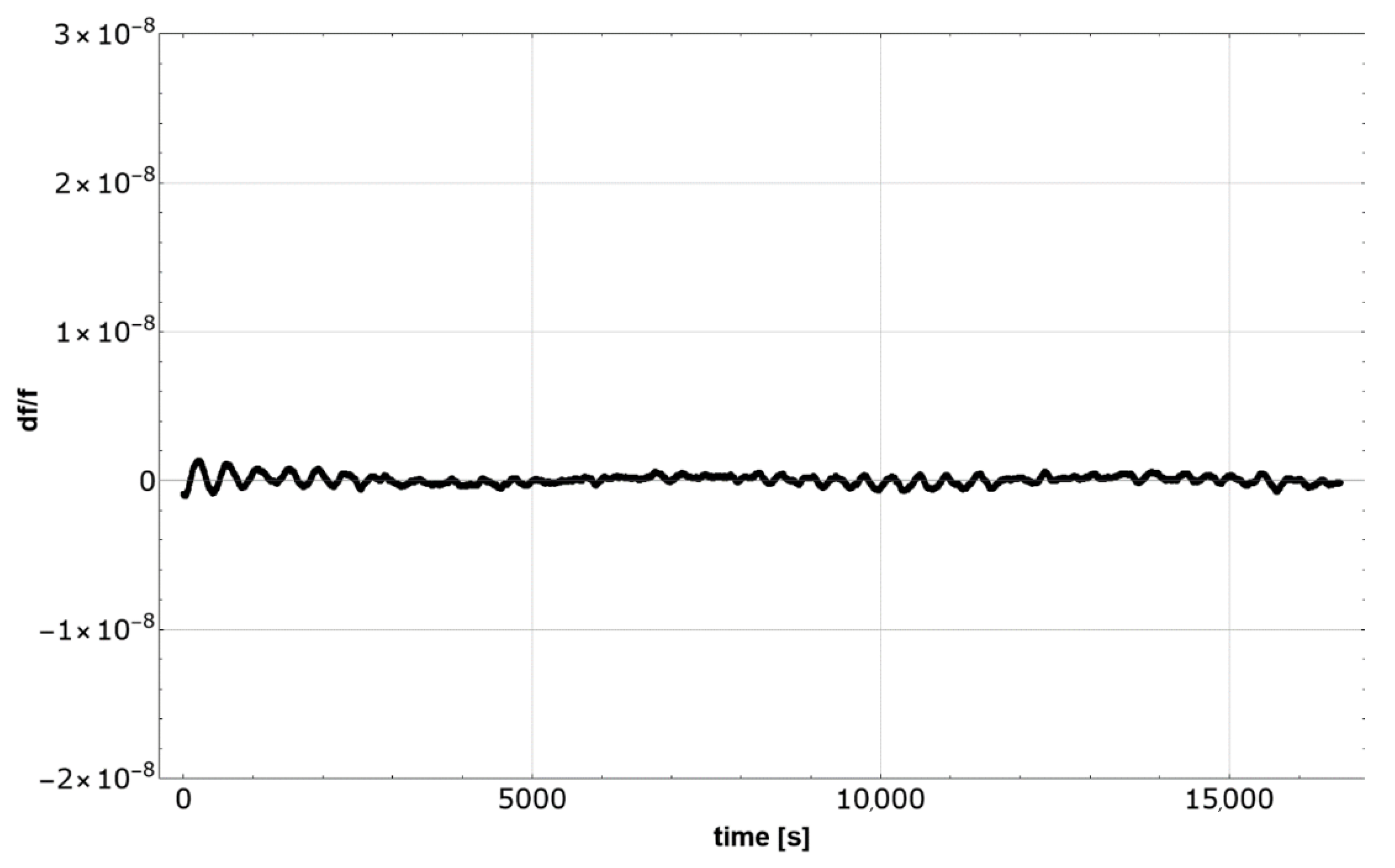

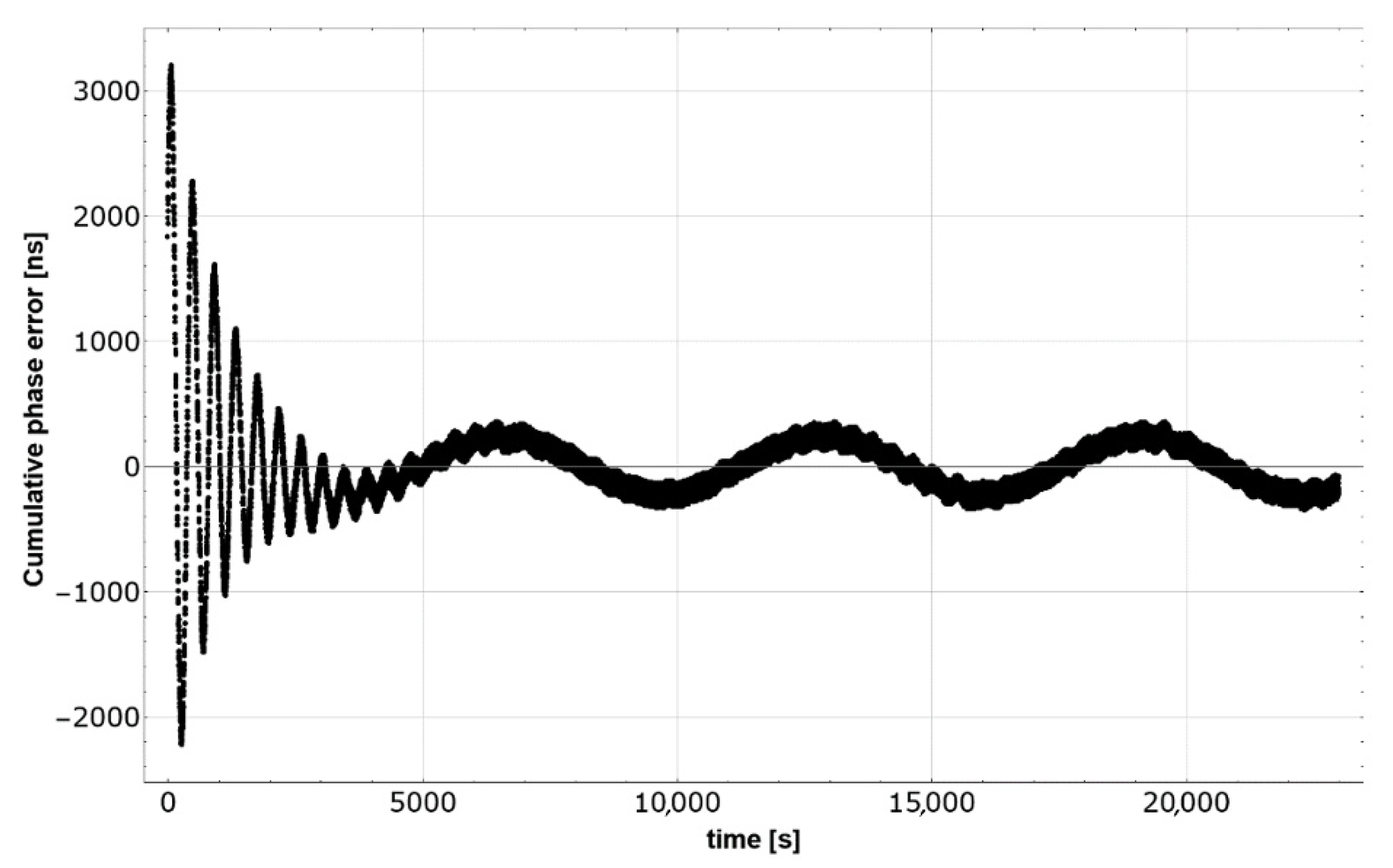

3.2.2. Simulation

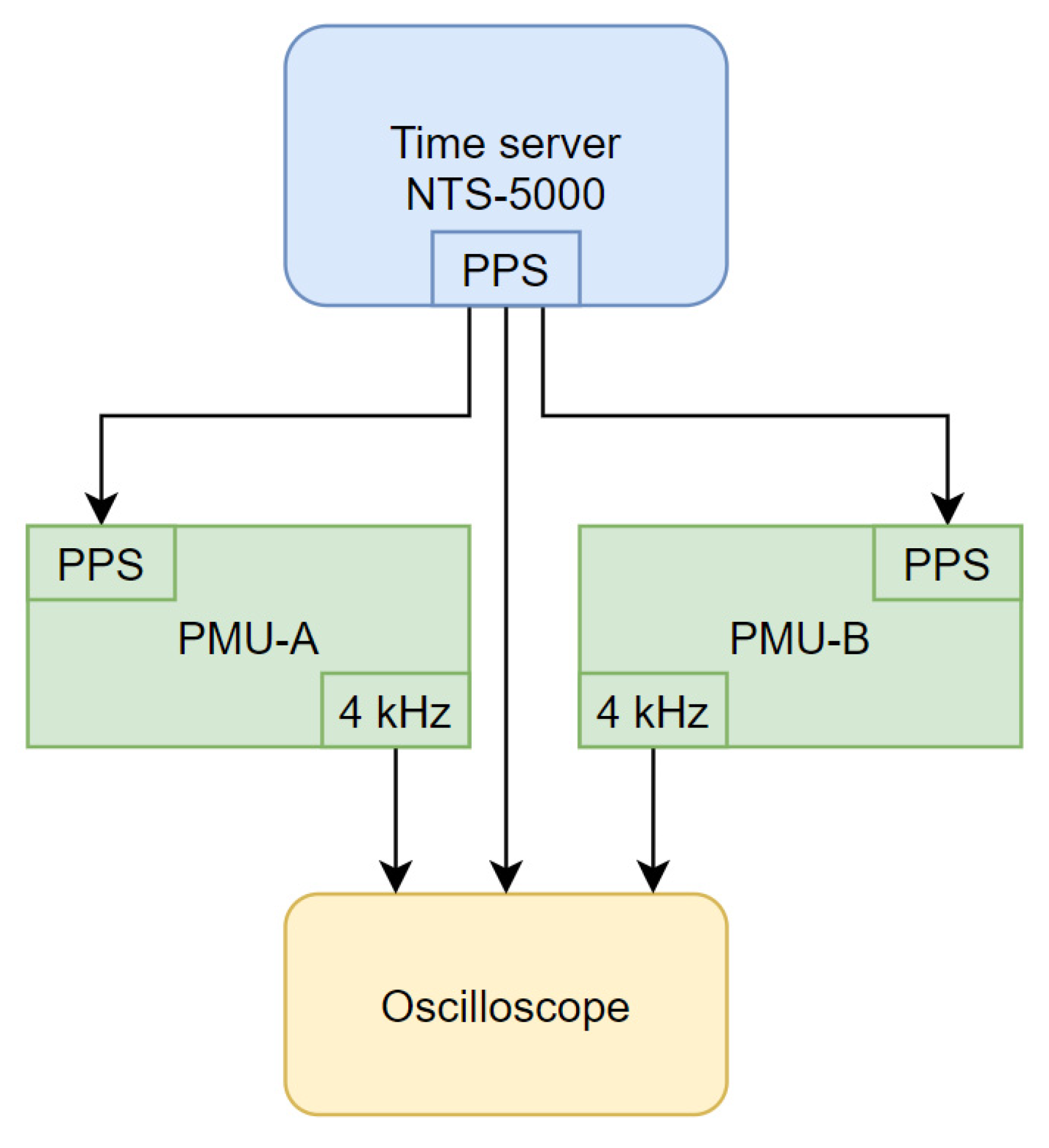

4. Experimental Setup

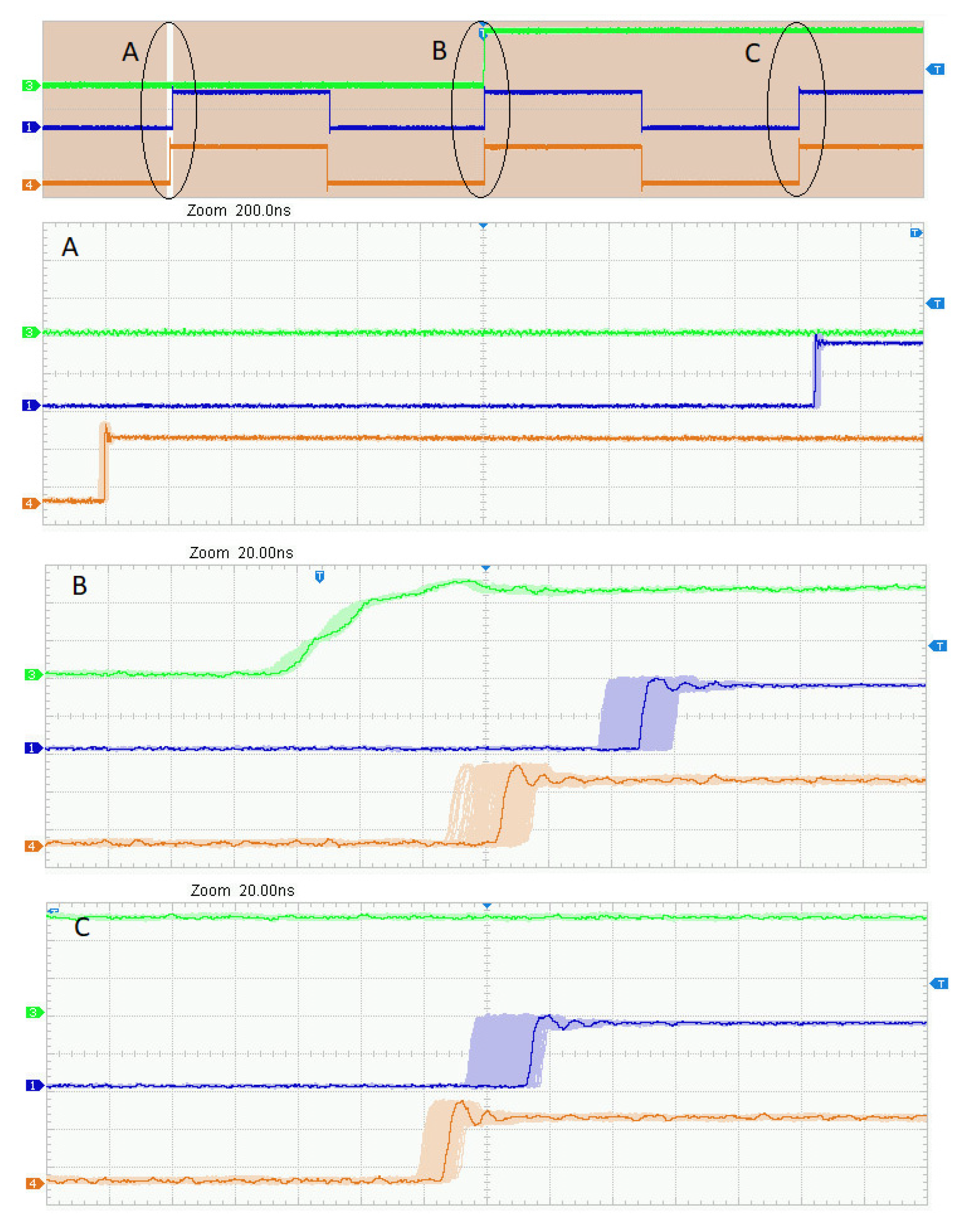

5. Results and Discussion

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Abbreviations

| ADC | Analog to Digital Converter |

| CPLD | Complex Programmable Logic Device |

| CLK | * clock |

| DAC | Digital to Analog Converter |

| FE | Frequency Error |

| FIR | Finite Impulse Response |

| FPGA | Field Programmable Gate Array |

| FRE | rate of change of FRequency Error |

| GPS | Global Positioning System |

| GNSS | Global Navigation Satellite Systems |

| IEC | International Electrotechnical Commission |

| IED | Intelligent Electronic Devices |

| IEEE | Institute of Electrical and Electronics Engineers |

| MU | Merging Unit |

| ns | nanosecond |

| OCXO | Oven Controlled Crystal Oscillator |

| PPS | Pulse Per Second |

| PLL | Phase Lock Loop |

| PTP | Precision Time Protocol |

| PWM | Pulse Width Modulation |

| PMU | Phasor Measurement Units |

| RES | Renewable Energy Sources |

| RMS | Root Mean Square |

| ROCOF | Rate Of Change Of Frequency |

| SPI | Serial Peripheral Interface |

| SV | Sampled Values |

| SCPI | Standard Commands for Programmable Instruments |

| TIE | Time Interval Error |

| TIM | timer |

| TVE | Total Vector Error |

| TCVCXO | Temperature Compensated Voltage Controlled Crystal Oscillator |

| UTC | Coordinated Universal Time |

References

- Lagos, D.; Papaspiliotopoulos, V.; Korres, G.; Hatziargyriou, N. Microgrid Protection Against Internal Faults: Challenges in Islanded and Interconnected Operation. IEEE Power Energy Mag. 2021, 19, 20–35. [Google Scholar] [CrossRef]

- Jones, K.W.; Pourbeik, P.; Kobet, G.; Berner, A.; Fischer, N.; Huang, F.; Holbach, J.; Jensen, M.; O’Connor, J.; Patel, M. Impact of inverter based generation on bulk power system dynamics and short-circuit performance. In Task Force on Short-Circuit and System Performance Impact of Inverter Based Generation; Tech. Rep. PES-TR68; IEEE: Piscataway, NJ, USA, 2018. [Google Scholar]

- IEC/IEEE 60255-118-1-2018; Measuring Relays and Protection Equipment–Part 118-1: Synchro-Phasor for Power Systems–Measurements. IEEE: Piscataway, NJ, USA, 2018.

- Pavičić, I.; Holjevac, N.; Ivanković, I.; Brnobić, D. Model for 400 kV Transmission Line Power Loss As-sessment Using the PMU Measurements. Energies 2021, 14, 5562. [Google Scholar] [CrossRef]

- Xiaotao, C.; Hangli, J.; Qian, S.; Dong, S.; Wujun, H.; Shihui, Y.; Weimin, L.; Yalin, L.; De, S.; Jiang, L. Fault Location Technology of Transmission Line based on Asynchronous Phasor Measurement from PMUs. IOP Conf. Ser. Earth Environ. Sci. 2021, 645, 012084. [Google Scholar] [CrossRef]

- Rong, C.; Cao, C.; Jian, H.; Li, J.; Chen, J. Fault Location Technology of Transmission Line and Asynchronous Phasor Measurement from PMUs. In Proceedings of the 2020 IEEE 4th Conference on Energy Internet and Energy System Integration (EI2), Wuhan, China, 30 October–1 November 2020; pp. 292–297. [Google Scholar]

- Paramo, G.; Bretas, A.; Meyn, S. Research Trends and Applications of PMUs. Energies 2022, 15, 5329. [Google Scholar] [CrossRef]

- Rebello, E.; Vanfretti, L.; Almas, M.S. Experimental testing of a real-time implementation of a PMU-based wide-area damping control system. IEEE Access 2020, 8, 25800–25810. [Google Scholar] [CrossRef]

- Borghetti, A.; Bottura, R.; Barbiroli, M.; Nucci, C.A. Synchrophasors-based distributed secondary voltage/VAR control via cellular network. IEEE Trans. Smart Grid 2016, 8, 262–274. [Google Scholar] [CrossRef]

- Stastny, L.; Franek, L.; Bradac, Z. Time synchronized low-voltage measurements for smart grids. Procedia Eng. 2015, 100, 1389–1395. [Google Scholar] [CrossRef]

- Del Prete, S.; Delle Femine, A.; Gallo, D.; Landi, C.; Luiso, M. Implementation of a distributed stand alone merging unit. J. Phys. Conf. Ser. 2018, 1065, 052042. [Google Scholar] [CrossRef]

- Ozansoy, C.R.; Zayegh, A.; Kalam, A. Time synchronisation in a IEC 61850 based substation automation system. In Proceedings of the 2008 Australasian Universities Power Engineering Conference, Sydney, Australia, 14–17 December 2008; pp. 1–7. [Google Scholar]

- IEC 61850-5:2013; Communication requirements for functions and device models. International Electrotechnical Commission: Geneva, Switzerland, 2013. Available online: https://webstore.iec.ch/publication/6012 (accessed on 12 September 2022).

- Liu, Z.; Chen, X.; Liu, J.; Li, C. High precision clock bias prediction model in clock synchronization system. Math. Probl. Eng. 2016, 2016, 1813403. [Google Scholar] [CrossRef]

- Shmaliy, Y.S.; Ibarra-Manzano, O. Clock current state estimation with a Kalman-like algorithm employing measurement of time errors. In Proceedings of the 2011 Joint Conference of the IEEE International Frequency Control and the European Frequency and Time Forum (FCS) Proceedings, San Francisco, CA, USA, 1–5 May 2011; pp. 1–4. [Google Scholar] [CrossRef]

- Arceo-Miquel, L.; Shmaliy, Y.S.; Ibarra-Manzano, O. Optimal synchronization of local clocks by GPS 1PPS signals using predictive FIR filters. IEEE Trans. Instrum. Meas. 2009, 58, 1833–1840. [Google Scholar] [CrossRef]

- Bui, T.Q.T.; Elango, A.; Landry, R.J. FPGA-Based Autonomous GPS-Disciplined Oscillators for Wireless Sensor Network Nodes. Sensors 2022, 22, 3135. [Google Scholar] [CrossRef] [PubMed]

- Boehmer, T.J.; Bilén, S.G. Low-Power GPS-Disciplined Oscillator Module for Distributed Wireless Sensor Nodes. Electronics 2021, 10, 716. [Google Scholar] [CrossRef]

- Pawłowski, E.; Warda, P. Method and system for disciplining a local reference oscillator by GPS 1PPS signal. Przegląd Elektrotechniczny 2018, 7, 94. [Google Scholar] [CrossRef]

- Yao, W.; Zhan, L.; Liu, Y.; Till, M.J.; Zhao, J.; Wu, L.; Teng, Z.; Liu, Y. A novel method for phasor measurement unit sampling time error compensation. IEEE Trans. Smart Grid 2016, 9, 1063–1072. [Google Scholar] [CrossRef]

- Connor-Winfield’s FTS250-HP GPS Disciplined Oscillator. Available online: http://www.conwin.com/datasheets/sg/sg176.pdf (accessed on 12 September 2022).

| IEC Time Synchronization Class | Time Synchronization Accuracy Requirements |

|---|---|

| T1 | ±1 ms |

| T2 | ±0.1 ms |

| T3 | ±25 μs |

| T4 | ±4 μs |

| T5 | ±1 μs |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Makowiecki, K.; Lisowiec, A.; Michalski, P.; Habrych, M. UTC Synchronized Signal Generation for Synchrophasors and Sampled Values Measurements. Energies 2022, 15, 7095. https://doi.org/10.3390/en15197095

Makowiecki K, Lisowiec A, Michalski P, Habrych M. UTC Synchronized Signal Generation for Synchrophasors and Sampled Values Measurements. Energies. 2022; 15(19):7095. https://doi.org/10.3390/en15197095

Chicago/Turabian StyleMakowiecki, Karol, Aleksander Lisowiec, Pawel Michalski, and Marcin Habrych. 2022. "UTC Synchronized Signal Generation for Synchrophasors and Sampled Values Measurements" Energies 15, no. 19: 7095. https://doi.org/10.3390/en15197095

APA StyleMakowiecki, K., Lisowiec, A., Michalski, P., & Habrych, M. (2022). UTC Synchronized Signal Generation for Synchrophasors and Sampled Values Measurements. Energies, 15(19), 7095. https://doi.org/10.3390/en15197095