High Performance 3.3 kV SiC MOSFET Structure with Built-In MOS-Channel Diode

Abstract

:1. Introduction

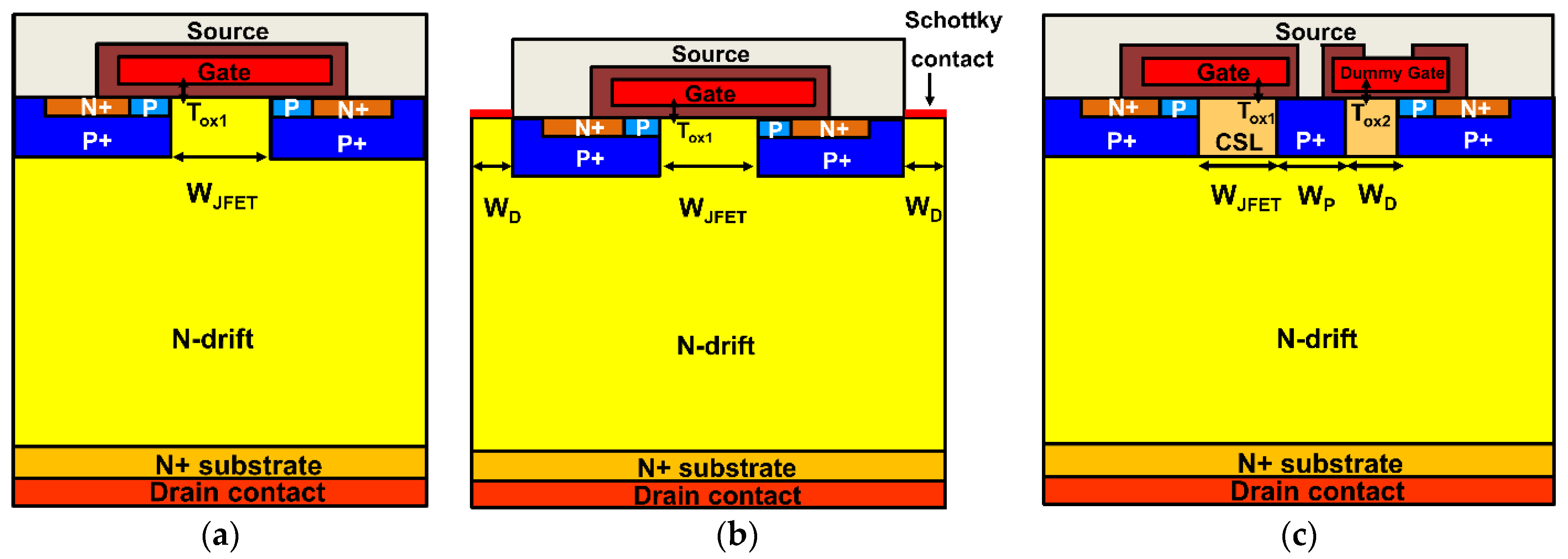

2. Device Optimizations and Methods

3. Simulation Results and Analysis

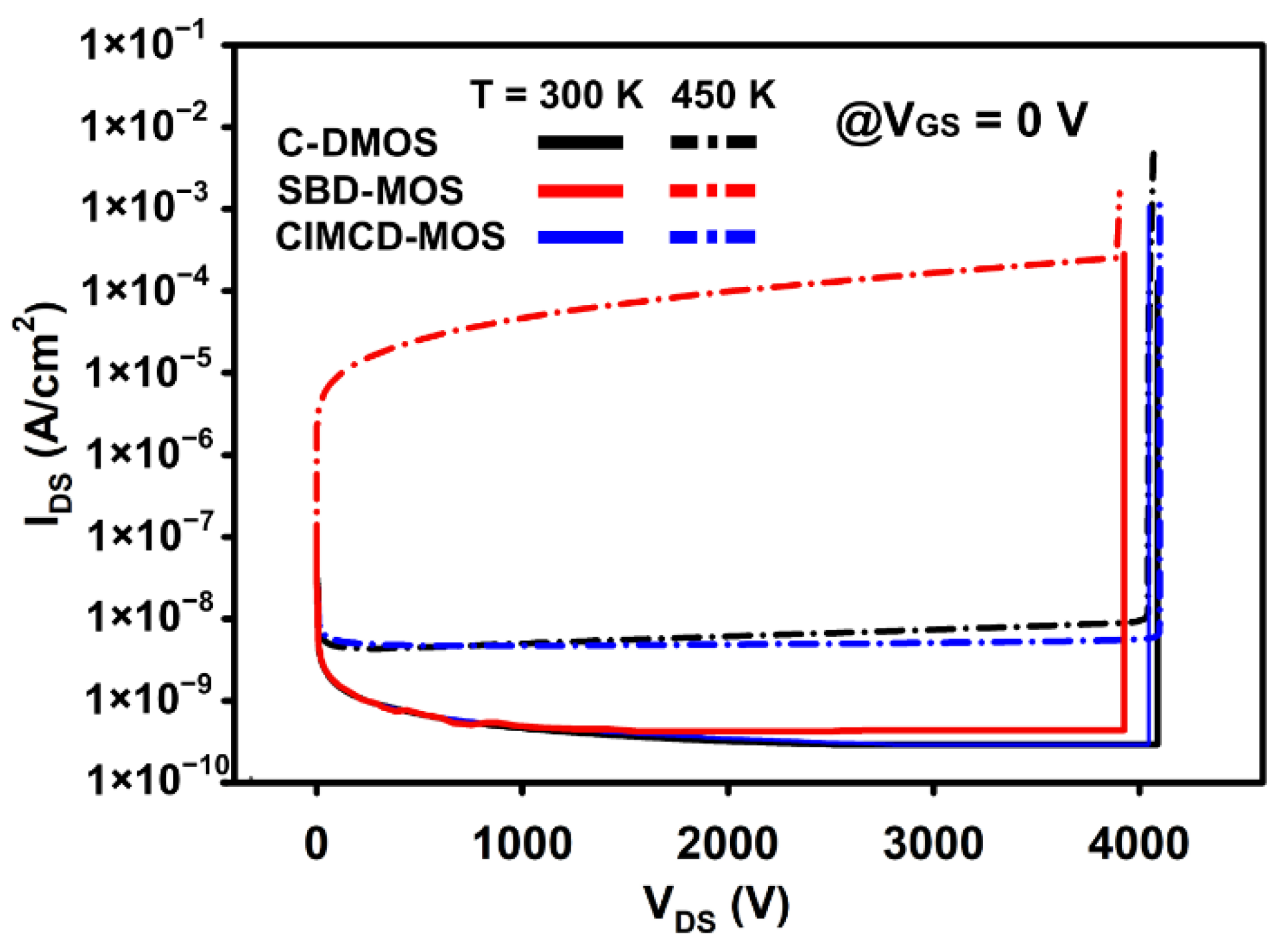

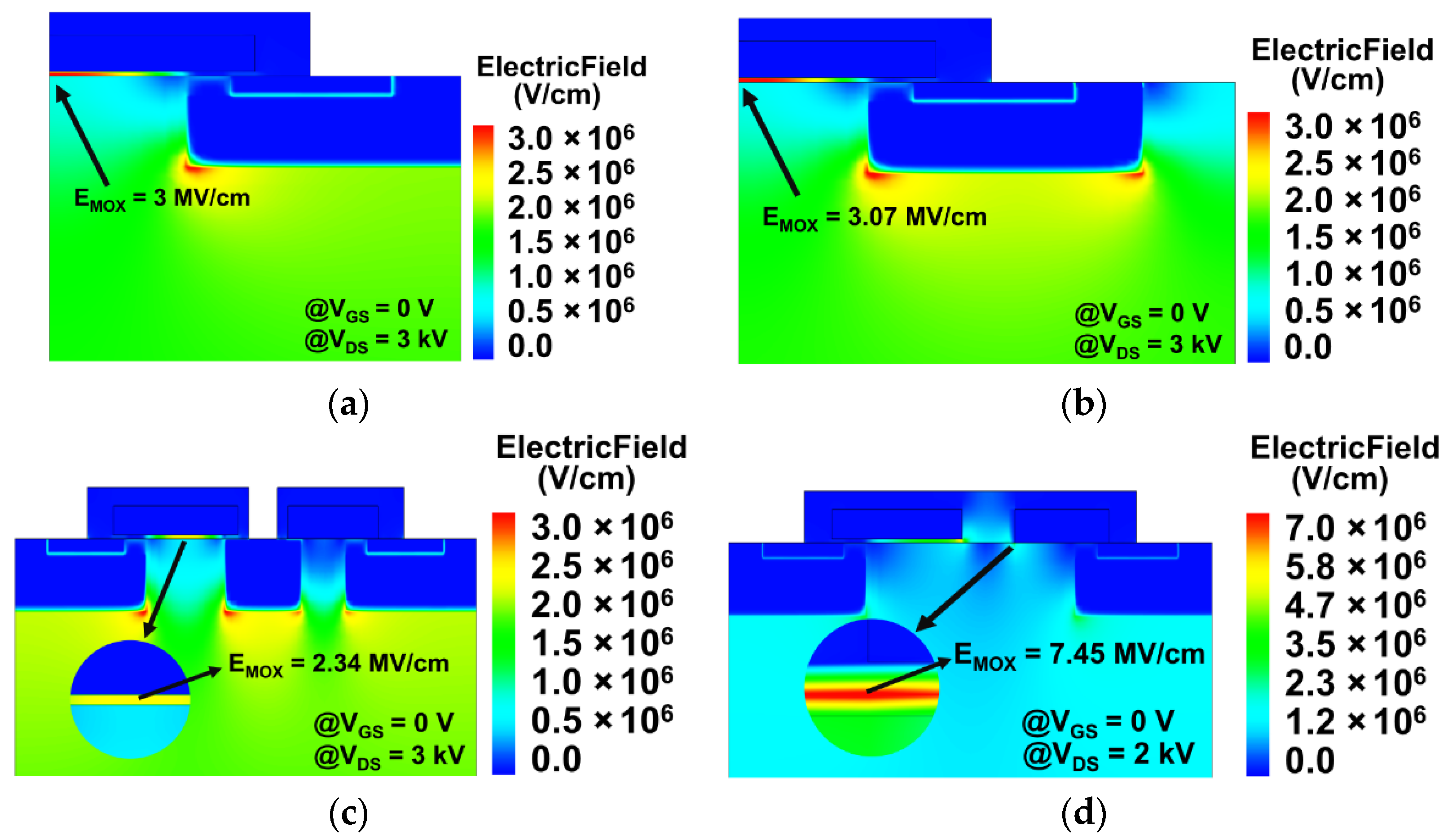

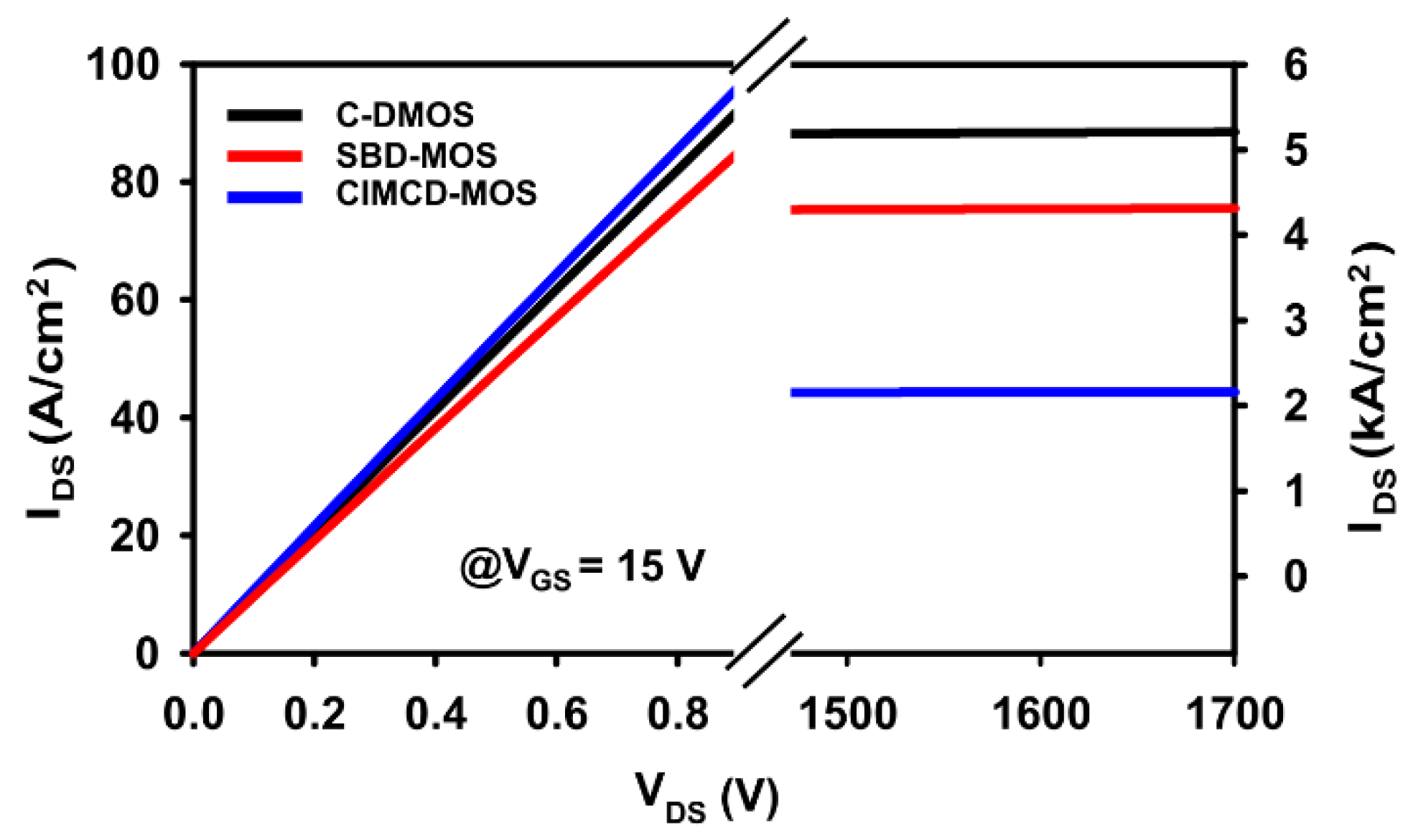

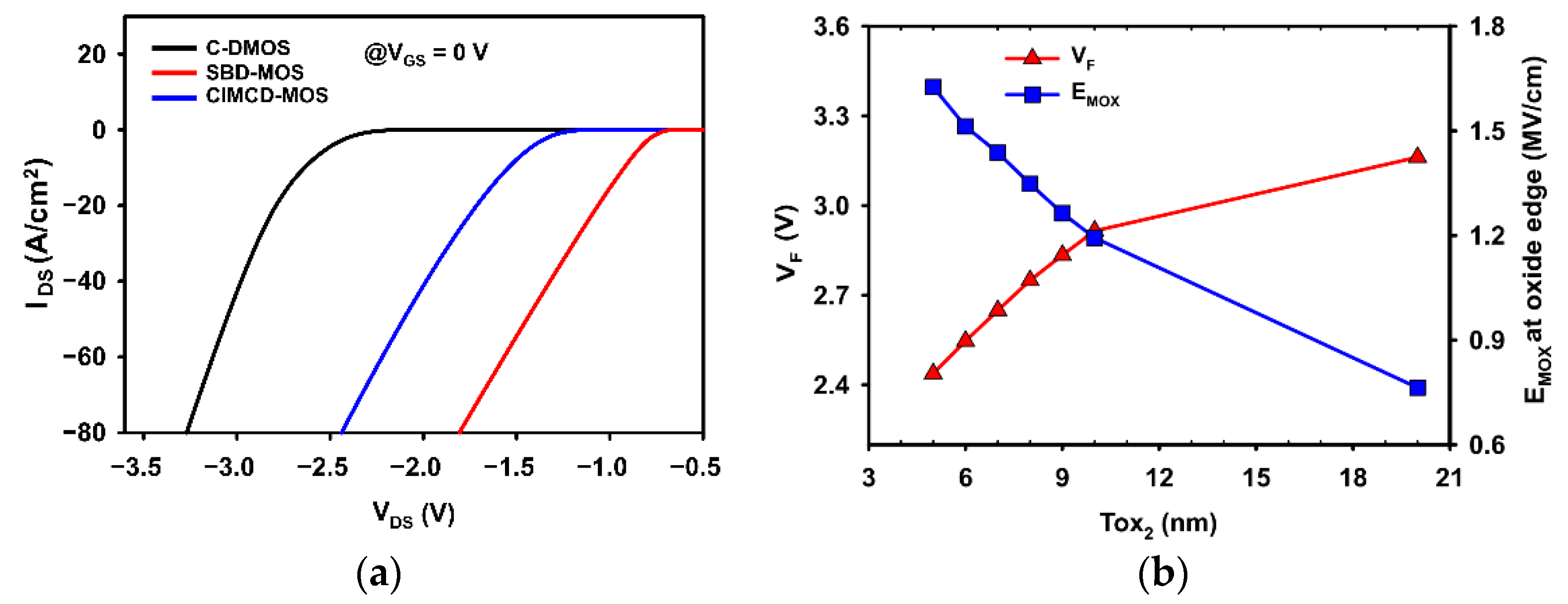

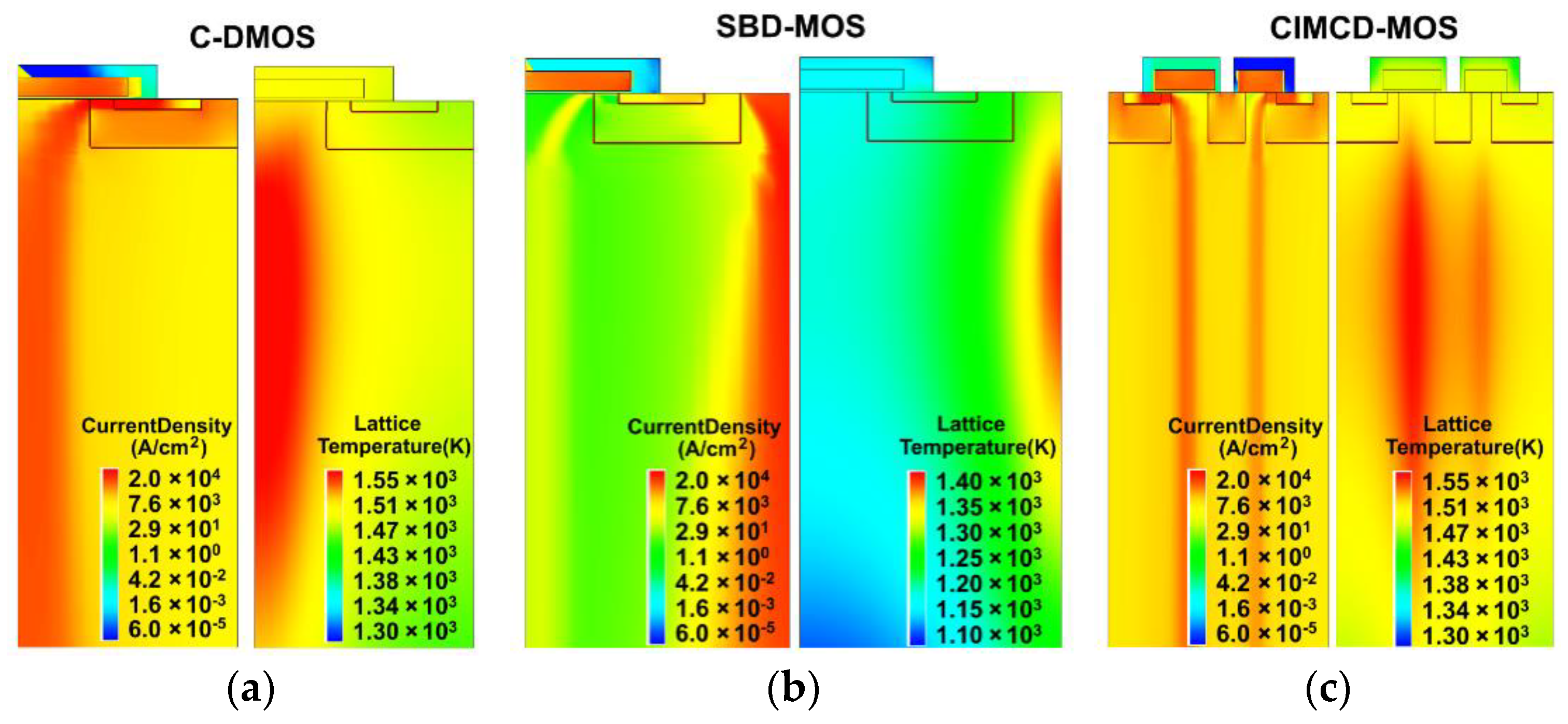

3.1. Static Performances

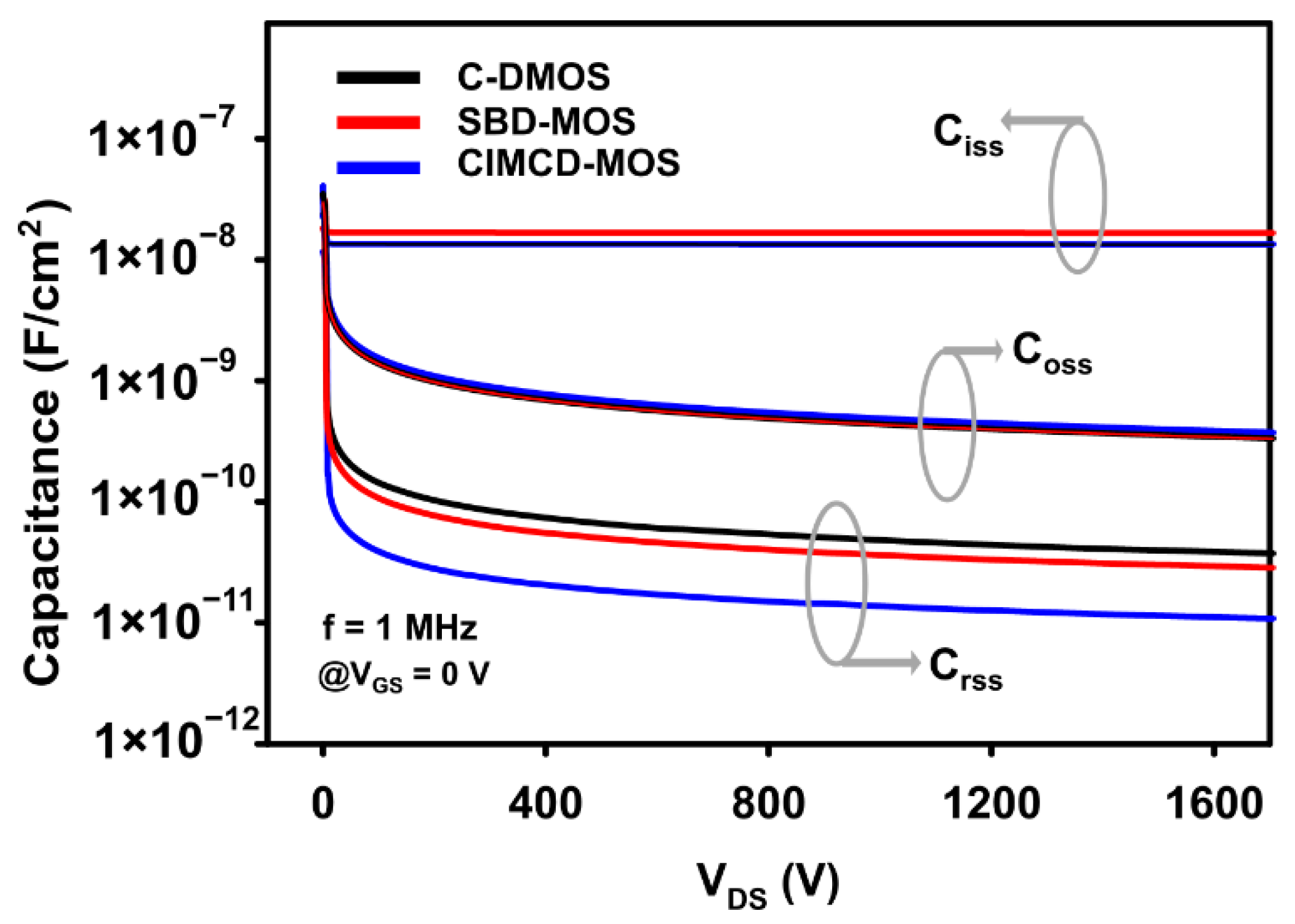

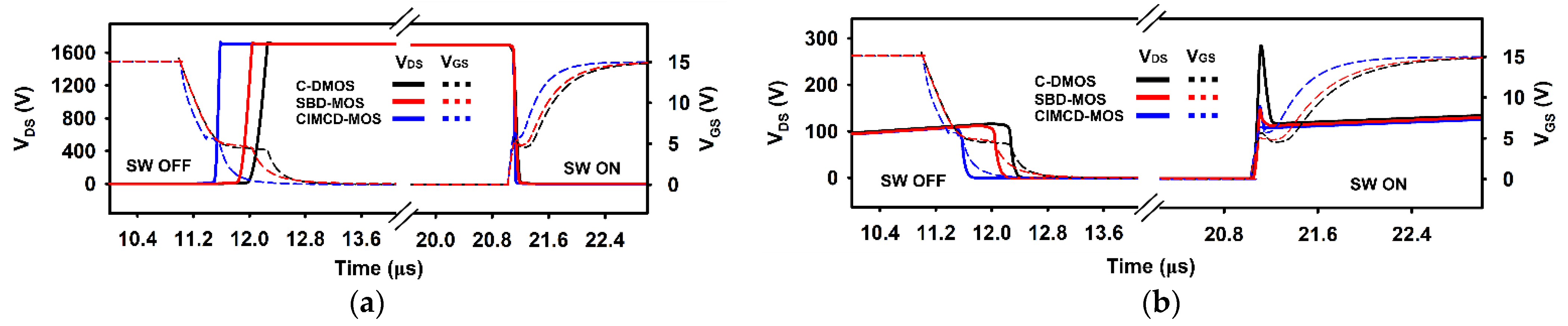

3.2. Dynamic Performances

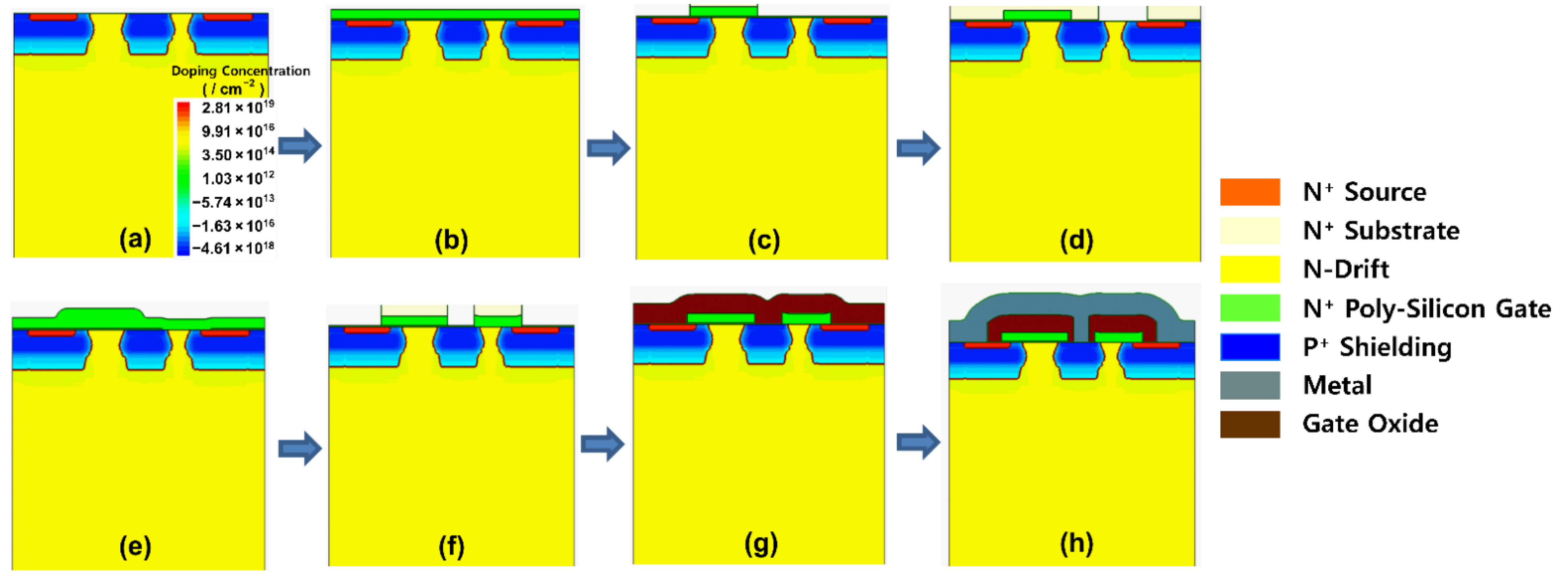

3.3. Proposed Fabrication Process

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Chow, T.P. Wide bandgap semiconductor power devices for energy efficient systems. In Proceedings of the 2015 IEEE 3rd Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Blacksburg, VA, USA, 2–4 November 2015; pp. 402–405. [Google Scholar]

- Cooper, J.A.; Agarwal, A. SiC power-switching devices-the second electronics revolution? Proc. IEEE 2002, 90, 956–968. [Google Scholar] [CrossRef]

- Baliga, B.J. Silicon Carbide Power Devices; World Scientific: Singapore, 2006; pp. 15–36. [Google Scholar]

- Wang, G.; Wang, F.; Magai, G.; Lei, Y.; Huang, A.; Das, M. Performance comparison of 1200V 100A SiC MOSFET and 1200 V 100 A silicon IGBT. In Proceedings of the 2013 IEEE Energy Conversion Congress and Exposition, Denver, CO, USA, 16–20 September 2013; pp. 3230–3234. [Google Scholar]

- Guan, Q.X.; Li, C.; Zhang, Y.; Wang, S.; Xu, D.D.; Li, W.; Ma, H. An Extremely High Efficient Three-Level Active Neutral-Point-Clamped Converter Comprising SiC and Si Hybrid Power Stages. IEEE Trans. Power Electron. 2018, 33, 8341–8352. [Google Scholar] [CrossRef]

- Fuentes, C.D.; Kouro, S.; Bernet, S. Comparison of 1700-V SiC-MOSFET and Si-IGBT Modules under Identical Test Setup Conditions. IEEE Trans. Ind. App. 2019, 55, 7765–7775. [Google Scholar] [CrossRef]

- Zhang, L.; Yuan, X.; Wu, X.; Shi, C.; Zhang, J.; Zhang, Y. Performance Evaluation of Hgih-Power SiC MOSFET Modules in Comparison to Si IGBT Modules. IEEE Trans. Power Electron. 2019, 34, 1181–1196. [Google Scholar] [CrossRef]

- Sabri, S.; Van Brunt, E.; Barkley, A.; Hull, B.; O’Loughlin, M.; Burk, A.; Allen, S.; Palmour, J. New generation 6.5 kV SiC power MOSFET. In Proceedings of the 2017 IEEE 5th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Albuquerque, NM, USA, 30 October–1 November 2017; pp. 246–250. [Google Scholar]

- Sakaguchi, T.; Aketa, M.; Nakamura, T.; Nakanishi, M.; Rahimo, M. Characterization of 3.3 kV and 6.5 kV SiC MOSFETs. In Proceedings of the PCIM Europe 2017, International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 16–18 May 2017; pp. 1–5. [Google Scholar]

- Horff, R.; März, A.; Lechler, M.; Bakran, M. Optimised switching of a SiC MOSFET in a VSI using the body diode and additional Schottky barrier diode. In Proceedings of the 2015 17th European Conference on Power Electronics and Applications (EPE’15 ECCE-Europe), Geneva, Switzerland, 8–10 September 2015; pp. 1–11. [Google Scholar]

- Efthymiou, L.; Camuso, G.; Longobardi, G.; Udrea, F.; Lin, E.; Chien, T.; Chen, M. Zero reverse recovery in SiC and GaN Schottky diodes: A comparison. In Proceedings of the 2016 28th International Symposium on Power Semiconductor Devices and IC’s (ISPSD), Prague, Czech Republic, 12–16 June 2016; pp. 71–74. [Google Scholar]

- Dyer, J.; Zhang, Z.; Wang, F.; Costinett, D.; Tolbert, L.M.; Blalock, B.J. Dead-time optimization for SiC based voltage source converters using online condition monitoring. In Proceedings of the 2017 IEEE 5th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Albuquerque, NM, USA, 30 October–1 November 2017; pp. 15–19. [Google Scholar]

- Ahmed, M.R.; Todd, R.; Forsyth, A.J. Switching performance of a SiC MOSFET body diode and SiC schottky diodes at different temperatures. In Proceedings of the 2017 IEEE Energy Conversion Congress and Exposition (ECCE), Cincinnati, OH, USA, 1–6 October 2017; pp. 5487–5494. [Google Scholar]

- Badawi, N.; Bahat-Treidel, E.; Dieckerhoff, S.; Hilt, O.; Würfl, J. Evaluation of 600V GaN and SiC Schottky diodes at different temperatures. In Proceedings of the 15th European Conference on Power Electronics and Applications (EPE), Lille, France, 2–6 September 2013; pp. 1–7. [Google Scholar]

- Jiang, X.; Wang, J.; Chen, J.; Li, Z.; Zhai, D.; Yang, X.; Bing, J.; Shen, Z.J. Investigation on Degradation of SiC MOSFET Under Surge Current Stress of Body Diode. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 77–89. [Google Scholar] [CrossRef]

- Kawahara, K.; Hino, S.; Sadamatsu, K.; Nakao, Y.; Iwamatsu, T.; Nakata, S.; Tomohisa, S.; Yamakawa, S. Impact of Embedding Schottky Barrier Diodes into 3.3 kV and 6.5 kV SiC MOSFETs. Mater. Sci. Forum 2017, 924, 663–666. [Google Scholar] [CrossRef]

- Wang, Z.; Ouyang, J.; Zhang, J.; Wu, X.; Sheng, K. Analysis on reverse recovery characteristic of SiC MOSFET intrinsic diode. In Proceedings of the 2014 IEEE Energy Conversion Congress and Exposition (ECCE), Pittsburgh, PA, USA, 14–18 September 2014; pp. 2832–2837. [Google Scholar]

- Nayak, D.P.; Yakala, R.K.; Kumar, M.; Pramanick, S.K. Temperature-Dependent Reverse Recovery Characterization of SiC MOSFETs Body Diode for Switching Loss Estimation in a Half–Bridge. IEEE Trans. Power Electron. 2022, 37, 5574–5582. [Google Scholar] [CrossRef]

- Tominaga, T.; Hino, S.; Mitsui, Y.; Nakashima, J.; Kawahara, K.; Tomohisa, S.; Miura, N. Superior Switching Characteristics of SiC-MOSFET Embedding SBD. In Proceedings of the 2019 31st International Symposium on Power Semiconductor Devices and IC’s (ISPSD), Shanghai, China, 19–23 May 2019; pp. 27–30. [Google Scholar]

- Matsui, K.; Aiba, R.; Yano, H.; Iwamuro, N.; Baba, M.; Harada, S. Comprehensive Study on Electrical Characteristics in 1.2 kV SiC SBD-integrated Trench and Planar MOSFETs. In Proceedings of the 2021 33rd International Symposium on Power Semiconductor Devices and IC’s (ISPSD), Nagoya, Japan, 30 May–3 June 2021; pp. 215–218. [Google Scholar]

- Li, X.; Tong, X.; Huang, A.Q.; Tao, H.; Zhou, K.; Jiang, Y.; Jiang, J.; Deng, X.; She, X.; Zhang, B.; et al. SiC Trench MOSFET With Integrated Self-Assembled Three-Level Protection Schottky Barrier Diode. IEEE Trans. Electron Devices 2018, 65, 347–351. [Google Scholar] [CrossRef]

- Hsu, F.J.; Yen, C.T.; Hung, C.C.; Hung, H.T.; Lee, C.Y.; Lee, L.S.; Huang, Y.-F.; Chen, T.-L.; Chuang, P.-J. High efficiency high reliability SiC MOSFET with monolithically integrated Schottky rectifier. In Proceedings of the 2017 29th International Symposium on Power Semiconductor Devices and IC’s (ISPSD), Sapporo, Japan, 28 May–1 June 2017; pp. 45–48. [Google Scholar]

- Yen, C.T.; Hung, C.C.; Hung, H.T.; Lee, L.S.; Lee, C.Y.; Yang, T.M.; Huang, Y.-F.; Cheng, C.-Y.; Chuang, P.-J. 1700 V/30 A 4H-SiC MOSFET with low cut–in voltage embedded diode and room temperature boron implanted termination. In Proceedings of the 2015 IEEE 27th International Symposium on Power Semiconductor Devices & IC’s (ISPSD), Hong Kong, China, 10–14 May 2015; pp. 265–268. [Google Scholar]

- Nicholls, J.; Dimitrijev, S.; Tanner, P.; Han, J. Description and verification of the fundamental current mechanisms in silicon carbide Schottky barrier diodes. Sci. Rep. 2019, 9, 1–9. [Google Scholar] [CrossRef]

- Saitoh, H.S.; Kimoto, T.; Matsunami, H. Origin of leakage current in SiC Schottky barrier diodes at high temperature. Mater. Sci. Forum 2004, 457, 997–1000. [Google Scholar] [CrossRef]

- Hatakeyama, T.; Kushibe, M.; Watanabe, T.; Imai, S.; Shinohe, T. Optimum Design of a SiC Schottky Barrier Diode Considering Reverse Leakage Current due to a Tunneling Process. Mater. Sci. Forum 2003, 433, 831–834. [Google Scholar] [CrossRef]

- Wang, Y.; Ma, Y.-C.; Hao, Y.; Hu, Y.; Wang, G.; Cao, F. Simulation Study of 4H-SiC UMOSFET Structure With P+-PolySi/SiC Shielded Region. IEEE Trans. Electron Devices 2017, 64, 3719–3724. [Google Scholar] [CrossRef]

- An, J.; Hu, S. Heterojunction Diode Shielded SiC Split-Gate Trench MOSFET with Optimized Reverse Recovery Characteristic and Low Switching Loss. IEEE Access 2019, 7, 28592–28596. [Google Scholar] [CrossRef]

- Liang, S.; Yu, H.; Liu, H.; Wang, Y.; Wang, J. A novel SiC power MOSFET with integrated polySi/SiC heterojunction freewheeling diode. Semicond. Sci. Tech. 2021, 36, 095017. [Google Scholar] [CrossRef]

- Yu, H.; Liang, S.; Liu, H.; Wang, J.; Shen, Z.J. Numerical Study of SiC MOSFET With Integrated n-/n-Type Poly-Si/SiC Heterojunction Freewheeling Diode. IEEE Trans. Electron Devices 2021, 68, 4571–4576. [Google Scholar] [CrossRef]

- Wang, Y.; Wang, H.; Cao, F.; Wang, H. High Performance of Polysilicon/4H–SiC Dual–Heterojunction Trench Diode. IEEE Trans. Electron Devices 2017, 64, 1653–1659. [Google Scholar] [CrossRef]

- Zhou, X.; Gong, H.; Jia, Y.; Hu, D.; Wu, Y.; Xia, T.; Pang, H.; Zhao, Y. SiC Planar MOSFETs With Built-In Reverse MOS-Channel Diode for Enhanced Performance. IEEE J. Electron Devices Soc. 2020, 8, 619–625. [Google Scholar] [CrossRef]

- Zhou, X.; Pang, H.; Jia, Y.; Hu, D.; Wu, Y.; Tang, Y.; Xia, T.; Gong, H.; Zhao, Y. SiC Double-Trench MOSFETs With Embedded MOS-Channel Diode. IEEE Trans. Electron Devices 2020, 67, 582–587. [Google Scholar] [CrossRef]

- Deng, X.; Xu, X.; Li, X.; Li, X.; Wen, Y.; Chen, W. A Novel SiC MOSFET Embedding Low Barrier Diode With Enhanced Third Quadrant and Switching Performance. IEEE Electron Device Lett. 2020, 41, 1472–1475. [Google Scholar] [CrossRef]

- Nguyen, T.-T.; Ahmed, A.; Thang, T.V.; Park, J.-H. Gate Oxide Reliability Issues of SiC MOSFETs Under Short-Circuit Operation. IEEE Trans. Power Electron. 2015, 30, 2445–2455. [Google Scholar] [CrossRef]

- Vudumula, P.; Kotamraju, S. Design and Optimization of 1.2-kV SiC Planar Inversion MOSFET Using Split Dummy Gate Concept for High-Frequency Applications. IEEE Trans. Electron Devices 2019, 66, 5266–5271. [Google Scholar] [CrossRef]

- Agarwal, A.; Baliga, B.J.; Francois, M.M.A.; Maxwell, E.; Berliner, N.; Papageorge, M. 3.3 kV 4H-SiC Planar-Gate MOSFETs Manufactured using Gen-5 PRESICETM Technology in a 4-inch Wafer Commercial Foundry. In Proceedings of the SoutheastCon 2021, Atlanta, GA, USA, 10–14 March 2021; pp. 1–4. [Google Scholar]

- Jiang, H.; Wei, J.; Dai, X.; Ke, M.; Zheng, C.; Deviny, I. Silicon carbide split-gate MOSFET with merged Schottky barrier diode and reduced switching loss. In Proceedings of the 2016 28th International Symposium on Power Semiconductor Devices and IC’s (ISPSD), Prague, Czech Republic, 12–16 June 2016; pp. 59–62. [Google Scholar]

- Lee, S.K.; Zetterling, C.M.; Östling, M. Schottky barrier height dependence on the metal work function for p-type Si Schottky diodes. J. Electron. Mater. 2004, 30, 242–246. [Google Scholar] [CrossRef]

- Yi, B.; Wu, Z.; Zhang, Q.; Cheng, J.J.; Huang, H.M.; Pan, Y.L.; Zhang, X.K.; Xiang, Y. A low loss single-channel SiC trench MOSFET with integrated trench MOS barrier Schottky diode. Semicond. Sci. Technol. 2021, 36, 075006. [Google Scholar] [CrossRef]

- Vudumula, P.; Kotamraju, S. Design and Optimization of SiC Super-Junction MOSFET Using Vertical Variation Doping Profile. IEEE Trans. Electron Devices 2019, 66, 1402–1408. [Google Scholar] [CrossRef]

- Hatakeyama, T.; Nishio, J.; Ota, C.; Shinohe, T. Physical Modeling and Scaling Properties of 4H-SiC Power Devices. In Proceedings of the 2005 International Conference on Simulation of Semiconductor Processes and Devices, Tokyo, Japan, 1–3 September 2005; pp. 171–174. [Google Scholar]

- Synopsys, Inc. TCAD SentaurusTM Device User Guide; Synopsys, Inc.: Mountain View, CA, USA, 2017. [Google Scholar]

- Ueno, K.; Asai, R.; Tsuji, T. 4H-SiC MOSFETs utilizing the H2 surface cleaning technique. IEEE Electron Device Lett. 1998, 19, 244–246. [Google Scholar] [CrossRef]

- An, J.; Hu, S. Experimental and Theoretical Demonstration of Temperature Limitation for 4H-SiC MOSFET during Unclamped Inductive Switching. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 206–214. [Google Scholar] [CrossRef]

- Schoen, K.P.; Woodall, J.M.; Cooper, J.A.; Melloch, M.R. Design considerations and experimental analysis of high-voltage SiC Schottky barrier rectifiers. IEEE Trans. Electron Devices 1998, 45, 1595–1604. [Google Scholar] [CrossRef]

- Jiang, H.; Wei, J.; Dai, X.; Ke, M.; Deviny, I.; Mawby, P. SiC Trench MOSFET With Shielded Fin-shaped Gate to Reduce Oxide Field and Switching Loss. IEEE Electron Device Lett. 2016, 37, 1324–1327. [Google Scholar] [CrossRef]

- Han, K.; Kanale, A.; Baliga, B.J.; Ballard, B.; Morgan, A.; Hopkins, D.C. New Short Circuit Failure Mechanism for 1.2kV 4H-SiC MOSFETs and JBSFETs. In Proceedings of the 2018 IEEE 6th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Atlanta, GA, USA, 31 October–2 November 2018; pp. 108–113. [Google Scholar]

- Namai, M.; An, J.; Yano, H.; Iwamuro, N. Investigation of short-circuit failure mechanisms of SiC MOSFETs by varying DC bus voltage. Jpn. J. Appl. Phys. 2018, 57, 074102. [Google Scholar] [CrossRef]

- Okawa, M.; Aiba, R.; Kanamori, T.; Kobayashi, Y.; Harada, S.; Yano, H.; Iwamuro, N. First Demonstration of Short–Circuit Capability for a 1.2 kV SiC SWITCH–MOS. IEEE J. Electron Devices Soc. 2019, 7, 613–620. [Google Scholar] [CrossRef]

- Aiba, R.; Matsui, K.; Baba, M.; Harada, S.; Yano, H.; Iwamuro, N. Demonstration of Superior Electrical Characteristics for 1.2 kV SiC Schottky Barrier Diode-Wall Integrated Trench MOSFET With Higher Schottky Barrier Height Metal. IEEE Electron Device Lett. 2020, 41, 1810–1813. [Google Scholar] [CrossRef]

- Jiang, J.-Y.; Huang, C.-F.; Wu, T.-L.; Zhao, F. Simulation Study of 4H–SiC Trench MOSFETs with Various Gate Structures. In Proceedings of the 2019 Electron Devices Technology and Manufacturing Conference (EDTM), Singapore, 12–15 March 2019; pp. 401–403. [Google Scholar]

- Yue, K.; Pang, L.; You, H.; Li, S.; Kong, D.; Li, Y.; Zhang, Q.; Liu, L. Reverse recovery characteristics of high power thyristors in HVDC converter valve. IEEE Trans. Dielectr. Electr. Insul. 2017, 24, 2132–2140. [Google Scholar] [CrossRef]

- Tian, K.; Hallén, A.; Qi, J.; Ma, S.; Fei, X.; Zhang, A.; Liu, W. An Improved 4H-SiC Trench-Gate MOSFET With Low On-Resistance and Switching Loss. IEEE Trans. Electron Devices 2019, 66, 2307–2313. [Google Scholar] [CrossRef]

- Shen, H.-J.; Tang, Y.-C.; Peng, Z.-Y.; Deng, X.-C.; Bai, Y.; Wang, Y.-Y.; Li, C.-Z.; Liu, K.-A.; Liu, X.-Y. Fabrication and Characterization of 1700 V 4H-SiC Vertical Double-Implanted Metal-Oxide-Semiconductor Field-Effect Transistors. Chin. Phys. 2015, 32, 127101. [Google Scholar] [CrossRef]

- Singh, R.; Capell, D.; Das, M.; Lipkin, L.; Palmour, J. Development of high-current 4H-SiC ACCUFET. IEEE Trans. Electron Devices 2003, 50, 471–478. [Google Scholar] [CrossRef]

- Han, K.; Baliga, B.J.; Sung, W. Split-Gate 1.2-kV 4H-SiC MOSFET: Analysis and Experimental Validation. IEEE Electron Device Lett. 2017, 38, 1437–1440. [Google Scholar] [CrossRef]

- Johnson, M.B.; Zvanut, M.E.; Richardson, O. HF chemical etching of SiO2 on 4H and 6H SiC. J. Electron. Mater. 2000, 29, 368–371. [Google Scholar] [CrossRef]

- Yano, H.; Hatayama, T.; Yraoka, Y.; Fuyuki, T. Characterization of 4H-SiC MOSFETs with NO-annealed CVD oxide. Mater. Sci. Forum 2006, 527, 971–974. [Google Scholar] [CrossRef]

| Parameter | C– | SBD– | CIMCD– |

|---|---|---|---|

| Cell pitch [μm] | 9 | 10.8 | 10.55 |

| Gate oxide thickness Tox1 [nm] | 50 | 50 | 50 |

| Gate oxide thickness Tox2 [nm] | - | - | 5 |

| P channel width [μm] | 0.5 | 0.5 | 0.5 |

| P+ base width [μm] | 3 | 3 | 3 |

| P+ base depth [μm] | 1 | 1 | 1 |

| N-drift thickness [μm] | 30 | 30 | 30 |

| N+ substrate thickness [μm] | 100 | 100 | 100 |

| WJFET [μm] | 3 | 2.8 | 1.8 |

| WD [μm] | - | 1 | 1 |

| WF [μm] | - | - | 1.75 |

| N-drift doping ND [cm−3] | 2.8 × 1015 | 3 × 1015 | 3.5 × 1015 |

| JFET doping [cm−3] | - | - | 2 × 1016 |

| P+ doping [cm−3] | 2 × 1018 | 2 × 1018 | 2 × 1018 |

| P channel doping [cm−3] | 2 × 1017 | 2 × 1017 | 2 × 1017 |

| N+ substrate doping [cm−3] | 1 × 1019 | 1 × 1019 | 1 × 1019 |

| Parameter | C– | SBD– | CIMCD– |

|---|---|---|---|

| BV [V] | 4089 | 3926 | 4045 |

| RON-SP [mΩ·cm2] | 9.8 | 10.61 | 9.4 |

| EMOX (@VDS = 3 kV) [MV/cm] | 3 | 3.07 | 2.34 |

| B–FOM [kV2/mΩ·cm2] | 1.706 | 1.566 | 1.741 |

| VF (@IDS = −80 A·cm2) [μm] | 3.27 | 1.81 | 2.44 |

| Parameter | C– | SBD– | CIMCD– |

|---|---|---|---|

| TSC [µs] | <10 | <3 | <23 |

| Crss [pF·cm−2] | 37.94 | 28.88 | 10.98 |

| Trr [ns] | 114 | 70.4 | 42.2 |

| IRM [A/cm−2] | 167 | 35 | 45 |

| Qrr [µC·cm−2] | 10.69 | 1.02 | 1.17 |

| TON [ns] | 139 | 122 | 92 |

| TOFF [ns] | 1206 | 991 | 551 |

| EON [mJ·cm−2] | 25.48 | 11.44 | 9.28 |

| EOFF [mJ·cm−2] | 17.26 | 12.22 | 4.48 |

| ET [mJ·cm−2] | 42.74 | 23.66 | 13.76 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Na, J.; Kim, M.; Kim, K. High Performance 3.3 kV SiC MOSFET Structure with Built-In MOS-Channel Diode. Energies 2022, 15, 6960. https://doi.org/10.3390/en15196960

Na J, Kim M, Kim K. High Performance 3.3 kV SiC MOSFET Structure with Built-In MOS-Channel Diode. Energies. 2022; 15(19):6960. https://doi.org/10.3390/en15196960

Chicago/Turabian StyleNa, Jaeyeop, Minju Kim, and Kwangsoo Kim. 2022. "High Performance 3.3 kV SiC MOSFET Structure with Built-In MOS-Channel Diode" Energies 15, no. 19: 6960. https://doi.org/10.3390/en15196960

APA StyleNa, J., Kim, M., & Kim, K. (2022). High Performance 3.3 kV SiC MOSFET Structure with Built-In MOS-Channel Diode. Energies, 15(19), 6960. https://doi.org/10.3390/en15196960