Research on Single-Phase and Three-Phase Compatible Isolated On-Board Charger and Control Technology

Abstract

:1. Introduction

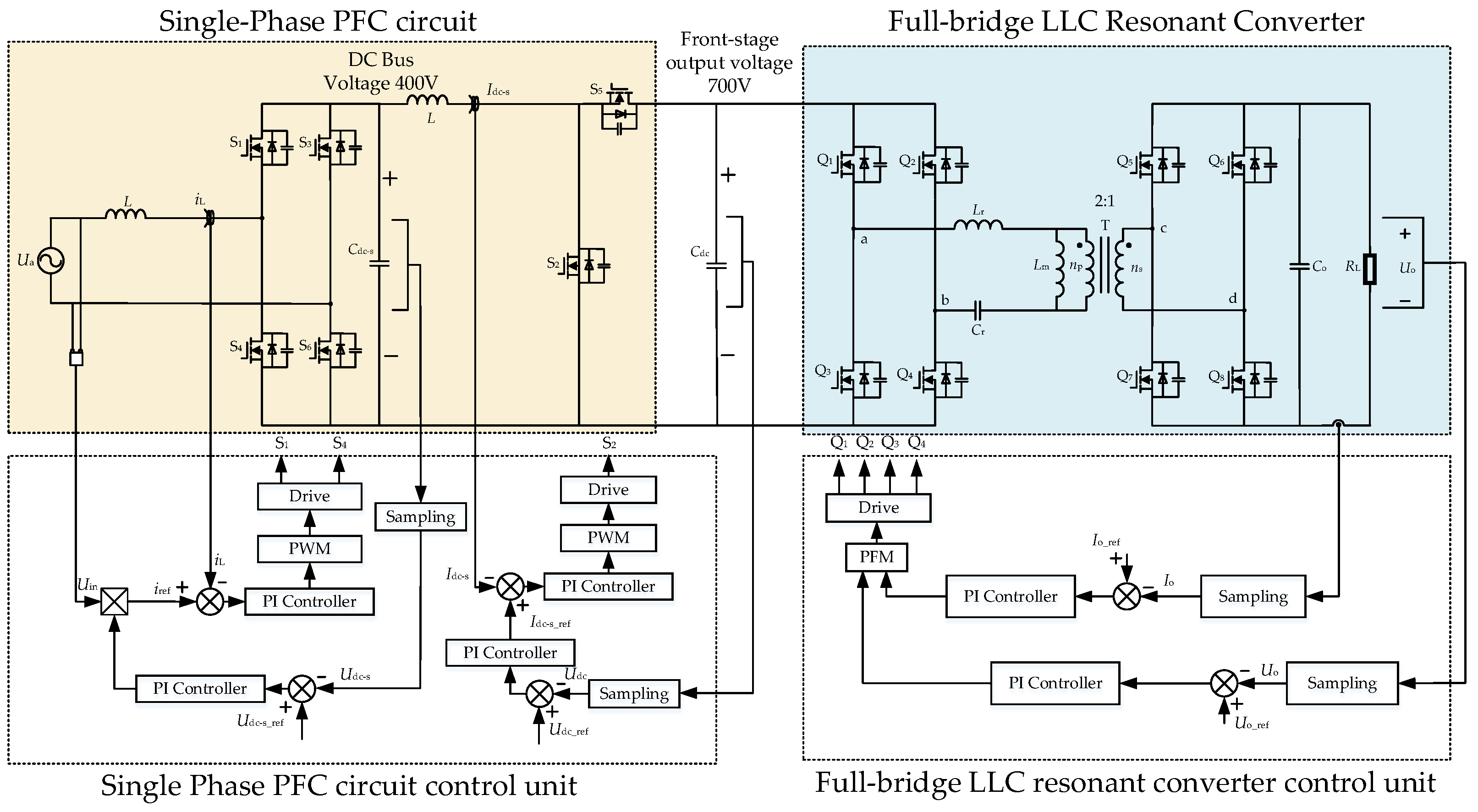

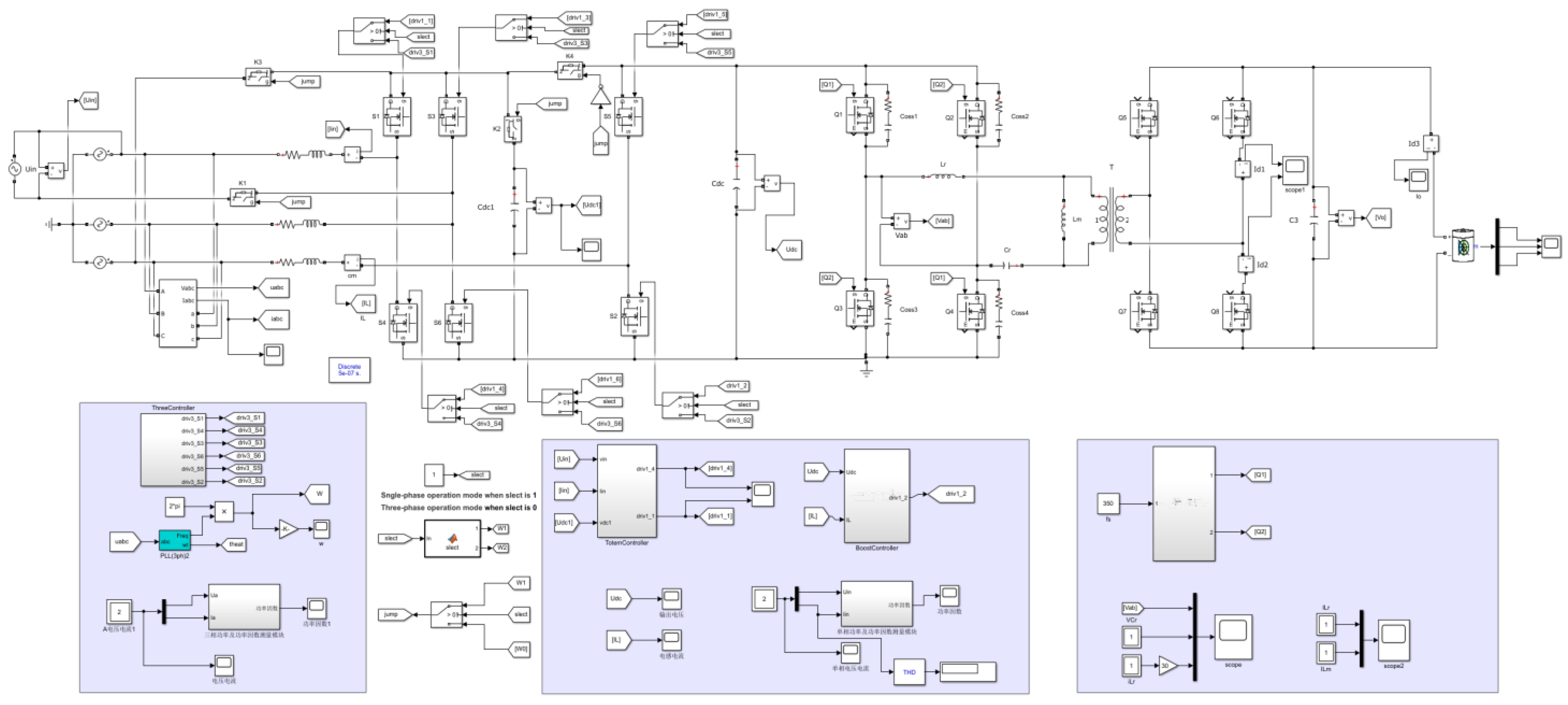

2. Topological Structure and Working Principle of the OBC System

2.1. Three-Phase Working Mode

2.2. Single-Phase Working Mode

3. Parameter Design

3.1. Parameter Design of the Front-Stage PFC Circuit

- (1)

- AC inductance L

- (2)

- DC bus capacitance Cdc-s

- (3)

- DC bus capacitance Cdc

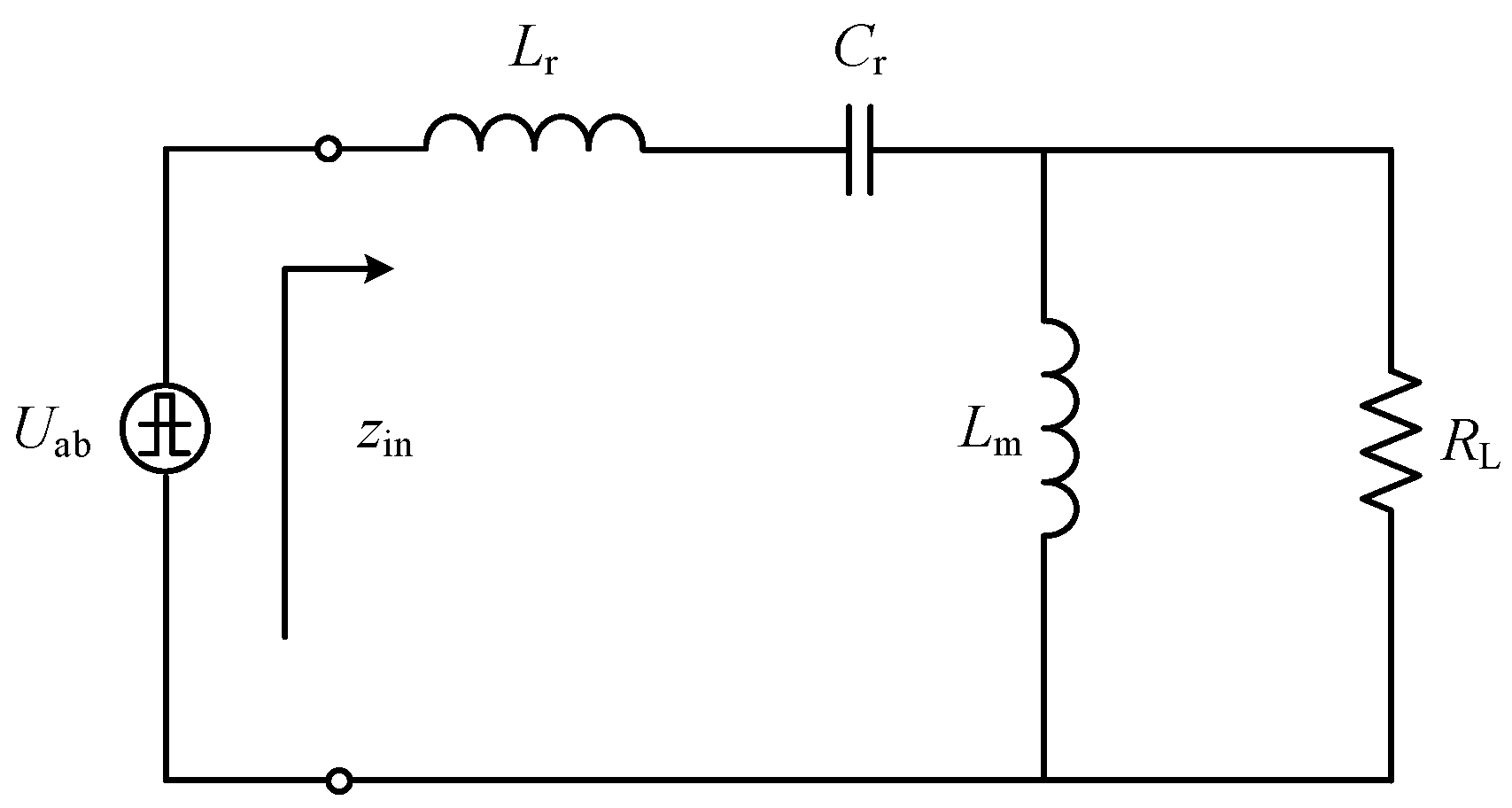

3.2. Parameter Design of the Rear-Stage Full-Bridge LLC Resonant Converter

- (1)

- Transformer ratio n

- (2)

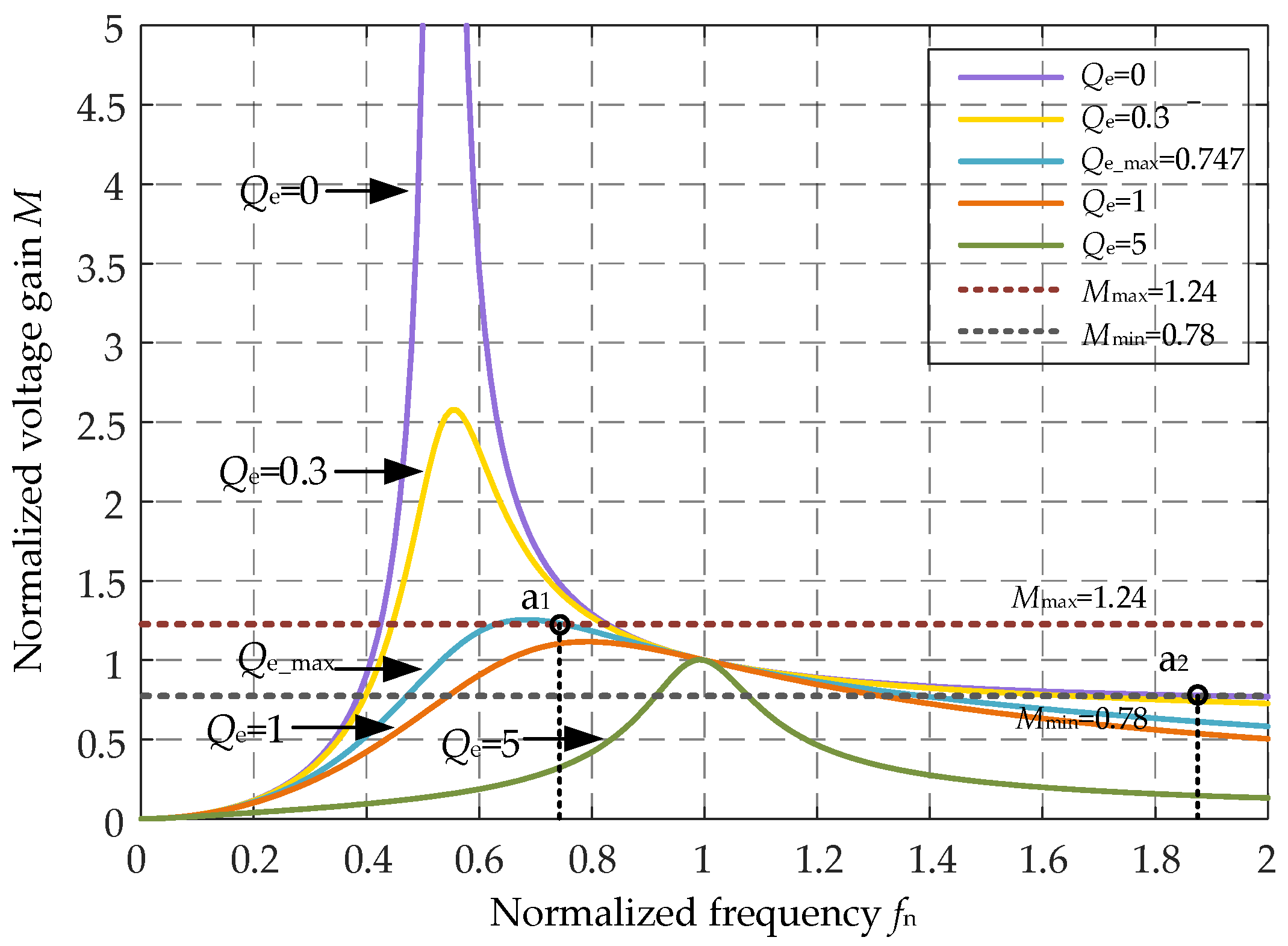

- Maximum gain Mmax and minimum gain Mmin

- (3)

- Inductance coefficient Ln

- (4)

- Quality factor Qe

- (5)

- Maximum operating frequency and minimum operating frequency

- (6)

- The equivalent impedance Rac of the primary side of the transformer

- (7)

- Resonant inductor Lr, resonant capacitance Cr, and excitation inductor Lm

4. Control Strategy

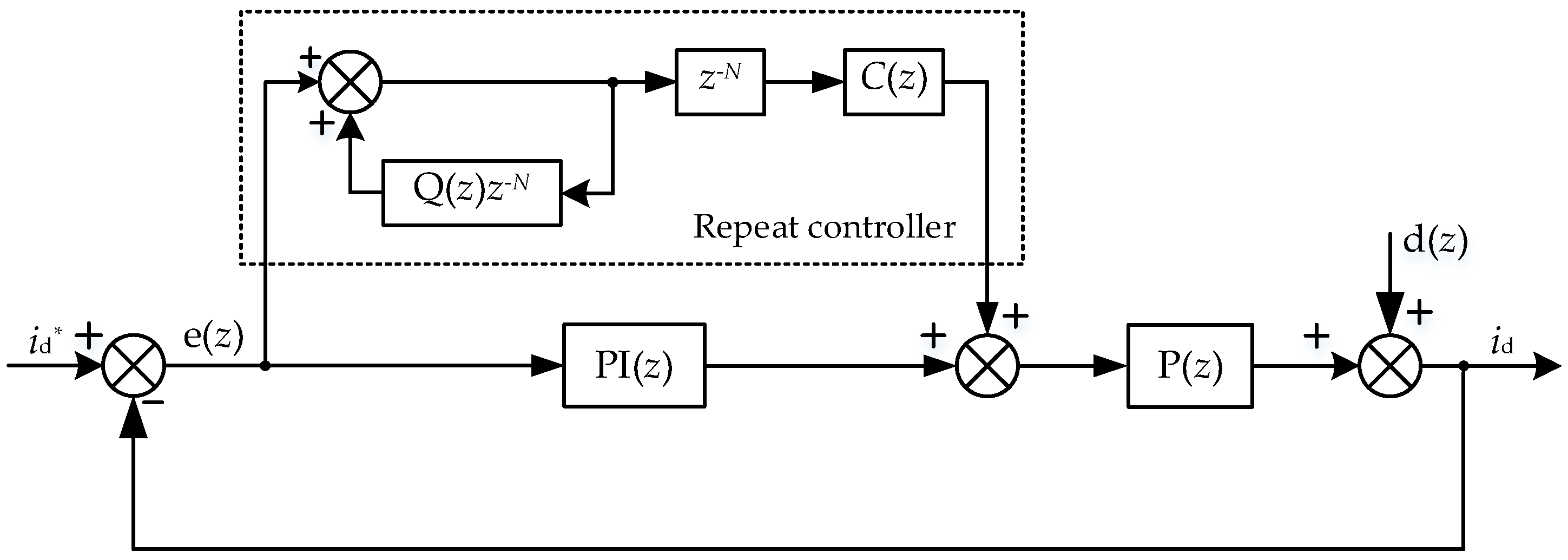

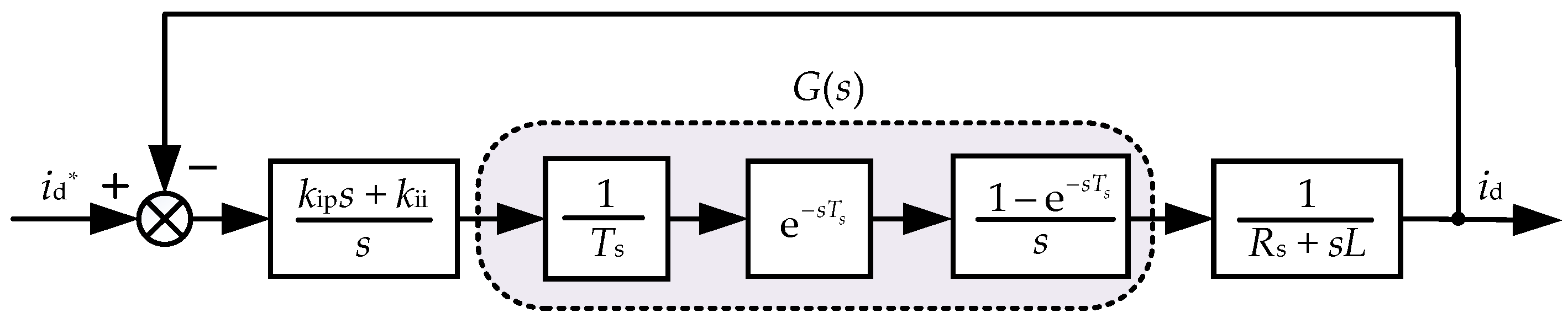

4.1. Front-Stage Three-Phase PFC Circuit Current Inner Loop Compound Controller

4.1.1. Design of Repetitive Controller

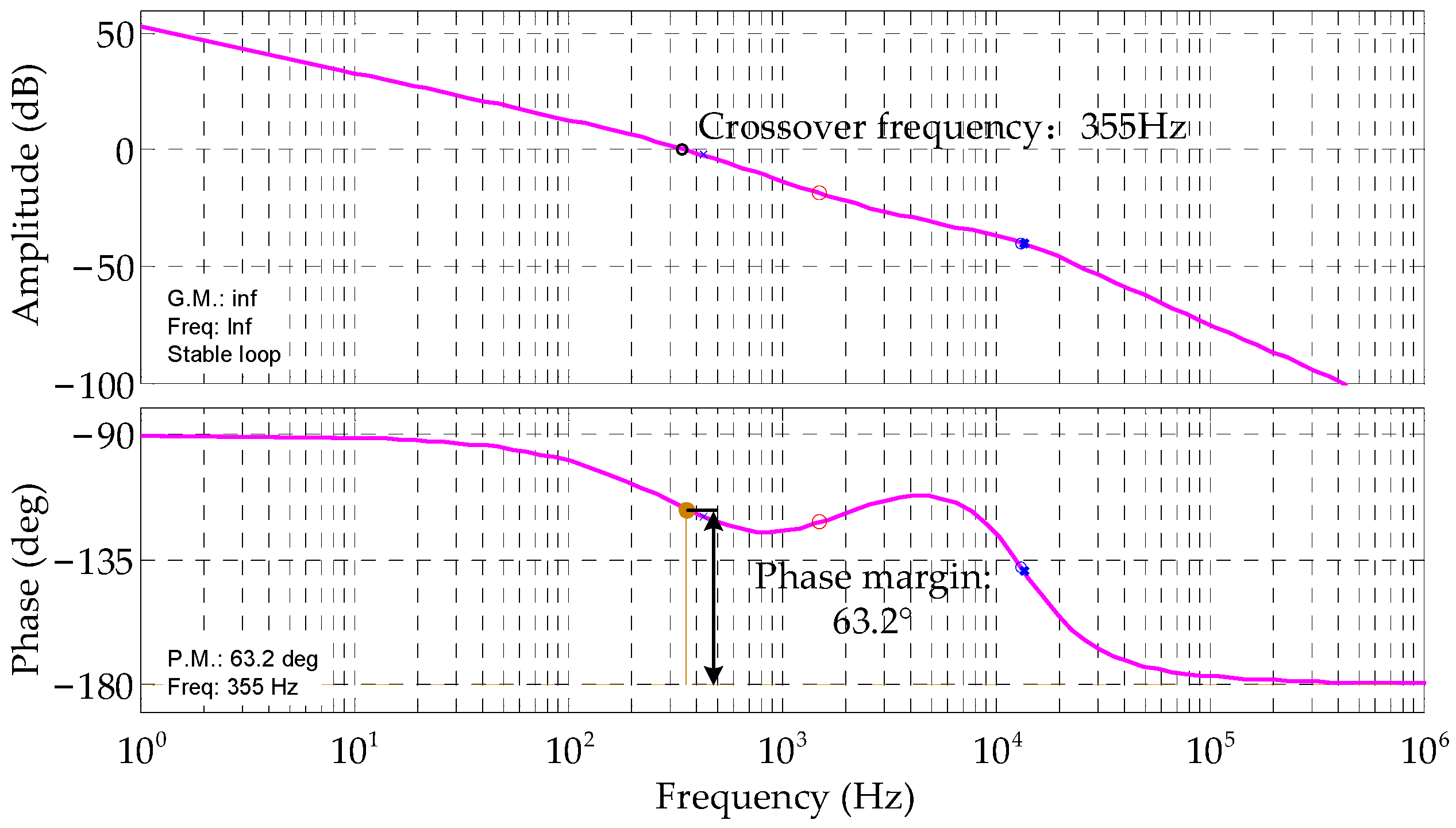

4.1.2. Design of Current Inner Loop PI Controller

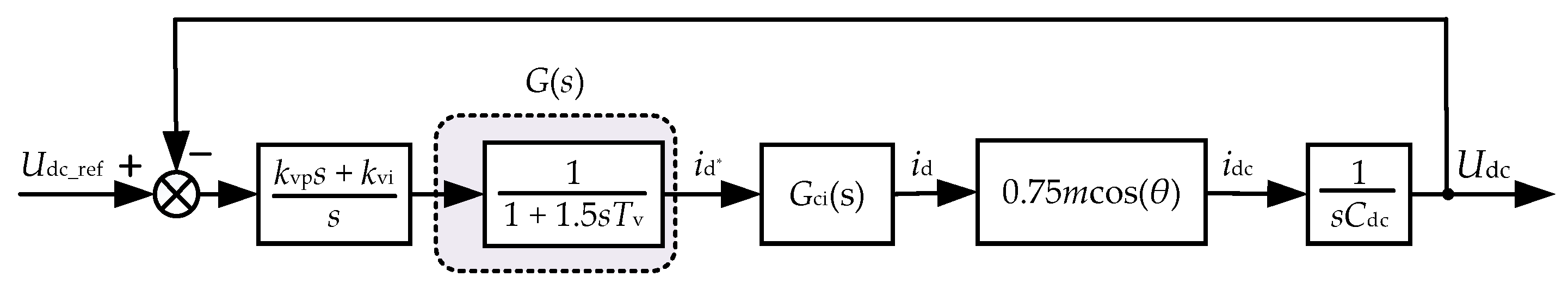

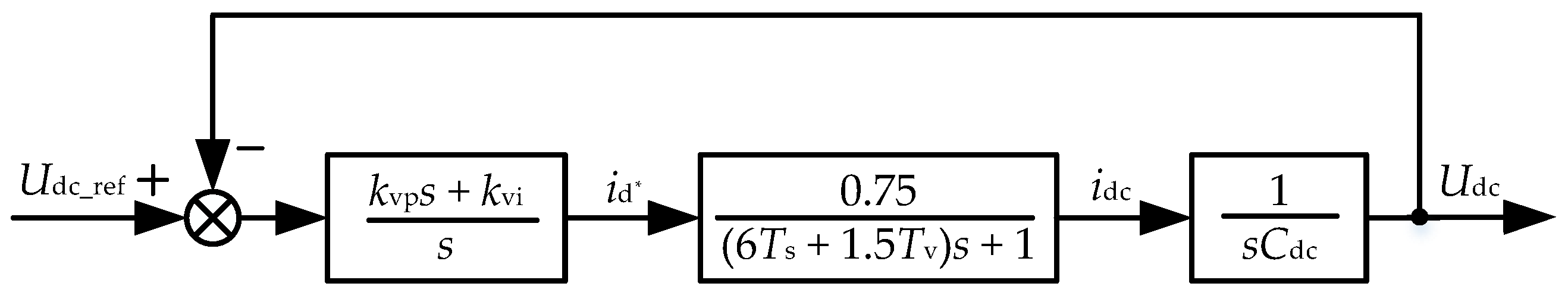

4.2. Front-Stage Three-Phase PFC Circuit Voltage Outer Loop Controller

4.3. Control Strategy of Rear-Stage Full-Bridge LLC Resonant Converter

5. System Simulation Analysis

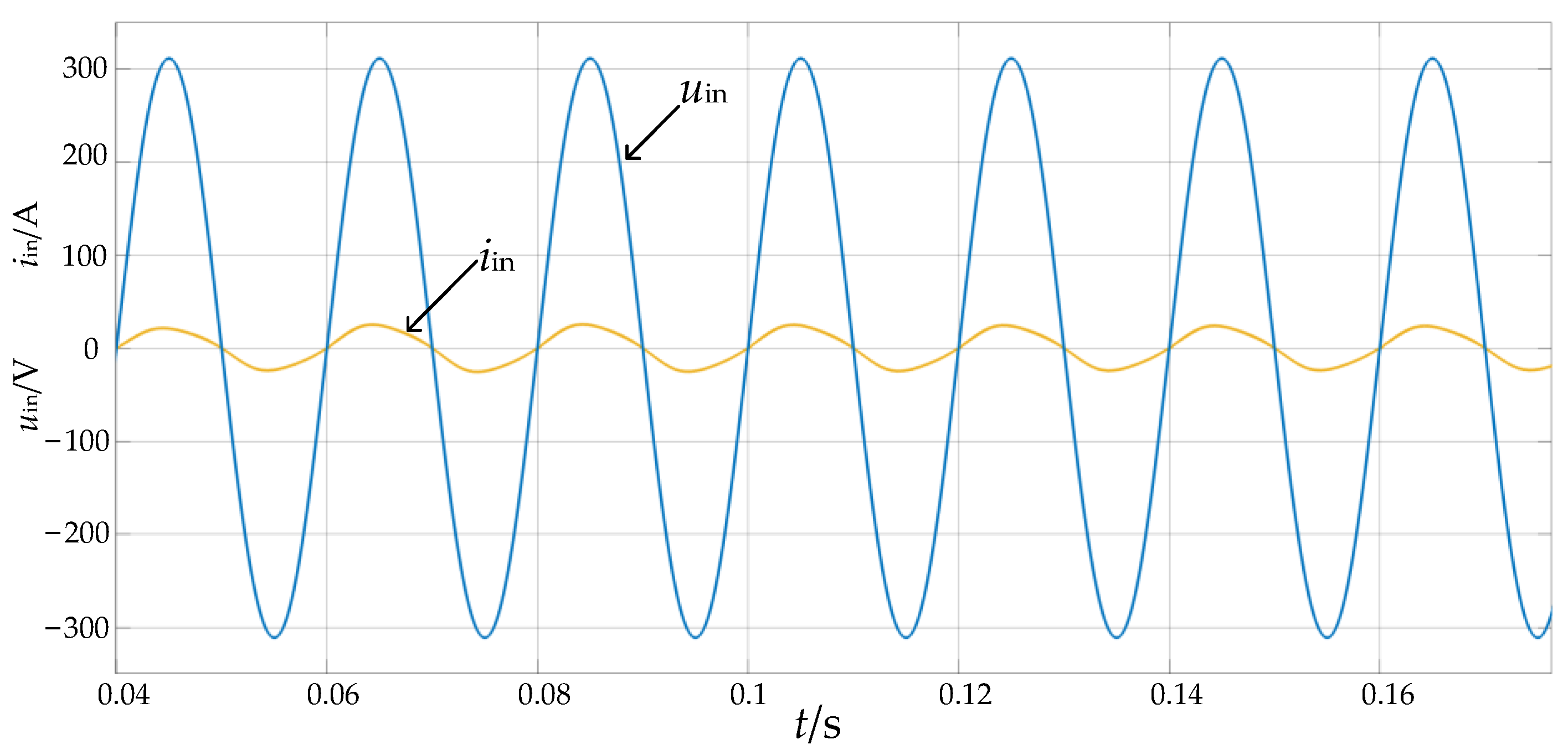

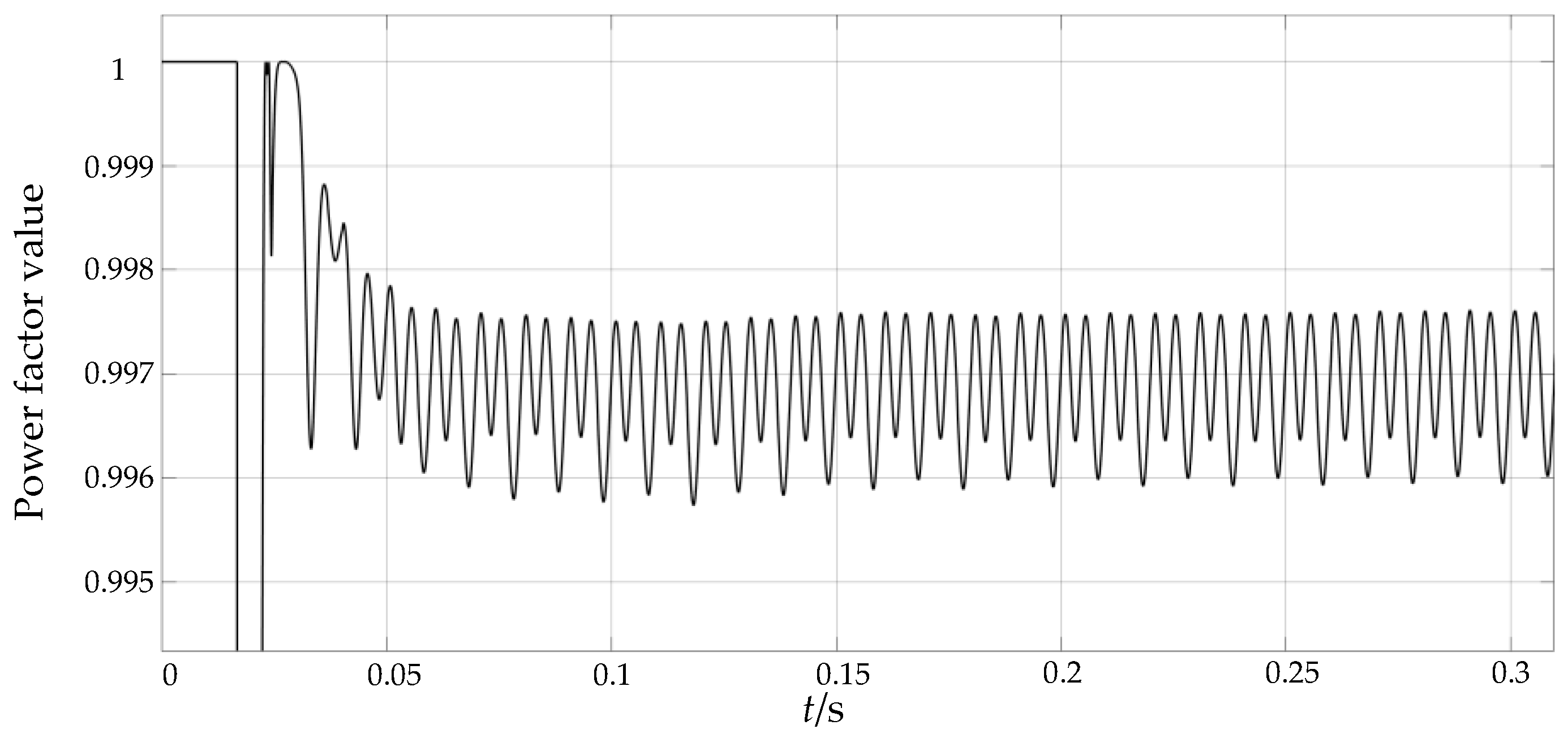

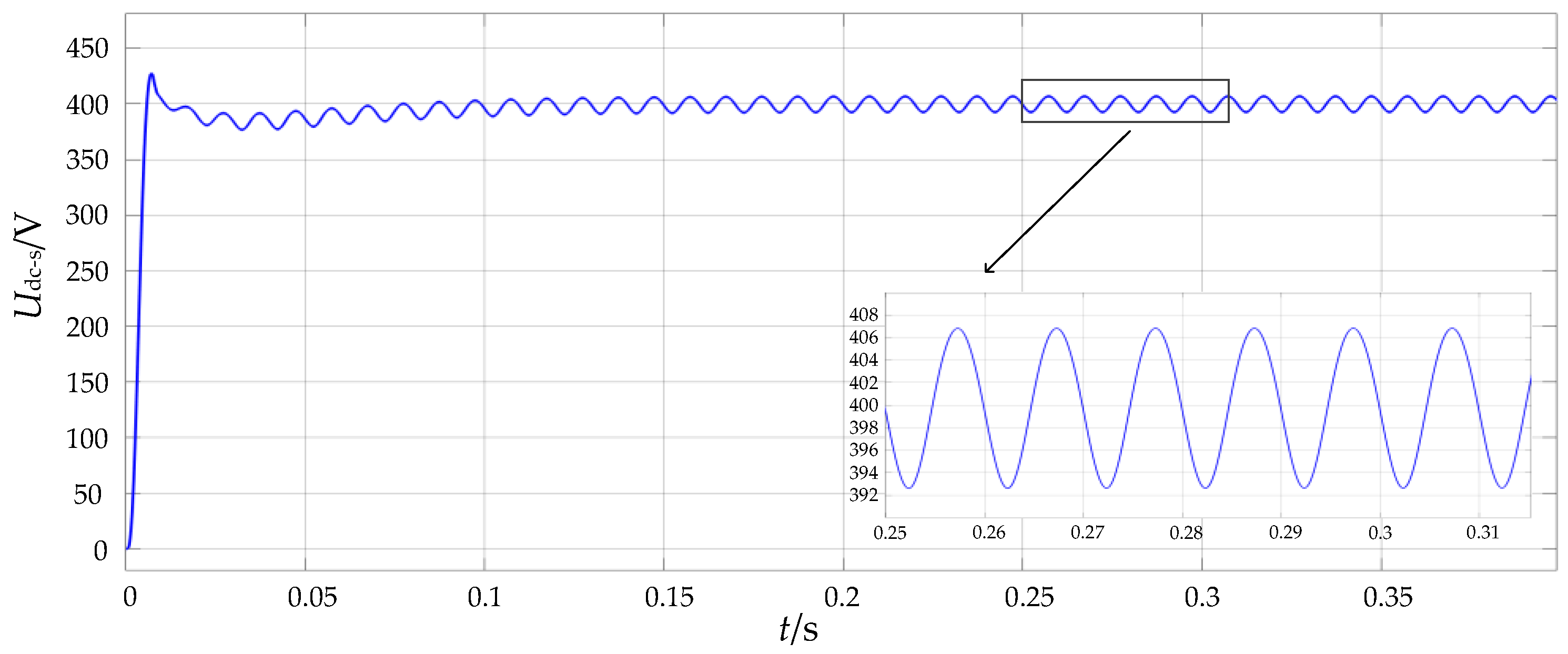

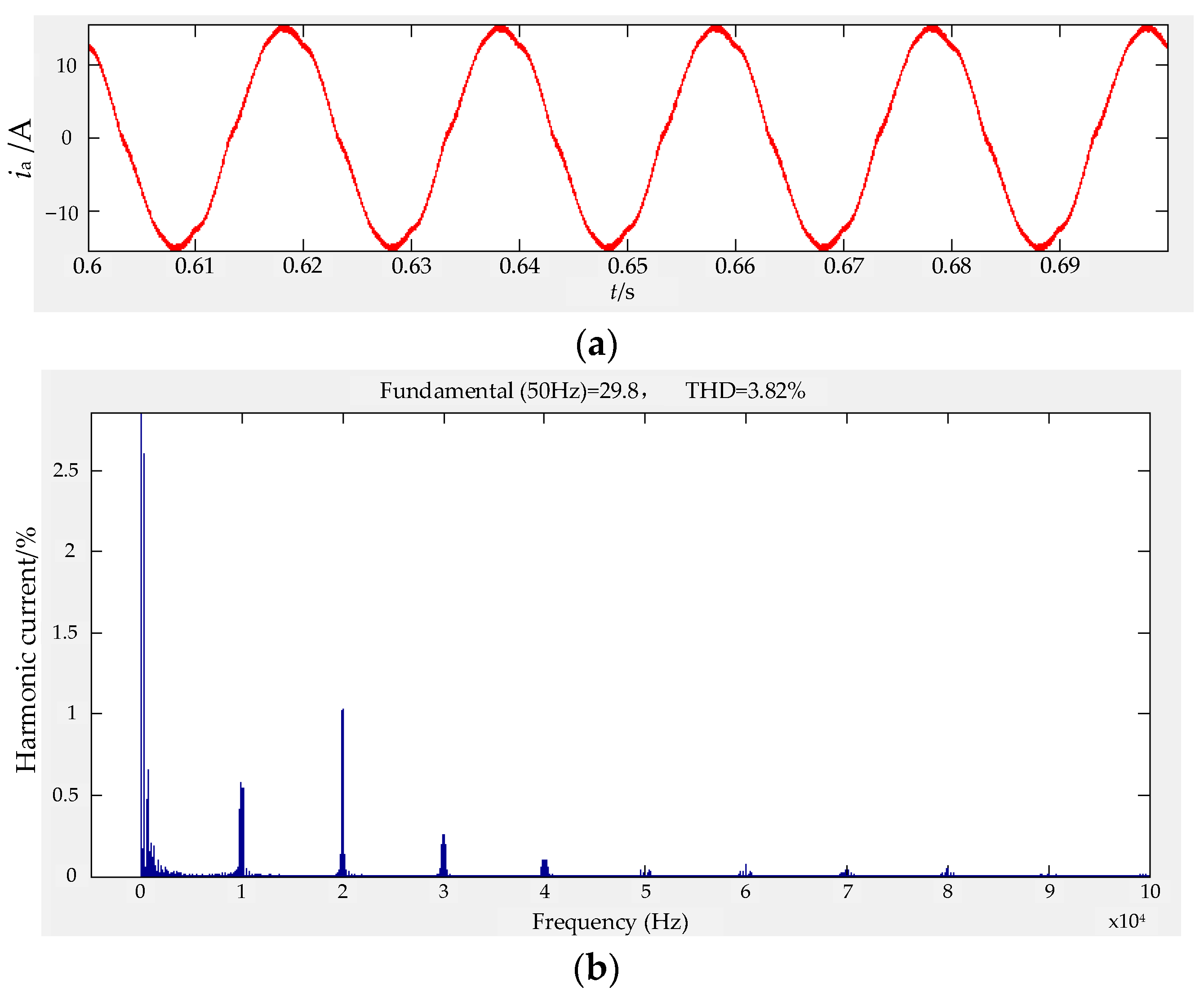

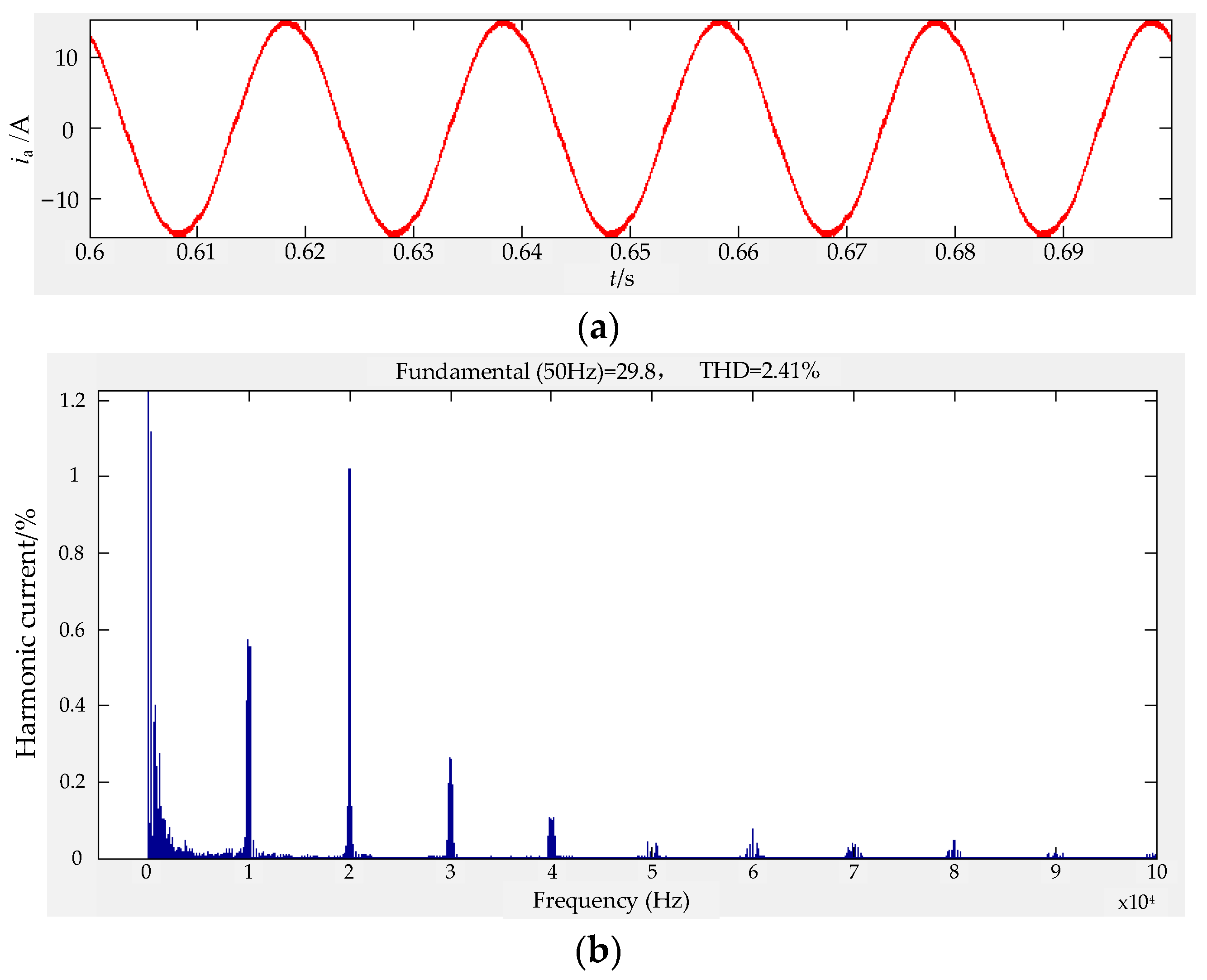

5.1. Single-Phase Input Mode Simulation Waveform

- (1)

- Grid current waveform

- (2)

- Output voltage waveform

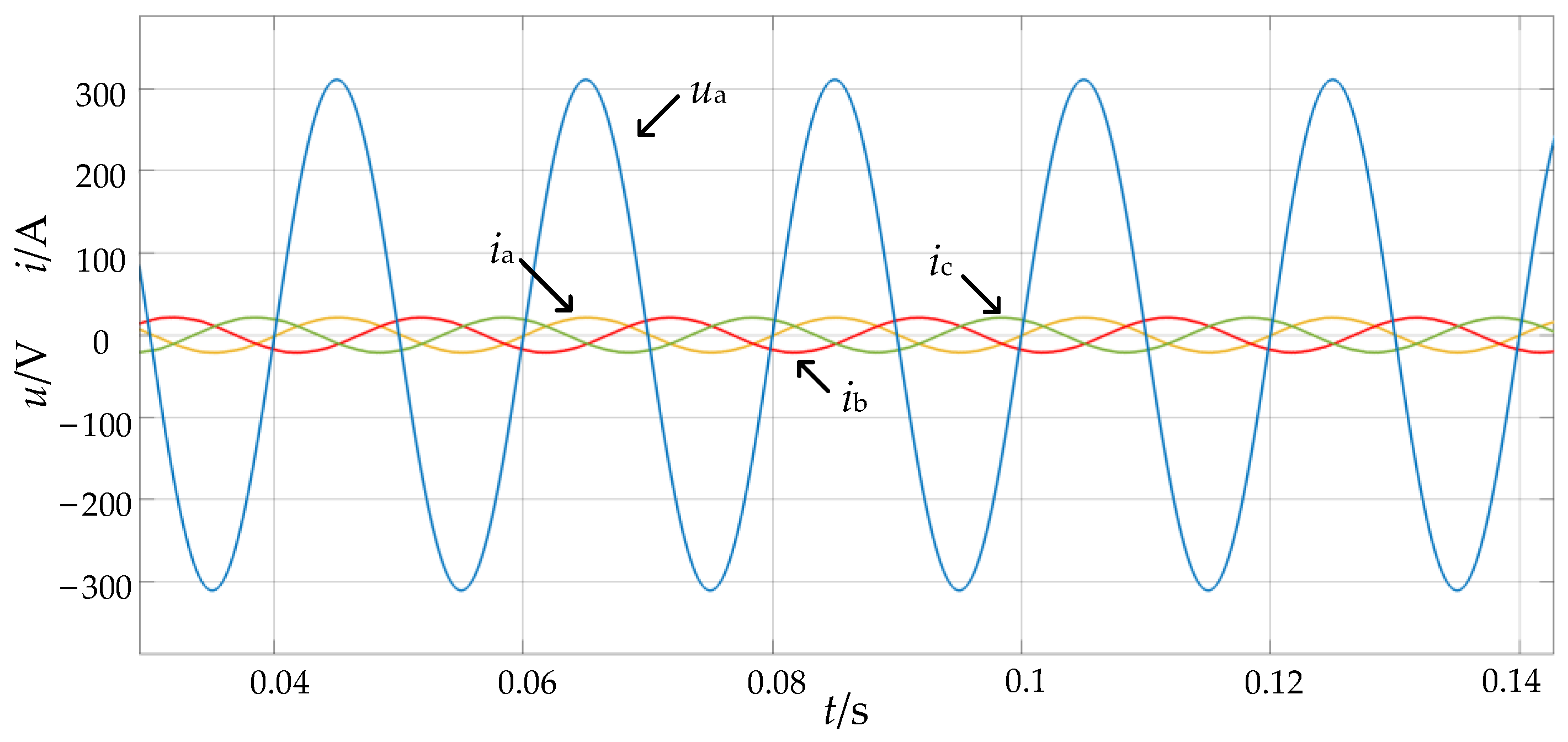

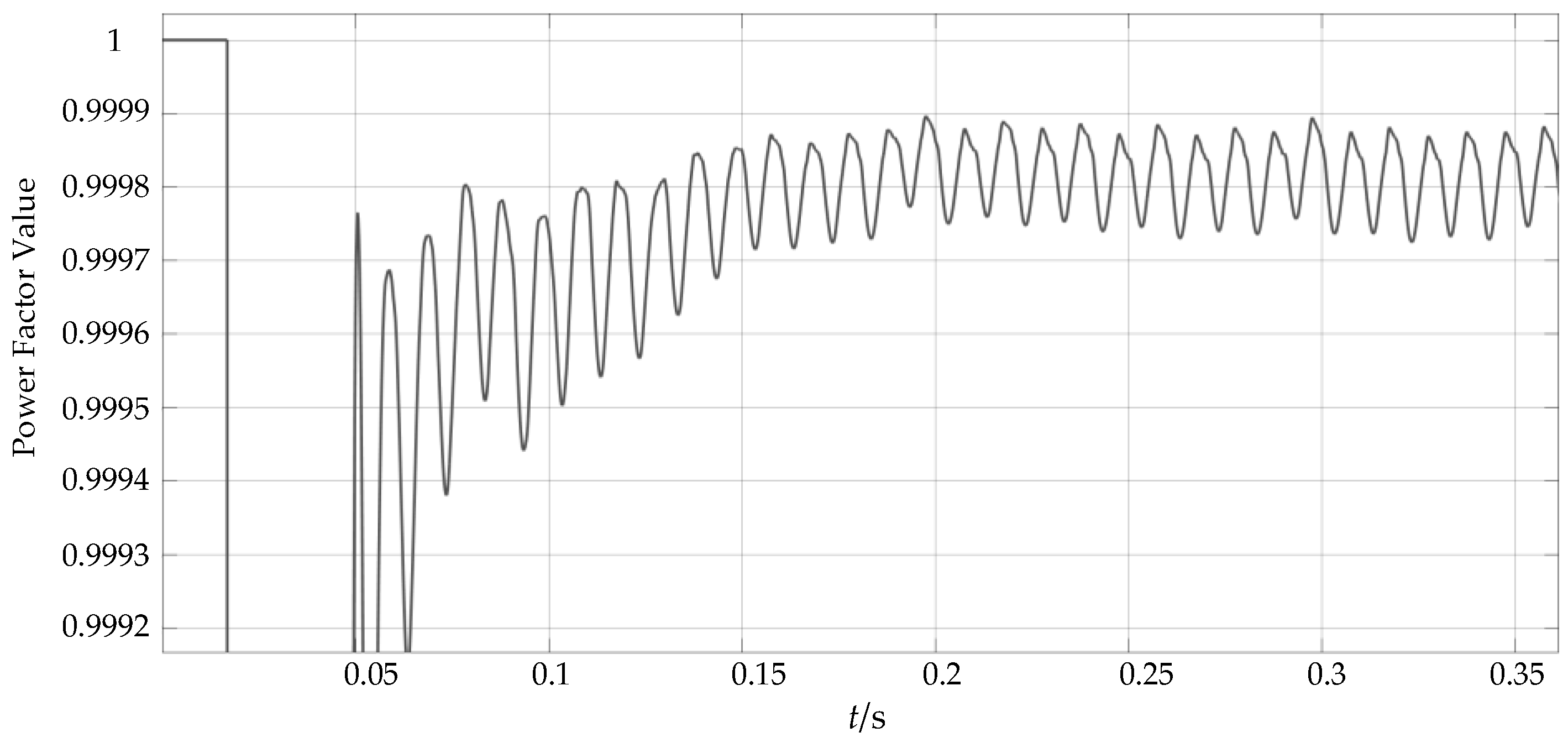

5.2. Three-Phase Input Mode Simulation Waveform

- (1)

- Power grid current wave type

- (2)

- Output voltage waveform

5.3. Simulation Waveform of Rear-Stage Full-Bridge LLC Resonant Converter

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Alireza, K.; Michael, D. Global trends in high-power on-board chargers for electric vehicle. IEEE Trans. Veh. Technol. 2019, 68, 3306–3324. [Google Scholar]

- Andreas, T.; Peter, B.A.; Tim, U.; Chresten, T.; Mattia, M. Electrification of personal vehicle travels in cities-Quantifying the public charging demand. eTransportation 2021, 9, 100125. [Google Scholar]

- Mi, N.; Sasic, B.; Marshall, J.; Tomasiewicz, S. A novel economical single stage battery charger with power factor correction. In Proceedings of the 18th Annual IEEE Applied Power Electronics Conference and Exposition, Miami, FL, USA, 9–13 February 2003. [Google Scholar]

- Zhao, W.H.; Shen, Y.X. Review on the research of electric vehicle on-board charger topologies. Control Eng. China 2019, 26, 29–36. [Google Scholar]

- Dai, H.C.; Ye, X.T.; Shou, Y.L.; Wang, Z.S. Research on control strategy of on-board charger (OBC) based on PFC and LLC two-level structure. Electr. Eng. 2020, 11, 38–42. [Google Scholar]

- Park, M.-H.; Baek, J.; Jeong, Y.; Moon, G.-W. An interleaved totem-pole bridgeless boost PFC converter with soft-switching capability adopting phase-shifting control. IEEE Trans. Power Electron. 2019, 34, 10610–10618. [Google Scholar] [CrossRef]

- Shi, C.; Wang, H.Y.; Dusmez, S.; Khaligh, A. A SiC-based high-efficiency isolated onboard PEV charger with ultrawide DC-link voltage range. IEEE Trans. Ind. Appl. 2017, 53, 501–511. [Google Scholar] [CrossRef]

- Meng, T.; Ben, H.Q.; Wang, X.S. A passive flyback auxiliary circuit with integrated transformer suitable for three-phase isolated full-bridge boost PFC converter. IEEE Trans. Power Electron. 2016, 31, 4995–5003. [Google Scholar] [CrossRef]

- Ebrahimi, S.; Taghavi, M.; Tahami, F.; Oraee, H. Integrated bidirectional isolated soft-switched battery charger for vehicle-to-grid technology using 4-Switch 3Φ-rectifier. In Proceedings of the IECON 39th Annual Conference of the IEEE Industrial Electronics Society, Vienna, Austria, 10–13 November 2013. [Google Scholar]

- Kim, H.; Park, J.; Kim, S.; Hakim, R.M.; Belkamel, H.; Choi, S. A single-stage electrolytic capacitor-less EV charger with single- and three-phase compatibility. IEEE Trans. Power Electron. 2022, 37, 6780–6791. [Google Scholar] [CrossRef]

- Zhang, T.S.; Peng, Y.Q.; Zhao, Y.Y.; Huang, X.R.; Liu, X.R. Research on double closed loop interval Type II fuzzy control model of front-stage variable on-board charger. Control Eng. China, 2022; 1–13, early access. [Google Scholar] [CrossRef]

- Zhou, S.Y. Research on Single and Three-Phase Compatible VIENNA Rectifier. Master’s Thesis, Nanjing University of Aeronautics and Astronautics, Nanjing, China, 2020. [Google Scholar]

- Sadilek, T.; Jang, Y.; Hao, S.; Jia, M.; Barbosa, P.; Husain, I. A new PFC CCM boost rectifier with extended gain and reduced voltage switching for 1-ph/3-ph universal input on-board charger for electric vehicles. In Proceedings of the 5th IEEE Applied Power Electronics Conference and Exposition, Phoenix, AZ, USA, 14–17 June 2021. [Google Scholar]

- Cao, J.F.; Xiong, H.J.; Lei, D.M. LCL-type grid-connected inverter based on fractional-order PID control. In Proceedings of the 3rd International Conference on Industrial Informatics-Computing Technology, Intelligent Technology, Industrial Information Integration (ICIICII), Wuhan, China, 2–3 December 2017. [Google Scholar]

- Liu, B.; Ben, H.; Bai, Y.; Sun, S. Analysis and suppression of current harmonics in grid side of PWM rectifiers during light load. Trans. China Electrotech. Soc. 2017, 31, 162–168. [Google Scholar]

- Ali, M.; Wang, L.; Chen, G. Design and control aspect of segmented proportional integral-repetitive controller parameter optimization of the three-phase boost power factor correction rectifier. Int. J. Circuit Theory Appl. 2021, 49, 554–575. [Google Scholar] [CrossRef]

- Zhang, J.; Wang, J.; Zhang, G.; Qian, Z. A hybrid driving scheme for full-bridge synchronous rectifier in LLC resonant converter. IEEE Trans. Power Electron. 2012, 27, 4549–4561. [Google Scholar] [CrossRef]

- Deng, J.; Li, S.; Hu, S.; Mi, C.; Ma, R. Design methodology of LLC resonant converters for electric vehicle battery Chargers. IEEE Trans. Veh. Technol. 2014, 63, 1581–1592. [Google Scholar] [CrossRef]

- Zhang, Z.G.; Li, S.F.; Li, X.; Cheng, P.M.; Luo, Q.M. A high efficiency totem-pole bridgeless PFC converter in CCM mode. Proc. CSEE 2022, 42, 1957–1968. [Google Scholar]

- He, L.; Zhang, K.; Xiong, J. A repetitive control scheme for harmonic suppression of circulating current in modular multilevel converters. IEEE Trans. Power Electron. 2015, 30, 471–481. [Google Scholar] [CrossRef]

- Zhou, K.; Fang, H.L.; Liu, Y. Driving–charging integrated controller for electric vehicles. IEEE Access 2022, 10, 66545–66563. [Google Scholar] [CrossRef]

- Yang, Y.; Zhang, J. Phase compensation resonant control strategy for three-phase PWM converter. Electr. Mach. Control 2013, 17, 43–49. [Google Scholar]

- Zhou, K.; Yuan, C.X.; Sun, D.Y.; Jin, N.Z.; Wu, X.G. Parameter adaptive terminal sliding mode control for Full-Bridge DC-DC converter. PLoS ONE 2021, 16, e0247228. [Google Scholar] [CrossRef] [PubMed]

| Performance Indicator | Value |

|---|---|

| Input phase voltage range (Uin) | 176~264 V |

| Input voltage frequency range (f) | 45~65 Hz |

| DC bus voltage (Udc-s) | 400 V |

| Front-stage output voltage (Udc) | 700 V |

| Output voltage range (Uo) | 280~420 V |

| Rated output voltage (Uo_nor) | 350 V |

| PFC circuit switching frequency (fsw) | 50 kHz |

| Power factor | ≥0.99 |

| Efficiency (η) | ≥93% |

| Simulation Parameter | Value |

|---|---|

| Filter inductance (L) | 1 mH |

| DC bus capacitance (Cdc-s) | 2700 μF |

| DC bus capacitance (Cdc) | 2000 μF |

| Resonant inductance (Lr) | 68 μH |

| Resonant capacitance (Cr) | 37.25 nF |

| Excitation inductance (Lm) | 170 μH |

| Output holding capacitance (Co) | 4000 μF |

| Load | Current Inner Loop PI Control | Current Inner Loop PI-Repetitive Control |

|---|---|---|

| THD (%) | THD (%) | |

| Full Load | 3.82 | 2.41 |

| Half Load | 6.74 | 4.36 |

| 25% Load | 10.82 | 8.65 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhou, K.; Chen, S.-M.; Jin, N.-Z.; Sun, D.-Y. Research on Single-Phase and Three-Phase Compatible Isolated On-Board Charger and Control Technology. Energies 2022, 15, 6445. https://doi.org/10.3390/en15176445

Zhou K, Chen S-M, Jin N-Z, Sun D-Y. Research on Single-Phase and Three-Phase Compatible Isolated On-Board Charger and Control Technology. Energies. 2022; 15(17):6445. https://doi.org/10.3390/en15176445

Chicago/Turabian StyleZhou, Kai, Si-Min Chen, Ning-Zhi Jin, and Dong-Yang Sun. 2022. "Research on Single-Phase and Three-Phase Compatible Isolated On-Board Charger and Control Technology" Energies 15, no. 17: 6445. https://doi.org/10.3390/en15176445

APA StyleZhou, K., Chen, S.-M., Jin, N.-Z., & Sun, D.-Y. (2022). Research on Single-Phase and Three-Phase Compatible Isolated On-Board Charger and Control Technology. Energies, 15(17), 6445. https://doi.org/10.3390/en15176445