An Efficient Non-Inverting Buck-Boost Converter with Improved Step Up/Down Ability

Abstract

:1. Introduction

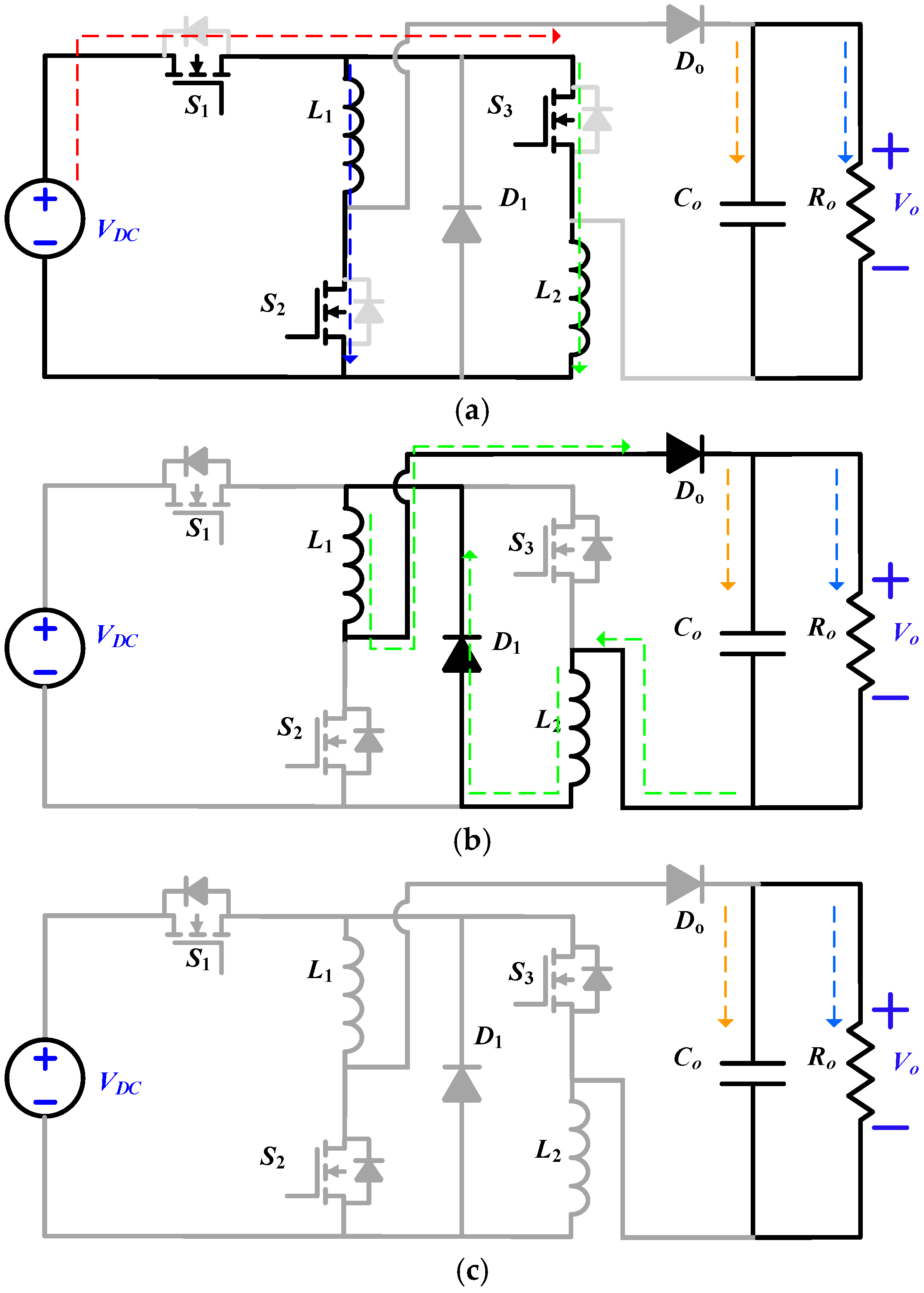

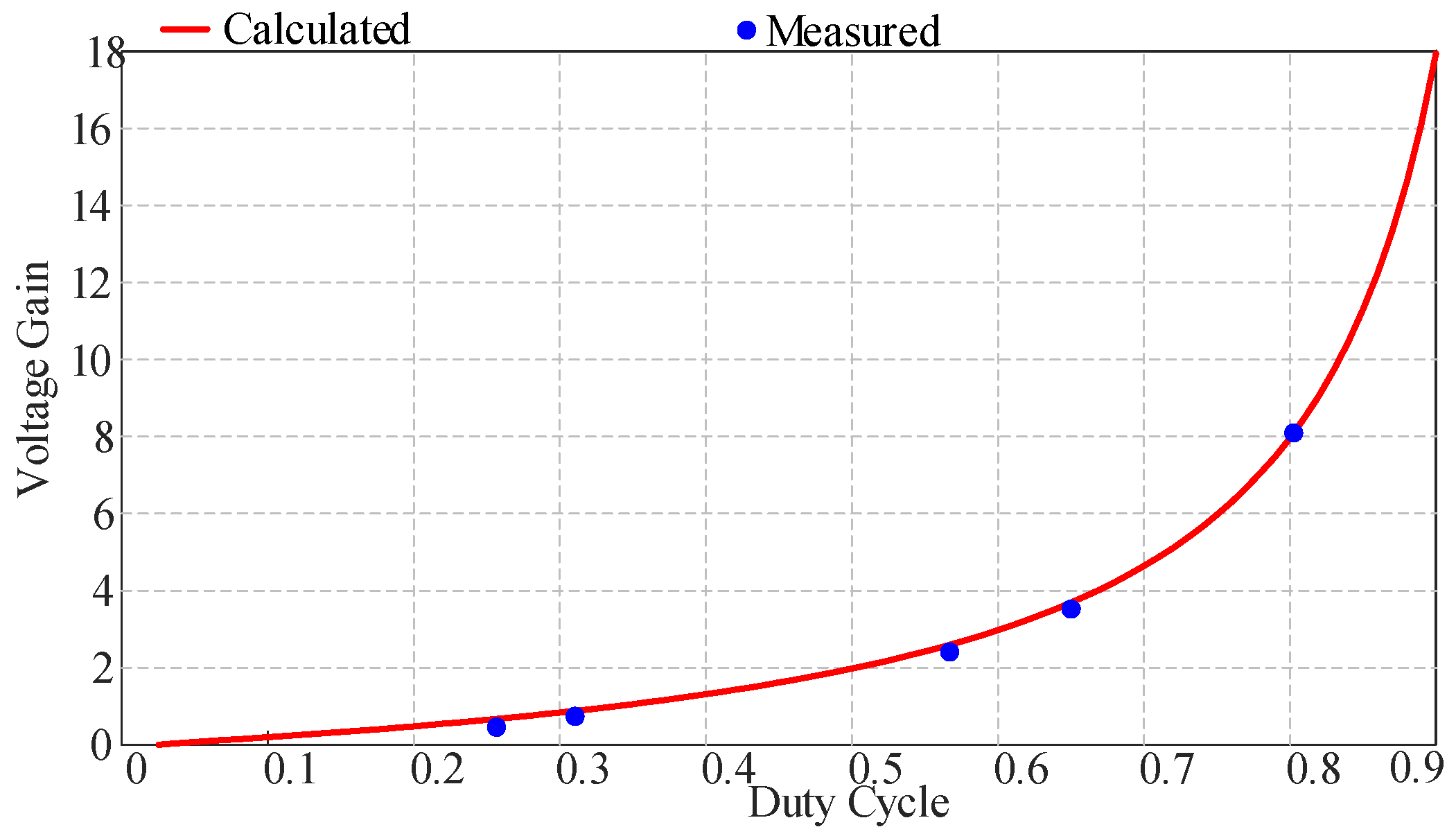

2. Proposed Buck-Boost Dc–Dc Converter

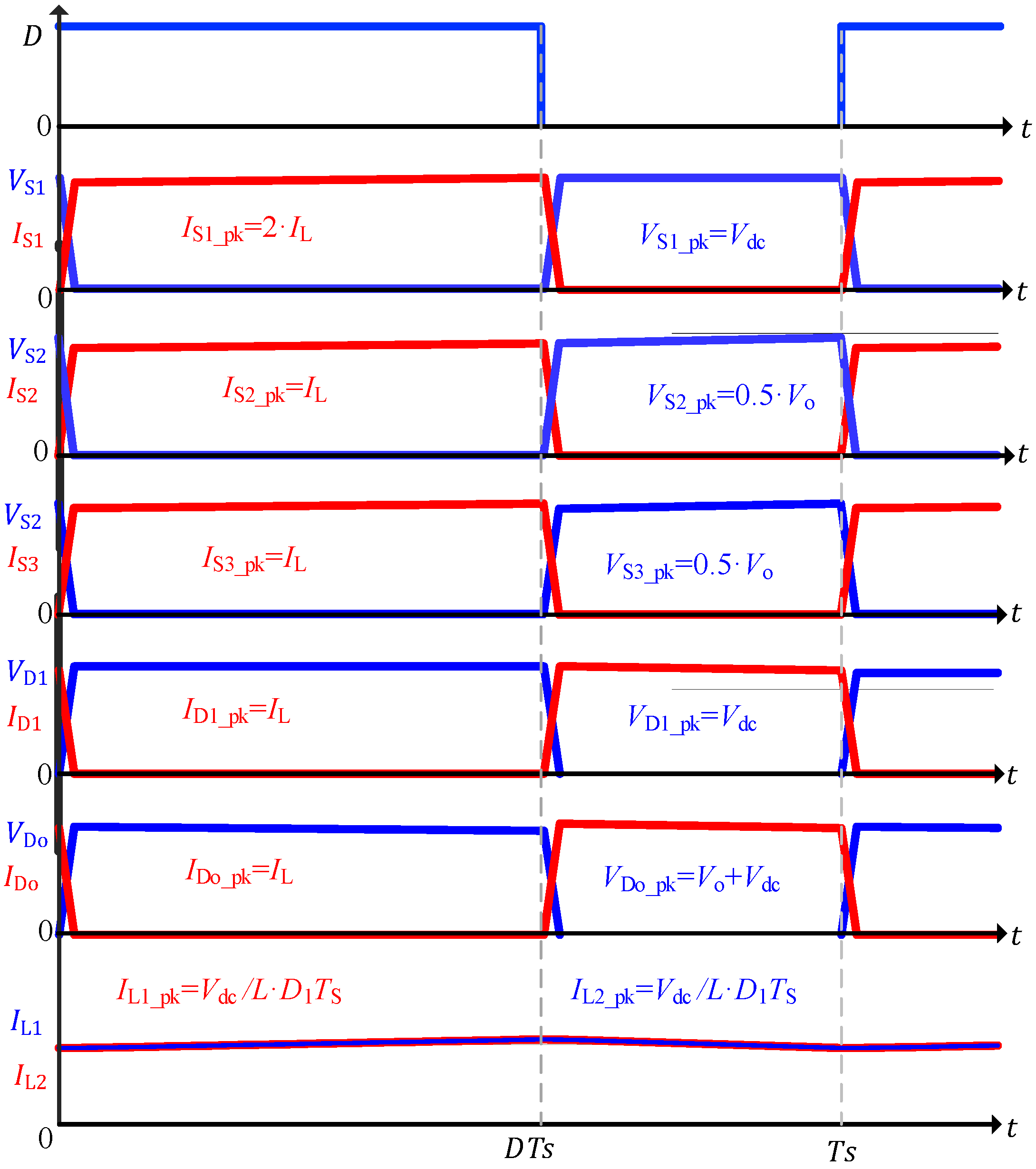

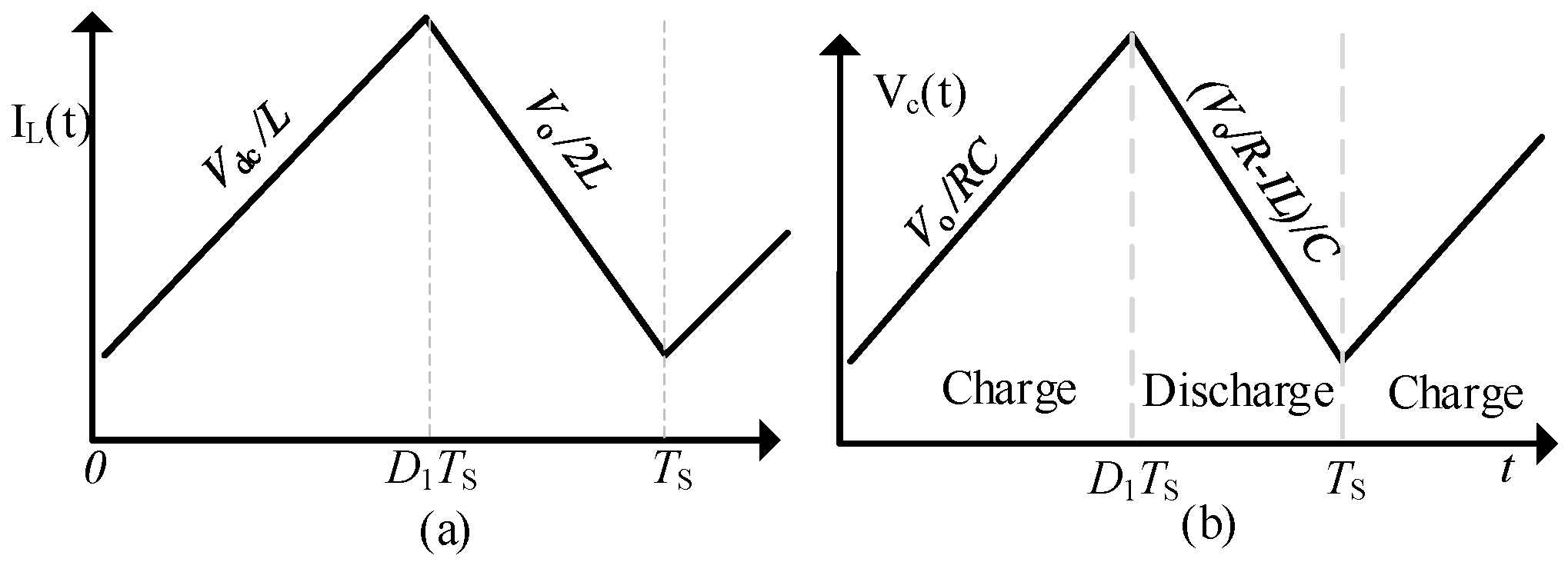

2.1. Continuous Conduction Mode

- ✓

- Capacitor voltage ripple is very small compared with the voltage itself, thus it could be neglected.

- ✓

- Inductor current ripple is negligible because of its very small value.

- ✓

- All semiconductor devices are ideal.

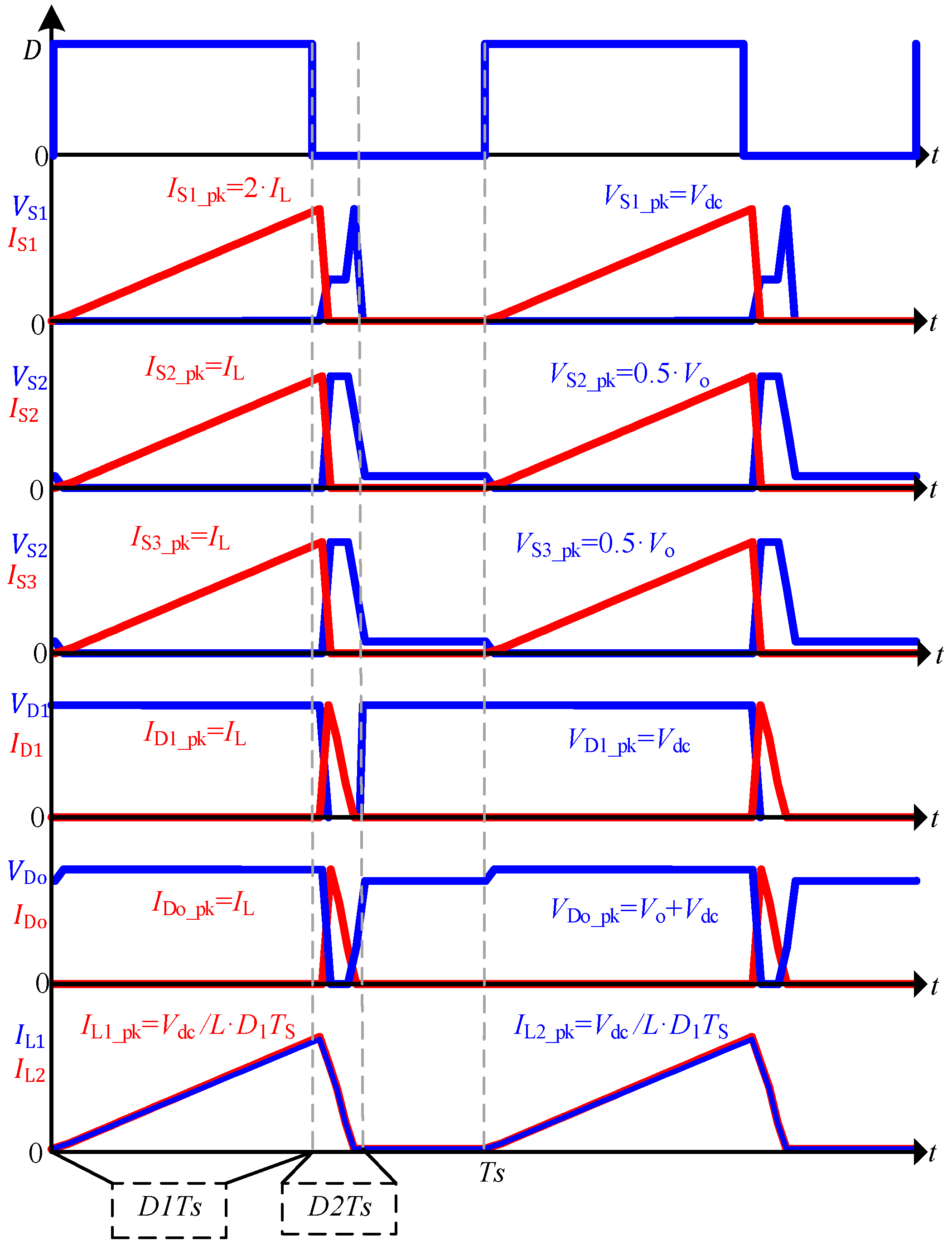

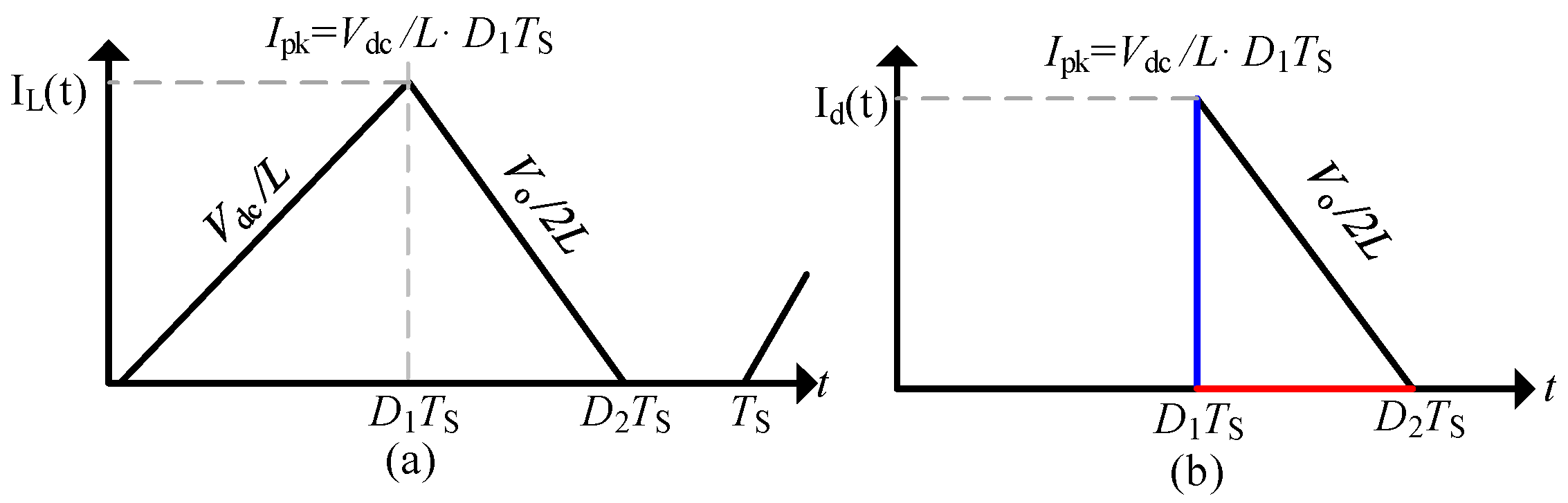

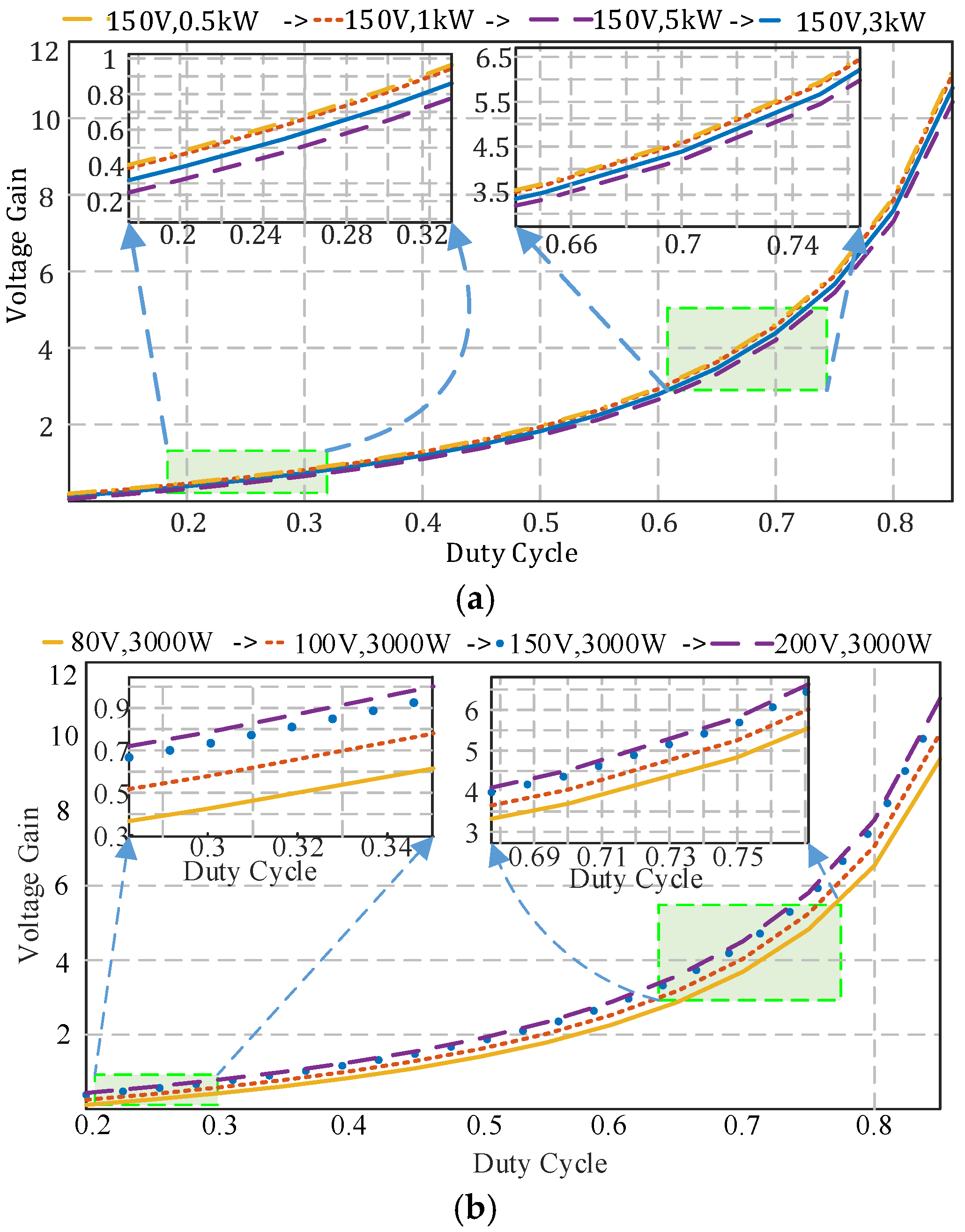

2.2. Discontinuous Conduction Mode

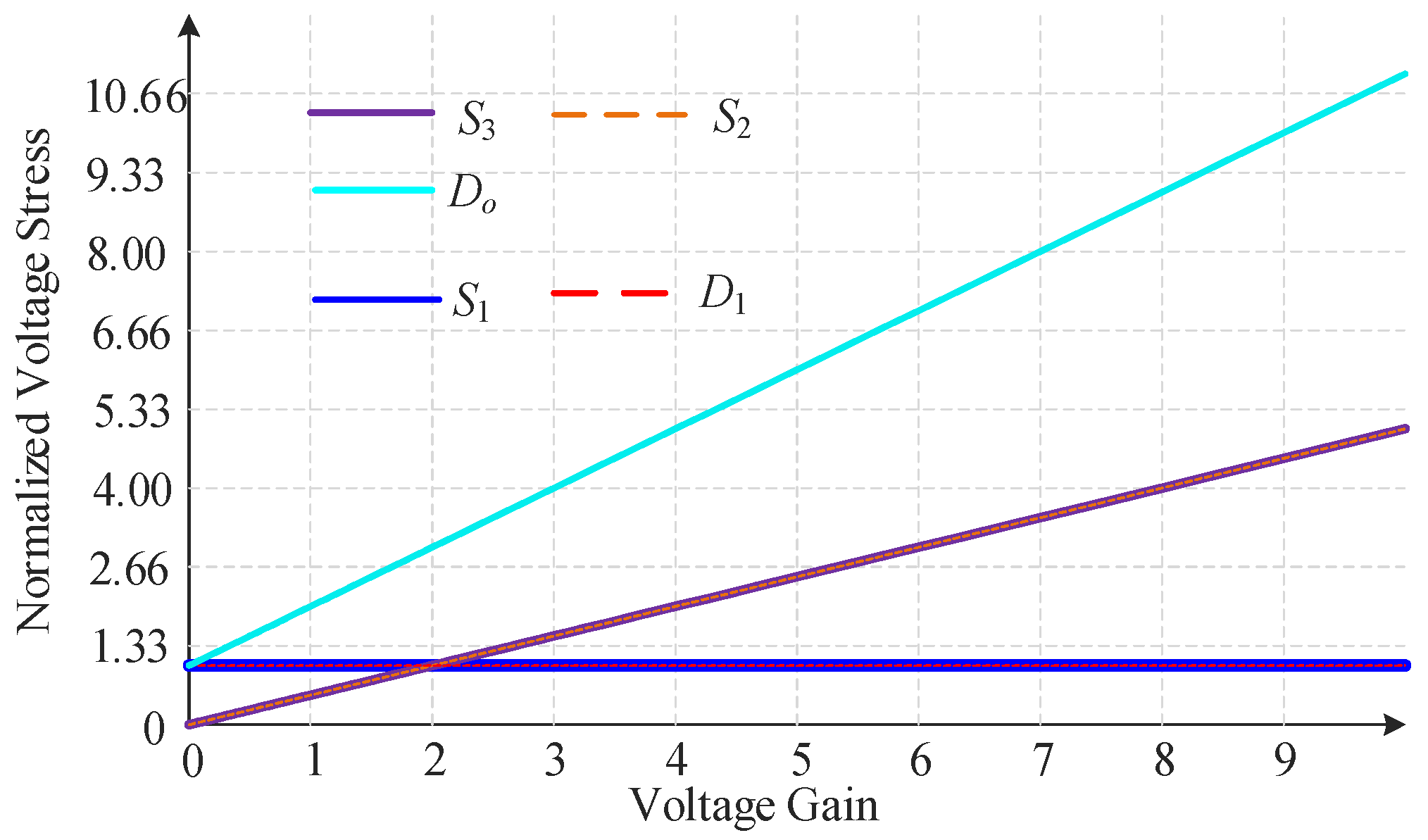

2.3. Switches’ and Diodes’ Voltage Stresses

2.4. Components’ Design

2.4.1. Inductors’ Design

2.4.2. Capacitors’ Design

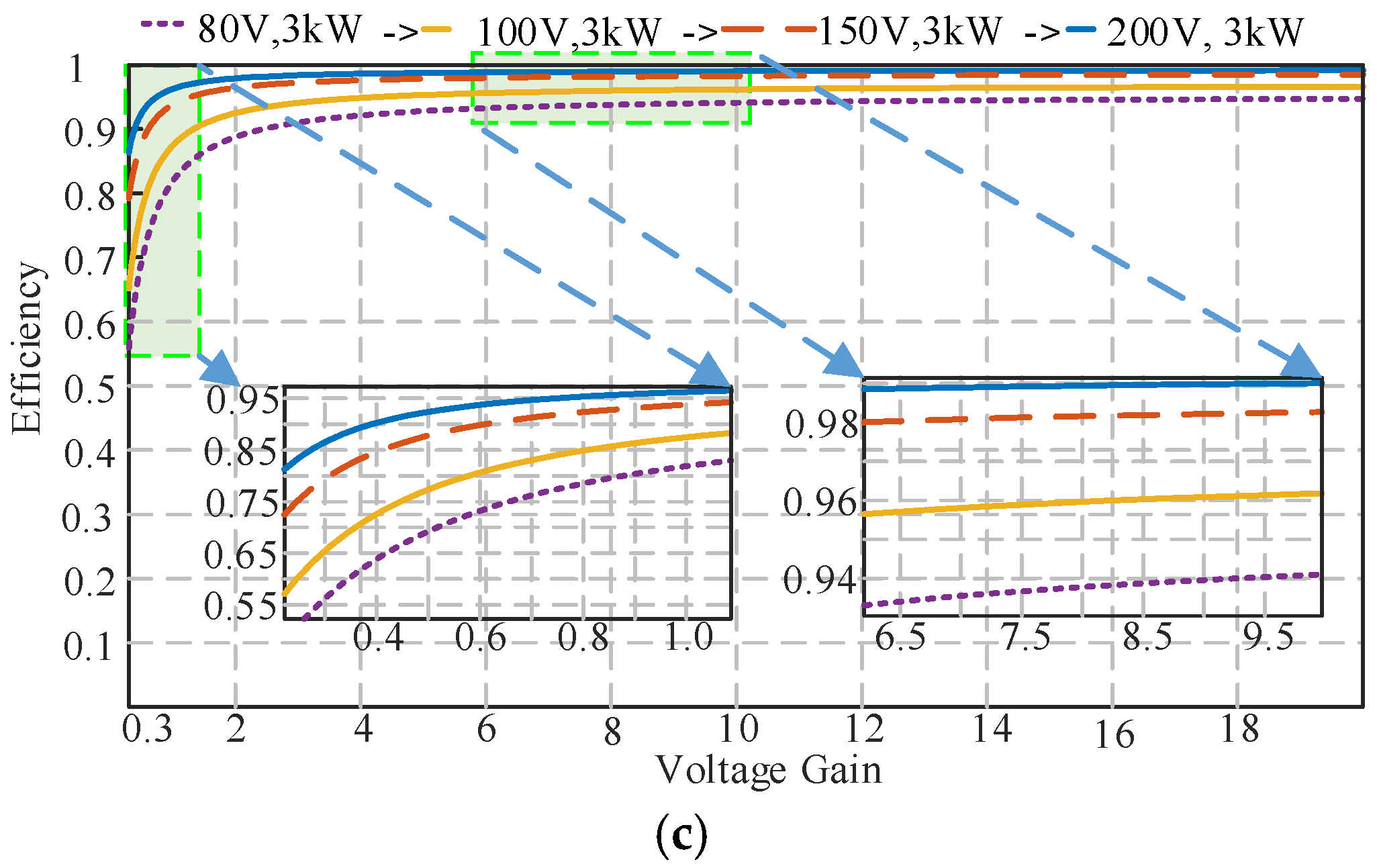

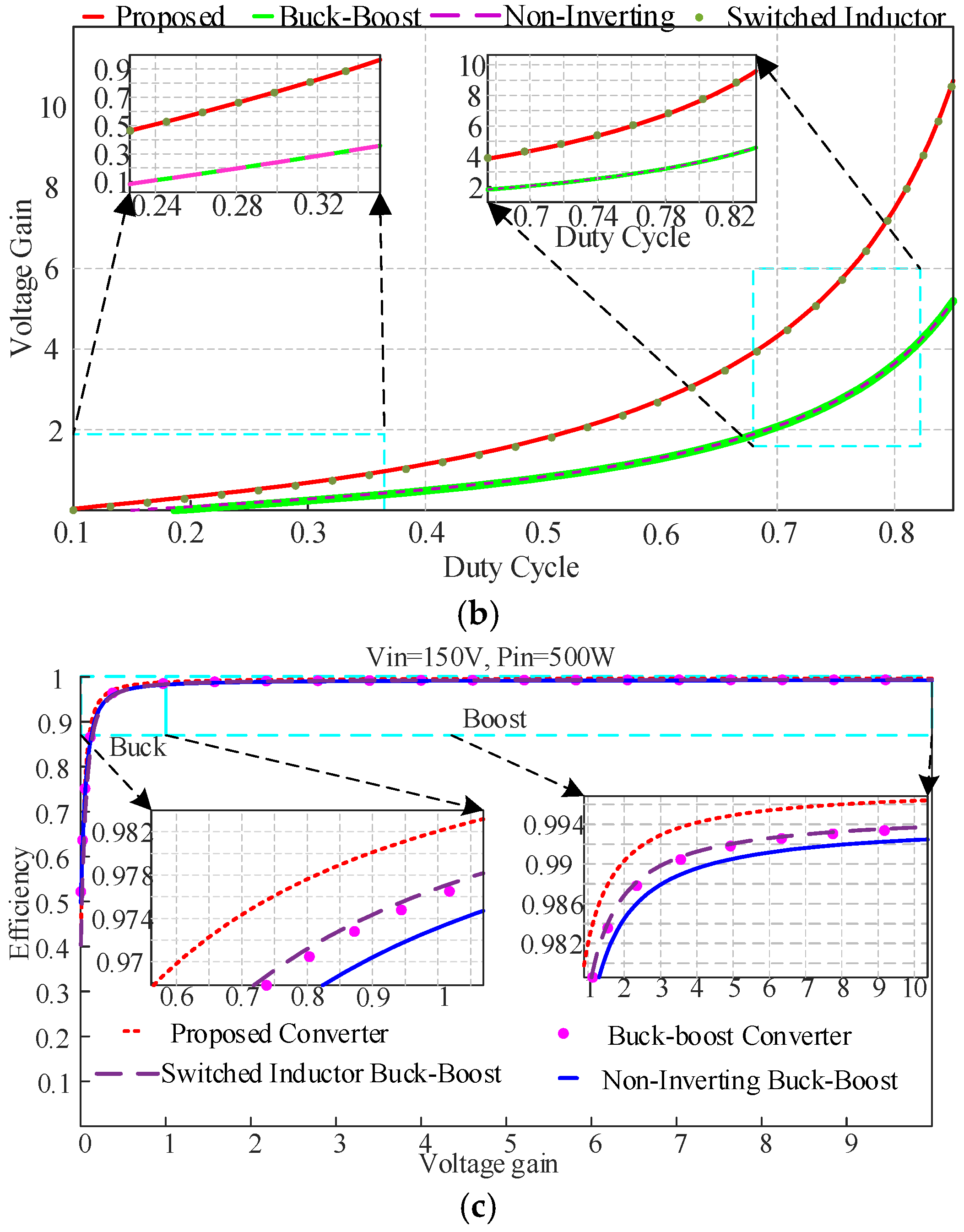

2.4.3. Comparative Study

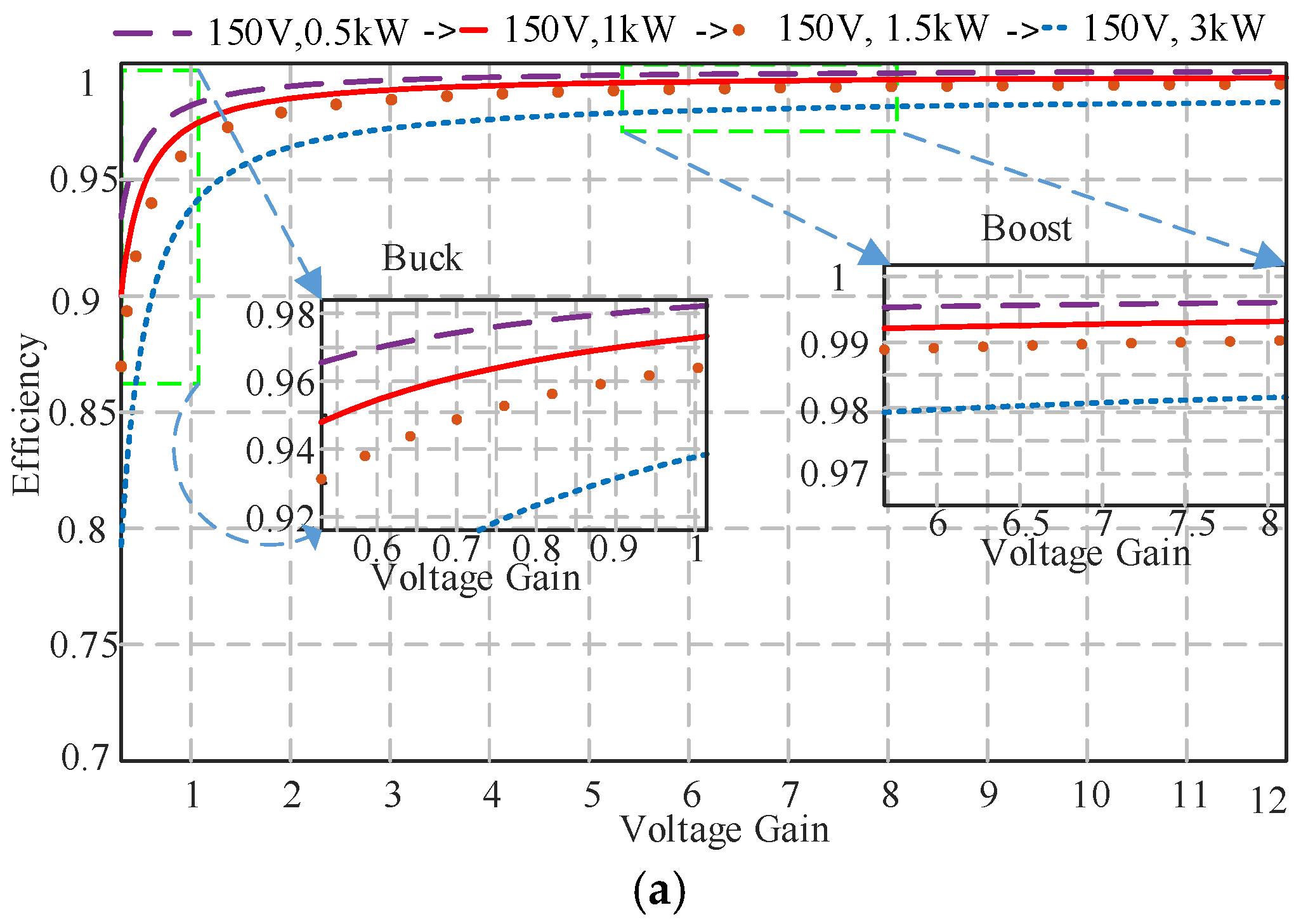

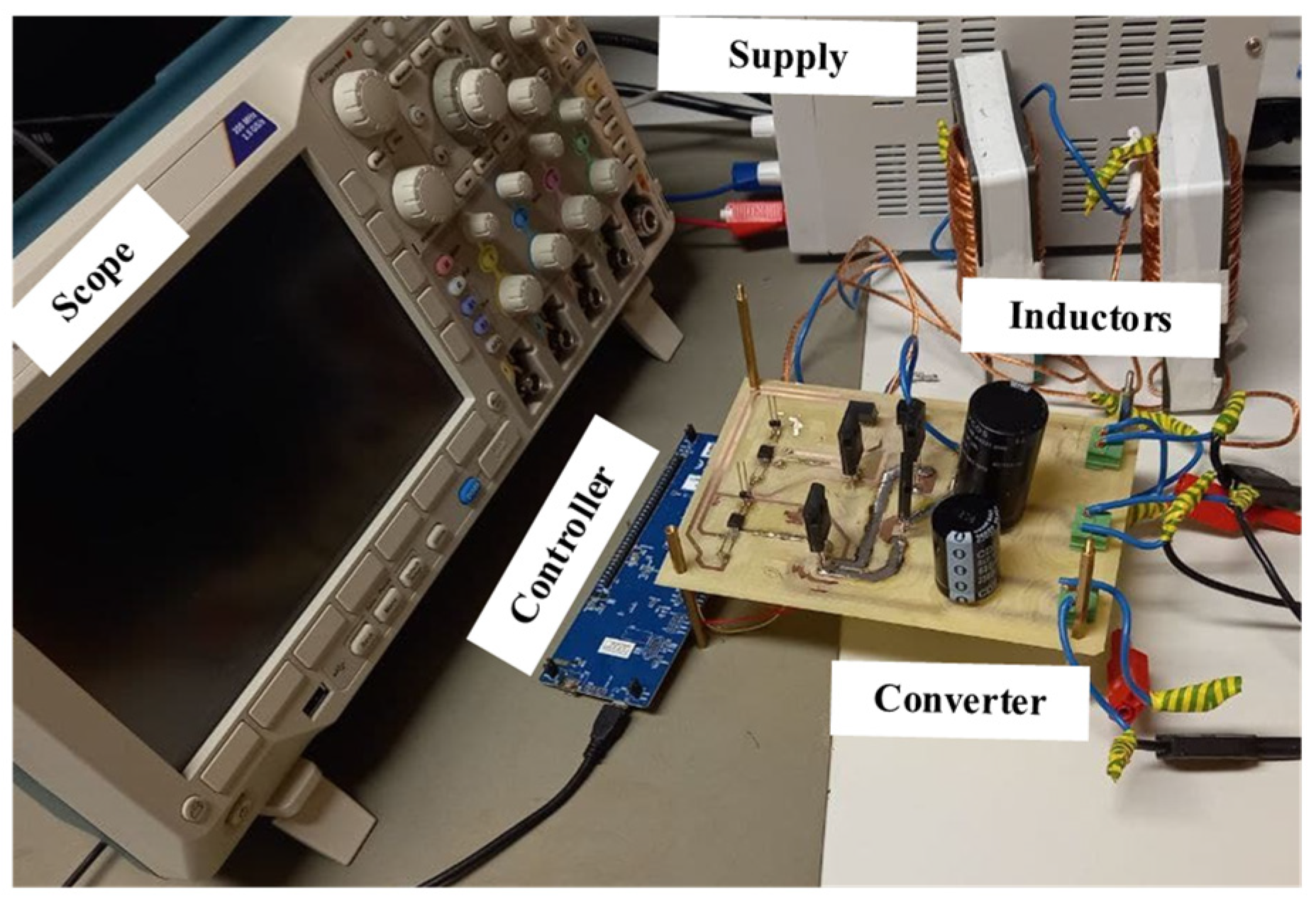

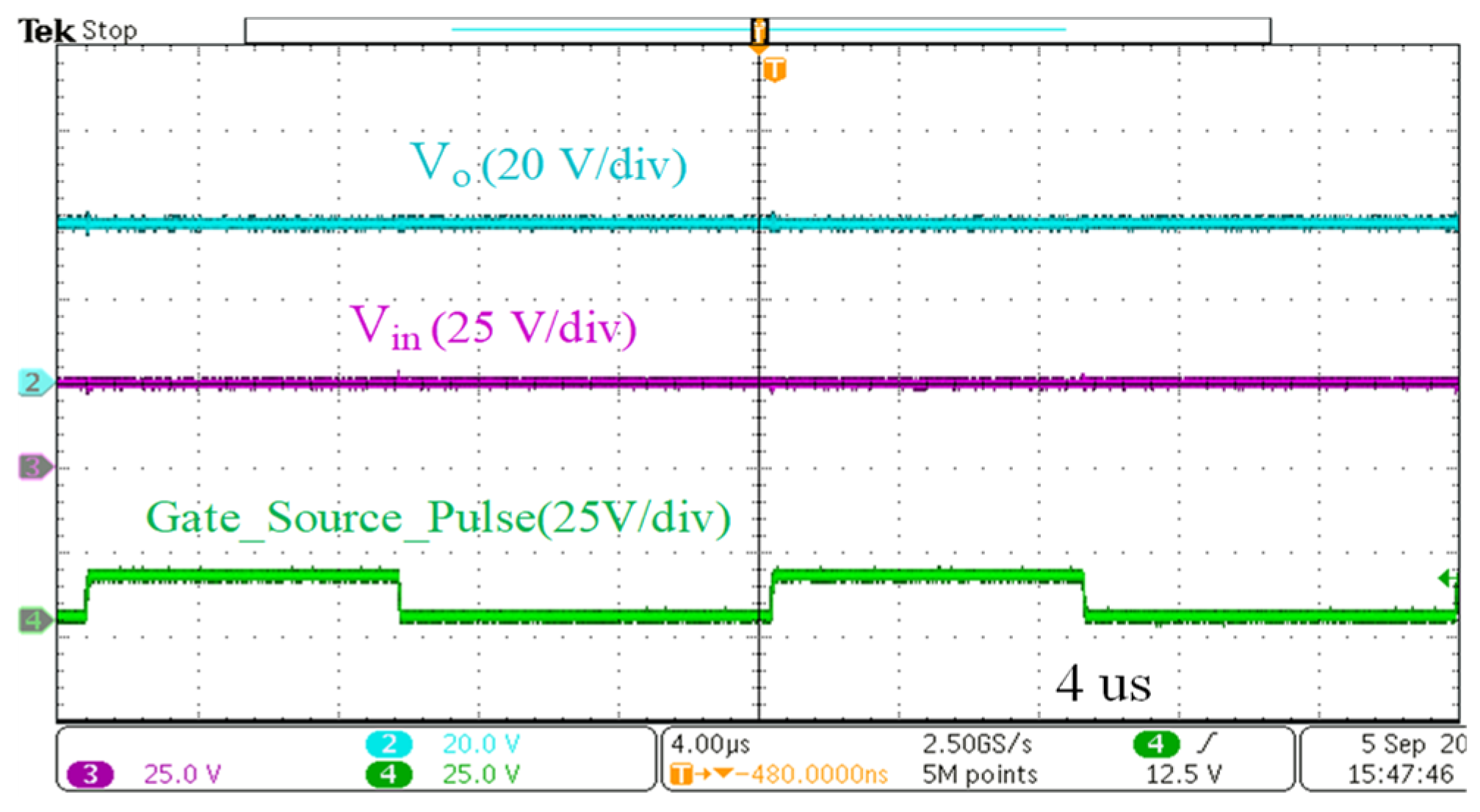

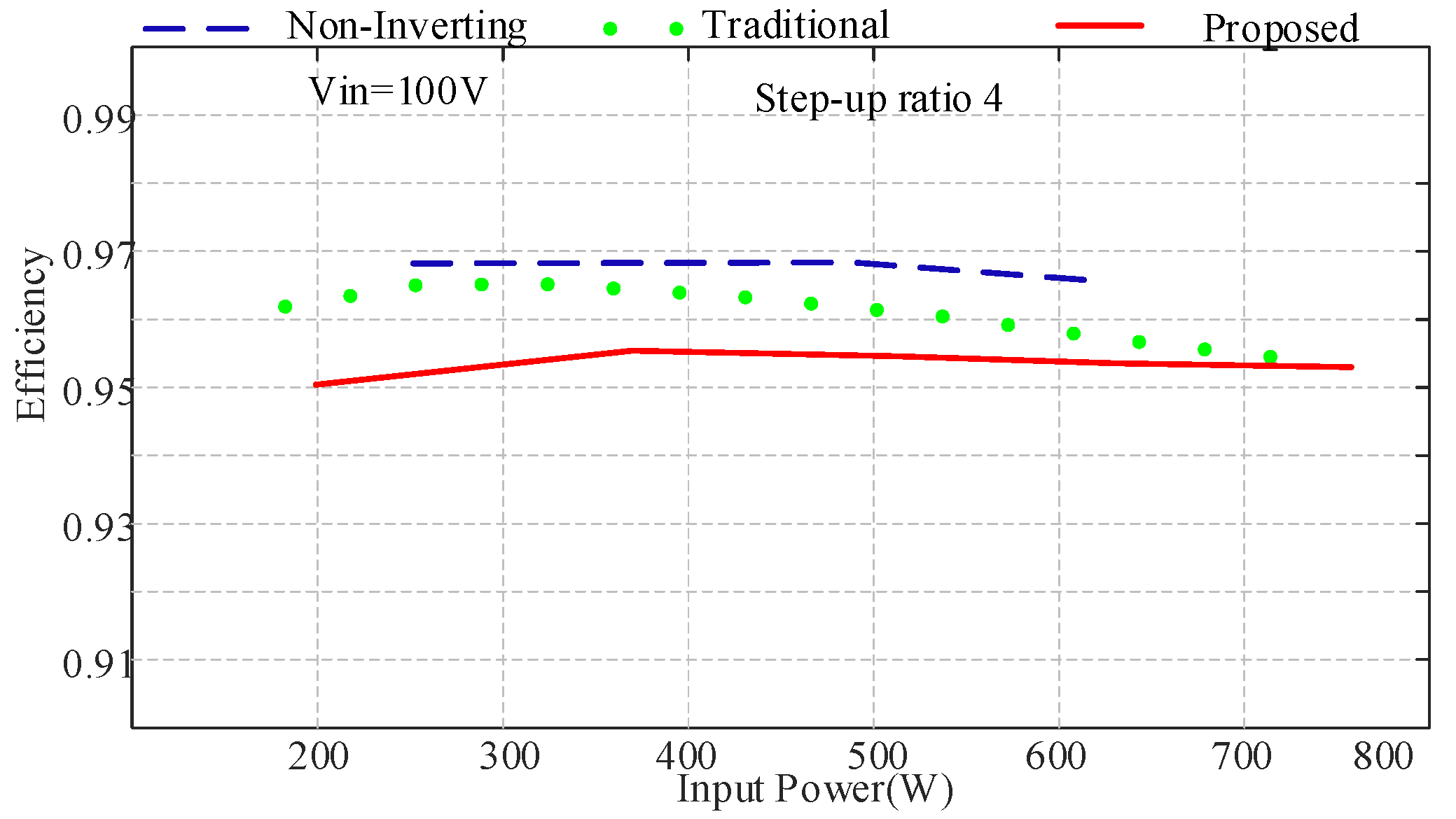

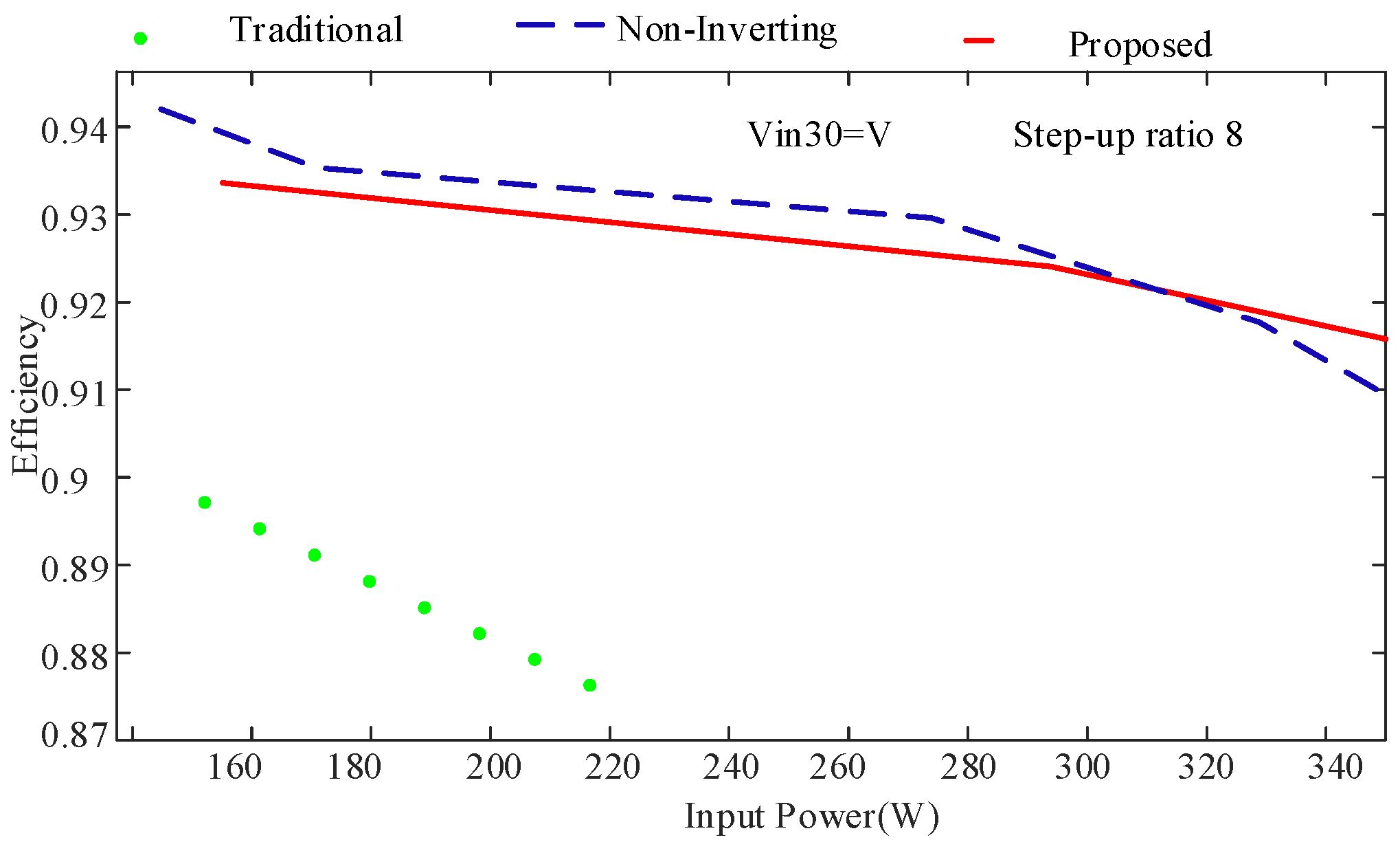

3. Experimental Verification

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Abdel-Rahim, O.; Chub, A.; Blinov, A.; Vinnikov, D. Buck-Boost Resonant Z-Source Parital Power Converter. In Proceedings of the 2022 3rd International Conference on Smart Grid and Renewable Energy (SGRE), Doha, Qatar, 20–22 March 2022; pp. 1–6. [Google Scholar] [CrossRef]

- Abdel-Rahim, O.; Orabi, M.; Ahmed, M.E. Buck-Boost Interleaved Inverter For Grid Connected Photovoltaic System. In Proceedings of the 2010 IEEE International Conference on Power and Energy, Kuala Lumpur, Malaysia, 29 November–1 December 2010; pp. 63–68. [Google Scholar] [CrossRef]

- Callegaro, L.; Ciobotaru, M.; Fletcher, J.E. An Intelligent Pass-Through Algorithm for Non-Inverting Buck-Boost Solar Power Optimizers. In Proceedings of the 2019 21st European Conference on Power Electronics and Applications (EPE ’19 ECCE Europe), Genova, Italy, 3–5 September 2019; pp. P.1–P.10. [Google Scholar] [CrossRef]

- Linares, L.; Erickson, R.W.; MacAlpine, S.; Brandemuehl, M. Improved Energy Capture in Series String Photovoltaics via Smart Distributed Power Electronics. In Proceedings of the 2009 Twenty-Fourth Annual IEEE Applied Power Electronics Conference and Exposition, Washington, DC, USA, 15–19 February 2009; pp. 904–910. [Google Scholar] [CrossRef]

- Abdel-Rahim, O.; Orabi, M.; Ahmed, M.E. High Gain Single-Stage Inverter For Photovoltaic AC Modules. In Proceedings of the 2011 Twenty-Sixth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Fort Worth, TX, USA, 6–11 March 2011; pp. 1961–1967. [Google Scholar] [CrossRef]

- Banaei, M.R.; Bonab, H.A.F. A High Efficiency Nonisolated Buck–Boost Converter Based on ZETA Converter. IEEE Trans. Ind. Electron. 2019, 67, 1991–1998. [Google Scholar] [CrossRef]

- Banaei, M.R.; Bonab, H.A.F. A novel structure for single-switch nonisolated transformerless buck–boost DC–DC con-verte. IEEE Trans. Ind. Electron. 2016, 64, 198–205. [Google Scholar] [CrossRef]

- Ajami, A.; Ardi, H.; Farakhor, A. Design, analysis and implementation of a buck–boost DC/DC converter. IET Power Electron. 2014, 7, 2902–2913. [Google Scholar] [CrossRef]

- Son, H.-S.; Kim, J.-K.; Lee, J.-B.; Moon, S.-S.; Park, J.-H.; Lee, S.-H. A New Buck–Boost Converter With Low-Voltage Stress and Reduced Conducting Components. IEEE Trans. Ind. Electron. 2017, 64, 7030–7038. [Google Scholar] [CrossRef]

- Abdel-Rahim, O.; Furiato, H. Switched Inductor Quadratic Boosting Ratio Inverter With Proportional Resonant Controller For Grid-Tie PV Applications. In Proceedings of the IECON 2014—40th Annual Conference of the IEEE Industrial Electronics Society, Dallas, TX, USA, 29 October–1 November 2014; pp. 5606–5611. [Google Scholar] [CrossRef]

- Maldonado, J.C.M.; Valdez-Resendiz, J.E.E.; Vite, P.M.G.; Rosas-Caro, J.C.; Rivera-Espinosa, M.D.R.; Valderrabano-Gonzalez, A. Quadratic Buck–Boost Converter with Zero Output Voltage Ripple at a Selectable Operating Point. IEEE Trans. Ind. Appl. 2019, 55, 2813–2822. [Google Scholar] [CrossRef]

- Rosas-Caro, J.C.; Valdez-Resendiz, J.E.; Mayo-Maldonado, J.C.; Alejo-Reyes, A.; Valderrabano-Gonzalez, A. Quadratic buck–boost converter with positive output voltage and minimum ripple point design. IET Power Electron. 2018, 11, 1306–1313. [Google Scholar] [CrossRef]

- Nousiainen, L.; Suntio, T. Dynamic characteristics of current-fed semi-quadratic buck-boost converter in photovoltaic applications. In Proceedings of the 2011 IEEE Energy Conversion Congress and Exposition, Phoenix, AZ, USA, 17–22 September 2011; pp. 1031–1038. [Google Scholar] [CrossRef]

- Yari, K.; Shahalami, S.H.; Mojallali, H. A Novel Nonisolated Buck–Boost Converter with Continuous Input Current and Semiquadratic Voltage Gain. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 9, 6124–6138. [Google Scholar] [CrossRef]

- Yari, K.; Mojallali, H.; Shahalami, S.H. A New Coupled-Inductor-Based Buck–Boost DC–DC Converter for PV Applications. IEEE Trans. Power Electron. 2021, 37, 687–699. [Google Scholar] [CrossRef]

- AL-Hakeem, K.M.; Ahmad, O.A. Buck-Boost In-Out of Phase Y-source AC Matrix Converter. In Proceedings of the 2018 Third Scientific Conference of Electrical Engineering (SCEE), Baghdad, Iraq, 19–20 December 2018; pp. 274–279. [Google Scholar] [CrossRef]

- Abdel-Rahim, O.; Chub, A.; Blinov, A.; Vinnikov, D. New High-Gain Non-Inverting Buck-Boost Converter. In Proceedings of the IECON 2021—47th Annual Conference of the IEEE Industrial Electronics Society, Toronto, ON, Canada, 13–16 October 2021; pp. 1–6. [Google Scholar] [CrossRef]

- Smedley, K.; Cuk, S. Dynamics of one-cycle controlled Cuk converters. IEEE Trans. Power Electron. 1995, 10, 634–639. [Google Scholar] [CrossRef] [Green Version]

- Ericson, R.; Maksimovic, D. Fundamentals of Power Electronics; Kluwer Academic Publishers: Dordrecht, The Netherlands, 2007. [Google Scholar]

- Abdel-Rahim, O.; Orabi, M.; Abdelkarim, E.; Ahmed, M.; Youssef, M.Z. Switched Inductor Boost Converter For PV Applications. In Proceedings of the 2012 Twenty-Seventh Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Orlando, FL, USA, 5–9 February 2012; pp. 2100–2106. [Google Scholar] [CrossRef]

- Lakshmi, M.; Hemamalini, S. Nonisolated High Gain DC–DC Converter for DC Microgrids. IEEE Trans. Ind. Electron. 2017, 65, 1205–1212. [Google Scholar] [CrossRef]

- Sarikhani, A.; Allahverdinejad, B.; Hamzeh, M. A Nonisolated Buck–Boost DC–DC Converter with Continuous Input Current for Photovoltaic Applications. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 9, 804–811. [Google Scholar] [CrossRef]

- Miao, S.; Wang, F.; Ma, X. A New Transformerless Buck–Boost Converter with Positive Output Voltage. IEEE Trans. Ind. Electron. 2016, 63, 2965–2975. [Google Scholar] [CrossRef]

| Converter Topology | Gain M = Vo/Vin | Components’ Count | Switches’ and Diodes’ Voltage Stress | Switches’ and Diodes’ Current Stress | |||

|---|---|---|---|---|---|---|---|

| Switch | Diode | L | C | ||||

| Buck-Boost [18] | (D/(1-D)) | 1 | 1 | 1 | 1 | S:Vo | IL |

| D:(Vo+Vin) | IL | ||||||

| Non-Inverting [19] | (D/(1-D)) | 2 | 2 | 1 | 1 | S1:Vin | IL |

| S2:Vo | IL | ||||||

| D1:Vin | IL | ||||||

| Do:Vo | IL | ||||||

| Cuk [5] | (D/(1-D)) | 1 | 2 | 2 | 1 | S1:Vin/(1-D) | IL |

| D1:Vin | IL | ||||||

| Do:Vo | IL | ||||||

| SEPIC [19] | (D/(1-D)) | 1 | 1 | 2 | 2 | S1:Vo+Vin | 2IL |

| D1:Vo+Vin | IL | ||||||

| SIBBC [20] | 2D/(1-D) | 1 | 4 | 2 | 1 | S1:Vo+Vin | 2IL |

| D1:Vin | IL | ||||||

| D2:Vo/2 | IL | ||||||

| D3:Vo/2 | IL | ||||||

| Do:Vo+Vin | IL | ||||||

| Lakshmi [21] | (1+D1)/(1-D1-D2) | 3 | 2 | 2 | 1 | S1:(Vo+Vin)/2 | IL |

| S2:(Vo+Vin)/2 | IL | ||||||

| S3:Vo | IL | ||||||

| D1:Vo | IL | ||||||

| Do:Vo+Vin | IL | ||||||

| [22] | 2D/(1-D)2 | 2 | 3 | 2 | 3 | S1:1/(1-D)*Vin | IL |

| S2:Vin *(1+D)/(1-D)2 | IL | ||||||

| D1:Vin/(1-D) | IL | ||||||

| D2:Vin/(1-D) | IL | ||||||

| Do:Vo+Vin/(1-D) | IL | ||||||

| [23] | D2/(1-D)2 | 2 | 2 | 2 | 2 | S1:1/(1-D)*Vin | 2IL |

| S2:Vin *D/(1-D)2 | IL | ||||||

| D1:Vin/(1-D) | IL | ||||||

| D2:Vin*D/(1-D)2 | IL | ||||||

| Proposed | 2D/(1-D) | 3 | 2 | 2 | 1 | S1:Vin | 2IL |

| S2:Vo/2 | IL | ||||||

| S3:Vo/2 | IL | ||||||

| D1:Vin | IL | ||||||

| Do:Vo+Vin | IL | ||||||

| Parameter | Value |

|---|---|

| Input voltage range [V] | 33–150 |

| P [W] | 700 W |

| Fs Switching Frequency | 30 kHz |

| Switches S1, S2, S3 | IMZ120R030M1HXKSA1 |

| Diodes D1, Do | DPG10I300PA |

| Inductors L1 = L2 | 1 mH |

| Capacitor Co | 320 µF |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Abdel-Rahim, O.; Chub, A.; Blinov, A.; Vinnikov, D.; Peftitsis, D. An Efficient Non-Inverting Buck-Boost Converter with Improved Step Up/Down Ability. Energies 2022, 15, 4550. https://doi.org/10.3390/en15134550

Abdel-Rahim O, Chub A, Blinov A, Vinnikov D, Peftitsis D. An Efficient Non-Inverting Buck-Boost Converter with Improved Step Up/Down Ability. Energies. 2022; 15(13):4550. https://doi.org/10.3390/en15134550

Chicago/Turabian StyleAbdel-Rahim, Omar, Andrii Chub, Andrei Blinov, Dmitri Vinnikov, and Dimosthenis Peftitsis. 2022. "An Efficient Non-Inverting Buck-Boost Converter with Improved Step Up/Down Ability" Energies 15, no. 13: 4550. https://doi.org/10.3390/en15134550

APA StyleAbdel-Rahim, O., Chub, A., Blinov, A., Vinnikov, D., & Peftitsis, D. (2022). An Efficient Non-Inverting Buck-Boost Converter with Improved Step Up/Down Ability. Energies, 15(13), 4550. https://doi.org/10.3390/en15134550