Transient Stability Analysis and Post-Fault Restart Strategy for Current-Limited Grid-Forming Converter

Abstract

:1. Introduction

- To address the aforementioned issues, this manuscript investigates the transient stability of grid-forming converters in the post-fault period. The dynamic performance of the grid-forming converter changes under current saturation, which is analyzed in this manuscript by large-signal modelling and by considering current saturation, and provides a theoretical basis for subsequent optimization of the control strategy.

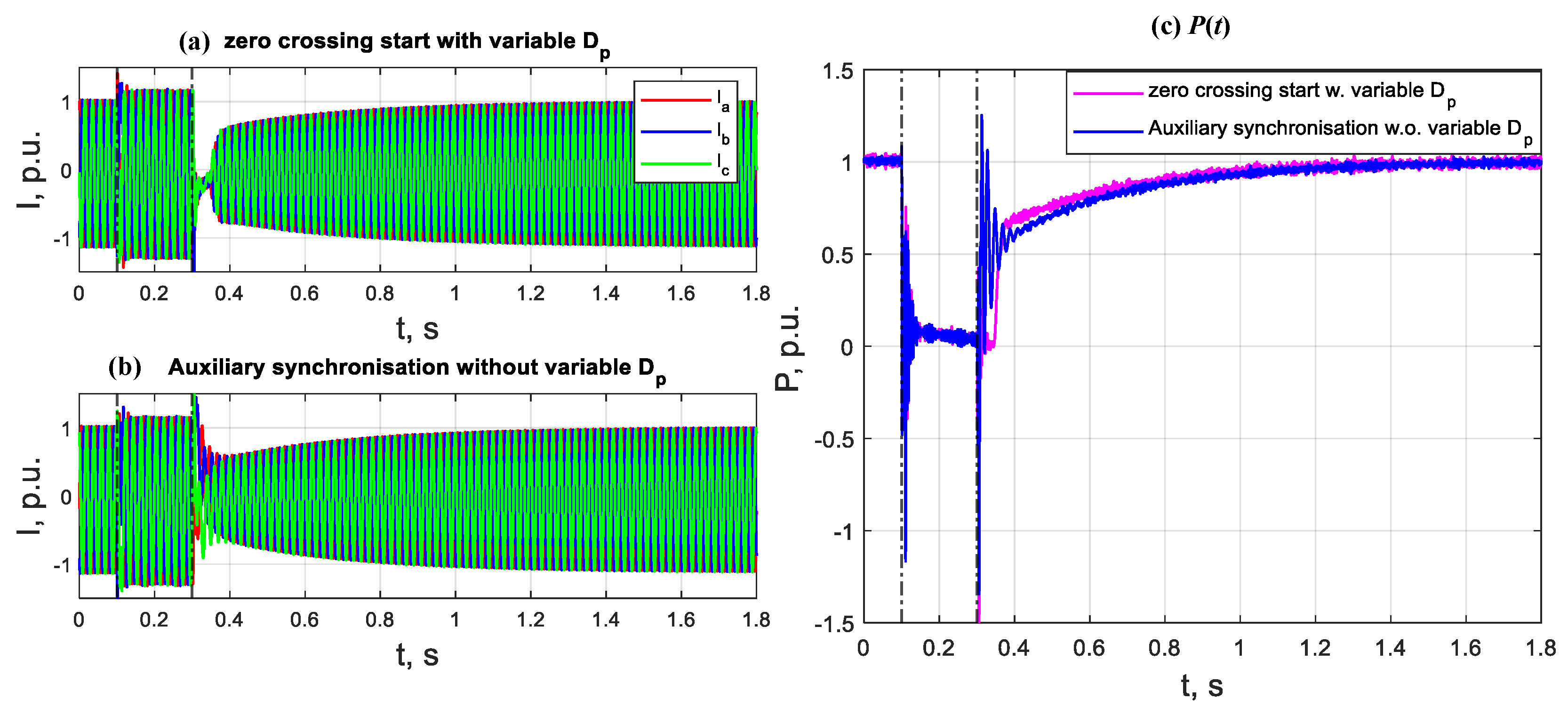

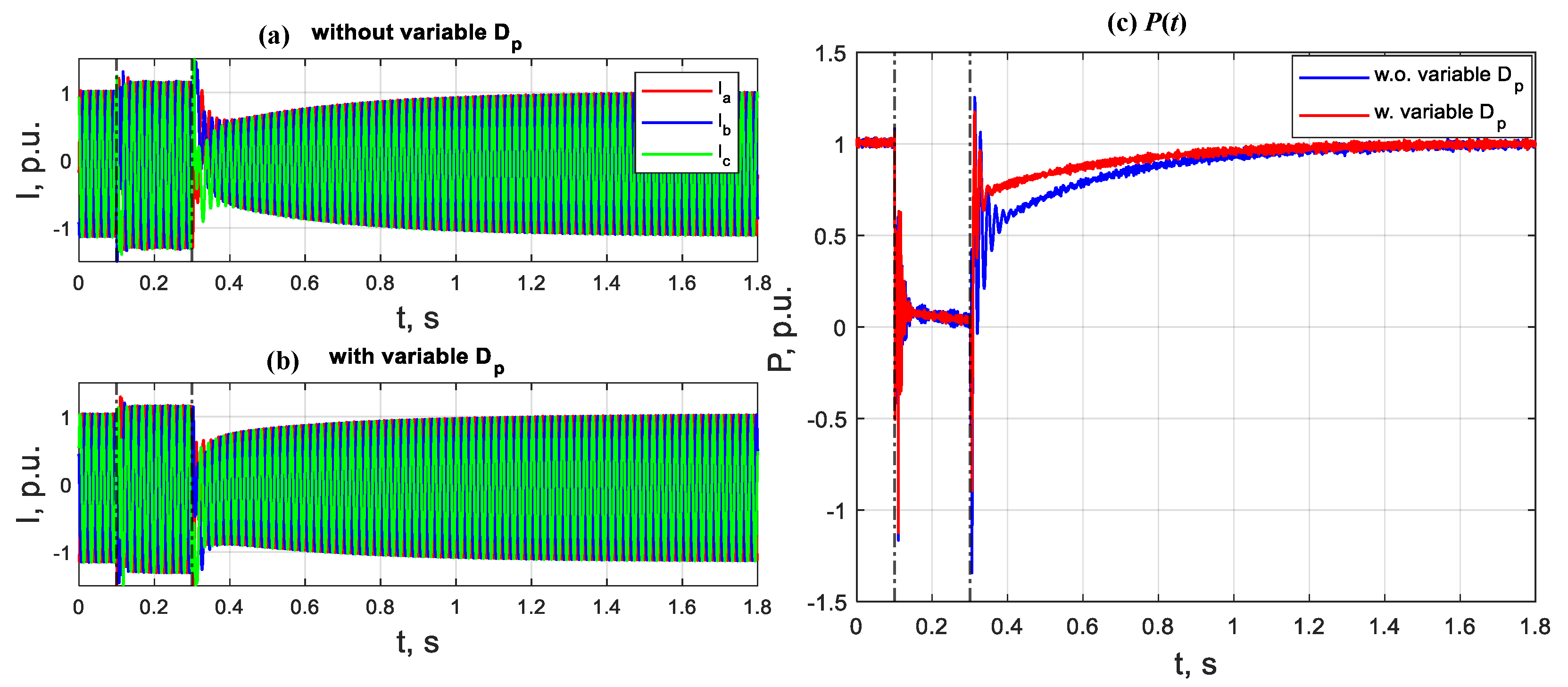

- In order to reduce the impact on the grid during the post-fault period, and in order to avoid instability, several restart strategies are proposed, such as a voltage zero-crossing start and an auxiliary synchronization strategy. In addition, control methods based on variable control parameters are proposed. The use of these strategies avoids putting the converter into current saturation during post-fault periods and allows for an increased rate of resynchronization and the speed up of the active power recovery after the restart to assist the grid in restoring active power balance.

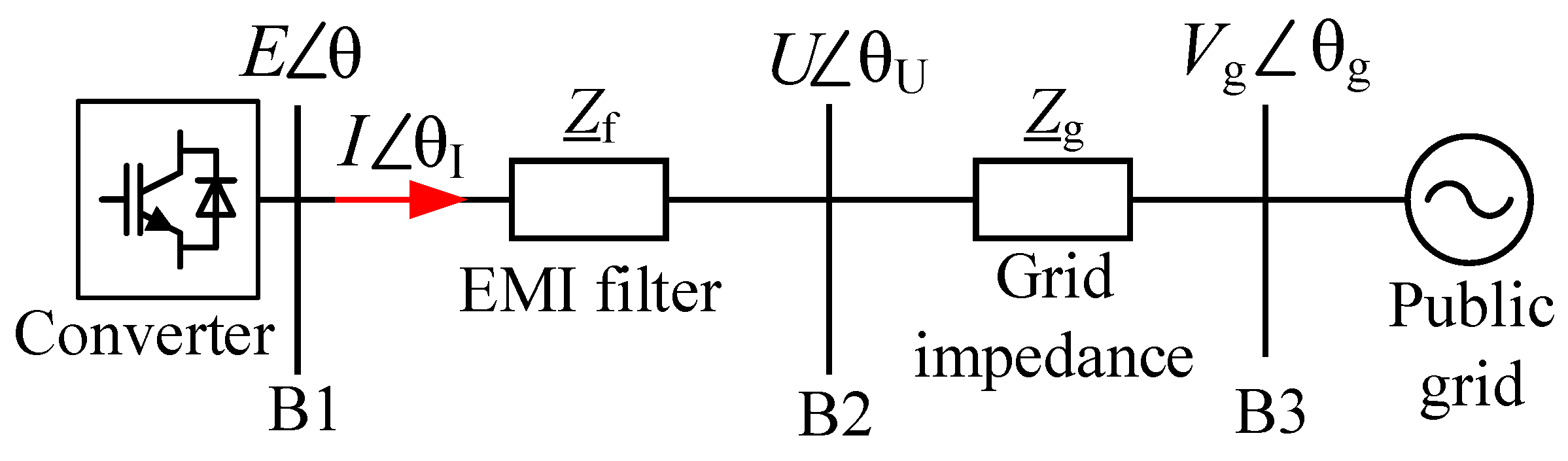

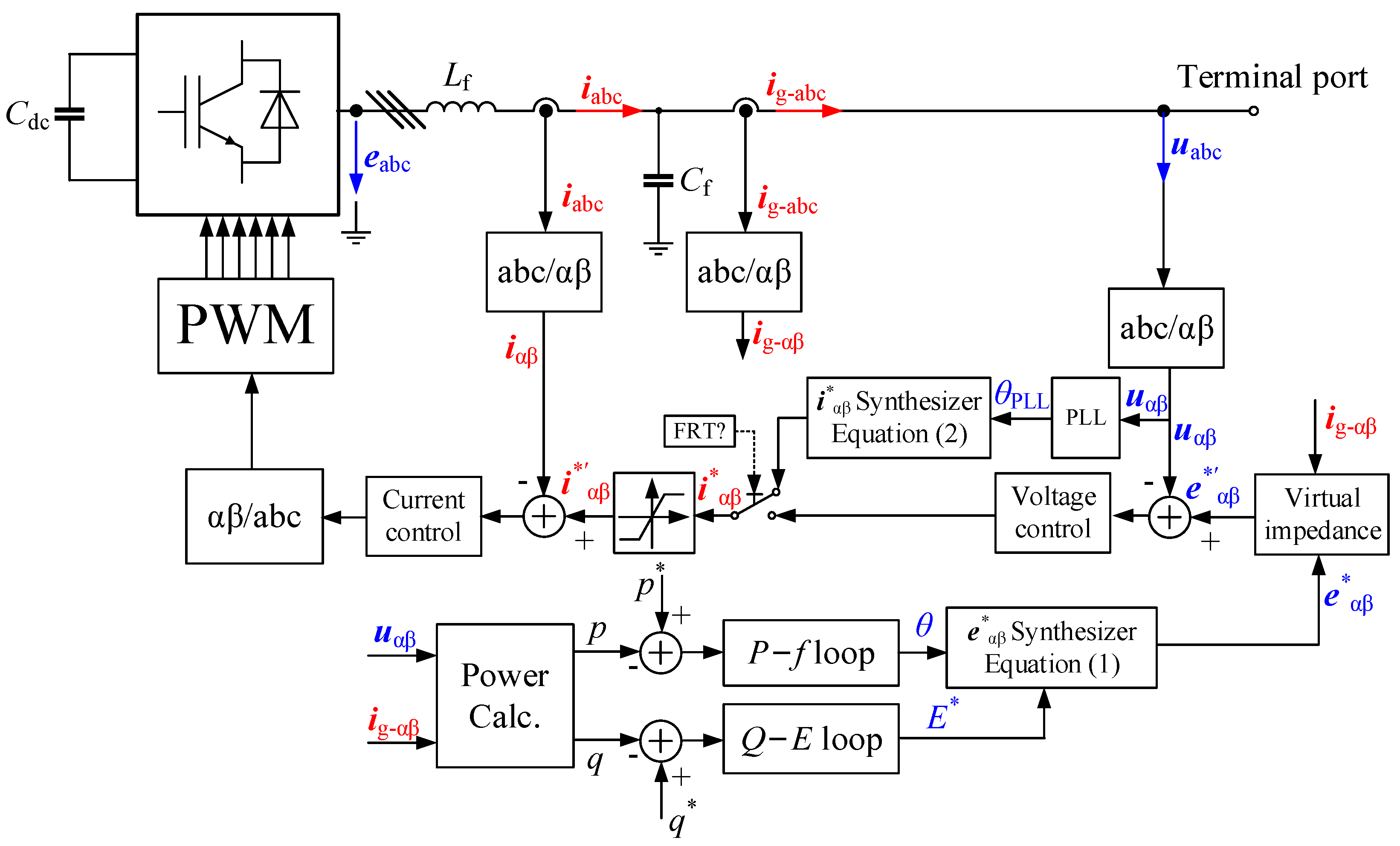

2. Large-Signal Analysis of the Grid-Forming Converter

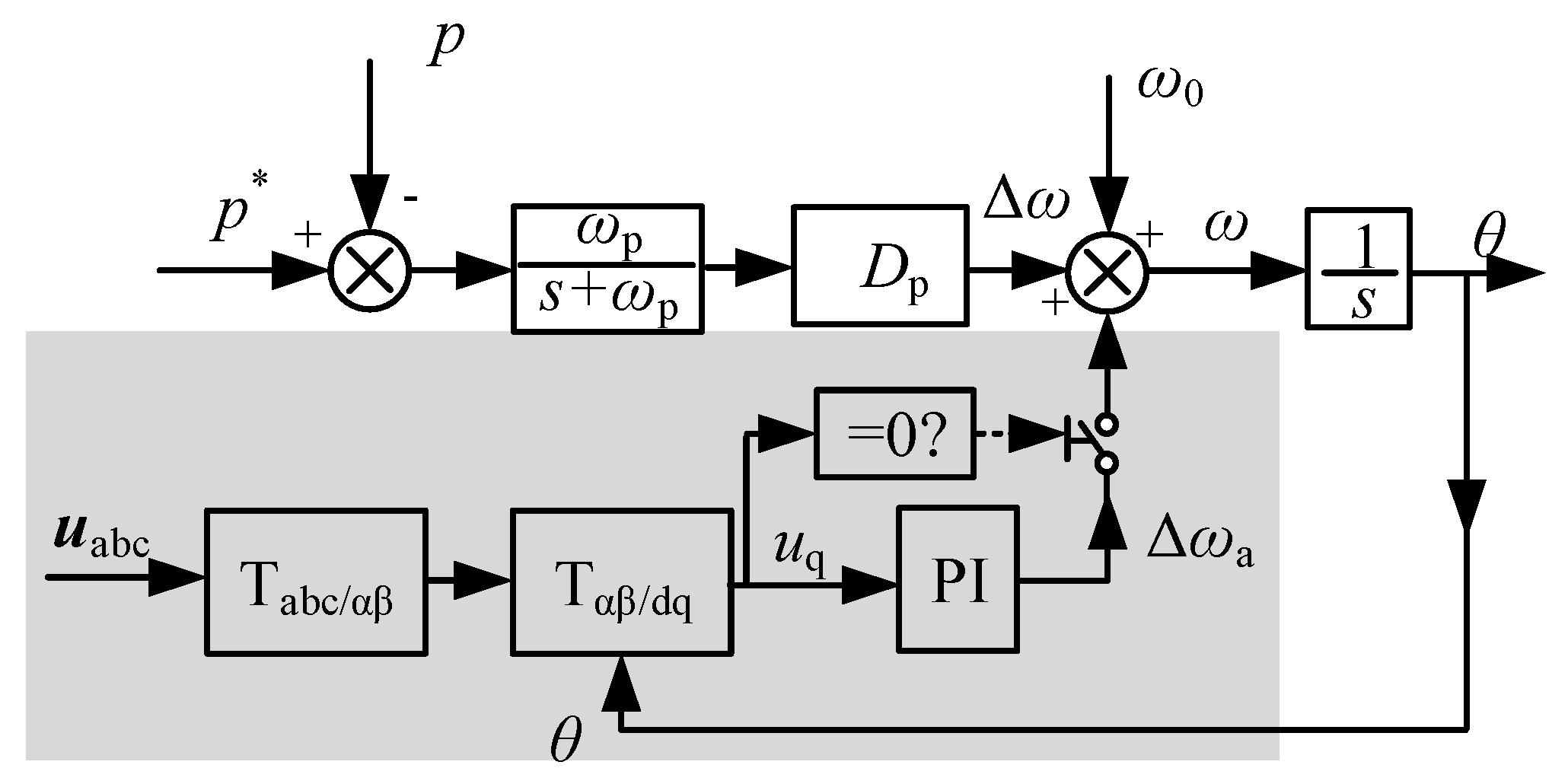

2.1. Control Strategies

2.2. Current-Unsaturated Converter-Grid System

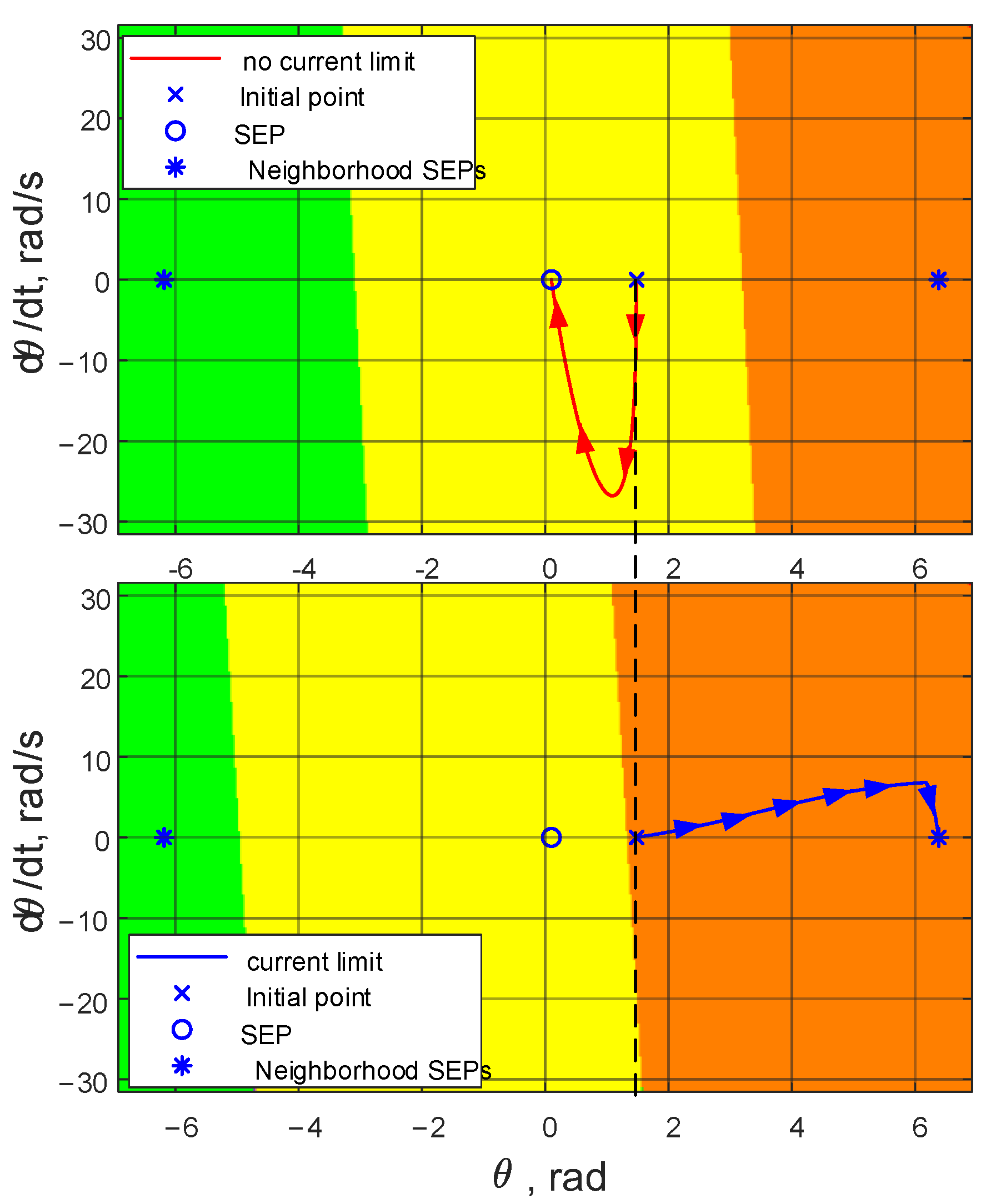

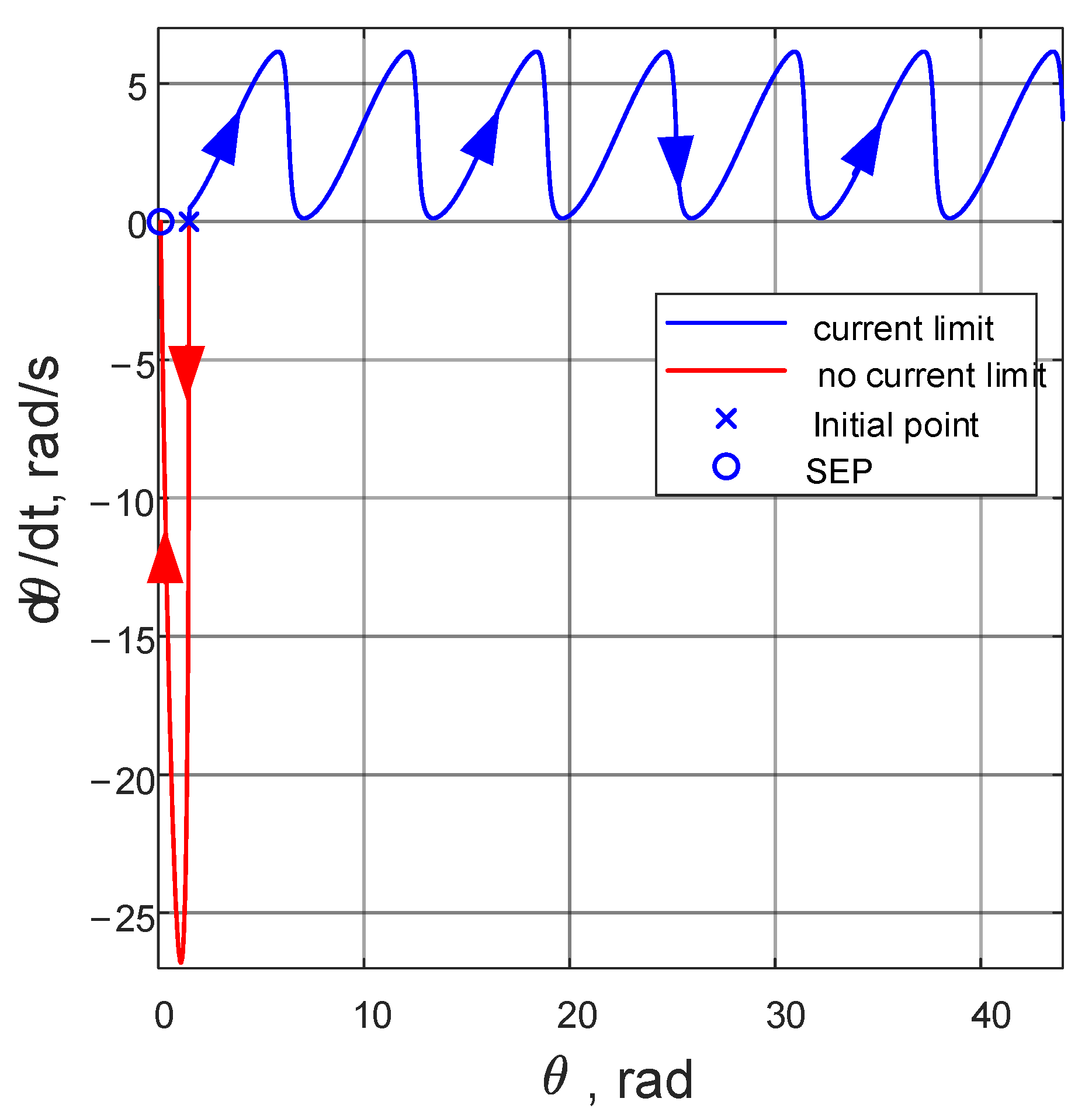

2.3. Current-Saturated Converter-Grid System

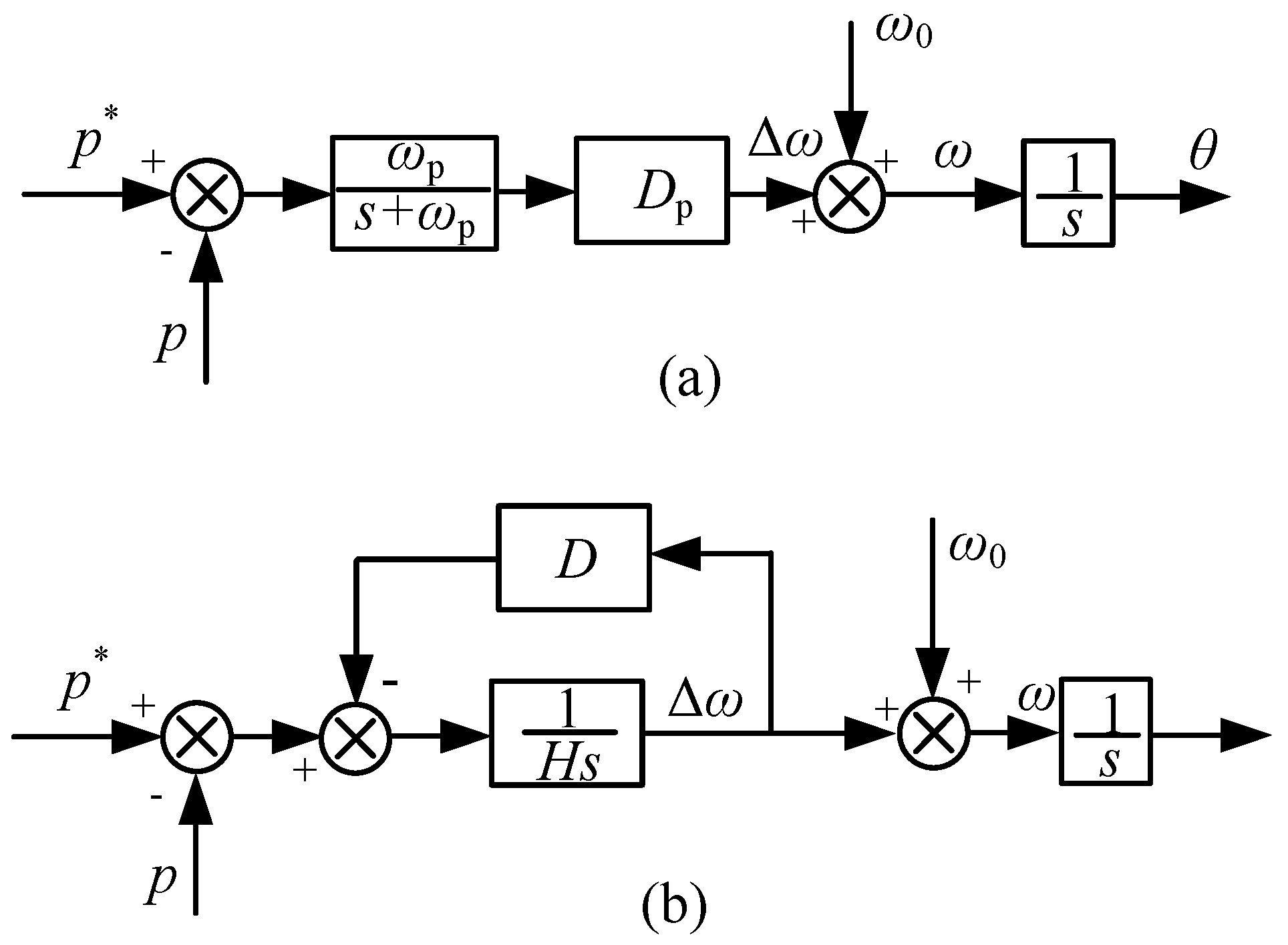

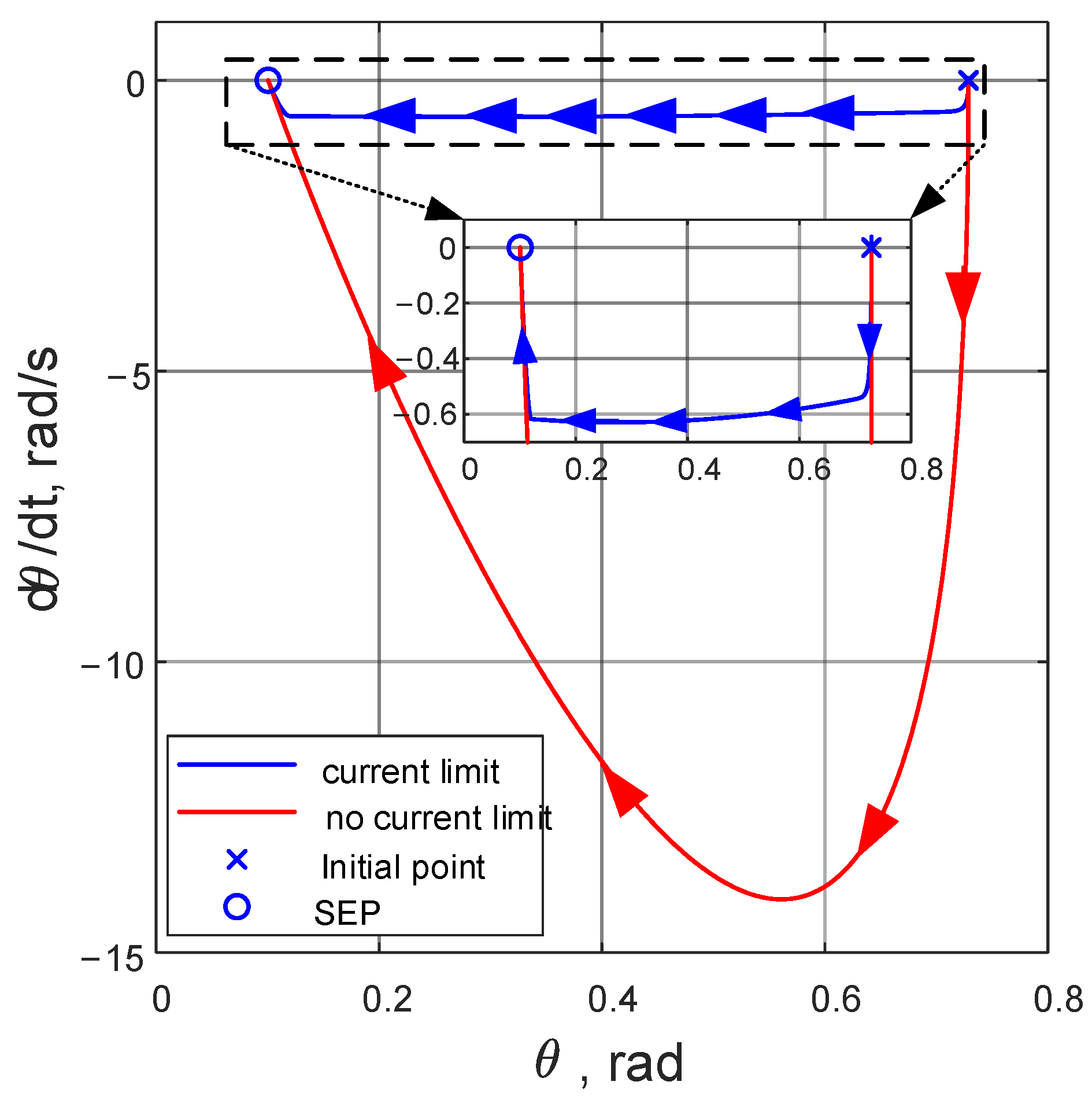

3. Investigation of Dynamic Performance during and after Fault

3.1. During a Fault

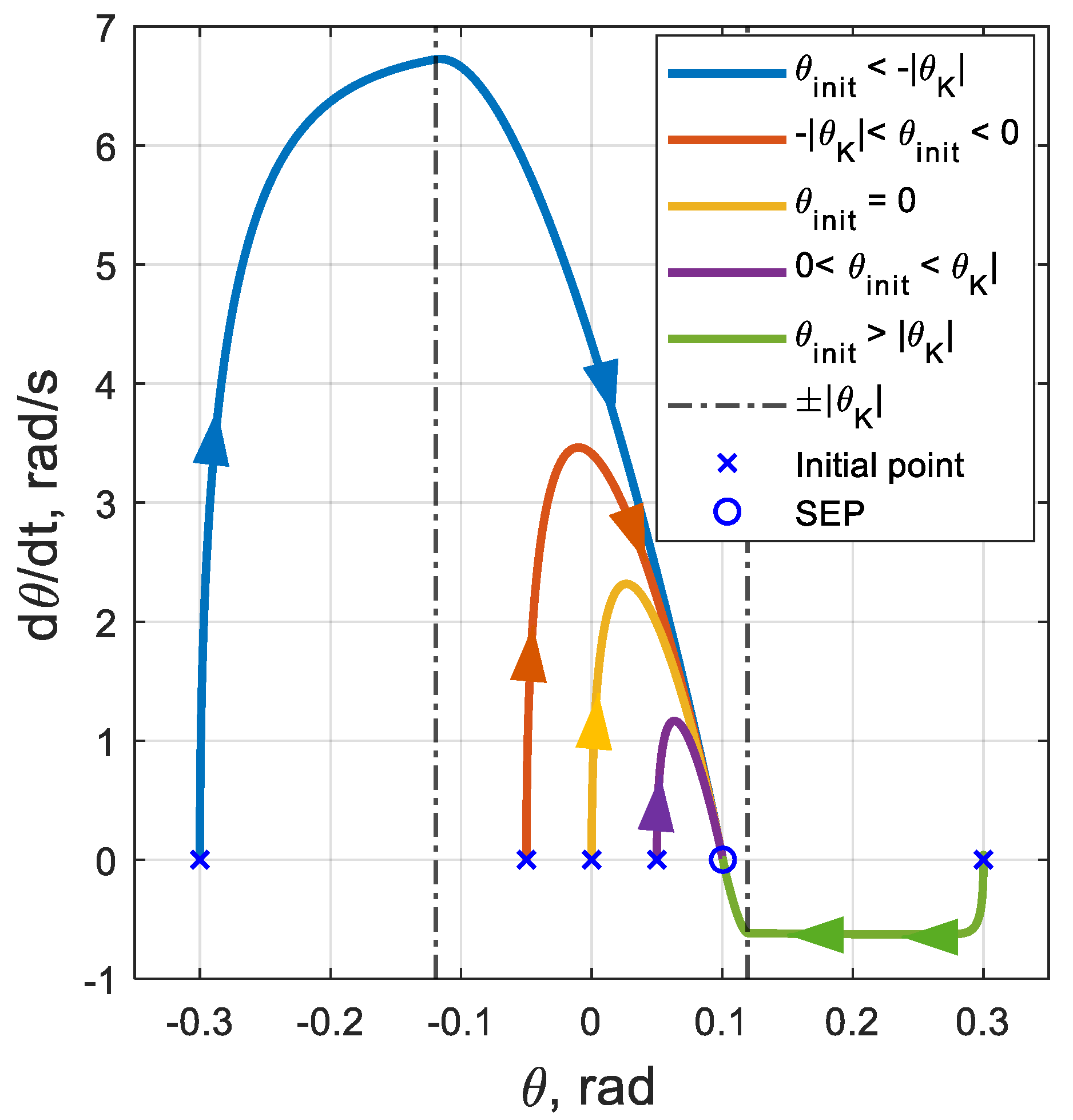

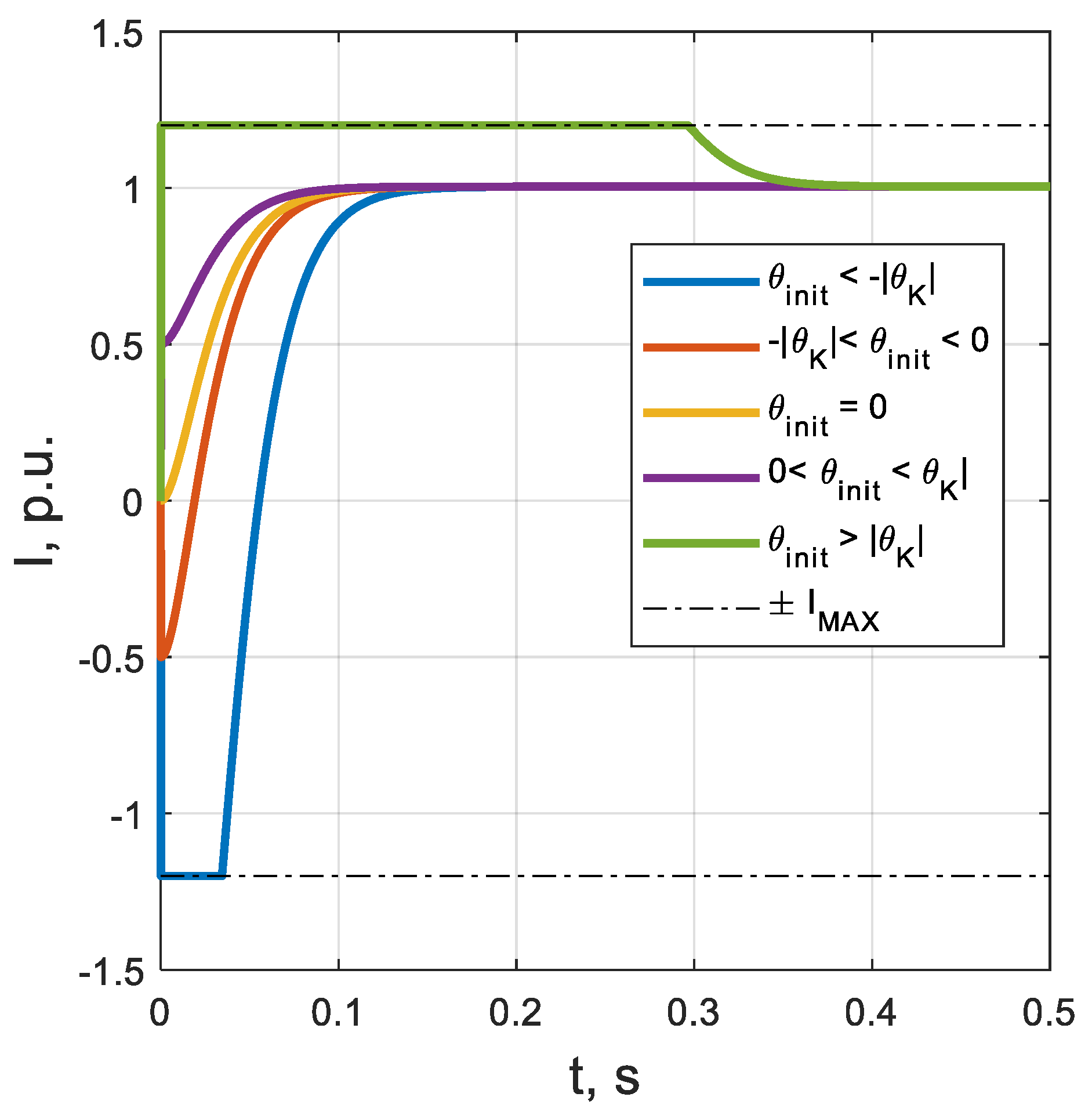

3.2. Post-Fault Clearing

3.3. Post-Fault Restart Strategy

3.3.1. Restart with Voltage Zero-Crossing Detection

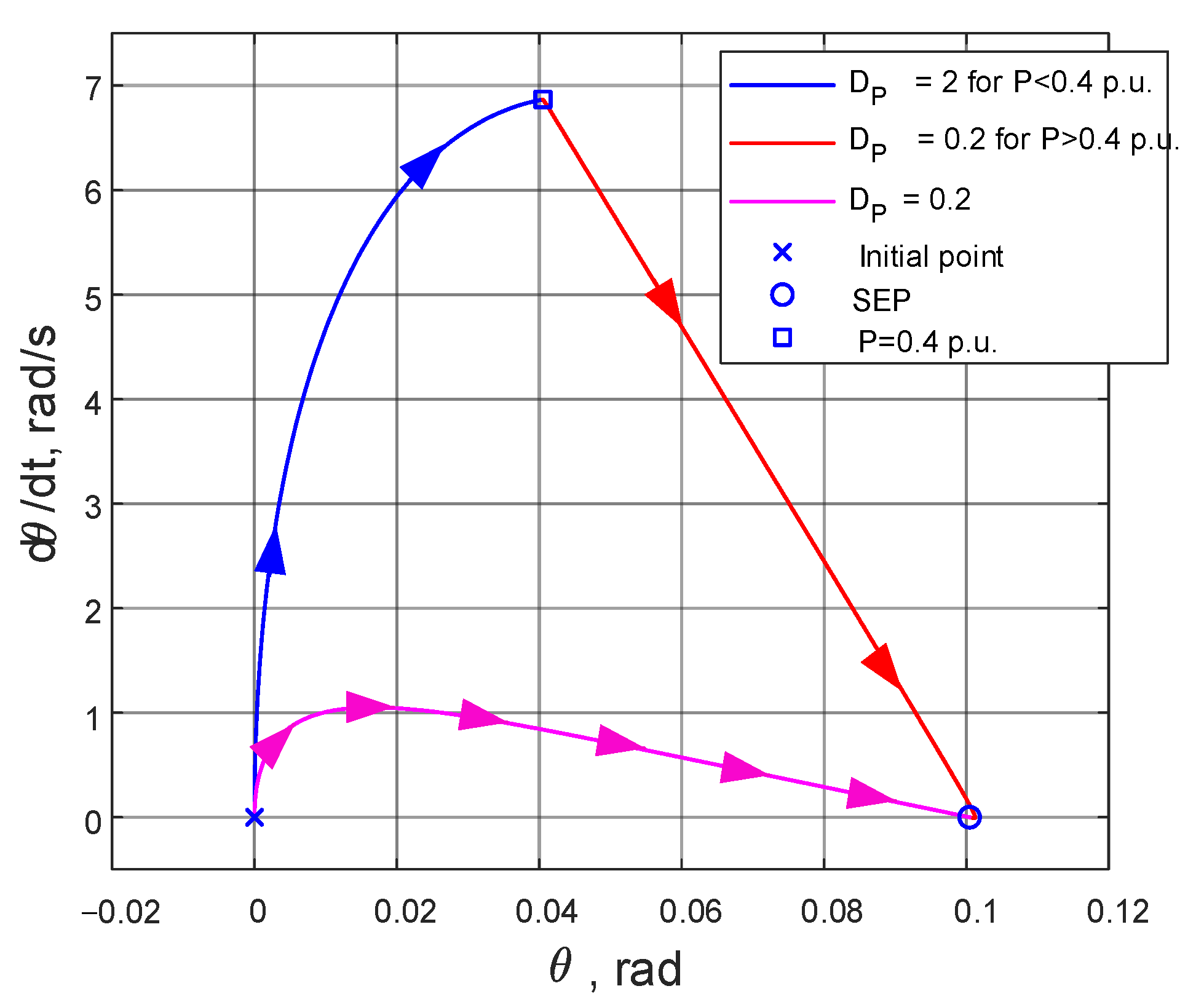

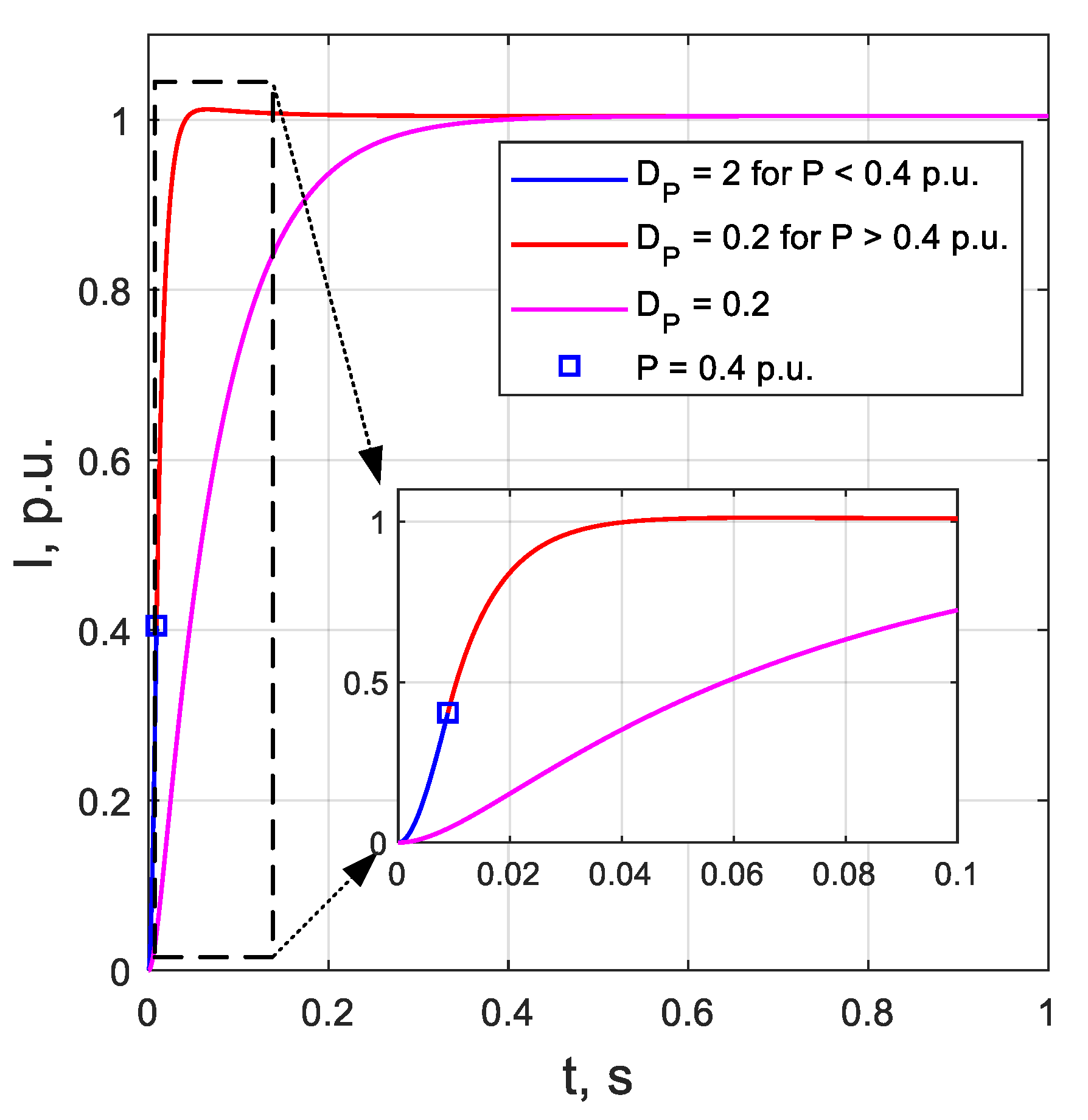

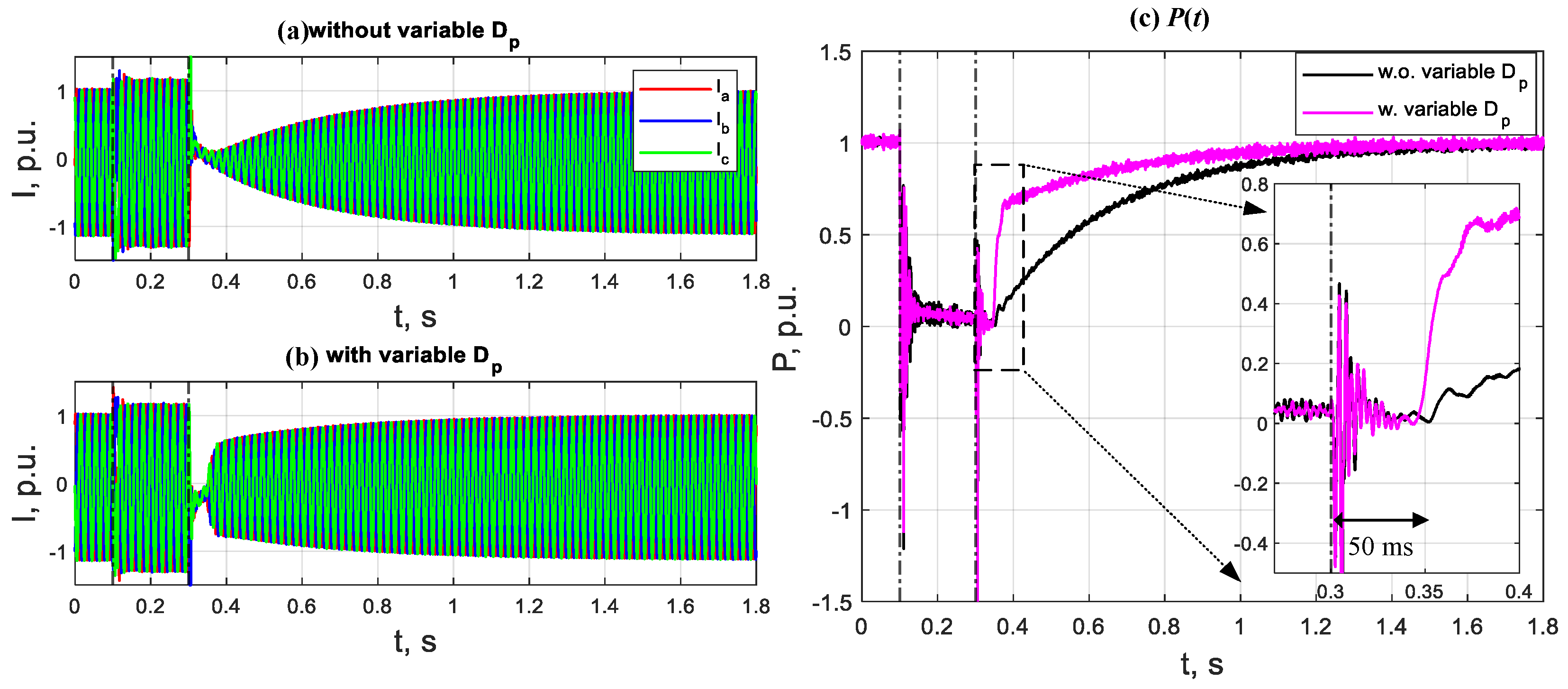

3.3.2. Restart with Variable Droop Factor

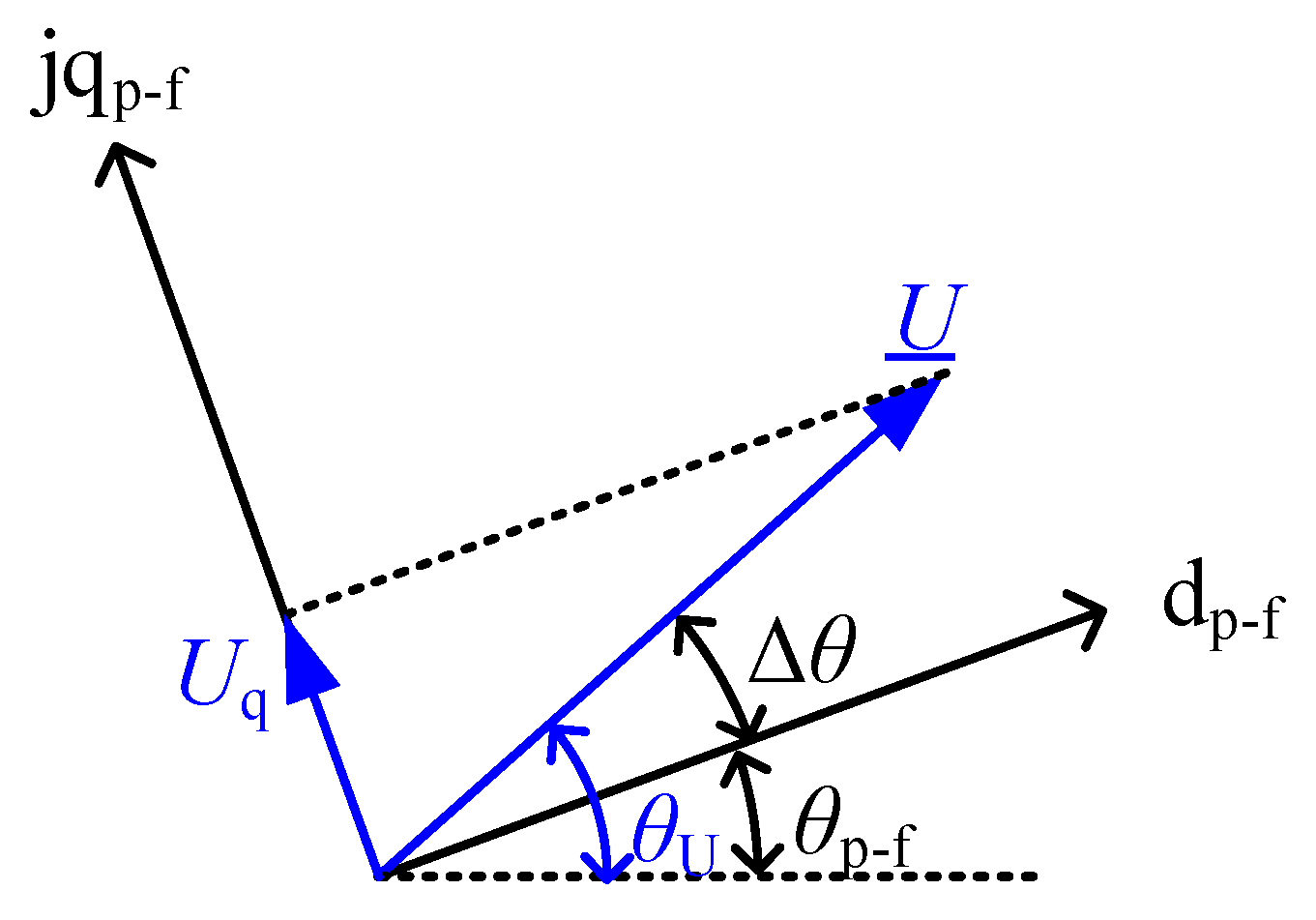

3.3.3. Restart with Auxiliary Synchronization

4. Test Verification

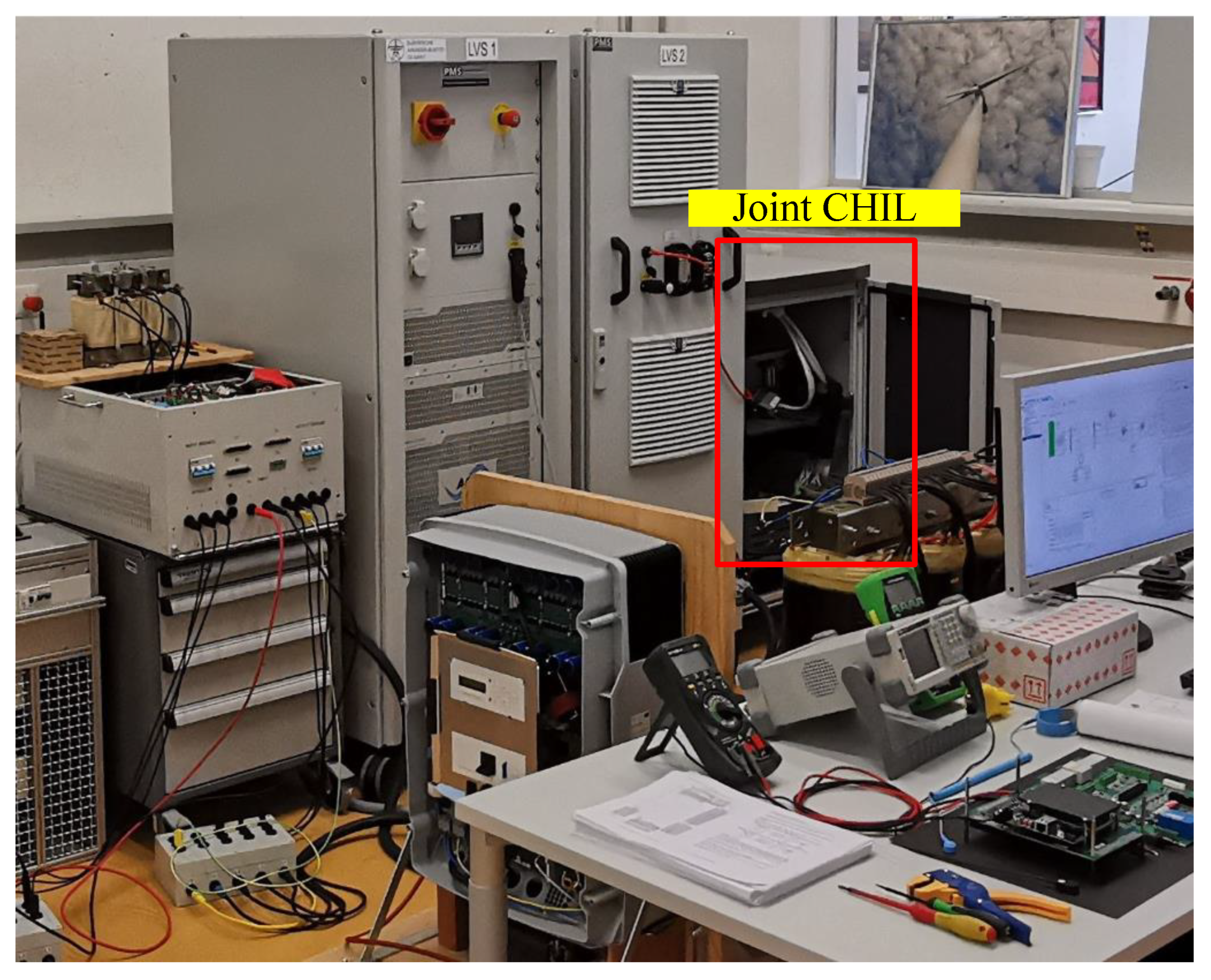

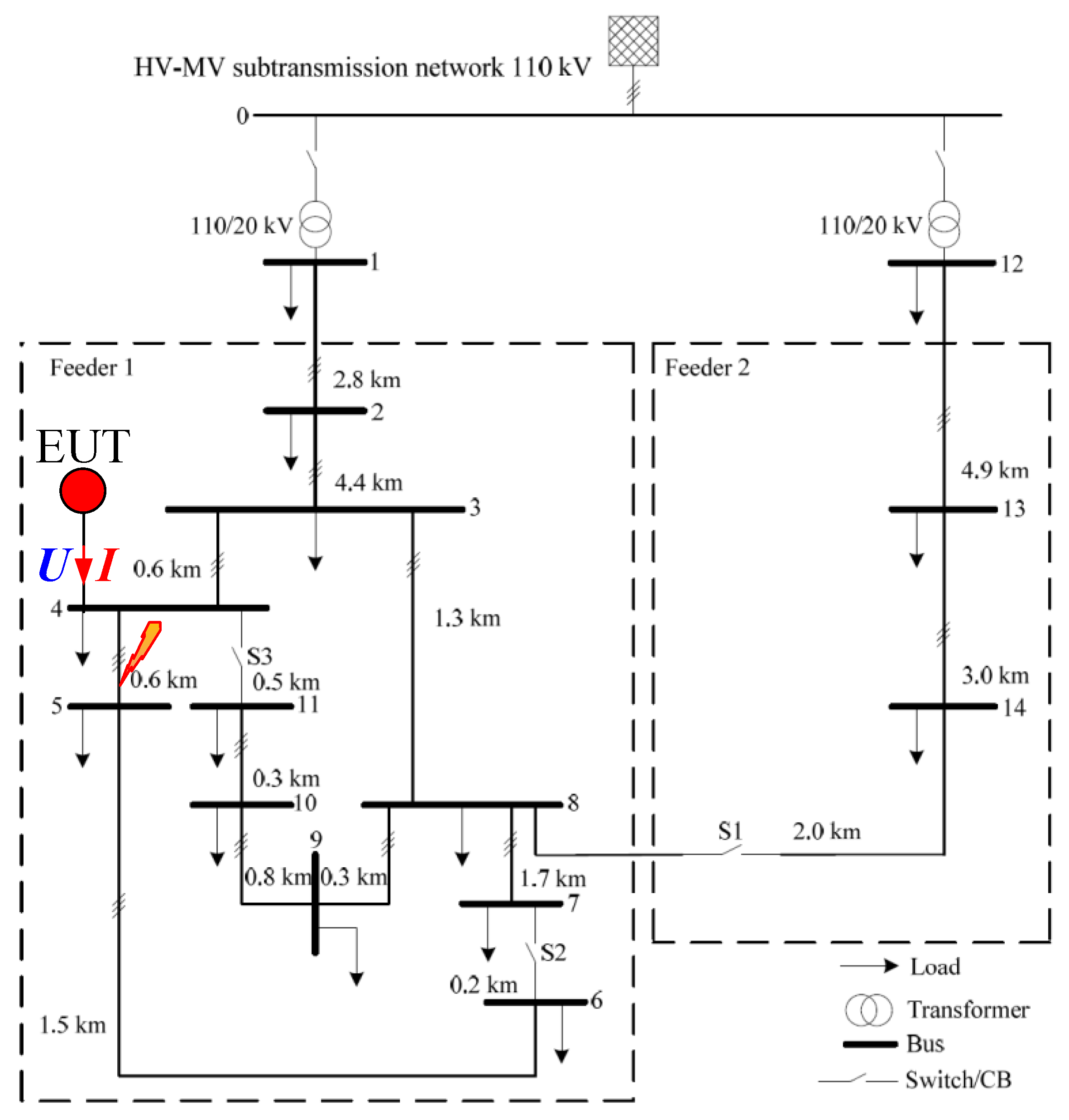

4.1. Test Setup

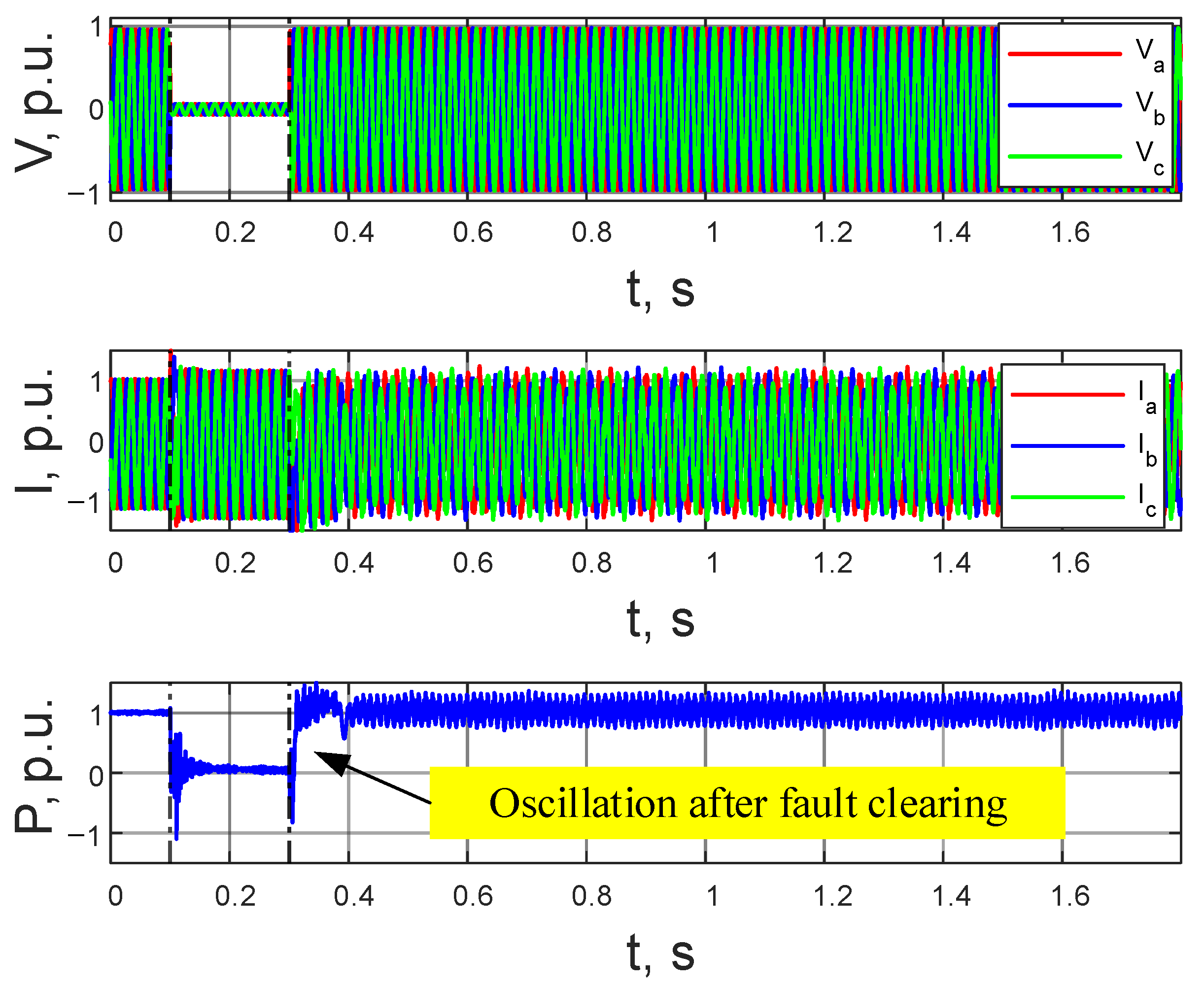

4.2. Test Results and Analysis

4.3. Summary and Discussion of Test Results

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Quintana-Rojo, C.; Callejas-Albiñana, F.-E.; Tarancón, M.; Martínez-Rodríguez, I. Econometric Studies on the Development of Renewable Energy Sources to Support the European Union 2020–2030 Climate and Energy Framework: A Critical Appraisal. Sustainability 2020, 12, 4828. [Google Scholar] [CrossRef]

- Rosso, R.; Wang, X.; Liserre, M.; Lu, X.; Engelken, S. Grid-Forming Converters: Control Approaches, Grid-Synchronization, and Future Trends—A Review. IEEE Open J. Ind. Appl. 2021, 2, 93–109. [Google Scholar] [CrossRef]

- Musengimana, A.; Li, H.; Zheng, X.; Yu, Y. Small-Signal Model and Stability Control for Grid-Connected PV Inverter to a Weak Grid. Energies 2021, 14, 3907. [Google Scholar] [CrossRef]

- Zhang, Z.; Gercek, C.; Renner, H.; Reinders, A.; Fickert, L. Resonance Instability of Photovoltaic E-Bike Charging Stations: Control Parameters Analysis, Modeling and Experiment. Appl. Sci. 2019, 9, 252. [Google Scholar] [CrossRef] [Green Version]

- Ratnam, K.; Palanisamy, K.; Yang, G. Future low-inertia power systems: Requirements, issues, and solutions—A review. Renew. Sustain. Energy Rev. 2020, 124, 109773. [Google Scholar] [CrossRef]

- Shair, J.; Xie, X.; Wang, L.; Liu, W.; He, J.; Liu, H. Overview of emerging subsynchronous oscillations in practical wind power systems. Renew. Sustain. Energy Rev. 2018, 99, 159–168. [Google Scholar] [CrossRef]

- Bialek, J. What does the GB power outage on 9 August 2019 tell us about the current state of decarbonised power systems? Energy Policy 2020, 146, 111821. [Google Scholar] [CrossRef]

- Zhang, L.; Harnefors, L.; Nee, H.-P. Interconnection of Two Very Weak AC Systems by VSC-HVDC Links Using Power-Synchronization Control. IEEE Trans. Power Syst. 2010, 26, 344–355. [Google Scholar] [CrossRef]

- Orihara, D.; Taoka, H.; Kikusato, H.; Hashimoto, J.; Otani, K.; Takamatsu, T.; Oozeki, T.; Matsuura, T.; Miyazaki, S.; Hamada, H.; et al. Internal Induced Voltage Modification for Current Limitation in Virtual Synchronous Machine. Energies 2022, 15, 901. [Google Scholar] [CrossRef]

- Hernandez-Alvidrez, J.; Darbali-Zamora, R.; Flicker, J.D.; Shirazi, M.; VanderMeer, J.; Thomson, W. Using Energy Storage-Based Grid Forming Inverters for Operational Reserve in Hybrid Diesel Microgrids. Energies 2022, 15, 2456. [Google Scholar] [CrossRef]

- Al-Shetwi, A.Q.; Issa, W.K.; Aqeil, R.F.; Ustun, T.S.; Al-Masri, H.M.K.; Alzaareer, K.; Abdolrasol, M.G.M.; Abdullah, M.A. Active Power Control to Mitigate Frequency Deviations in Large-Scale Grid-Connected PV System Using Grid-Forming Single-Stage Inverters. Energies 2022, 15, 2035. [Google Scholar] [CrossRef]

- Zhang, Z.; Schürhuber, R.; Fickert, L.; Friedl, K.; Chen, G.; Zhang, Y.; Wang, F. Differences in Transient Stability Between Grid Forming and Grid Following in Synchronization Mechanism. In Proceedings of the CIRED 2021—The 26th International Conference and Exhibition on Electricity Distribution, Online, 20–23 September 2021; pp. 1096–1100. [Google Scholar] [CrossRef]

- Ray, I. Review of Impedance-Based Analysis Methods Applied to Grid-Forming Inverters in Inverter-Dominated Grids. Energies 2021, 14, 2686. [Google Scholar] [CrossRef]

- Kkuni, K.V.; Yang, G. Effects of current limit for grid forming converters on transient stability: Analysis and solution. arXiv 2021, arXiv:2106.13555. [Google Scholar] [CrossRef]

- Zhang, Z.; Schürhuber, R.; Fickert, L.; Chen, G.; Zhang, Y. Low Voltage Ride Through Characteristics of Grid Forming inverters. In Proceedings of the 21st International Scientific Conference on Electric Power Engineering (EPE), Prague, Czech Republic, 19–21 October 2020; pp. 1–6. [Google Scholar] [CrossRef]

- Deng, H.; Fang, J.; Qi, Y.; Debusschere, V.; Tang, Y. A Low Voltage Ride Through Strategy with Load and Grid Support for Grid-Forming Converters. In Proceedings of the 2020 IEEE 9th International Power Electronics and Motion Control Conference (IPEMC2020-ECCE Asia), Nanjing, China, 29 November–2 December 2020; pp. 331–335. [Google Scholar] [CrossRef]

- Chen, M.; Zhou, D.; Blaabjerg, F. Enhanced Transient Angle Stability Control of Grid-Forming Converter Based on Virtual Synchronous Generator. IEEE Trans. Ind. Electron. 2021, 69, 9133–9144. [Google Scholar] [CrossRef]

- Qoria, T.; Gruson, F.; Colas, F.; Kestelyn, X.; Guillaud, X. Current limiting algorithms and transient stability analysis of grid-forming VSCs. Electr. Power Syst. Res. 2020, 189, 106726. [Google Scholar] [CrossRef]

- Rokrok, E.; Qoria, T.; Bruyere, A.; Francois, B.; Guillaud, X. Transient Stability Assessment and Enhancement of Grid-Forming Converters Embedding Current Reference Saturation as Current Limiting Strategy. IEEE Trans. Power Syst. 2021, 37, 1519–1531. [Google Scholar] [CrossRef]

- Pattabiraman, D.; Lasseter, R.H.; Jahns, T.M. Transient Stability Modeling of Droop-Controlled Grid-Forming Inverters with Fault Current Limiting. In Proceeding of the 2020 IEEE Power & Energy Society General Meeting (PESGM), Montreal, QC, Canada, 2–6 August 2020; pp. 1–5. [Google Scholar]

- Qoria, T.; Gruson, F.; Colas, F.; Denis, G.; Prevost, T.; Guillaud, X. Critical Clearing Time Determination and Enhancement of Grid-Forming Converters Embedding Virtual Impedance as Current Limitation Algorithm. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 8, 1050–1061. [Google Scholar] [CrossRef] [Green Version]

- Chen, J.; Prystupczuk, F.; O’Donnell, T. Use of voltage limits for current limitation in grid-forming converters. CSEE J. Power Energy Syst. 2020, 6, 259–269. [Google Scholar] [CrossRef]

- Taul, M.G.; Wang, X.; Davari, P.; Blaabjerg, F. Current Reference Generation Based on Next-Generation Grid Code Requirements of Grid-Tied Converters During Asymmetrical Faults. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 8, 3784–3797. [Google Scholar] [CrossRef] [Green Version]

- Rodriguez, P.; Teodorescu, R.; Candela, I.; Timbus, A.V.; Liserre, M.; Blaabjerg, F. New Positive-sequence Voltage Detector for Grid Synchronization of Power Converters under Faulty Grid Conditions. In Proceedings of the 37th IEEE Power Electronics Specialists Conference, Jeju, Korea, 18–22 June 2006. [Google Scholar] [CrossRef]

- Pinto, J.; Carvalho, A.; Rocha, A.; Araújo, A. Comparison of DSOGI-Based PLL for Phase Estimation in Three-Phase Weak Grids. Electricity 2021, 2, 244–270. [Google Scholar] [CrossRef]

- Taul, M.G.; Wang, X.; Davari, P.; Blaabjerg, F. Current Limiting Control with Enhanced Dynamics of Grid-Forming Converters During Fault Conditions. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 8, 1062–1073. [Google Scholar] [CrossRef] [Green Version]

- Alassi, A.; Ahmed, K.; Egea-Alvarez, A.; Foote, C. Modified Grid-forming Converter Control for Black-Start and Grid-Synchronization Applications. In Proceedings of the 56th International Universities Power Engineering Conference (UPEC), Middlesbrough, UK, 7–10 September 2021; pp. 1–5. [Google Scholar] [CrossRef]

- Alassi, A.; Ahmed, K.; Egea-Alvarez, A.; Ellabban, O. Performance Evaluation of Four Grid-Forming Control Techniques with Soft Black-Start Capabilities. In Proceedings of the 9th International Conference on Renewable Energy Research and Application (ICRERA), Glasgow, UK, 27–30 September 2020; pp. 221–226. [Google Scholar] [CrossRef]

- Rao, S.; Dutta, S.; Lwin, M.; Howard, D.; Konopinski, R.; Achilles, S.; MacDowell, J. Grid-Forming Inverters-Real-Life Implementation Experience and Lessons Learned. In Proceedings of the 9th Renewable Power Generation Conference (RPG Dublin Online 2021), Dublin, Ireland, 1–2 March 2021; pp. 7–12. [Google Scholar] [CrossRef]

- Duckwitz, D.; Knobloch, A.; Welck, F.; Becker, T.; Gloeckler, C.; Buelo, T. Experimental Short-Circuit Testing of Grid-Forming Inverters in Microgrid and Interconnected Mode. In Proceedings of the NEIS 2018 Conference on Sustainable Energy Supply and Energy Storage Systems, Hamburg, Germany, 20–21 September 2018; pp. 1–6. [Google Scholar]

- Hu, J.; Chi, Y.; Tian, X.; Zhou, Y.; He, W. A coordinated and steadily fault ride through strategy under short-circuit fault of the wind power grid connected system based on the grid-forming control. Energy Rep. 2022, 8, 333–341. [Google Scholar] [CrossRef]

- Choopani, M.; Hosseinian, S.H.; Vahidi, B. New Transient Stability and LVRT Improvement of Multi-VSG Grids Using the Frequency of the Center of Inertia. IEEE Trans. Power Syst. 2020, 35, 527–538. [Google Scholar] [CrossRef]

- Kabsha, M.M.; Rather, Z.H. Advanced LVRT Control Scheme for Offshore Wind Power Plant. IEEE Trans. Power Deliv. 2021, 36, 3893–3902. [Google Scholar] [CrossRef]

- Zhao, L.; Jin, Z.; Wang, X. Transient Performance Evaluation of Grid-forming Control for Railway Traction Converters Considering Inter-Phase Operation. In Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE), Online, 10–14 October 2021; pp. 2958–2963. [Google Scholar] [CrossRef]

- Raza, M.; Peñalba, M.A.; Gomis-Bellmunt, O. Short circuit analysis of an offshore AC network having multiple grid forming VSC-HVDC links. Int. J. Electr. Power Energy Syst. 2018, 102, 364–380. [Google Scholar] [CrossRef]

- Zhang, Z.; Schuerhuber, R.; Fickert, L.; Friedl, K. Study of stability after low voltage ride-through caused by phase-locked loop of grid-side converter. Int. J. Electr. Power Energy Syst. 2021, 129, 106765. [Google Scholar] [CrossRef]

- Zhang, Z.; Schuerhuber, R.; Fickert, L.; Friedl, K.; Chen, G.; Zhang, Y. Domain of Attraction’s Estimation for Grid Connected Converters with Phase-Locked Loop. IEEE Trans. Power Syst. 2021, 37, 1351–1362. [Google Scholar] [CrossRef]

- Zhao, X.; Flynn, D. Freezing Grid-Forming Converter Virtual Angular Speed to Enhance Transient Stability Under Current Reference Limiting. In Proceedings of the 2020 IEEE 21st Workshop on Control and Modeling for Power Electronics (COMPEL), Aalborg, Denmark, 9–12 November 2020; pp. 1–7. [Google Scholar]

- Zhao, X.; Flynn, D. Dynamic studies for 100% converter-based Irish power system. In Proceedings of the 9th Renewable Power Generation Conference (RPG Dublin Online 2021), Dublin, Ireland, 14–15 October 2021; pp. 389–394. [Google Scholar] [CrossRef]

- Barsali, S. Benchmark Systems for Network Integration of Renewable and Distributed Energy Resources; Stampa: Turin, Italy, 2014. [Google Scholar]

- Zhang, Z.; Fickert, L.; Zhang, Y. Power hardware-in-the-loop test for cyber physical renewable energy infeed: Retroactive effects and an optimized power Hardware-in-the-Loop interface algorithm. In Proceedings of the 17th International Scientific Conference on Electric Power Engineering (EPE), Prague, Czech Republic, 16–18 May 2016; pp. 1–6. [Google Scholar] [CrossRef]

| Phase | Description |

|---|---|

| Phase of the terminal voltage | |

| Initial phase of the P-f loop at post-fault | |

| Phase threshold to avoid current saturation | |

| Output reference phase of the P-f loop |

| Method | Advantages | Disadvantages |

|---|---|---|

| Zero-crossing start | Simple to implement, no control parameter tuning to consider | Slow recovery of active power after restart. |

| Start with variable droop factor | Fast resynchronization | Careful tuning of the parameters is required. |

| Start with auxiliary synchronization | Fast resynchronization | Additional control loops need to be added. |

| Name | Value |

|---|---|

| Rated power of the converter | 1 MVA |

| Rated voltage of the converter | 0.69 kV |

| Filter inductance | 0.1 p.u. |

| Equivalent resistance on the filter | 0.005 p.u. |

| Filter capacitance | 0.33 p.u. |

| Ratio of the unit transformer | 0.69/20 kV |

| Rated power of the unit transformer | 1.25 MVA |

| Vector group of the unit transformer | Dy11 |

| of the unit transformer | 6% |

| Name | Value |

|---|---|

| Droop factor of the P-f loop | 0.2 p.u./Hz |

| Cut-off frequency of low-pass filter in P-f loop | 20 Hz |

| Droop factor of the Q-E loop | 1 |

| Cut-off frequency of low-pass filter in Q-E loop | 1 Hz |

| Control parameters of the backup PLL | |

| Control parameters of the voltage loop | |

| Control parameters of the current loop | |

| Current amplitude threshold | 1.2 p.u. |

| Control parameters of auxiliary synchronization | and |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, Z.; Lehmal, C.; Hackl, P.; Schuerhuber, R. Transient Stability Analysis and Post-Fault Restart Strategy for Current-Limited Grid-Forming Converter. Energies 2022, 15, 3552. https://doi.org/10.3390/en15103552

Zhang Z, Lehmal C, Hackl P, Schuerhuber R. Transient Stability Analysis and Post-Fault Restart Strategy for Current-Limited Grid-Forming Converter. Energies. 2022; 15(10):3552. https://doi.org/10.3390/en15103552

Chicago/Turabian StyleZhang, Ziqian, Carina Lehmal, Philipp Hackl, and Robert Schuerhuber. 2022. "Transient Stability Analysis and Post-Fault Restart Strategy for Current-Limited Grid-Forming Converter" Energies 15, no. 10: 3552. https://doi.org/10.3390/en15103552

APA StyleZhang, Z., Lehmal, C., Hackl, P., & Schuerhuber, R. (2022). Transient Stability Analysis and Post-Fault Restart Strategy for Current-Limited Grid-Forming Converter. Energies, 15(10), 3552. https://doi.org/10.3390/en15103552