Accurate Circuit-Level Modelling of IGBTs with Thermal Phenomena Taken into Account

Abstract

1. Introduction

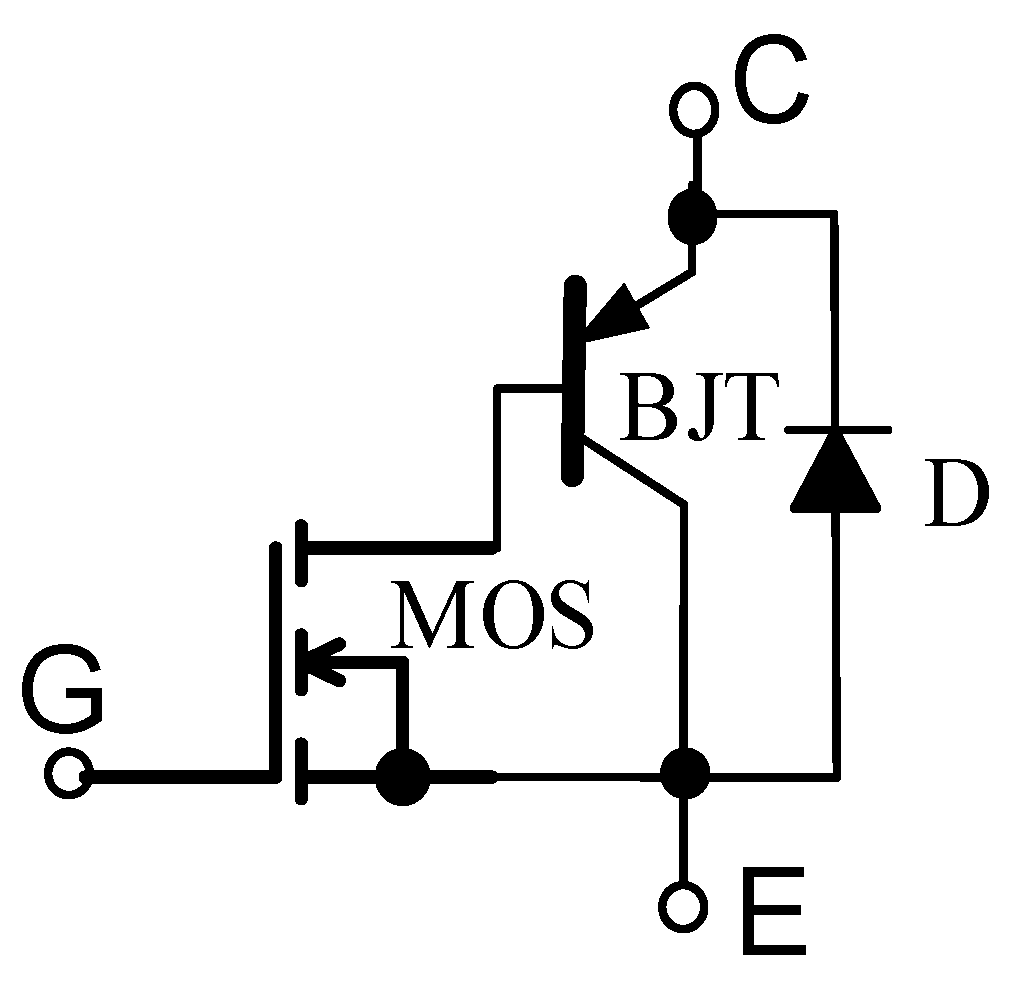

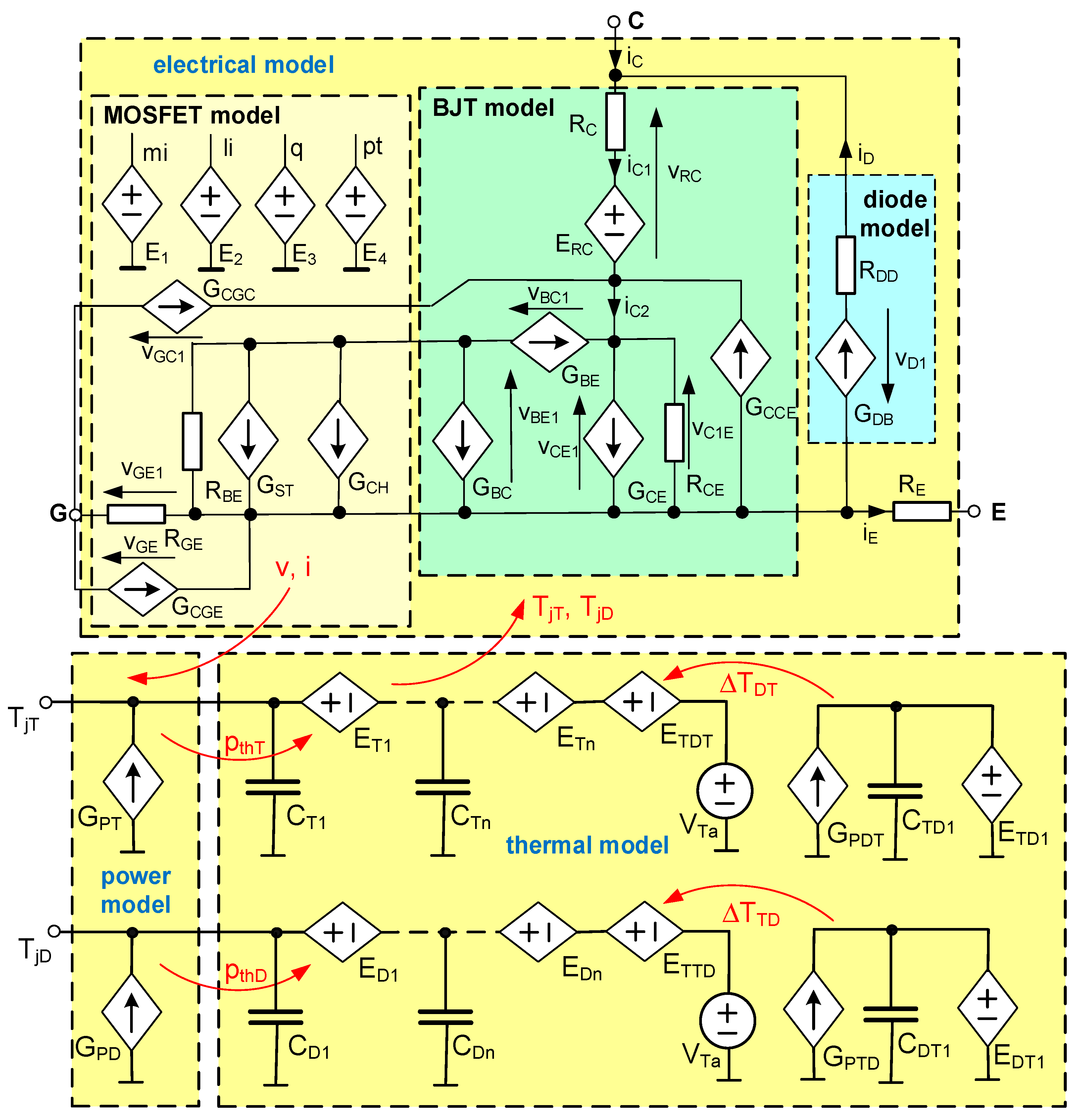

2. Model Form

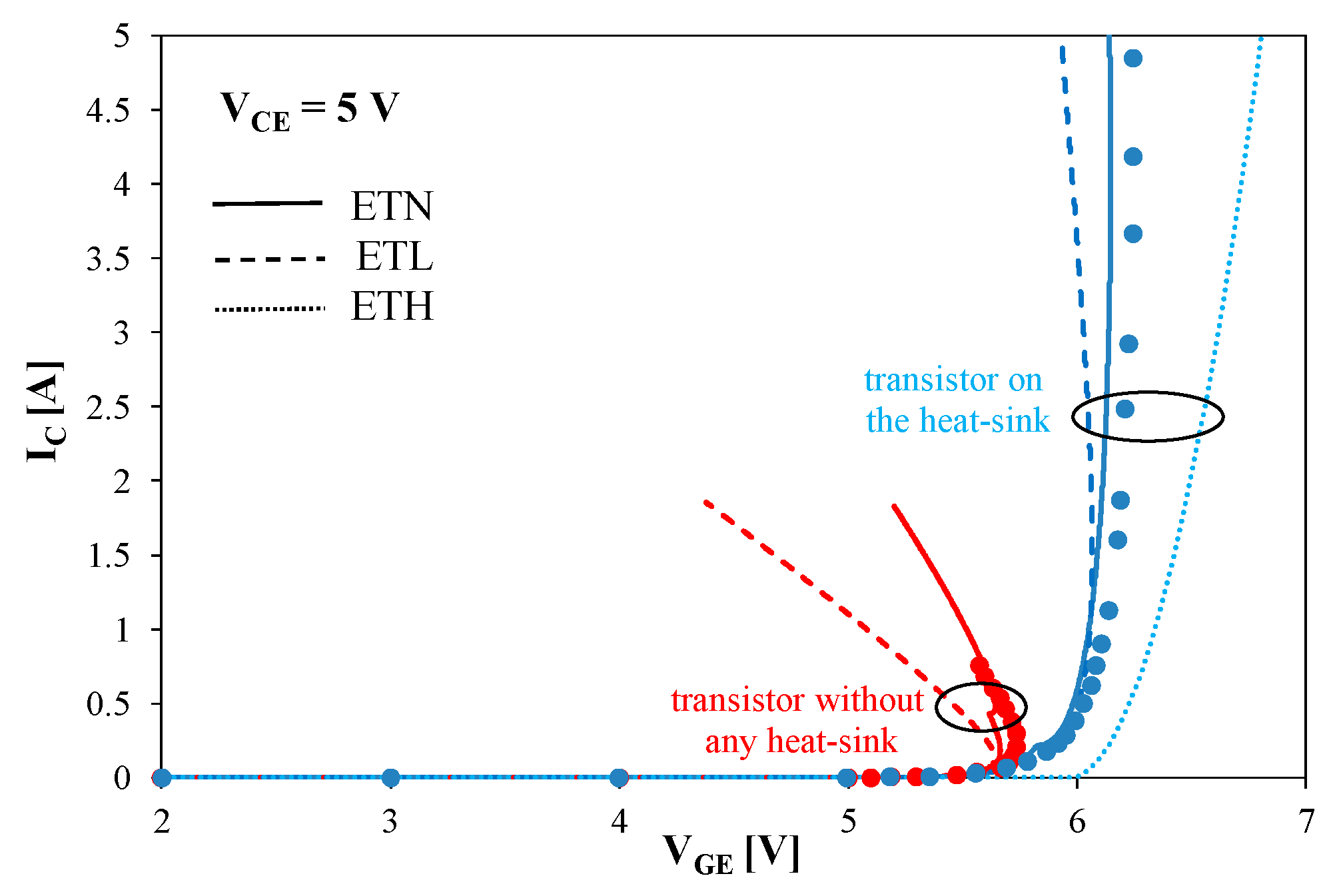

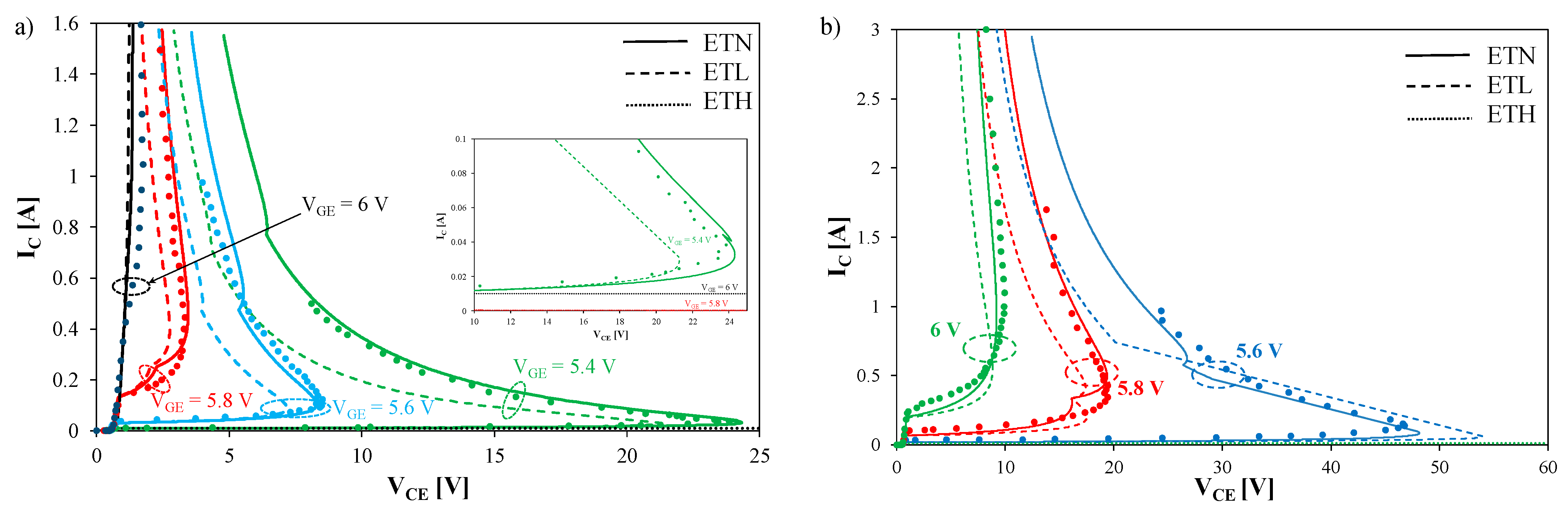

2.1. Electrical Model

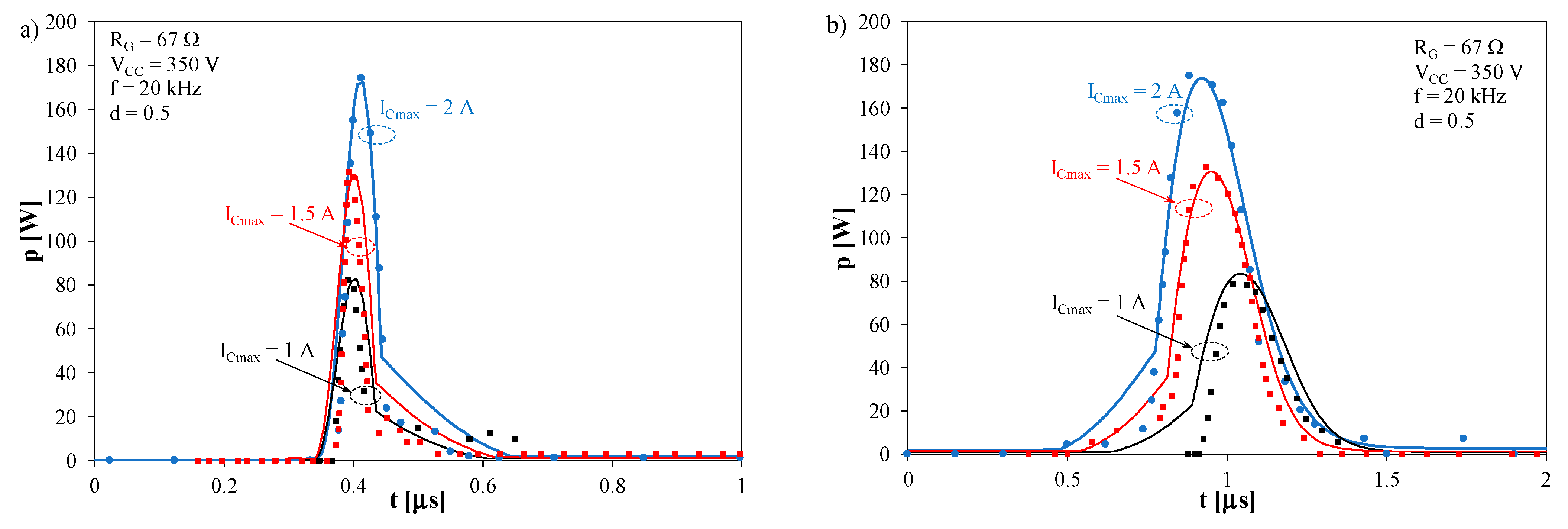

2.2. Power Model

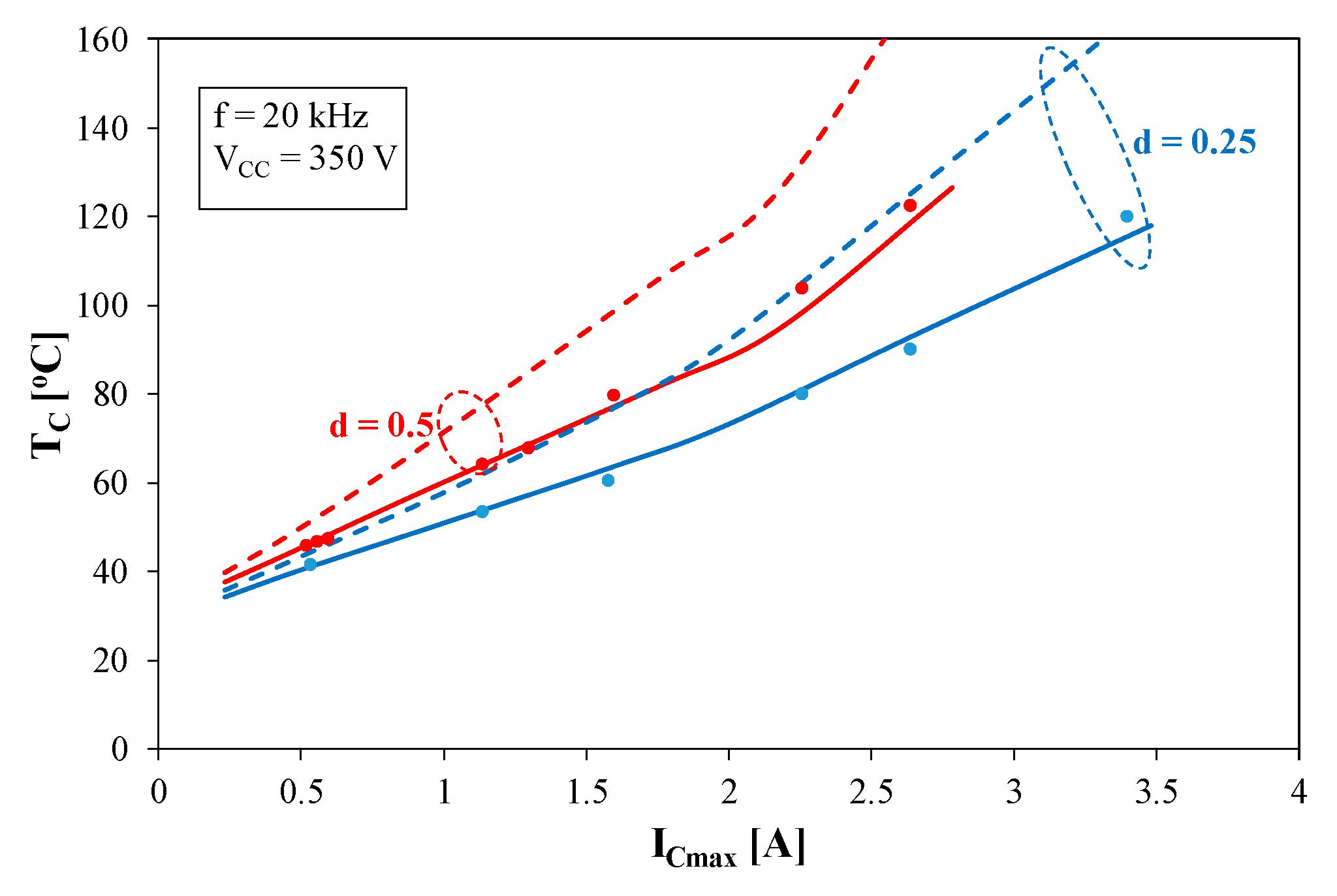

2.3. Thermal Model

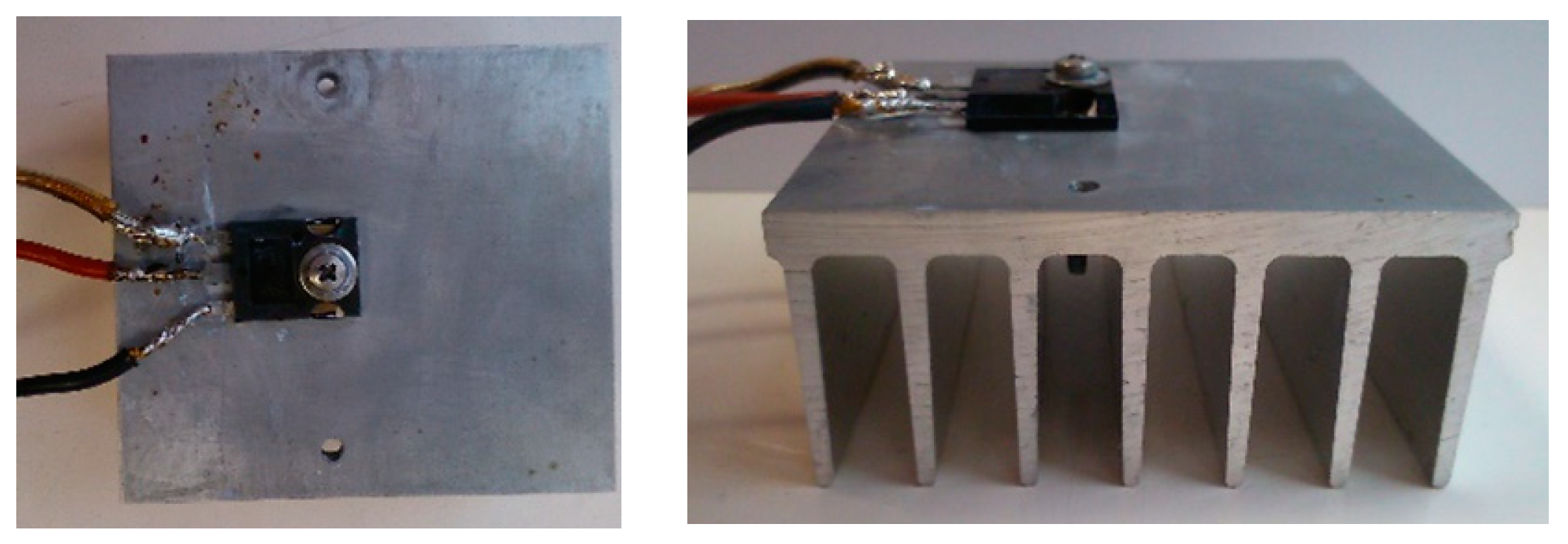

3. Estimation of the Model Parameters

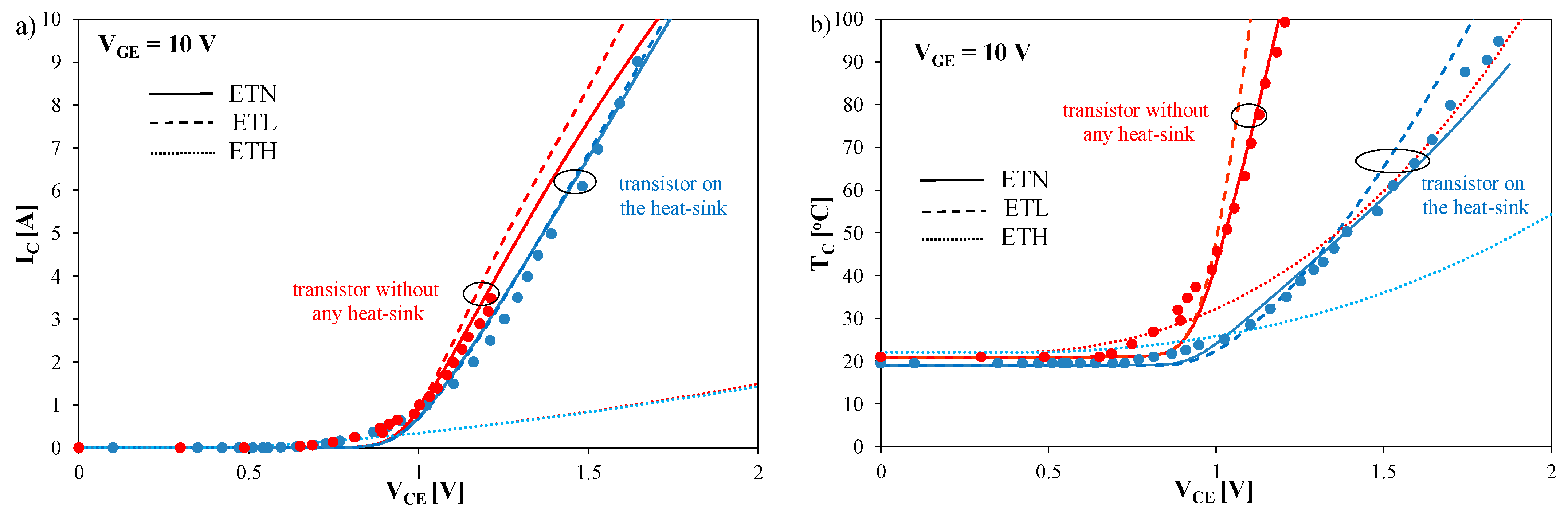

4. Verification of the Formulated Model

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

Nomenclature

| isothermal characteristics | characteristics determined at a constant value of the device internal temperature |

| non-isothermal characteristics | characteristics determined with thermal phenomena taken into account |

| electrothermal model | a model describing current-voltage-temperature dependences with thermal phenomena taken into account |

| iC | collector current of the IGBT |

| k | the Boltzmann constant |

| LIMIT(x, min, max) | a standard-function of SPICE, whose value is equal to min, if x < min, max, if x > max, and in other cases it is equal to x |

| pthT | thermal power dissipated in the transistor |

| pthD | thermal power dissipated in the diode |

| q | electron charge |

| RthT | thermal resistance of the transistor |

| RthD | thermal resistance of the diode |

| RthTD | transfer thermal resistance between the transistor and the diode |

| RthT1, RthT0, a, b, TZ | parameters occurring in the dependence RthT(Ta, TjT) |

| Ta | ambient temperature |

| TjD | internal temperature of the diode |

| TjT | internal temperature of the IGBT |

| T0 | reference temperature |

| vBE1, vGE1, vBC1, vGE, vGC1, vC1E | voltages between the internal terminals of the BJT and the MOSFET contained in the structure of the IGBT marked in Figure 2 |

| vCE | collector-emitter voltage of the IGBT |

| vGE | gate-emitter voltage of the IGBT |

| Vgo | voltage corresponding to a band-gap of silicon |

| ε0 | dielectric permeability of free air |

| εox | relative dielectric permeability of silicon |

| Parameters of a MOS transistor: | |

| B | parameter of the main component of drain current |

| CGD0 | capacitance between the gate and the drain per unit of widths of the channel |

| CGE0 | capacitance between the gate and the emitter per unit of widths of the channel |

| Cox | capacitance dependent on thickness tOX of the layer of SiO2 under the gate |

| C1, C2, y, e, n, VGCmin | parameters describing CGD0 capacitance |

| iD, iC1, iC2, iE | currents marked in Figure 2 |

| IPO | parameter of sub-threshold current |

| L | length of the channel |

| np | the emission coefficient of sub-threshold current |

| vmi | voltages on terminals of controlled voltage sources E1, to which the main part of drain current is proportional; the value of this voltage depends on voltages vGE1, vBG1 and vVT |

| vPH | the Fermi level linearly dependent on temperature TjT |

| vVT | threshold voltage linearly dependent on temperature TjT |

| w | width of the channel |

| VGEmax, VGEmin, CG1, CG2, x, u and k1 | parameters of the model describing CGE0 capacitance |

| Parameters of a BJT: | |

| I0 | parameter, to which the collector current is proportional |

| Mj2 | parameter describing the doping profile of the base-emitter junction |

| n1 | the emission coefficient of the base-emitter junction |

| UAN | Early voltage |

| VjC | built-in potential of the base-emitter junction |

| vRC, vCE1 | voltages between the internal terminals of the BJT marked in Figure 2 |

| βF | the current amplification coefficient within the forward active mode; this coefficient depends on temperature TjT and the collector current |

| Parameters of a diode: | |

| CCE0 | capacitance at zero voltage on the diode |

| I0D | parameter, to which the diode current is proportional |

| Mj | parameter describing the doping profile of the junction |

| nD | the emission coefficient of the diode |

| r | the temperature coefficient of parameter Mj. |

| Vj | built-in potential |

References

- Baliga, B.; Adler, M.; Love, R.; Gray, P.; Zommer, N. The insulated gate transistor: A new three-terminal MOS-controlled bipolar power device. IEEE Trans. Electron. Devices 1984, 31, 821–828. [Google Scholar] [CrossRef]

- Iwamuro, N.; Laska, T. IGBT History, state-of-the-art, and future prospects. IEEE Trans. Electron. Devices 2017, 64, 741–752. [Google Scholar] [CrossRef]

- Choi, U.-M.; Vernica, I.; Blaabjerg, F. Effect of asymmetric layout of IGBT Modules on reliability of motor drive inverters. IEEE Trans. Power Electron. 2019, 34, 1765–1772. [Google Scholar] [CrossRef]

- Yaghoubi, M.; Moghani, J.S.; Noroozi, N.; Zolghadri, M.R. IGBT open-circuit fault diagnosis in a quasi-z-source inverter. IEEE Trans. Ind. Electron. 2019, 66, 2847–2856. [Google Scholar] [CrossRef]

- Bae, C.; Lee, D.; Nguyen, T.H. Detection and identification of multiple IGBT open-circuit faults in PWM inverters for AC machine drives. IET Power Electron. 2019, 12, 923–931. [Google Scholar] [CrossRef]

- Li, B.; Zhao, X.; Cheng, D.; Zhang, S.; Xu, D.G. Novel hybrid DC/DC converter topology for HVDC interconnections. IEEE Trans. Power Electron. 2019, 34, 5131–5146. [Google Scholar] [CrossRef]

- Wang, J.; Li, Z.; Jiang, X.; Zeng, C.; Shen, Z.J. Gate control optimization of Si/SiC hybrid switch for junction temperature balance and power loss reduction. IEEE Trans. Power Electron. 2019, 34, 1744–1754. [Google Scholar] [CrossRef]

- Dudrik, J.; Pastor, M.; Lacko, M.; Zatkovic, R. Zero-voltage and zero-current switching PWM DC–DC converter using controlled secondary rectifier with one active switch and nondissipative turn-off snubber. IEEE Trans. Power Electron. 2017, 33, 6012–6023. [Google Scholar] [CrossRef]

- Górecki, K.; Detka, K. Application of average electrothermal models in the spice-aided analysis of boost converters. IEEE Trans. Ind. Electron. 2019, 66, 2746–2755. [Google Scholar] [CrossRef]

- Hefner, A.R.; Diebolt, D.M. An experimentally verified igbt model implemented in the saber circuit simulator. In Proceedings of the PESC ‘91 Record. 22nd Annual IEEE Power Electronics Specialists Conference, Cambridge, MA, USA, 24–27 June 1991; IEEE: Piscataway Township, NJ, USA, 2002; Volume 9, pp. 532–542. [Google Scholar] [CrossRef]

- Riccio, M.; De Falco, G.; Mirone, P.; Maresca, L.; Tedesco, M.; Breglio, G.; Irace, A. Accurate SPICE modeling of reverse-conducting IGBTs including self-heating effects. IEEE Trans. Power Electron. 2017, 32, 3088–3098. [Google Scholar] [CrossRef]

- Azar, R.; Udrea, F.; Ng, W.T.; Dawson, F.; Findlay, W.; Waind, P.; Amaratunga, G. Advanced electrothermal SPICE modelling of large power IGBTs. IEE Proc. Circuits Devices Syst. 2004, 151, 249–253. [Google Scholar] [CrossRef]

- Bagnoli, P.E.; Casarosa, C.; Ciampi, M.; Dallago, E. Thermal resistance analysis by induced transient (TRAIT) method for power electronic devices thermal characterization—part I: Fundamentals and theory. IEEE Trans. Power Electron. 1998, 13, 1208–1219. [Google Scholar] [CrossRef]

- Deng, E.; Zhao, Z.; Zhang, P.; Li, J.; Huang, Y. Study on the methods to measure the junction-to-case thermal resistance of IGBT modules and press pack IGBTs. Microelectron. Reliab. 2017, 79, 248–256. [Google Scholar] [CrossRef]

- Bryant, A.T.; Mawby, P.A.; Palmer, P.R.; Santi, E.; Hudgins, J.L. Exploration of Power Device Reliability Using Compact Device Models and Fast Electrothermal Simulation. IEEE Trans. Ind. Appl. 2008, 44, 894–903. [Google Scholar] [CrossRef]

- Zarębski, J.; Górecki, K. SPICE-aided modelling of dc characteristics of power bipolar transistors with self-heating taken into account. Int. J. Numer. Model. Electron. Netw. Devices Fields 2009, 22, 422–433. [Google Scholar] [CrossRef]

- Górecki, K.; Górecki, P. Modelling the influence of self-heating on characteristics of IGBTs. In Proceedings of the 21st International Conference Mixed Design of Integrated Circuits and Systems (MIXDES), Lublin, Poland, 19–21 June 2014; IEEE: Piscataway Township, NJ, USA, 2014; pp. 298–302. [Google Scholar]

- Hefner, A.R. Dynamic electro-thermal model for the IGBT. IEEE Trans. Ind. Appl. 1994, 30, 394–405. [Google Scholar] [CrossRef]

- Górecki, P.; Górecki, K.; Zarębski, J. Modelling the temperature influence on dc characteristics of the IGBT. Microelc. Reliab. 2017, 79, 96–103. [Google Scholar] [CrossRef]

- Rashid, M. SPICE for Power Electronics and Electronic Power, 3rd ed.; Taylor and Francis Group: Oxfordshire, UK, 2016. [Google Scholar]

- Eguchi, K.; Asadi, F.; Kuwahara, K.; Ishibashi, T.; Oota, I. A small direct SC AC-AC converter with cascade topology. Int. J. Innov. Comput. Inf. Control 2018, 14, 1741–1753. [Google Scholar]

- Detka, K.; Górecki, K.; Zarębski, J. Modeling single inductor DC–DC converters with thermal phenomena in the inductor taken into account. IEEE Trans. Power Electron. 2017, 32, 7025–7033. [Google Scholar] [CrossRef]

- Górecki, P.; Wojciechowski, D. Accurate computation of IGBT junction temperature in PLECS. IEEE Trans. Electron. Devices 2020, 67, 2865–2871. [Google Scholar] [CrossRef]

- Basso, C. Switch-Mode Power Supply SPICE Cookbook; McGraw-Hill: New York, NY, USA, 2001. [Google Scholar]

- Maksimovic, D.; Stankovic, A.M.; Thottuvelil, V.J.; Verghese, G.C. Modeling and simulation of power electronic converters. Proc. IEEE 2001, 89, 898–912. [Google Scholar] [CrossRef]

- Napieralski, A.; Napieralska, M. Polowe Półprzewodnikowe Przyrządy Dużej Mocy; Wydawnictwo Naukowo-Techniczne: Warszawa, Poland, 1995. (In Polish) [Google Scholar]

- Rashid, M.H.; Rashid, H.M. Spice for Power Electronics and Electric Power; CRC Press: Boca Raton, FL, USA, 2006. [Google Scholar]

- Górecki, P.; Górecki, K. Modelling a switching process of IGBTs with influence of temperature taken into account. Energies 2019, 12, 1894. [Google Scholar] [CrossRef]

- Wilamowski, B.; Jager, R.C. Computerized Circuit Analysis Using SPICE Programs; McGraw-Hill: New York, NY, USA, 1997. [Google Scholar]

- Sheng, K.B.; Williams, W.; Finney, S.J. A review of IGBT models. IEEE Trans. Power Electron. 2000, 15, 1250–1266. [Google Scholar] [CrossRef]

- Gamage, S.; Pathirana, V.; Udrea, F. Electrothermal model for an SOI-based LIGBT. IEEE Trans. Electron. Devices 2006, 53, 1698–1704. [Google Scholar] [CrossRef]

- Ji, S.Q.; Zhao, Z.M.; Lu, T.; Yuan, L.Q.; Yu, H.L. HVIGBT physical model analysis during transient. IEEE Trans. Power Electron. 2013, 28, 2616–2624. [Google Scholar] [CrossRef]

- Xu, Y.; Ho, C.N.M.; Ghosh, A.; Muthumuni, D. A behavioral transient model of IGBT for switching cell power loss estimation in electromagnetic transient simulation. In Proceedings of the 2018 IEEE Applied Power Electronics Conference and Exposition (APEC), San Antonio, TX, USA, 4–8 March 2018; IEEE: Piscataway Township, NJ, USA, 2018; pp. 270–275. [Google Scholar]

- Xue, P.; Fu, G.; Zhang, N. Modeling inductive switching characteristics of high-speed buffer layer IGBT. IEEE Trans. Power Electron. 2016, 32, 3075–3087. [Google Scholar] [CrossRef]

- Musikka, T.; Smirnova, L.; Niemelä, M.; Silventoinen, P.; Pyrhönen, O. Modelling of high-power IGBT module short-circuit operation and current distribution by a behavioural model. IET Power Electron. 2016, 9, 2700–2705. [Google Scholar] [CrossRef]

- Yang, X.; Otsuki, M.; Palmer, P.R. Physics-based insulated-gate bipolar transistor model with input capacitance correction. IET Power Electron. 2015, 8, 417–427. [Google Scholar] [CrossRef]

- Duan, Y.; Xiao, F.; Luo, Y.; Iannuzzo, F. A lumped-charge approach based physical SPICE-model for high power soft-punch through IGBT. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 7, 62–70. [Google Scholar] [CrossRef]

- Wang, Z.; Qiao, W.; Tian, B.; Qu, L. An effective heat propagation path-based online adaptive thermal model for IGBT modules. In Proceedings of the 2014 IEEE Applied Power Electronics Conference and Exposition—APEC, Fort Worth, TX, USA, 16–20 March 2014; IEEE: Piscataway Township, NJ, USA, 2014; pp. 513–518. [Google Scholar]

- Marcault, E.J.; Massol, L.; Tounsi, P.; Dorkel, J.M. Distributed electrothermal modelling methodology for MOS gated power devices simulations. In Proceedings of the MIXDES 2013: 20th International Conference Mixed Design of Integrated Circuits and Systems, Gdynia, Poland, 20–22 June 2013; pp. 301–305. [Google Scholar]

- Sfakianakis, G.E.; Nawaz, M. Development of a modeling platform for 4.5 kV IGBT power modules. Proceedings of IECON 2014—40th Annual Conference of the IEEE Industrial Electronics Society, Dallas, TX, USA, 29 October–1 November 2014; IEEE: Piscataway Township, NJ, USA, 2014; pp. 1416–1422. [Google Scholar]

- Wu, R.; Wang, H.; Pedersen, K.B.; Ma, K.; Ghimire, P.; Iannuzzo, F.; Blaabjerg, F. A temperature-dependent thermal model of IGBT modules suitable for circuit-level simulations. IEEE Trans. Ind. Appl. 2016, 52, 3306–3314. [Google Scholar] [CrossRef]

- Hyeong-Seok, O.; El Nokali, M. A new IGBT behavioral model. Solid State Electron. 2001, 45, 2069–2075. [Google Scholar]

- Iannuzzo, F.; Busatto, G. Physical CAD model for high-voltage IGBTs based on lumped-charge approach. IEEE Trans. Power Electron. 2004, 19, 885–893. [Google Scholar] [CrossRef]

- Meng, J.; Ning, P.; Wen, X. A physical modeling method for NPT IGBTs verified by experiments. In Proceedings of the IEEE Conference and Expo Transportation Electrification, Asia-Pacific (ITEC Asia-Pacific), Beijing, China, 31 August–3 September 2014; IEEE: Piscataway, NJ, USA, 2014; pp. 1–6. [Google Scholar]

- Górecki, P.; Górecki, K. Measurements and computations of internal temperatures of the IGBT and the diode situated in the common case. Electronics 2021, 10, 210. [Google Scholar] [CrossRef]

- Spice Models and Saber Models. Website of International Rectifier. Available online: http://www.irf.com/product-info/models/saber/ (accessed on 21 April 2021).

- Górecki, K.; Górecki, P. Modelling dynamic characteristics of the IGBT with thermal phenomena taken into account. Microelectron. Int. 2017, 34, 160–164. [Google Scholar] [CrossRef]

- Codecasa, L.; d’Alessandro, V.; Magnani, A.; Irace, A. Circuit-based electrothermal simulation of power devices by an ultrafast nonlinear MOS approach. IEEE Trans. Power Electron. 2016, 31, 5906–5916. [Google Scholar] [CrossRef]

- Górecki, K.; Górecki, P. Nonlinear compact thermal model of the IGBT dedicated to SPICE. IEEE Trans. Power Electron. 2020, 35, 13420–13428. [Google Scholar] [CrossRef]

- Zarębski, J.; Górecki, K. The electrothermal large-signal model of power MOS transistors for SPICE. IEEE Trans. Power Electron. 2010, 25, 1265–1274. [Google Scholar] [CrossRef]

- Zarębski, J.; Górecki, K. Parameters estimation of the d.c. electrothermal model of the bipolar transistor. Int. J. Numer. Model. Electron. Netw. Devices Fields 2002, 15, 181–194. [Google Scholar] [CrossRef]

- IRG4PC40UD. Insulated Gate Bipolar Transistor with Ultrafast Soft Recovery Diode, Data Sheet. International Rectifier. Available online: http://www.irf.com/product-info/datasheets/data/irg4pc40ud.pdf (accessed on 21 April 2021).

- Hefner, A.R., Jr. INSTANT—IGBT Network Simulation and Transient Analysis Tool. Special Publication SP 400-88; National Institute of Standards and Technology: Gaithersburg, MD, USA, 1992. [Google Scholar]

- Hefner, A.R., Jr. An investigation of the drive circuit requirements for the power Insulated Gate Bipolar Transistor (IGBT). IEEE Trans. Power Electron. 1991, 6, 208–219. [Google Scholar] [CrossRef]

- Hefner, A.R., Jr. Modeling buffer layer IGBTs for circuit simulation. IEEE Trans. Power Electron. 1995, 10, 111–123. [Google Scholar] [CrossRef]

- Zarębski, J.; Górecki, K. The electrothermal macromodel of MA7800 monolithic positive voltage regulators family. Int. J. Numer. Model. Electron. Netw. Devices Fields 2006, 19, 331–343. [Google Scholar] [CrossRef]

- Górecki, K.; Zarębski, J. The method of a fast electrothermal transient analysis of single-inductance dc-dc converters. IEEE Trans. Power Electron. 2012, 27, 4005–4012. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Górecki, P.; Górecki, K.; Zarębski, J. Accurate Circuit-Level Modelling of IGBTs with Thermal Phenomena Taken into Account. Energies 2021, 14, 2372. https://doi.org/10.3390/en14092372

Górecki P, Górecki K, Zarębski J. Accurate Circuit-Level Modelling of IGBTs with Thermal Phenomena Taken into Account. Energies. 2021; 14(9):2372. https://doi.org/10.3390/en14092372

Chicago/Turabian StyleGórecki, Paweł, Krzysztof Górecki, and Janusz Zarębski. 2021. "Accurate Circuit-Level Modelling of IGBTs with Thermal Phenomena Taken into Account" Energies 14, no. 9: 2372. https://doi.org/10.3390/en14092372

APA StyleGórecki, P., Górecki, K., & Zarębski, J. (2021). Accurate Circuit-Level Modelling of IGBTs with Thermal Phenomena Taken into Account. Energies, 14(9), 2372. https://doi.org/10.3390/en14092372