Design of a Highly Efficient N-Stage Harmonic Terminated Voltage Multiplier for Wireless Power Transfer

Abstract

:1. Introduction

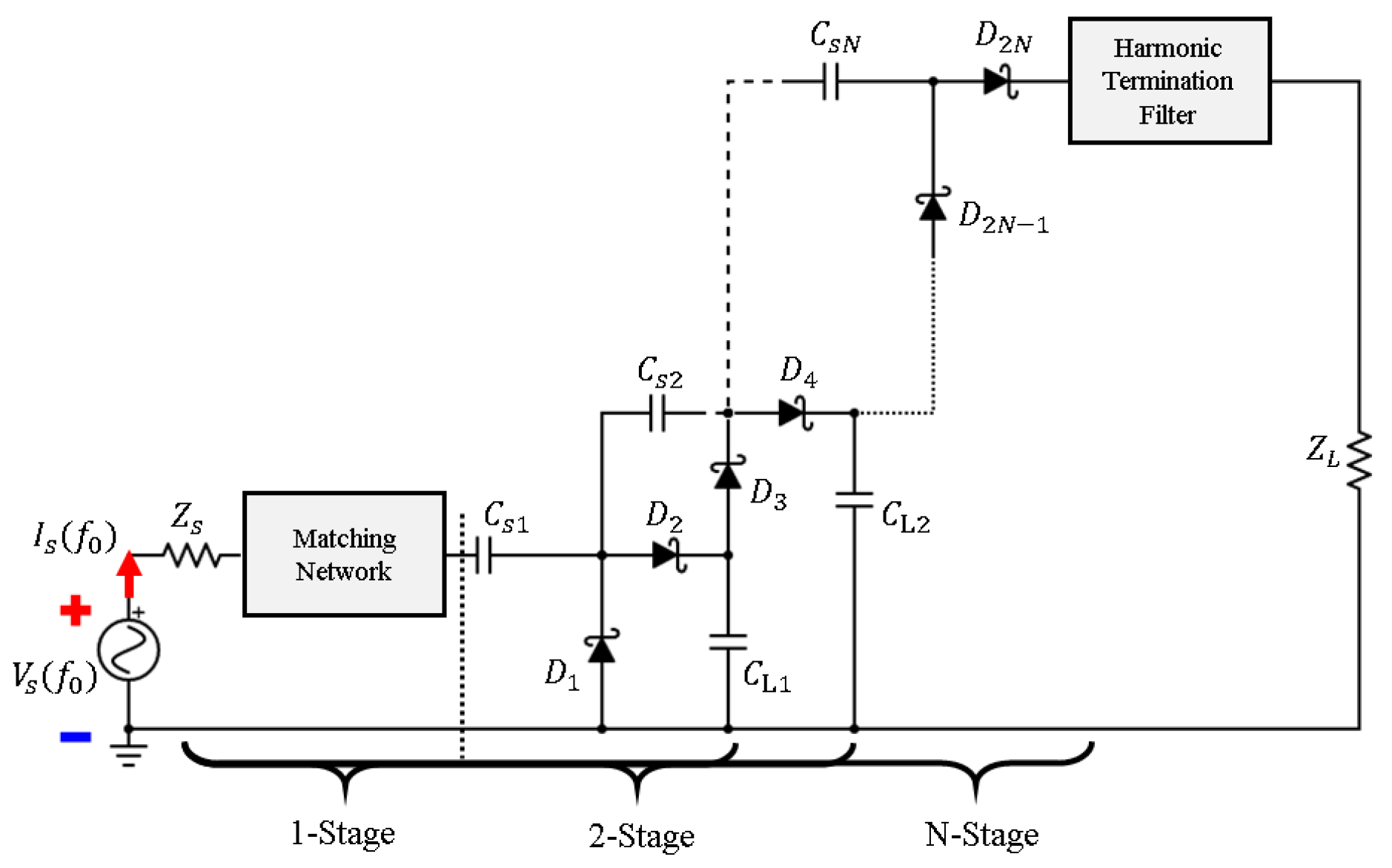

2. N-Stage Harmonic Terminated Voltage Multiplier Theory

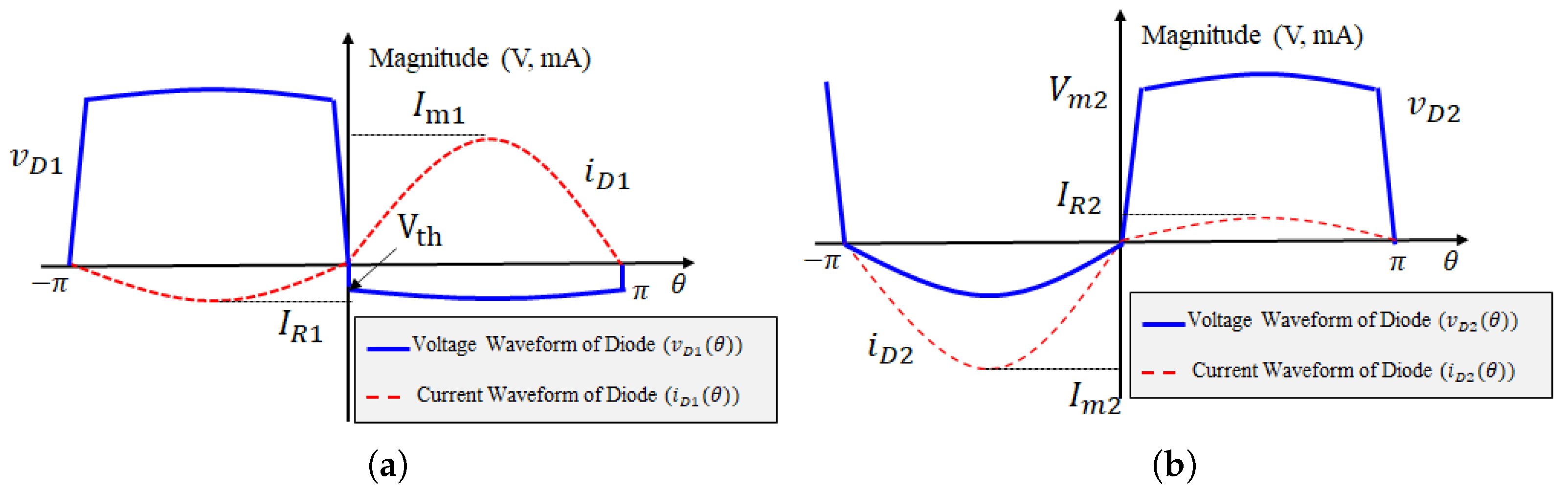

2.1. Mathematical Analysis of N-Stage HTVM under Breakdown Voltage Region

2.2. Mathematical Analysis of N-Stage HTVM over Breakdown Voltage Region

3. Design Method of Harmonic Termination Filter

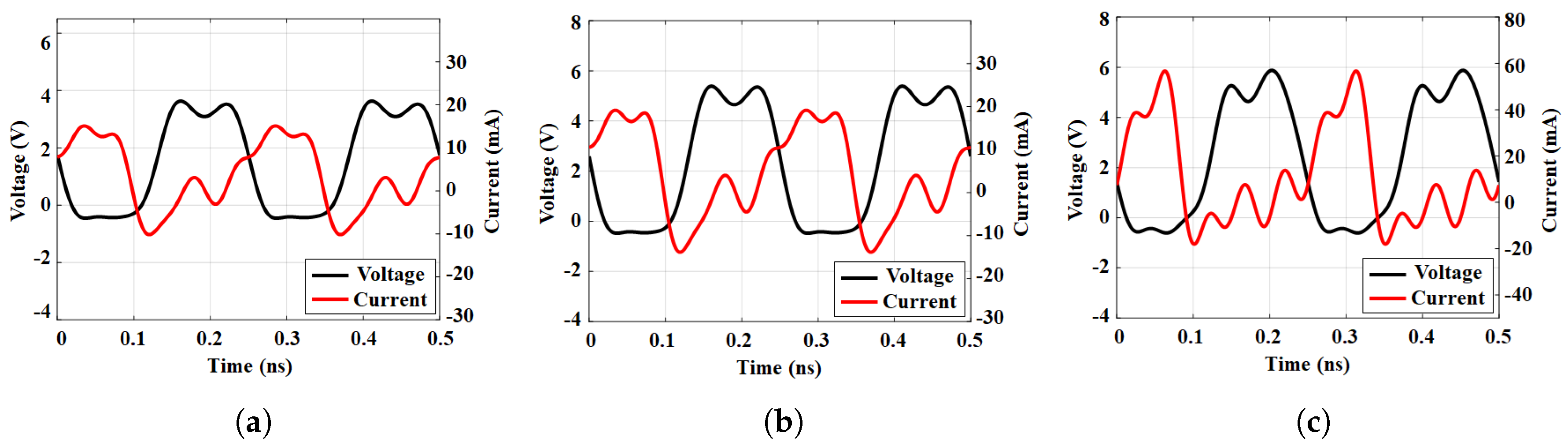

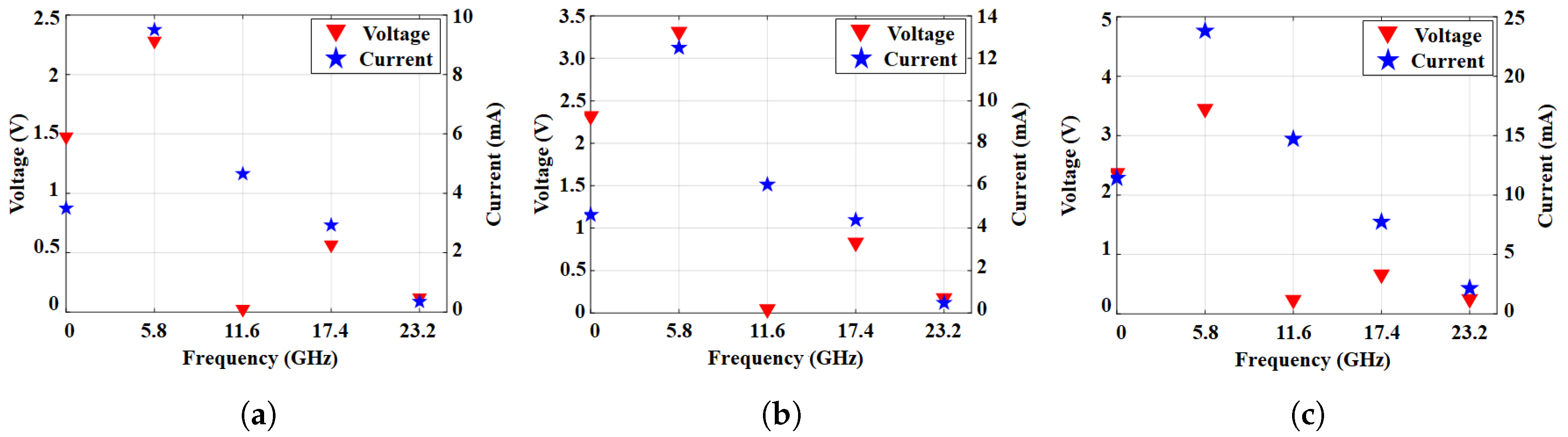

4. Simulation and Measurement

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Conflicts of Interest

References

- Kapil, B.; Pramod, K. Highly Efficient 2.4 GHz and 5.8 GHz Dual-Band Rectenna for Energy Harvesting Applications. IEEE Antennas Wirel. Propag. Lett. 2019, 12, 1–14. [Google Scholar]

- Erez, F.; Michael, R.; Zoya, P. Low-Power Wireless Power Delivery. IEEE Trans. Microw. Theory Tech. 2012, 6, 2277–2286. [Google Scholar]

- Shohei, I.; Shoichi, T.; Kazuhiro, F.; Minoru, S.; Shigeji, N. Efficiency and harmonics generation in microwave to DC conversion circuits of half-wave and full-wave rectifier types. In Proceedings of the IEEE MTT-S International Microwave Workshop Series on Innovative Wireless Power Transmission, Kyoto, Japan, 12–13 May 2011. [Google Scholar]

- Michael, R.; Tibault, R.; Ignacio, R.; Erez, A.F.; Zoya, P. High-Efficiency Harmonically Terminated Diode and Transistor Rectifiers. IEEE Trans. Microw. Theory Tech. 2012, 60, 4043–4052. [Google Scholar]

- Zhang, Q.; Ou, J.-H.; Wu, Z.; Tan, H.-Z. Novel Microwave Rectifier Optimizing Method and Its Application in Rectenna Designs. IEEE Access 2018, 6, 53557–53665. [Google Scholar] [CrossRef]

- Bae, J.; Yi, S.-H.; Choi, W.; Koo, H.; Hwang, K.-C.; Lee, K.-Y.; Yang, Y. 5.8 GHz High-Efficiency RF-DC Converter Based on Common-Ground Multiple-Stack Structure. Sensors 2019, 19, 3257. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Lu, P.; Song, C.; Huang, K.M. A Compact Rectenna Design With Wide Input Power Range for Wireless Power Transfer. IEEE Trans. Power Electron. 2020, 35, 6705–6710. [Google Scholar] [CrossRef]

- Jisu, K.; Juntaek, O. Compact Rectifier Array With Wide Input Power and Frequency Ranges Based on Adaptive Power Distribution. IEEE Microw. Wirel. Power Compon. Lett. 2021, 31, 513–516. [Google Scholar]

- Samuel, A.R.; Symon, K.P.; Pascual, D.H.R.; Mateo, S.; George, G.; Jaesup, L. Efficient Rectifier for Wireless Power Transmission Systems. IEEE Trans. Microw. Theory Tech. 2020, 68, 1921–1932. [Google Scholar]

- Ferran, B.; Javier, B.; Ana, C.; Apostolos, G. RF Energy Harvesting From Multi-Tone and Digitally Modulated Signals. IEEE Trans. Microw. Theory Tech. 2016, 64, 1918–1927. [Google Scholar]

- Du, Z.-X.; Zhang, X.Y. High-Efficiency Microwave Rectifier With Less Sensitivity to Input Power Variation. IEEE Microw. Wirel. Power Compon. Lett. 2017, 27, 1001–1003. [Google Scholar] [CrossRef]

- Song, G.; Liu, X.; Liu, C. Wide-Range Rectifier for Wireless Power Transfer Based on Power Compensation. IEEE Microw. Wirel. Power Compon. Lett. 2021, 31, 509–512. [Google Scholar] [CrossRef]

- Joseph, S.D.; Hsu, S.S.H.; Alieldin, A.; Song, C.; Liu, Y.; Huang, Y. High-Power Wire Bonded GaN Rectifier for Wireless Power Transmission. IEEE Access 2020, 8, 82035–82041. [Google Scholar] [CrossRef]

- Alirio, B.; Ana, C.; Nuno, B.C.; Apostolos, G. Optimum behavior: Wireless power transmission system design through behavioral models and efficient synthesis techniques. IEEE Microw. Mag. 2013, 14, 26–35. [Google Scholar]

- Ce, W.; Naoki, S.; Tomohiko, M. Study on 5.8 GHz Single-Stage Charge Pump rectifier for Internal Wireless System of Satellite. IEEE Trans. Microw. Theory Tech. 2017, 65, 1058–1065. [Google Scholar]

- Guo, J.; Zhang, H.; Zhu, X. Theoretical Analysis of RF-DC Conversion Efficiency for Class-F Rectifiers. IEEE Trans. Microw. Theory Tech. 2014, 62, 977–985. [Google Scholar] [CrossRef]

- Akihito, N.; Hiroyuki, S. Compact Class-F RF-DC Converter with Antisymmetric Dual-Diode Configuration. In Proceedings of the IEEE MTT-S International Microwave Symposium Digest, Motreal, QC, Canada, 17–22 June 2012. [Google Scholar]

- Zhao, F.; Inserra, D.; Wen, G.; Li, J.; Huang, Y. A High-Efficiency Inverse Class-F Microwave Rectifier for Wireless Power Transmission. IEEE Microw. Wirel. Compon. Lett. 2019, 29, 725–728. [Google Scholar] [CrossRef]

| Parameters | Unit | Description | Value |

|---|---|---|---|

| Zero junction capacitance | 0.39 | ||

| Series parasitic resistance | 2.65 | ||

| V | Breakdown voltage | 2.65 | |

| V | Built-in potential | 0.224 | |

| N | - | Number of stages | 1–3 |

| f | Frequency | 5.8 | |

| Load impedance | 100–2000 | ||

| Characteristic impedance | 100 |

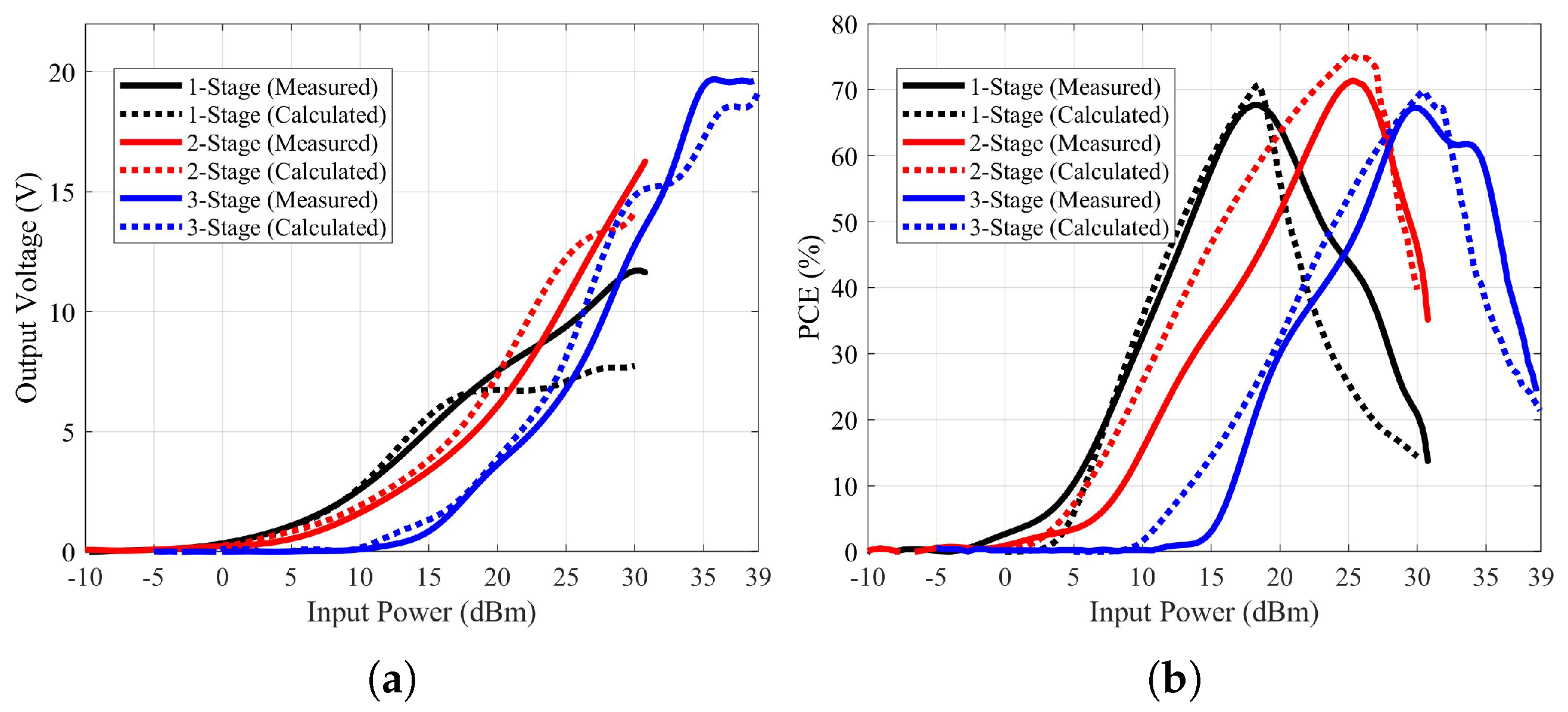

| Number of Stages (N) | Maximum Value | |

|---|---|---|

| (V) | PCE (%) | |

| 1 | 11.6 | 68% @18 dBm |

| 2 | 15.8 | 71% @25 dBm |

| 3 | 19.8 | 67% @30 dBm |

| Circuit Topology | Device Type | Freq. (GHz) | Input Range (dBm) | Optimum Load () | Max PCE (%) | Technique | |

|---|---|---|---|---|---|---|---|

| [15] | Class F | Schotty Diode (N/A) | 5.8 | 10∼16 | 1300 | 71 | Harmonic Termination (third) |

| [4] | Class C | Schottky Diode (SMS7630) | 2.45 | 0∼10 | 200∼1200 | 72.8 | Harmonic Termination |

| [2] | Shunt Diode | Schottky Diode (SMS7630) | 1.96 | 0∼10 | 200∼1200 | 63 | Rectenna |

| [16] | Class F | Schottky Diode (HSMS8202) | 5.8 | 0∼17 | 300∼700 | 80 | Harmonic Termination (second, third) |

| [17] | Class F | Schottky Diode (HSMS2822) | 2.45 | 10∼28 | 1000 | 75.4 | Harmonic Termination |

| [18] | Class F | Schottky Diode (HSMS2860) | 2.35 | 0∼18 | 100∼1000 | 80.4 | Harmonic Termination (second, third) |

| [3] | Full wave | Schottky Diode (MA4E2054) | 5.8 | 0∼22 | 100∼800 | 65.3 | Harmonic Termination (second) |

| [1] | Series diode | Schottky Diode (HSMS2860) | 5.8 | −10∼15 | 1000 | 51.5 | Dual band impedance matching |

| [5] | Shut diode | Schottky Diode (BAT1503) | 5.81 | 0∼9 | 1300 | 69.2 | Harmonic Termination (second, third) |

| [6] | Dickson charge pump | Schottky Diode (HSMS2862) | 5.8 | 21∼25 | 1000 | 64 | Harmonic Termination (third) |

| This work | N-stage HTVM | Schottky Diode (BAT1704) | 5.8 | 0∼32 | 1500 | 68 (one-stage), 71 (two-stage), 67 (three-stage) | Harmonic Termination (second, third) |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kim, J.; Park, I.; Ku, H. Design of a Highly Efficient N-Stage Harmonic Terminated Voltage Multiplier for Wireless Power Transfer. Energies 2021, 14, 7203. https://doi.org/10.3390/en14217203

Kim J, Park I, Ku H. Design of a Highly Efficient N-Stage Harmonic Terminated Voltage Multiplier for Wireless Power Transfer. Energies. 2021; 14(21):7203. https://doi.org/10.3390/en14217203

Chicago/Turabian StyleKim, Juwan, Inho Park, and Hyunchul Ku. 2021. "Design of a Highly Efficient N-Stage Harmonic Terminated Voltage Multiplier for Wireless Power Transfer" Energies 14, no. 21: 7203. https://doi.org/10.3390/en14217203

APA StyleKim, J., Park, I., & Ku, H. (2021). Design of a Highly Efficient N-Stage Harmonic Terminated Voltage Multiplier for Wireless Power Transfer. Energies, 14(21), 7203. https://doi.org/10.3390/en14217203