Technical Limits of Passivity-Based Control Gains for a Single-Phase Voltage Source Inverter

Abstract

1. Introduction

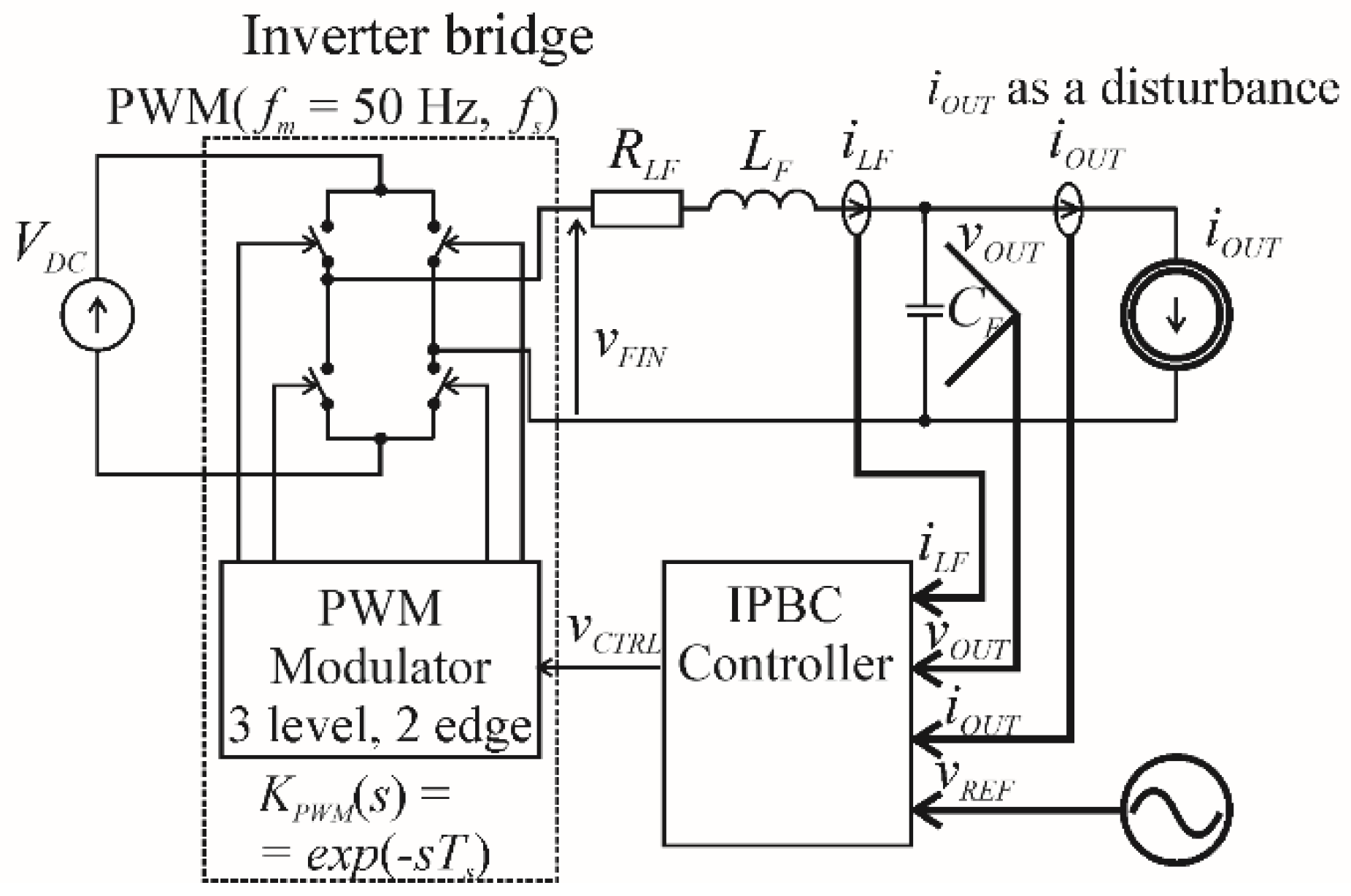

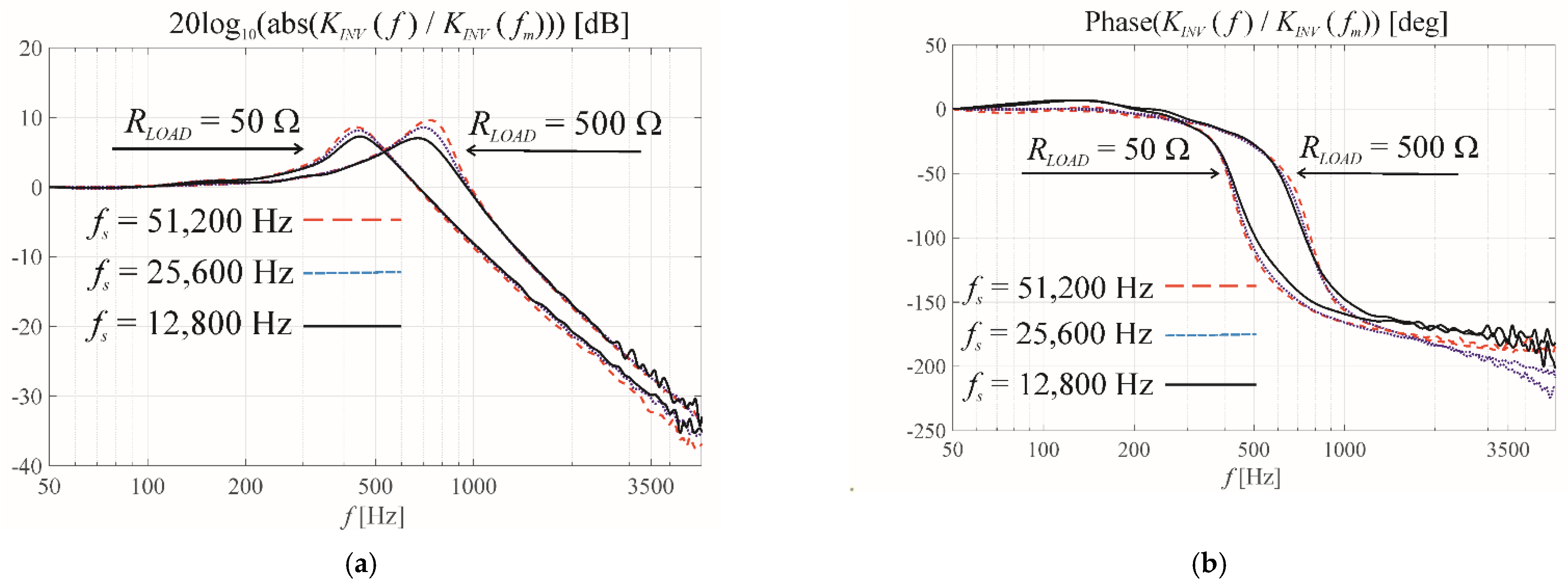

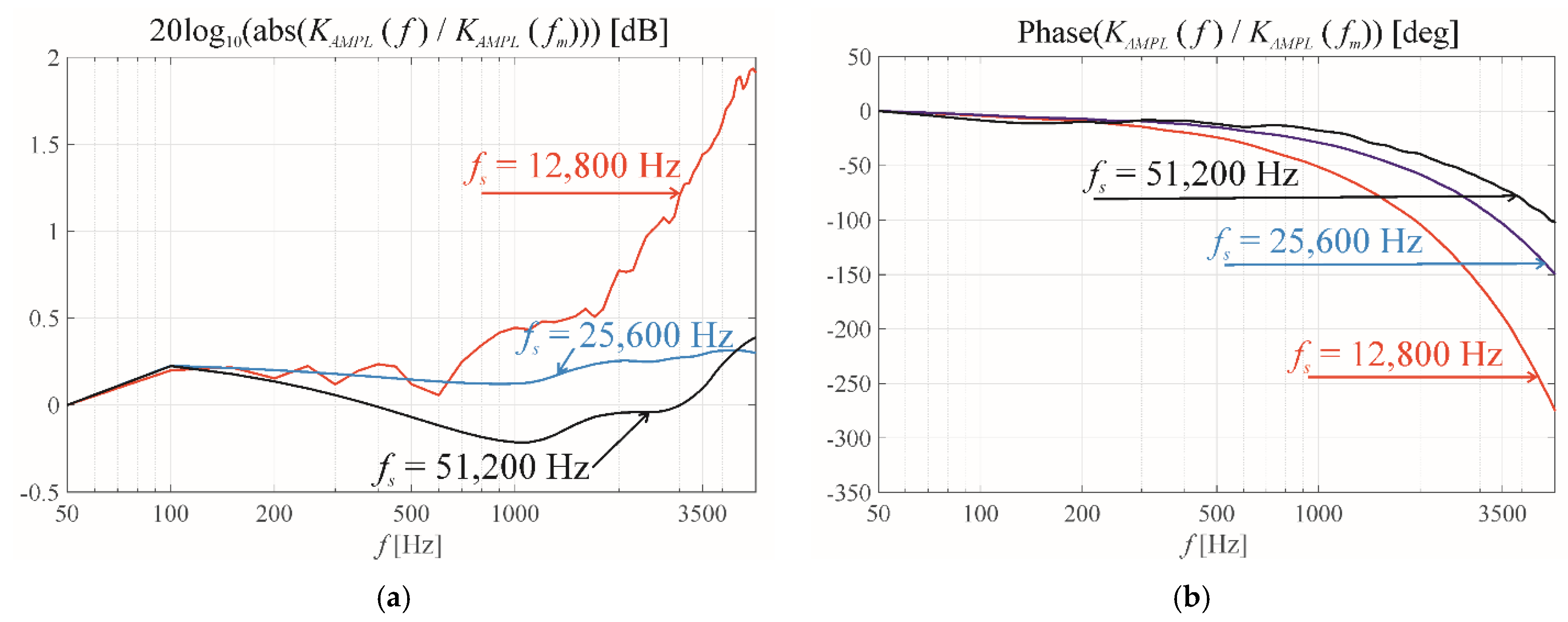

2. Fundamentals of PBC Controller Design

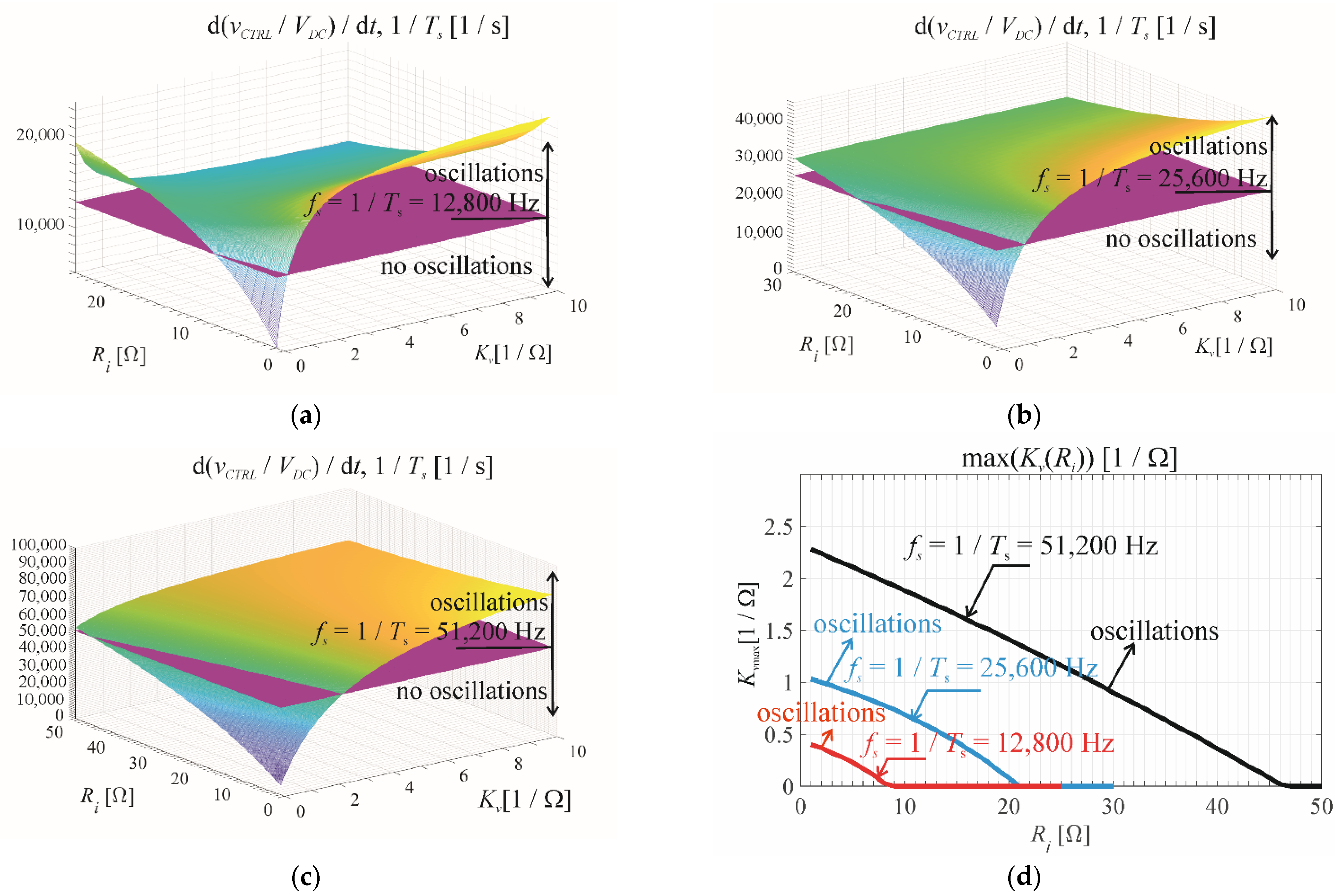

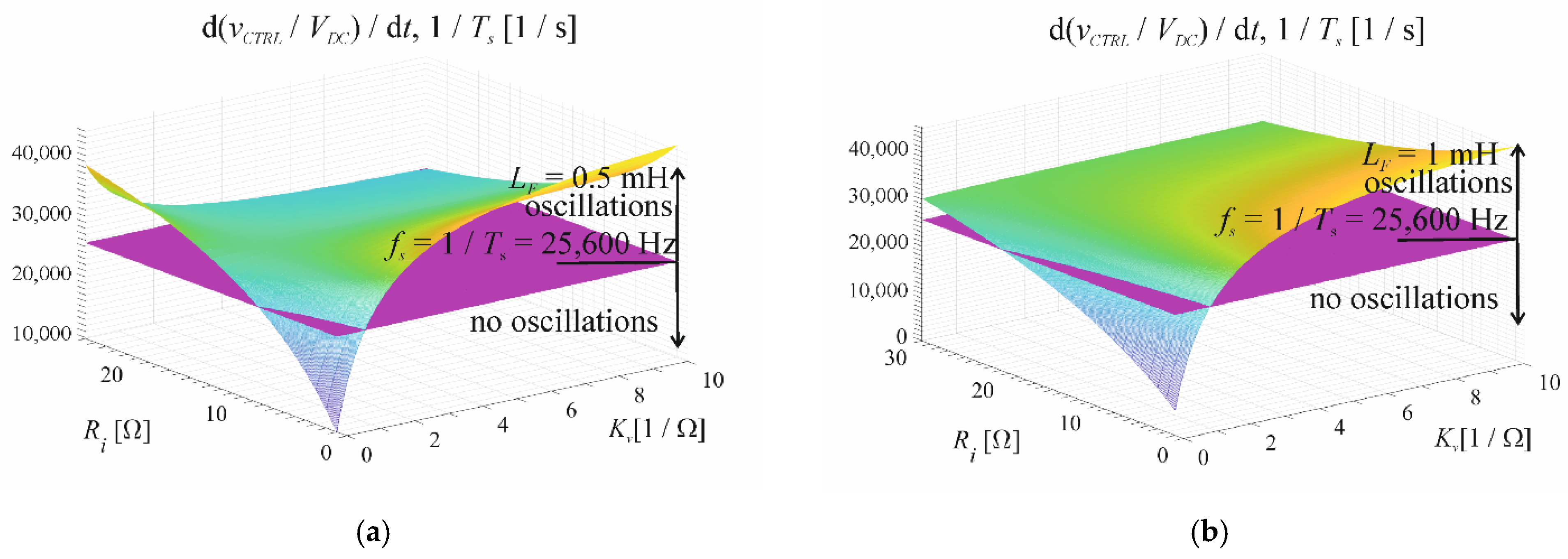

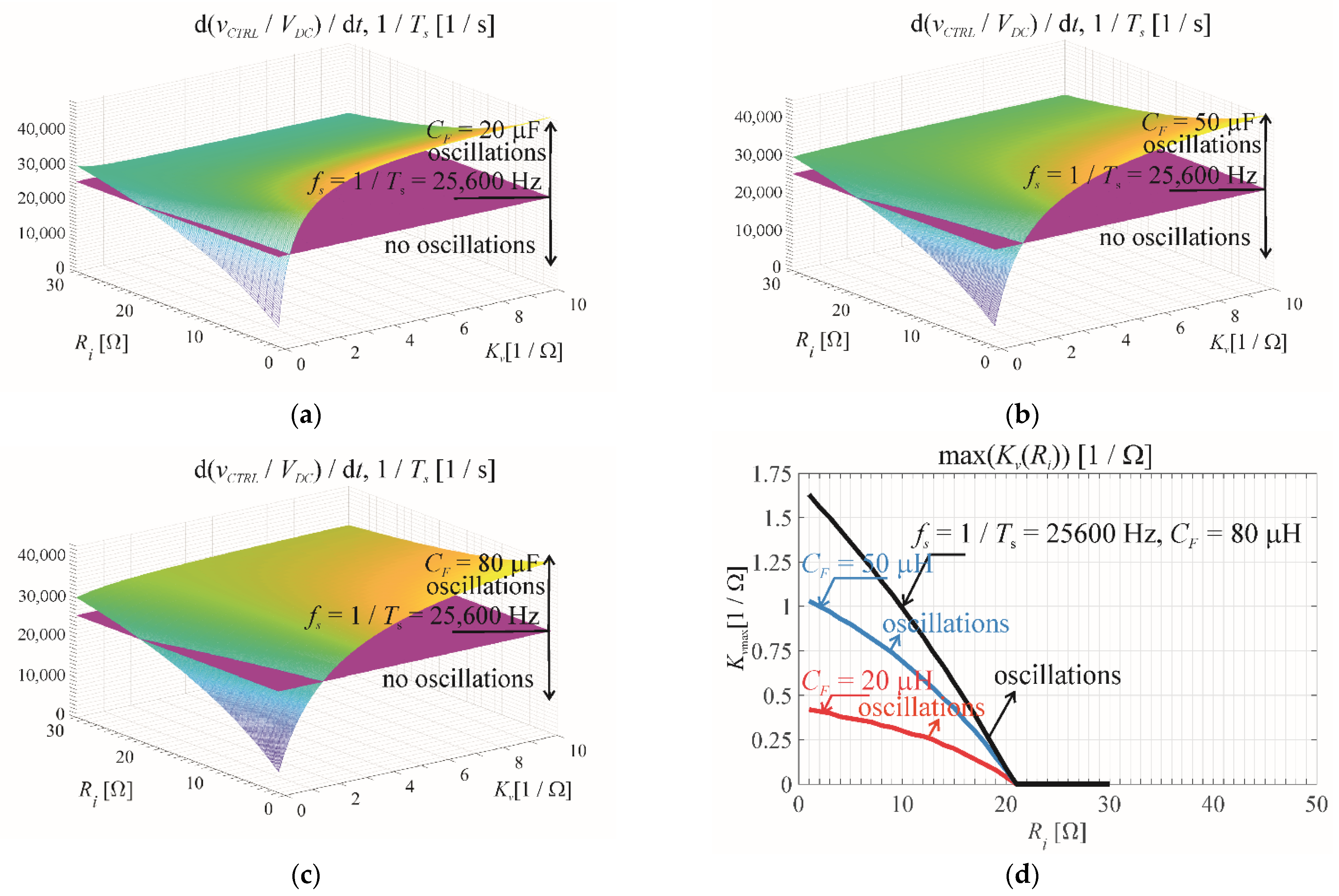

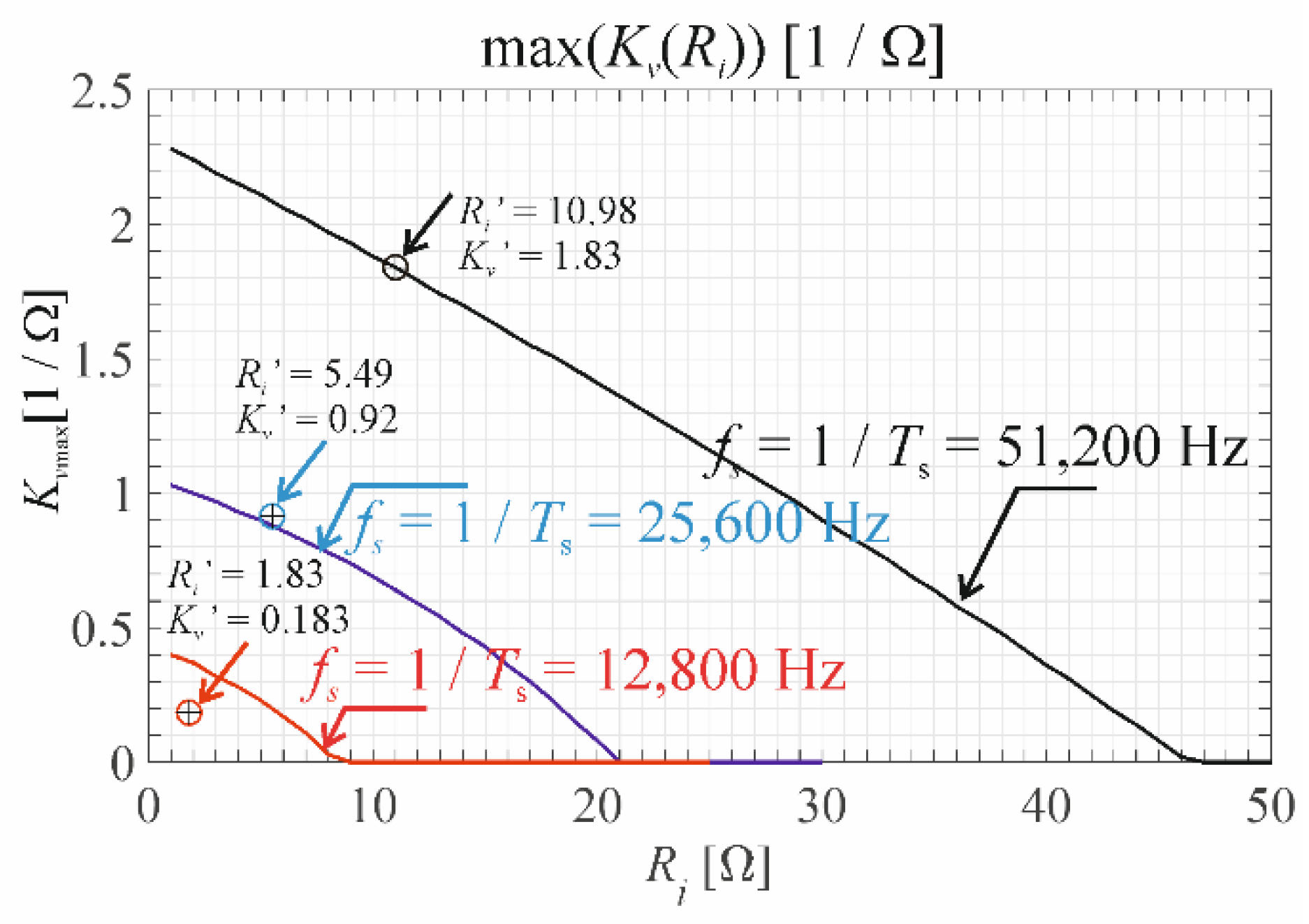

3. The Influence of the Switching Frequency and Output Filter Parameters on the Border IPBC Gains

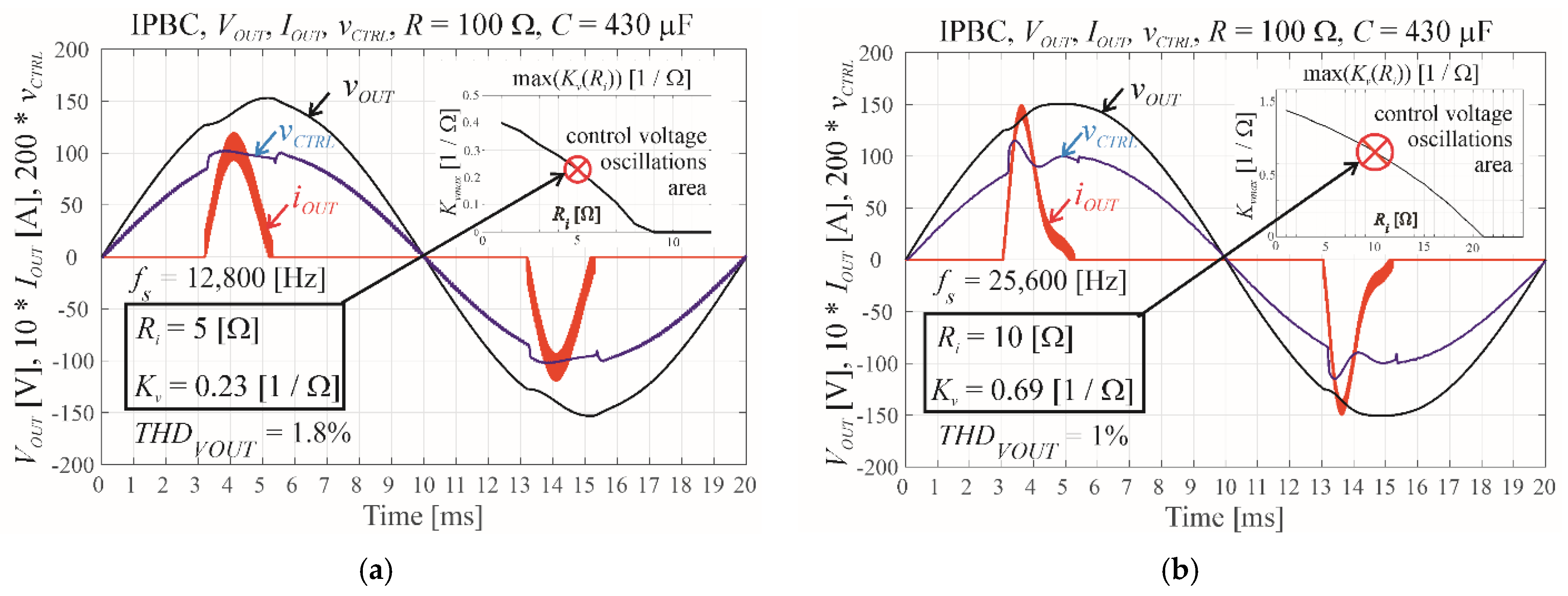

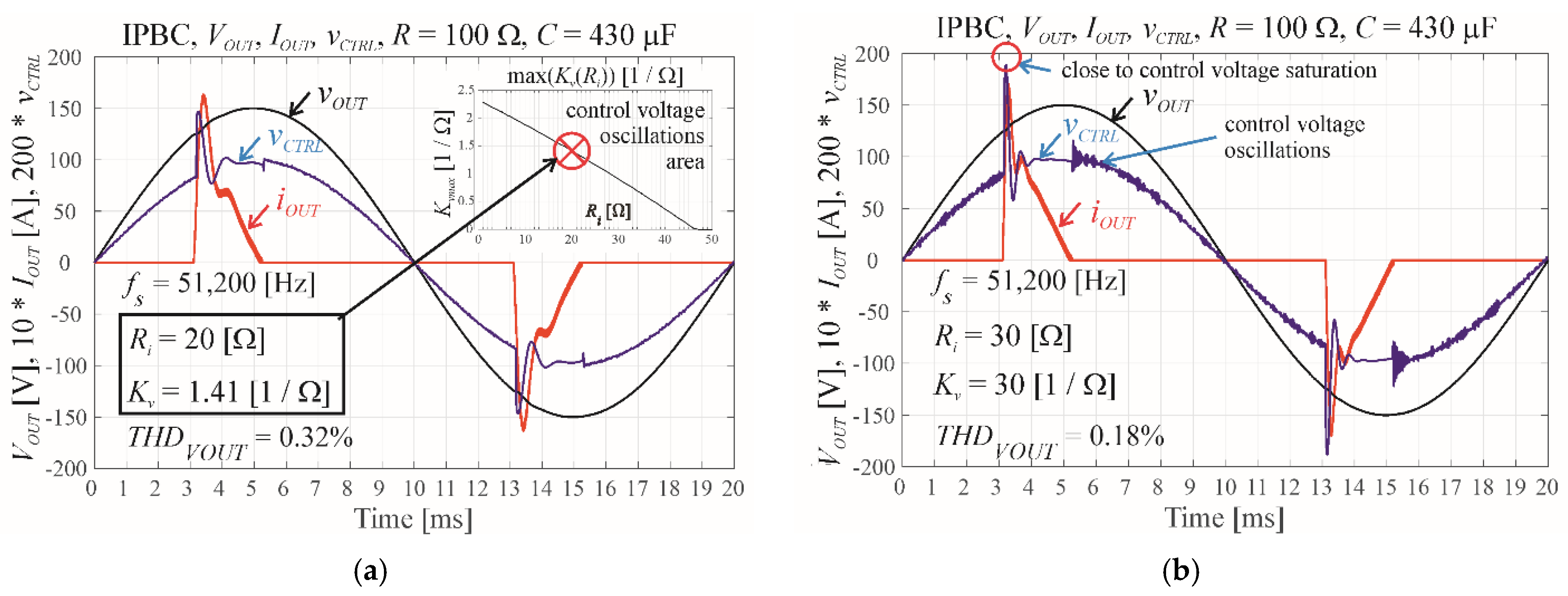

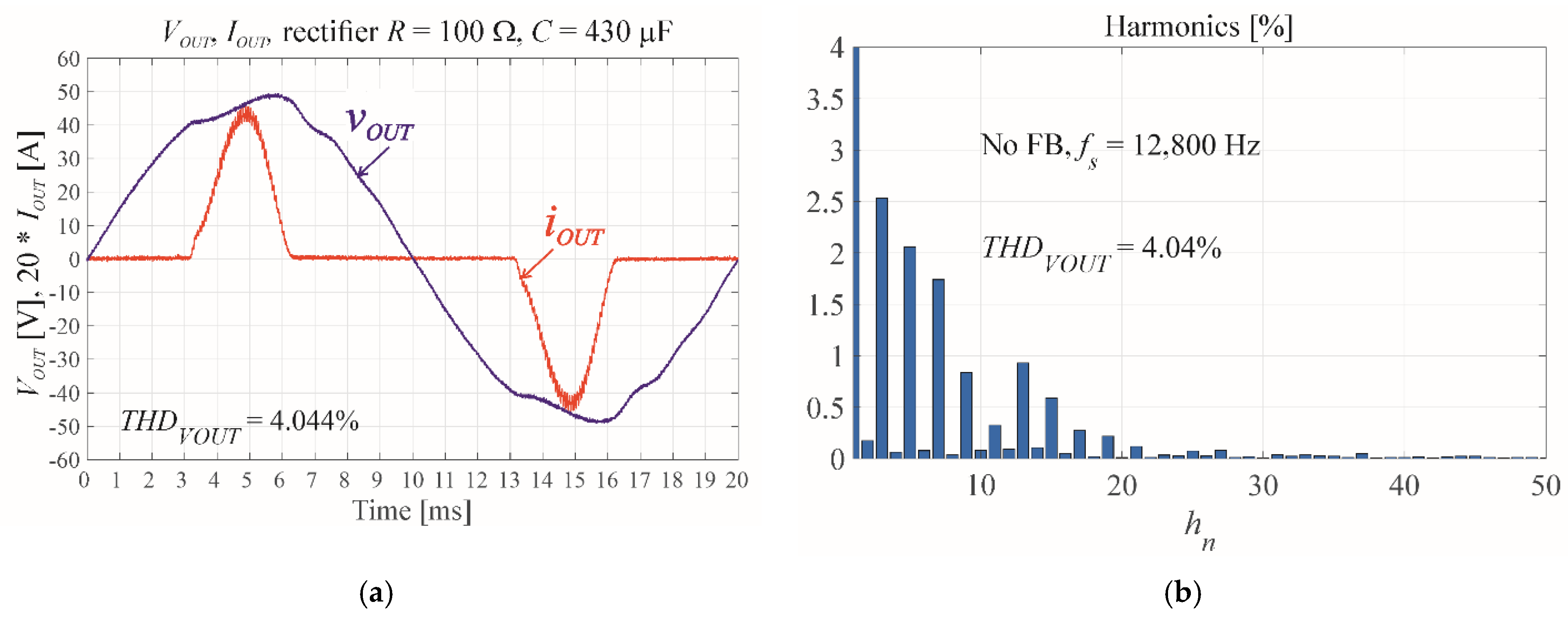

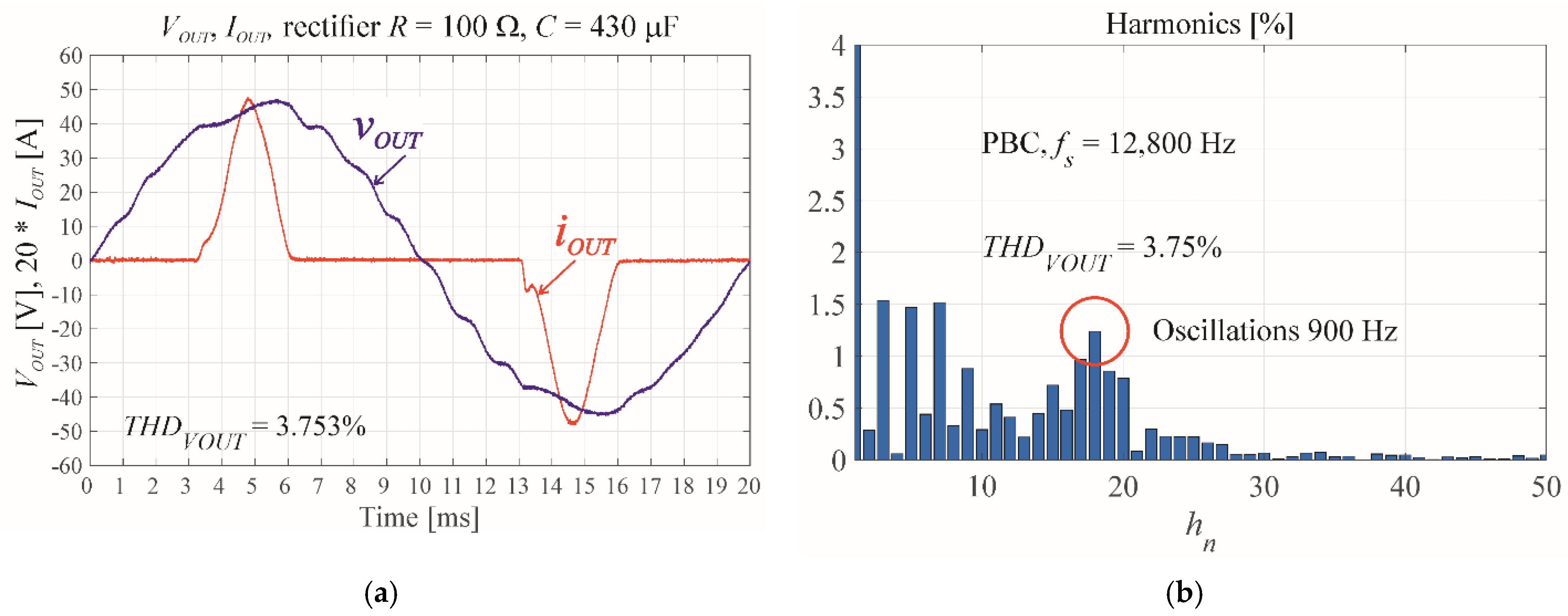

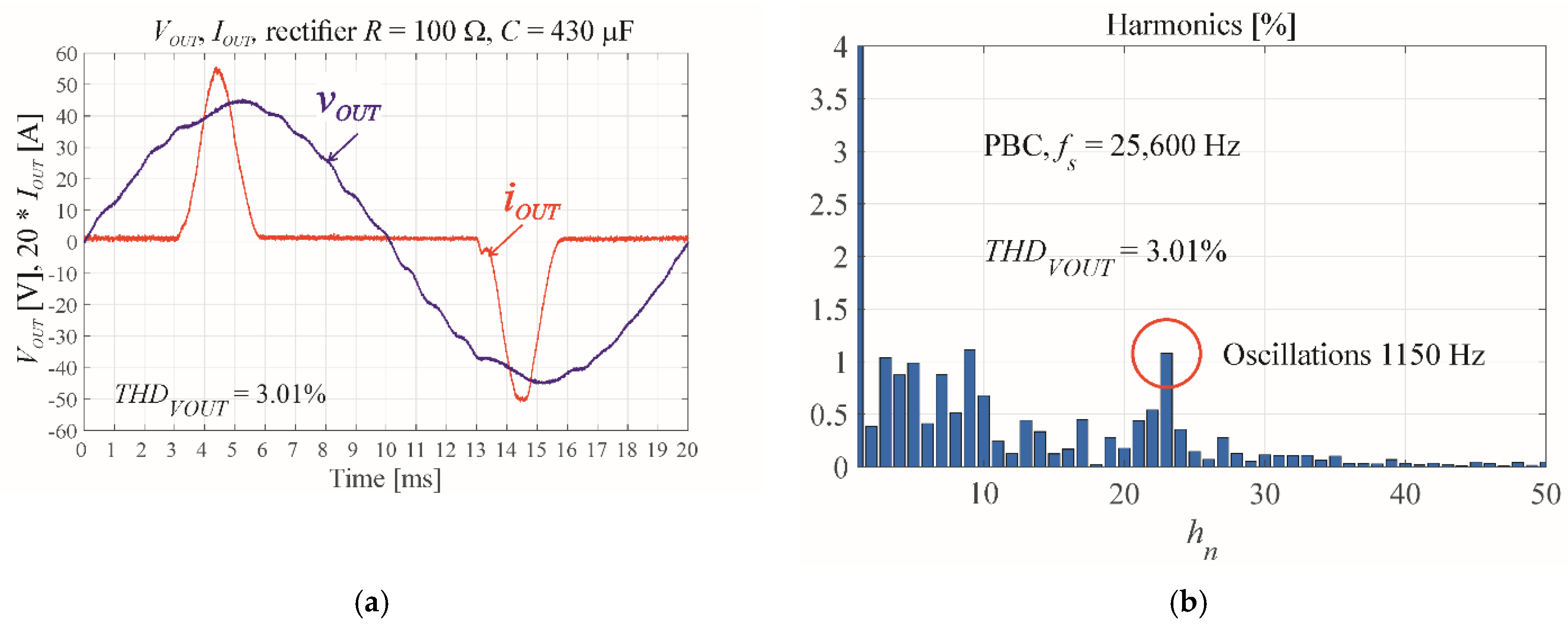

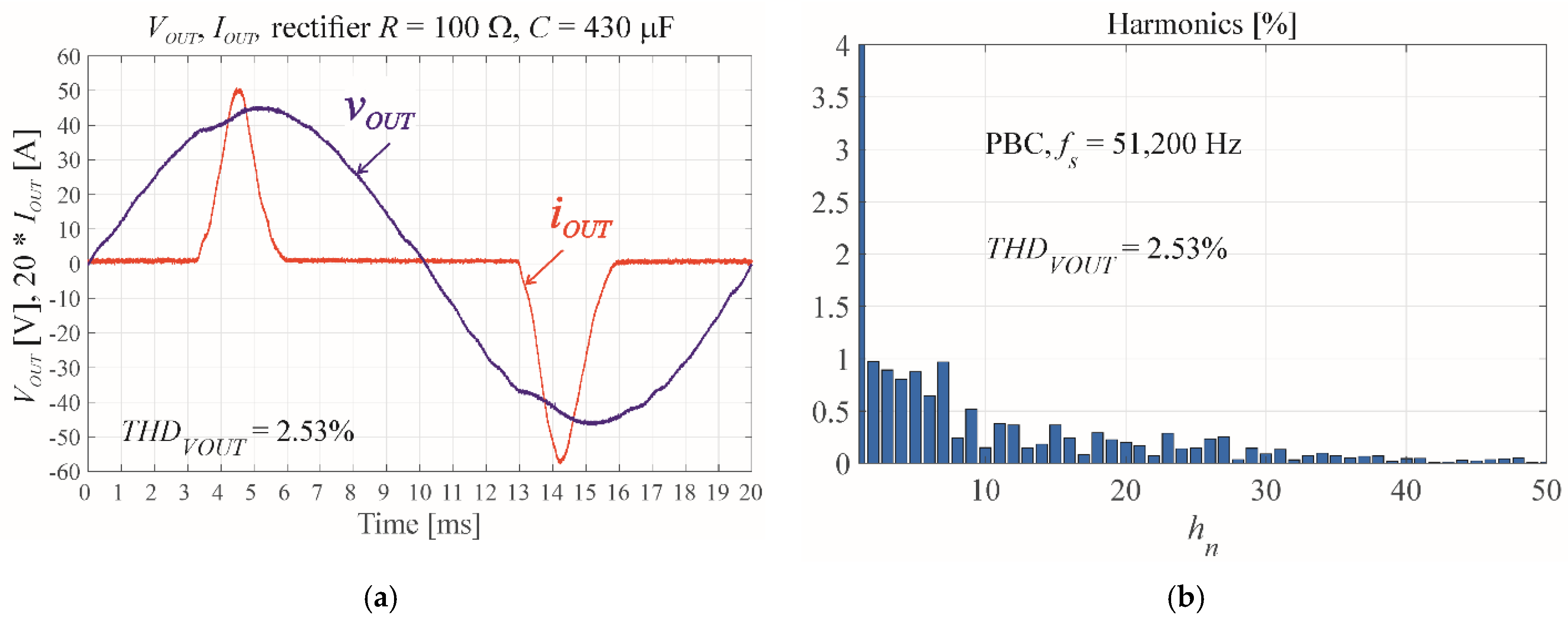

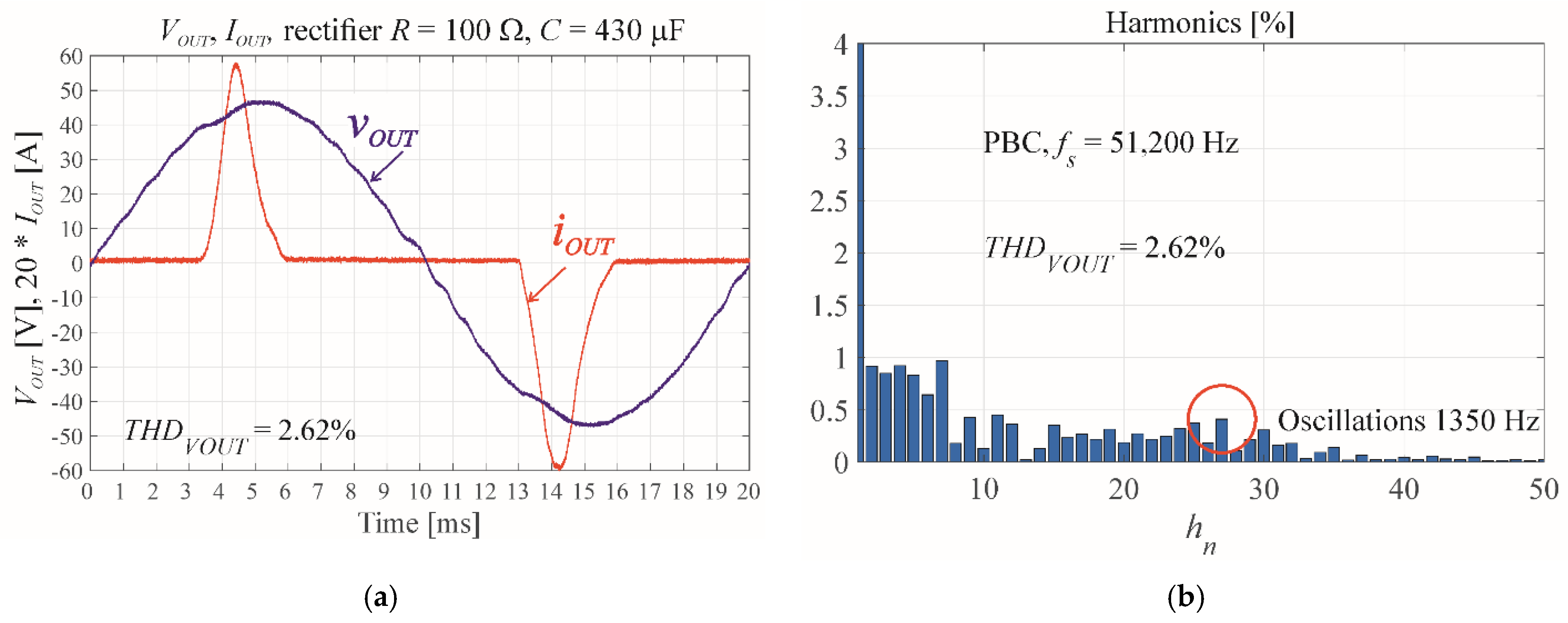

4. Simulations of a VSI with an IPBC for a Nonlinear Rectifier RC Load

5. Discussion of the Simulation Results

- For the frequencies analyzed (12,800, 25,600, and 51,200 Hz), it was important to consider the delay of the PWM modulator in the control law. Even the simplest prediction of the variables in the next switching period using the discrete state space equations allowed an estimation of the PBC border gains to lower distortions of the inverter output voltage and a better dynamic load change response.

- Basic PBC theory does not enable the limits of the PBC gains to be found. For positive gains, a system is always theoretically stable [9]. The technical properties of an inverter control system cause the restrictions. Below the border gains of the PBC, there are no output voltage oscillations. The border gains are calculated based on the assumption that the increase of the control voltage should not be faster than the possible increase of the PWM modulator voltage (VDC voltage in one switching period Ts).

- Additional gain increases over the border values causes oscillations of the output voltage and the inductor current and output voltage distortions. It is possible to find the maximum gains of the PBC for the minimum of the output voltage THD.

- A lower modulation index, M, is preferable—it is a (1–M)VDC margin of voltage that forces an inductor current increase. However, low values of M will not be used in a practical design because we always allow for the potential of full input voltage (M close to unity).

- A lower M helps avoid saturation of the PWM modulator (Figure 6b) for higher controller gains.

- The oscillations of the inductor current slightly increase the power losses in the inductor core.

- The results shown in Table 1 confirm the preference for using a higher switching frequency. However, we should not forget about potential technical problems. In one switching period, we count up to a value that equals the PWM comparator frequency divided by the switching frequency. In the experimental work, we used an STM32F407VG microprocessor with an 84 MHz frequency in the PWM modulator. Using fs = 51,200 Hz (1024 switching time periods per fundamental period), we obtained the maximum counted value per switching period of ≈1640 (the amplitude of the sinusoidal reference waveform was 820). The resolution, 1/820 = 1.2 × 10−3, was insufficient for the generated sinusoidal waveform close to π because the change of 1 − sin(2π × (256 − 1)/1024) = 1.8825 × 10−5, was lower than the resolution. It caused the width of some (in our case 16) neighboring PWM pulses of the reference waveform close to π/2 or 3π/2 to be the same; however, in this case, the additional distortions were ignored (ΔTHD = 0.051%). Therefore, fs = 51,200 Hz was assigned as the highest switching frequency for the STM32F407VG microprocessor control.

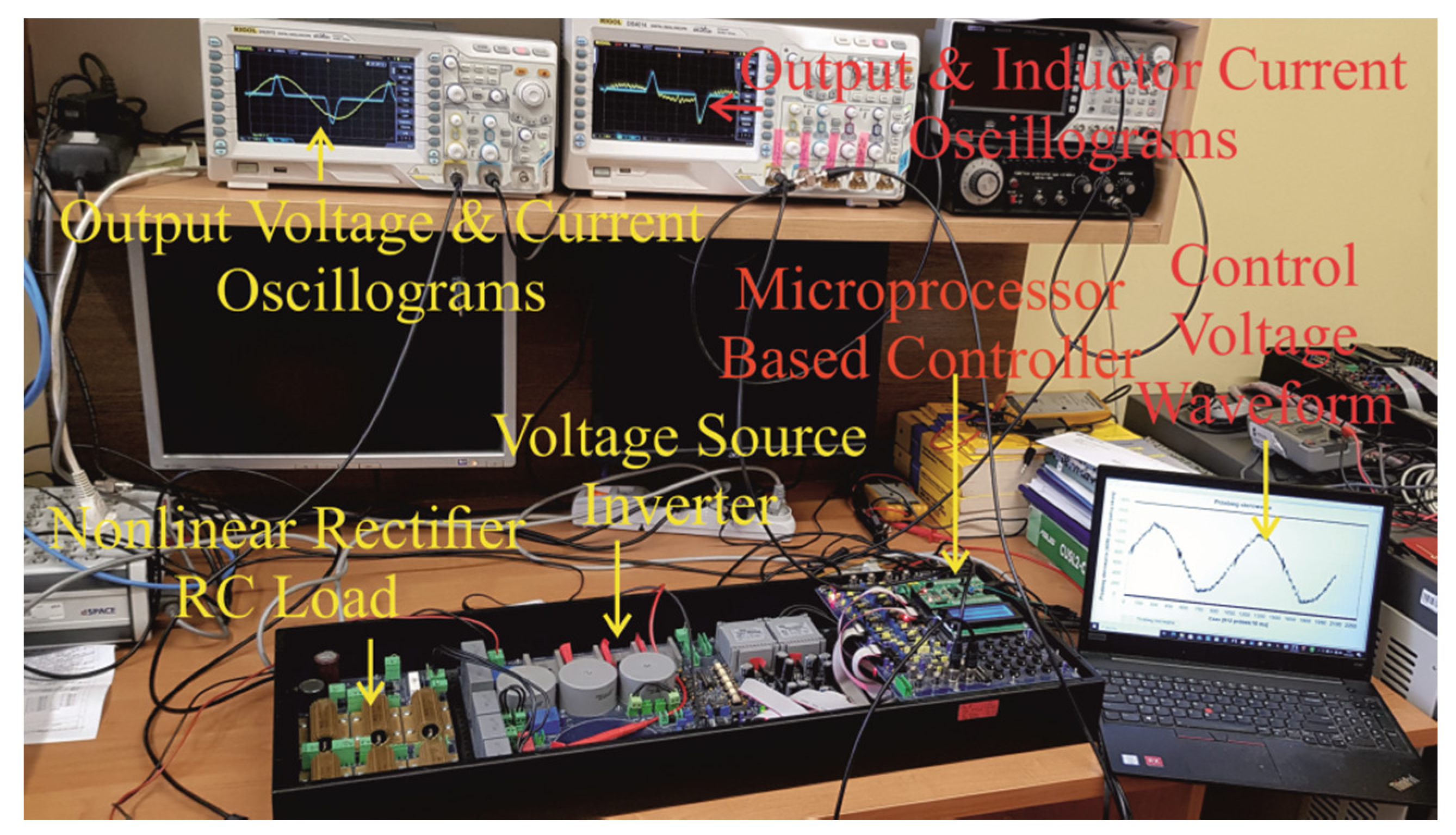

6. Experimental Verification

7. Discussion of the Experimental Results

8. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Conflicts of Interest

References

- Ortega, R.; Garcıa-Canseco, E. Interconnection and Damping Assignment Passivity-Based Control: A Survey. Eur. J. Control 2004, 10, 432–450. [Google Scholar] [CrossRef]

- Wang, Z.; Goldsmith, P. Modified energy-balancing-based control for the tracking problem. IET Control Theory Appl. 2008, 2, 310–312. [Google Scholar] [CrossRef]

- Cupertino, A.F.; Carlette, L.P.; Perez, F.; Resende, J.T.; Seleme, S.I., Jr.; Pereira, H.A. Use of Control Based on Passivity to Mitigate the Harmonic Distortion Level of Inverters. In Proceedings of the 2013 IEEE PES Conference on Innovative Smart Grid Technologies (ISGT Latin America), Sao Paulo, Brazil, 15–17 April 2013; pp. 1–7. [Google Scholar] [CrossRef]

- Biel, J.M.; Scherpen, A. Passivity-based control of active and reactive power in single-phase PV inverters. In Proceedings of the 2017 IEEE 26th International Symposium on Industrial Electronics (ISIE), Edinburgh, UK, 19–21 June 2017; pp. 999–1004. [Google Scholar] [CrossRef]

- Komurcugil, H. Improved passivity-based control method and its robustness analysis for single-phase uninterruptible power supply inverters. IET Power Electron. 2015, 8, 1558–1570. [Google Scholar] [CrossRef]

- Rymarski, Z.; Bernacki, K.; Dyga, Ł. Some aspects of voltage source inverter control. Elektron. Ir Elektrotechnika 2017, 23, 26–30. [Google Scholar] [CrossRef][Green Version]

- Zhang, Z.; Yao, N.; Wang, C.; Kang, L.; Kang, L. A Passivity-based Control Method for the Single-Phase Three-level Inverter. In Proceedings of the 18th International Conference on Electrical Machines and Systems (ICEMS), Pattaya City, Thailand, 25–28 October 2015; pp. 1515–1518. [Google Scholar]

- Rymarski, Z.; Bernacki, K.; Dyga, Ł. Decreasing the single-phase inverter output voltage distortions caused by impedance networks. IEEE Trans. Ind. Appl. 2019, 55, 7586–7594. [Google Scholar] [CrossRef]

- Rymarski, Z.; Bernacki, K. Different Features of Control Systems for Single-Phase Voltage Source Inverters. Energies 2020, 13, 4100. [Google Scholar] [CrossRef]

- Serra, F.M.; De Angelo, C.H.; Forchetti, D.G. IDA-PBC control of a DC–AC converter for sinusoidal three-phase voltage generation. Int. J. Electron. 2016, 104, 93–110. [Google Scholar] [CrossRef]

- Rymarski, Z.; Bernacki, K.; Dyga, Ł. A control for an unbalanced 3-phase load in UPS systems. Elektron. Ir Elektrotechnika 2018, 24, 27–31. [Google Scholar] [CrossRef]

- Rymarski, Z.; Bernacki, K.; Dyga, Ł.; Davari, P. Passivity-Based Control Design Methodology for UPS Systems. Energies 2019, 12, 4301. [Google Scholar] [CrossRef]

- IEC. IEC 62040-3:2021 Uninterruptible Power Systems (UPS)—Part 3: Method of Specifying the Performance and Test Requirements; IEC: Geneva, Switzerland, 2021. [Google Scholar]

- IEC. IEC 61000-2-2:2003 Electromagnetic Compatibility (EMC)—Part 2-2: Environment—Compatibility Levels for Low-Frequency Conducted Disturbances and Signalling in Public Low-Voltage Power Supply Systems; IEC: Geneva, Switzerland, 2003. [Google Scholar]

- Slovenski Standard. EN 50160:2010—Voltage Characteristics of Electricity Supplied by Public Distribution Systems; Slovenski Standard: Ljubljana, Slovenija, 2010. [Google Scholar]

- IEEE. IEEE 519-2014—IEEE Recommended Practice and Requirements for Harmonic Control in Electric Power Systems; IEEE: Piscataway, NJ, USA, 2014. [Google Scholar]

- Akagi, H.; Hirokazu, E.; Aredes, W.M. Instantaneous Power Theory and Applications to Power Conditioning, 2nd ed.; Wiley-IEEE Press: Piscataway, NJ, USA, 2017. [Google Scholar] [CrossRef]

- Rymarski, Z.; Bernacki, K. Different approaches to modelling single-phase voltage source inverters for uninterruptible power supply systems. IET Power Electron. 2016, 9, 1513–1520. [Google Scholar] [CrossRef]

- Rymarski, Z. Design Method of Single-Phase Inverters for UPS Systems. Int. J. Electron. 2009, 96, 521–535. [Google Scholar] [CrossRef]

- Rymarski, Z. The discrete model of the power stage of the voltage source inverter for UPS. Int. J. Electron. 2011, 98, 1291–1304. [Google Scholar] [CrossRef]

- Xie, R.; Hao, X.; Yang, X.; Chen, W.; Huang, L.; Wang, C. An Exact Discrete-Time Model Considering Dead-Time Nonlinearity for an H-Bridge Grid Connected Inverter. In Proceedings of the 2014 International Power Electronics Conference, Hiroshima, Japan, 18–21 May 2014; pp. 2950–2953. [Google Scholar]

- Rymarski, Z. Measuring the real parameters of single-phase voltage source inverters for UPS systems. Int. J. Electron. 2017, 104, 1020–1033. [Google Scholar] [CrossRef]

- Bernacki, K.; Rymarski, Z.; Dyga, Ł. Selecting the coil core powder material for the output filter of a voltage source inverter. Electron. Lett. 2017, 53, 1068–1069. [Google Scholar] [CrossRef]

- Rymarski, Z.; Bernacki, K.; Dyga, Ł. Measuring the power conversion losses in voltage source inverters. AEU Int. J. Electron. Commun. 2020, 124, 153359. [Google Scholar] [CrossRef]

- Yuan, W.; Wang, Y.; Liu, D.; Deng, F.; Chen, Z. Robust Droop Control of AC Microgrid Against Nonlinear Characteristic of Inductor. In Proceedings of the 2019 IEEE 10th International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Xi’an, China, 3–6 June 2019; pp. 642–647. [Google Scholar] [CrossRef]

- Kawamura, A.; Chuarayapratip, R.; Haneyoshi, T. Deadbeat Control of PWM Inverter with Modified Pulse Patterns for Uninterruptible Power Supply. IEEE Trans. Ind. Electron. 1988, 35, 295–300. [Google Scholar] [CrossRef]

- Rech, C.; Pinheiro, H.; Gründling, H.A.; Hey, H.L.; Pinheiro, J.R. Comparison of Digital Control Techniques with Repetitive Integral Action for Low Cost PWM Inverters. IEEE Trans. Power Electron. 2003, 18, 401–410. [Google Scholar] [CrossRef]

- Cheng, X.; Chen, Y.; Chen, X.; Zhang, B.; Qiu, D. An extended analytical approach for obtaining the steady-state periodic solutions of SPWM single-phase inverters. In Proceedings of the 2017 IEEE Energy Conversion Congress and Exposition (ECCE), Cincinnati, OH, USA, 1–5 October 2017; pp. 1311–1316. [Google Scholar] [CrossRef]

- Bowes, S.R.; Bird, B.M. Novel approach to the analysis and synthesis of modulation processes in power convertors. IET 1975, 122, 507–513. [Google Scholar] [CrossRef]

- Bowes, S.R.; Mech, M.I. New sinusoidal pulse width-modulated invertor. IET 1975, 122, 1279–1285. [Google Scholar]

- Cheng, Y.; Zha, X.; Liu, Y. Nonlinear modeling of inverter using the Hammerstein’s approach. In Proceedings of the INTELEC 2009—31st International Telecommunications Energy Conference, Incheon, Korea, 18–22 October 2009; pp. 1–4. [Google Scholar] [CrossRef]

- Ryan, M.J.; Brumsickle, W.E.; Lorenz, R.D. Control topology options for single-phase UPS inverters. IEEE Trans. Ind. Appl. 1997, 33, 493–501. [Google Scholar] [CrossRef]

- Kawamura, A.; Yokoyama, T. Comparison of Five Different Approaches for Real Time Digital Feedback Control of PWM Inverters. In Proceedings of the Conference Record of the 1990 IEEE Industry Applications Society Annual Meeting, Seattle, WA, USA, 7–12 October 1990; pp. 1005–1011. [Google Scholar] [CrossRef]

- Astrom, K.J.; Wittenmark, B. Computer-Controlled Systems: Theory and Design, 3rd ed.; Dover Publications Inc.: Mineola, NY, USA, 2011; ISBN 9780486486130. [Google Scholar]

- Bertotti, G. General properties of power losses in soft ferromagnetic materials. IEEE Trans. Magn. 1988, 24, 621–630. [Google Scholar] [CrossRef]

- Micrometals Arnold Powers Cores 2012. Available online: https://vdocuments.mx/arnold-powder-cores-2012.html (accessed on 16 May 2021).

- Olivier, C.H.G. Measurement and Modelling of Core Loss in Powder Core Materials. 2012. Available online: https://www.psma.com/sites/default/files/uploads/tech-forums-magnetics/presentations/2012-apec-131b-measurement-and-modeling-core-loss-powder-core-materials.pdf (accessed on 16 May 2021).

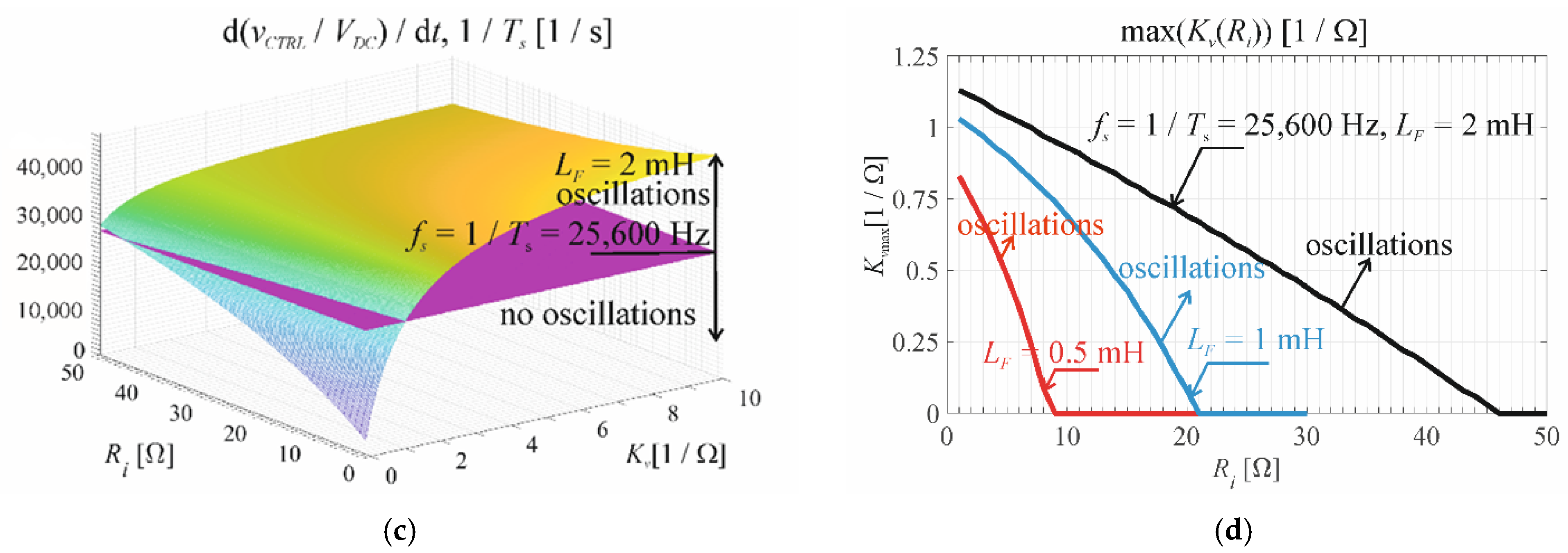

| Switching Frequency, Ri [Ω], Kv [1/Ω] | THDVOUT (Rectifier RC Load, R = 50 Ω, C = 430 μF) | Power Losses Increase ΔPlosses | Overvoltage after the Step Load Decrease (500||50)/500 Ω | |

|---|---|---|---|---|

| 12,800 [Hz], Ri = 5, Kv = 0.23 | Border gains | 1.8% | - | 2.71% |

| 25,600 [Hz], Ri = 10, Kv = 0.69 | Border gains | 1.0% | - | 1.81% |

| 51,200 [Hz], Ri = 20, Kv = 1.41 | Border gains | 0.32% | - | 0.94% |

| 51,200 Hz, Ri = 30, Kv = 30 (oscillations begin) | The values over the border gains | 0.18% | negligible | 0.77% |

| Switching Frequency, Gains: Ri [Ω], Kv [1/Ω] | THDVOUT (Rectifier RC Load, R = 50 Ω, C = 430 μF) | Power Losses Increase ΔPlosses | Overvoltage for the Step Load Decrease (500||50)/500 Ω | |

|---|---|---|---|---|

| 12800 [Hz], Ri = 2, Kv = 0.2 Ri’ = 1.83, Kv’ = 0.183 | Border gains | 3.753% | - | 6% |

| 25600 [Hz], Ri = 3, Kv = 0.5 Ri’ = 5.49, Kv’ = 0.92 | Border gains | 3.01% | - | 5.5% |

| 51200 [Hz], Ri = 3, Kv = 0.5 Ri’ = 10.98, Kv’ = 1.83 | Border gains | 2.53% | - | 5% |

| 51200 Hz, Ri = 3, Kv = 0.7 Ri’ = 10.98, Kv’ = 2.56 | Above the border values | 2.62% | 18.6% | 3.5% |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Rymarski, Z.; Bernacki, K. Technical Limits of Passivity-Based Control Gains for a Single-Phase Voltage Source Inverter. Energies 2021, 14, 4560. https://doi.org/10.3390/en14154560

Rymarski Z, Bernacki K. Technical Limits of Passivity-Based Control Gains for a Single-Phase Voltage Source Inverter. Energies. 2021; 14(15):4560. https://doi.org/10.3390/en14154560

Chicago/Turabian StyleRymarski, Zbigniew, and Krzysztof Bernacki. 2021. "Technical Limits of Passivity-Based Control Gains for a Single-Phase Voltage Source Inverter" Energies 14, no. 15: 4560. https://doi.org/10.3390/en14154560

APA StyleRymarski, Z., & Bernacki, K. (2021). Technical Limits of Passivity-Based Control Gains for a Single-Phase Voltage Source Inverter. Energies, 14(15), 4560. https://doi.org/10.3390/en14154560