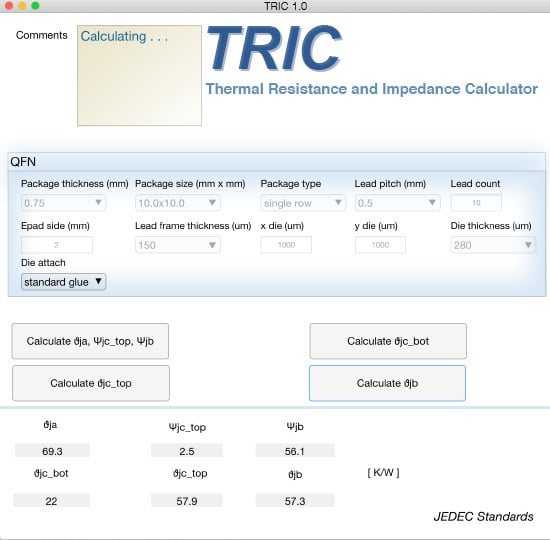

TRIC: A Thermal Resistance and Impedance Calculator for Electronic Packages †

Abstract

1. Introduction

- providing an exhaustive picture of the TRIC features;

- reporting and discussing a larger number of results, including those obtained for the newly included package families (eQFN-mr and PowerSSO);

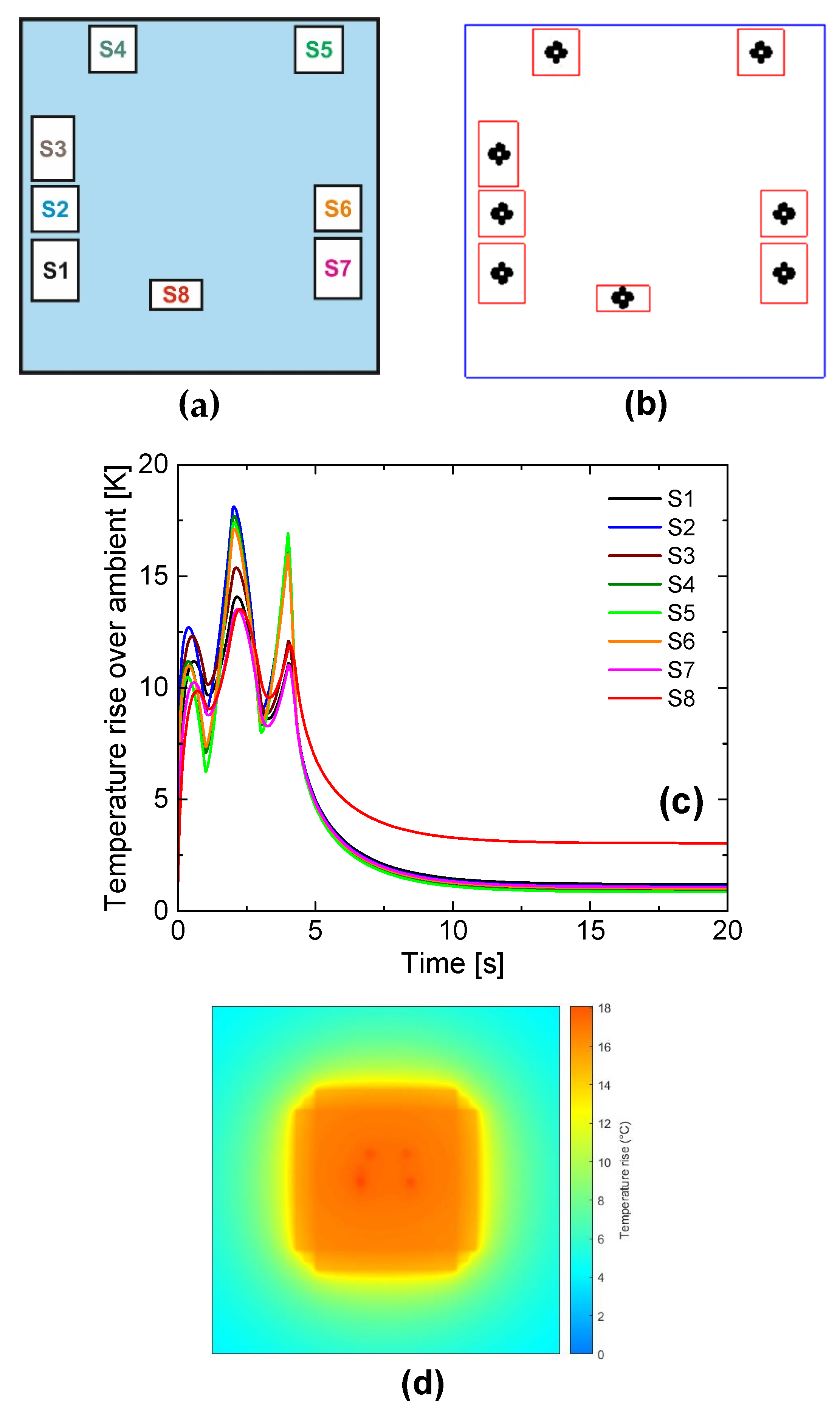

- showing a simulated temperature map at a chosen time instant for a multi-source case of practical relevance.

2. TRIC Features

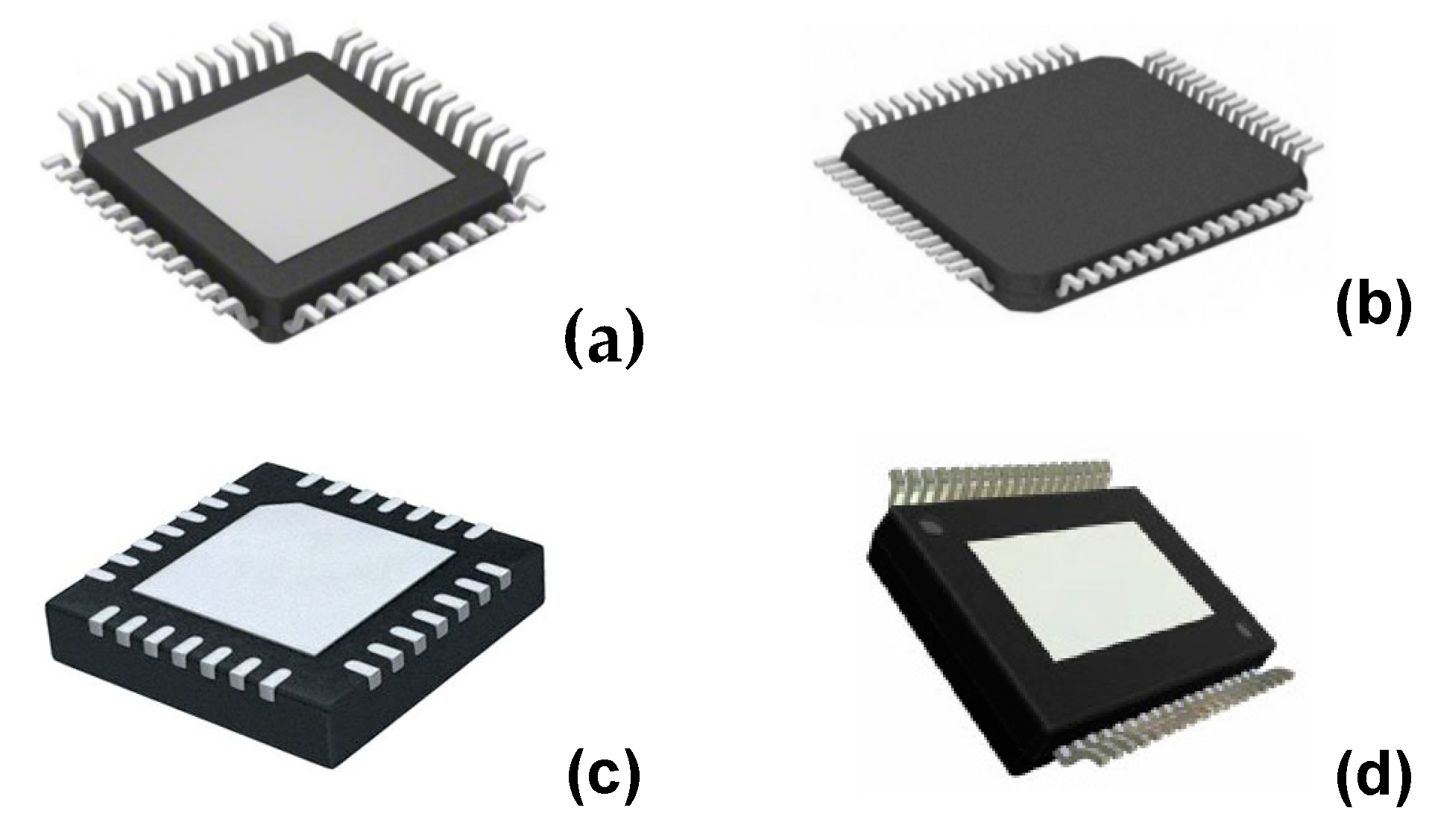

- eQFPs, which are surface mount integrated circuit packages with a flat rectangular body, and leads extending from all the four sides. In particular, both the eLQFP and eTQFP variants are available, which differ in terms of body thickness (1.4 and 1 mm, respectively). The square epad structure, which is a standard lead frame wherein the die pad is depressed down to the package bottom face, represents a valuable solution to ease the heat dissipation from die to board. The horizontal size of the body can be 7 × 7, 10 × 10, 14 × 14, 20 × 20, 24 × 24 mm2, the total number of leads can be 32, 48, 64, 80, 100, 128, 144, 176, 216 for both variants; several sizes for the epad are available, which span from 3.5 × 3.5 to 9 × 9 mm2. Various types of glue for die attach can be selected. The die thickness can amount to 100, 280, 375 (used in the simulations shown in Section 4), and 580 µm (the latter value for the eLQFPs only), while any technologically-reasonable horizontal size can be chosen. It is worth noting that only parameter sets corresponding to real packages fabricated by STMicroelectronics can be selected, whereas all other combinations are obviously not possible; examples are: the 10 × 10 mm2 eTQFP with 80 leads can be equipped only with an epad with sizes 3.5 × 3.5, 5.4 × 5.4, 6.2 × 6.2 mm2; many sizes are instead possible for the epad in the 14 × 14 mm2 eLQFPs with 100 leads, namely, 3.5 × 3.5, 4.5 × 4.5, 6.0 × 6.0, 7.2 × 7.2, 7.6 × 7.6, 8.5 × 8.5 mm2; 32, 40, and 48 leads are available only for the 7 × 7 mm2 eLQFP.

- pLQFPs, where, contrary to the eLQFP counterparts, the mold covers the entire package surface, so that the metal base of the lead frame is not “exposed” and thus not visible from the package bottom. With a few exceptions, all the parameter sets already reported for the eLQFPs are possible.

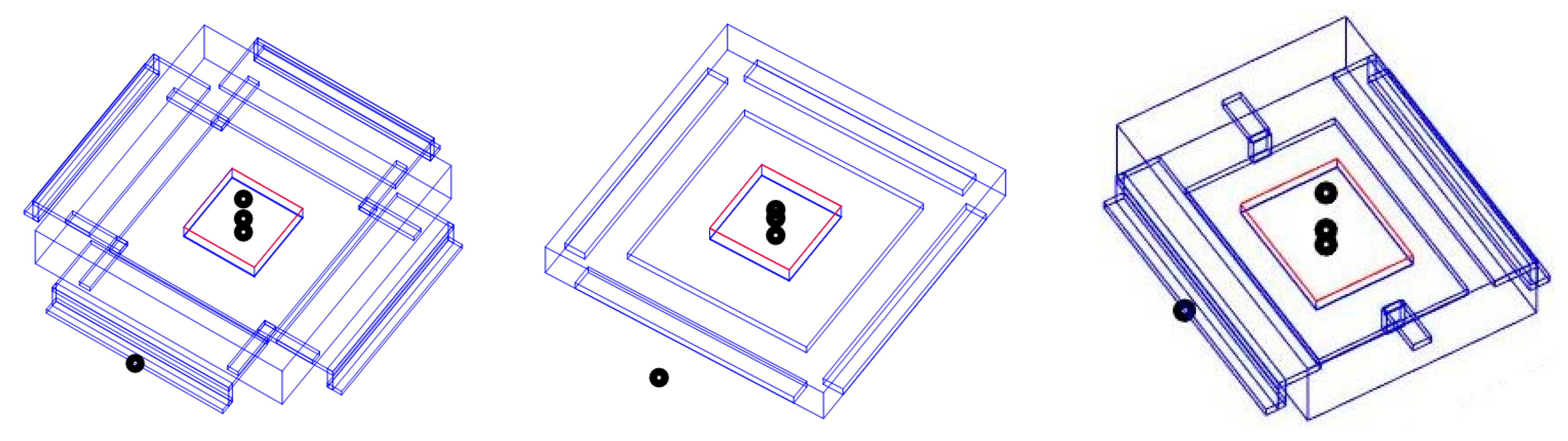

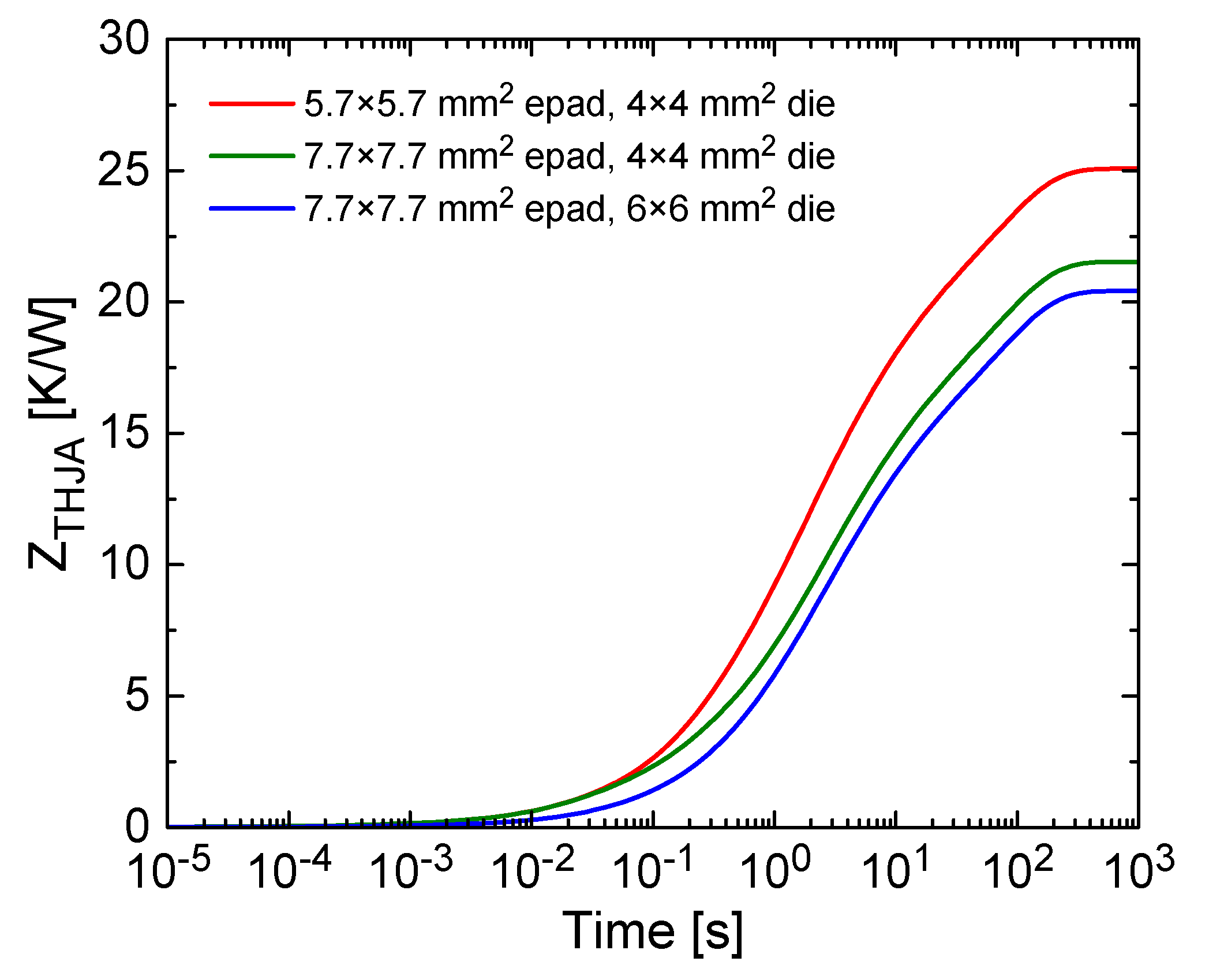

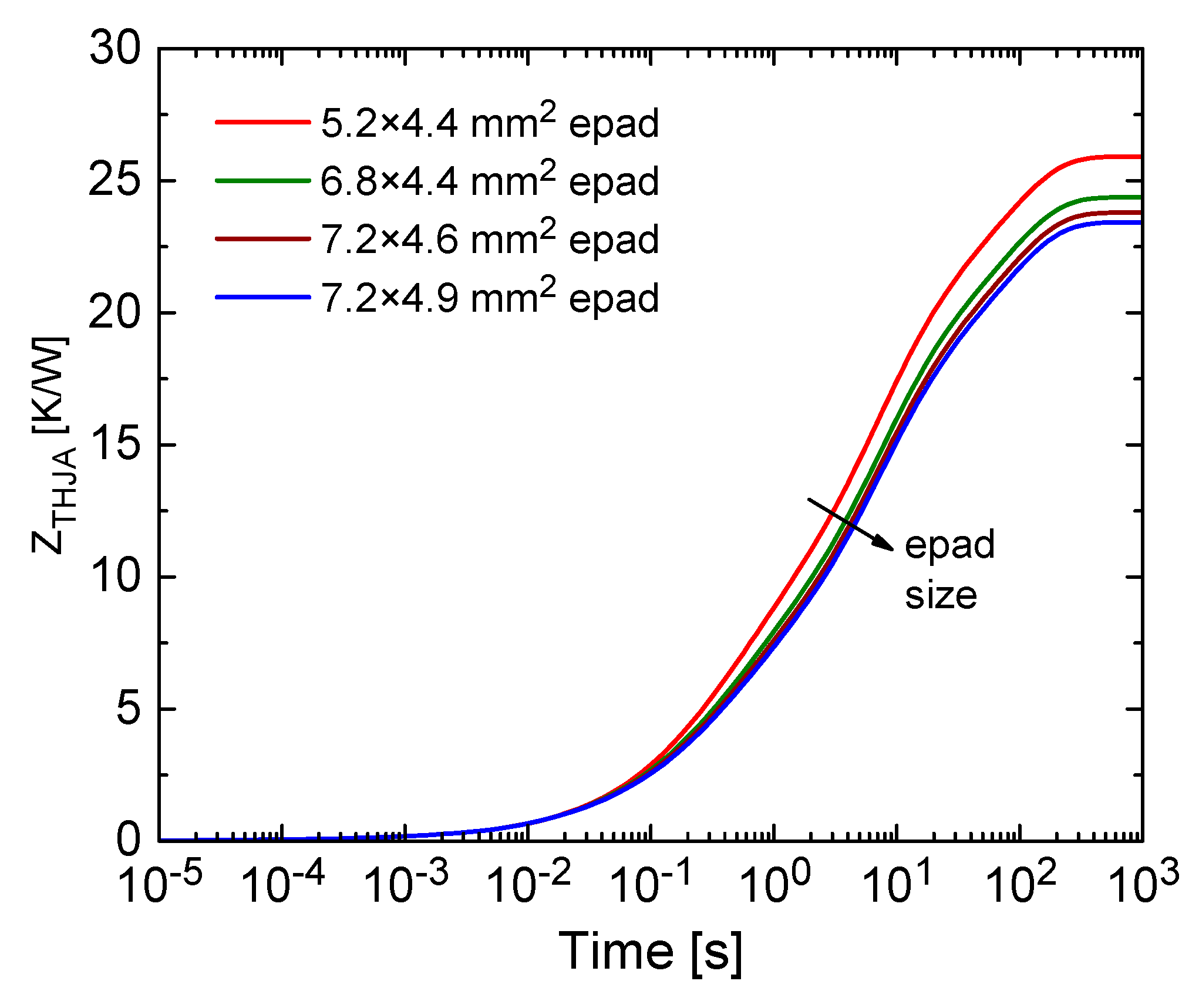

- eQFN packages, which are lead-less flat molded structures built with a metal lead-frame manufactured by etching, and represent a popular cost-effective and high-performance packaging solution by virtue of the lower inductance than in leaded packages. Several horizontal sizes of the square package body are available, spanning from 2 × 2 to 15 × 15 mm2, while the thickness can be equal to 0.55, 0.75, and 0.9 mm (the latter being adopted for the simulations in Section 4). The horizontal sizes of epad and die can be arbitrarily chosen in the ranges allowed by the design rules. Various types of die attach can be selected. Specimens of this family can be equipped with a single row of pins (single-row QFN) or with multiple rows of pins (eQFN-mr), this option being not available in the former TRIC version.

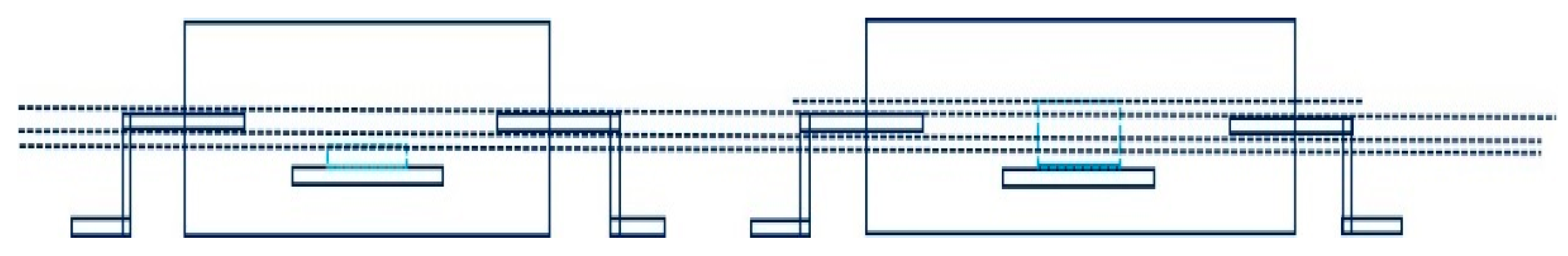

- PowerSSO packages, which are derived from the well-known Small Outline (SO) family and benefit from footprint and height 30%–50% smaller than a conventional dual in-line package. More specifically, epad PowerSSO structures are considered, which are conceived to favor the heat removal without extra cost penalty. Many packages belonging to the PowerSSO family have been included, namely (i) PowerSSO-12, PowerSSO-14, and PowerSSO-16, all sharing a 4.9 × 3.9 × 1.5 mm3 body and equipped with 12 leads (the lead pitch being 0.8 mm), 14 leads (0.65 mm), and 16 leads (0.5 mm), respectively; (ii) PowerSSO-24, PowerSSO-28, and PowerSSO-36, all sharing a 7.5 × 10.3 × 2.3 mm3 body, and equipped with 24 leads (the lead pitch being 0.8 mm), 28 leads (0.65 mm), and 36 leads (0.5 mm), respectively. PowerSSO packages were not covered by the first TRIC release.

3. TRIC Solution Algorithm

| Algorithm 1: Extraction of Projection Basis. | |

| 1 | form = 1, ... , M do |

| for each σ do | |

| pick a random value p in P | |

| set | |

| set space Sm(σ): = | |

| set ρ: = +∞ (norm of the residual) | |

| while ρ > ε do | |

| 2 | solve (2) for using as initial guess |

| 3 | add to space Sm(σ) |

| for Ξ times do | |

| pick a random value p in P | |

| apply Algorithm 2 | |

| 4 | compute residual ρ of (2) for |

| if ρ > ε do | |

| break | |

| Algorithm 2: Performing Projection. | |

| 1 | set V: = |

| for each element (q,Θ) of Sm(σ) do | |

| transform into | |

| set V: = | |

| 2 | project (3) onto the space spanned by columns of V |

| 3 | solve (4) determining as an approximation of |

| Algorithm 3: Performing Projection |

| set space S(p):= |

| form = 1, ... , M do |

| for each σ do |

| apply Algorithm 2 |

| add to space S(p) |

4. Numerical Results

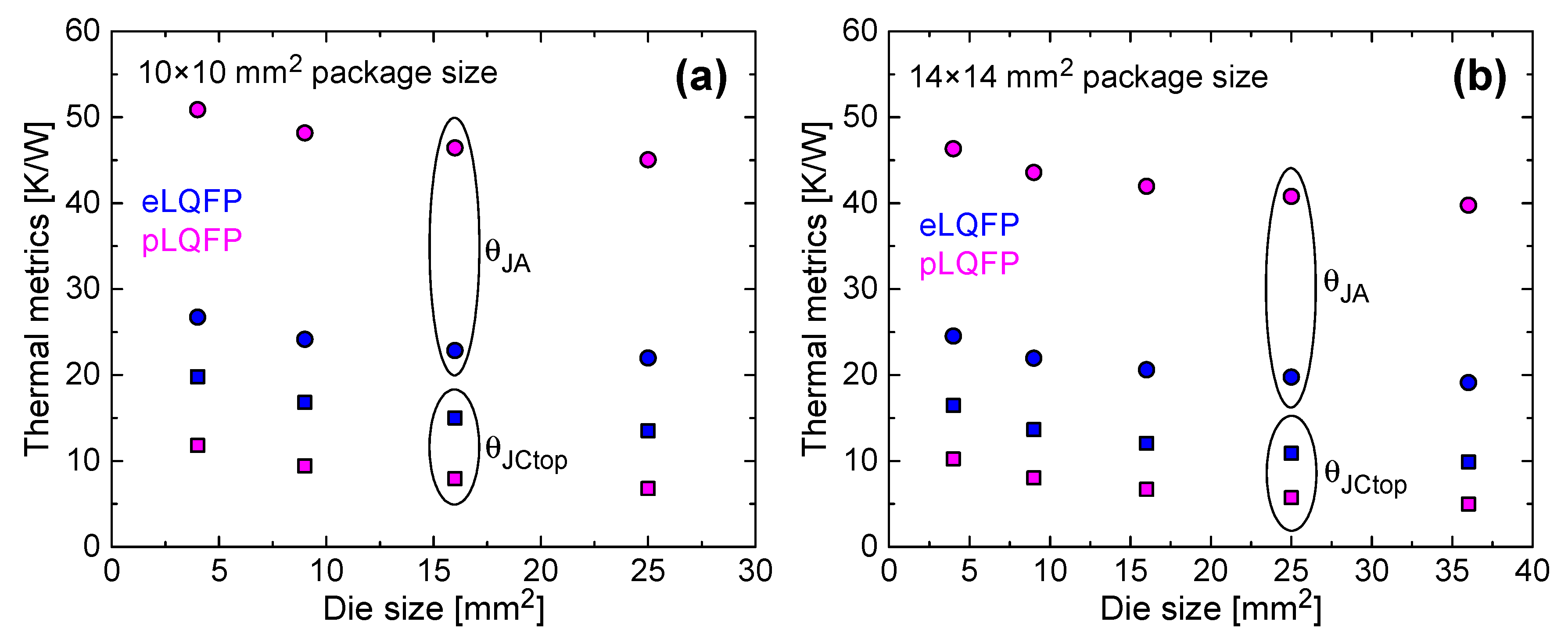

4.1. Full-Plastic LQFP vs. Epad LQFP

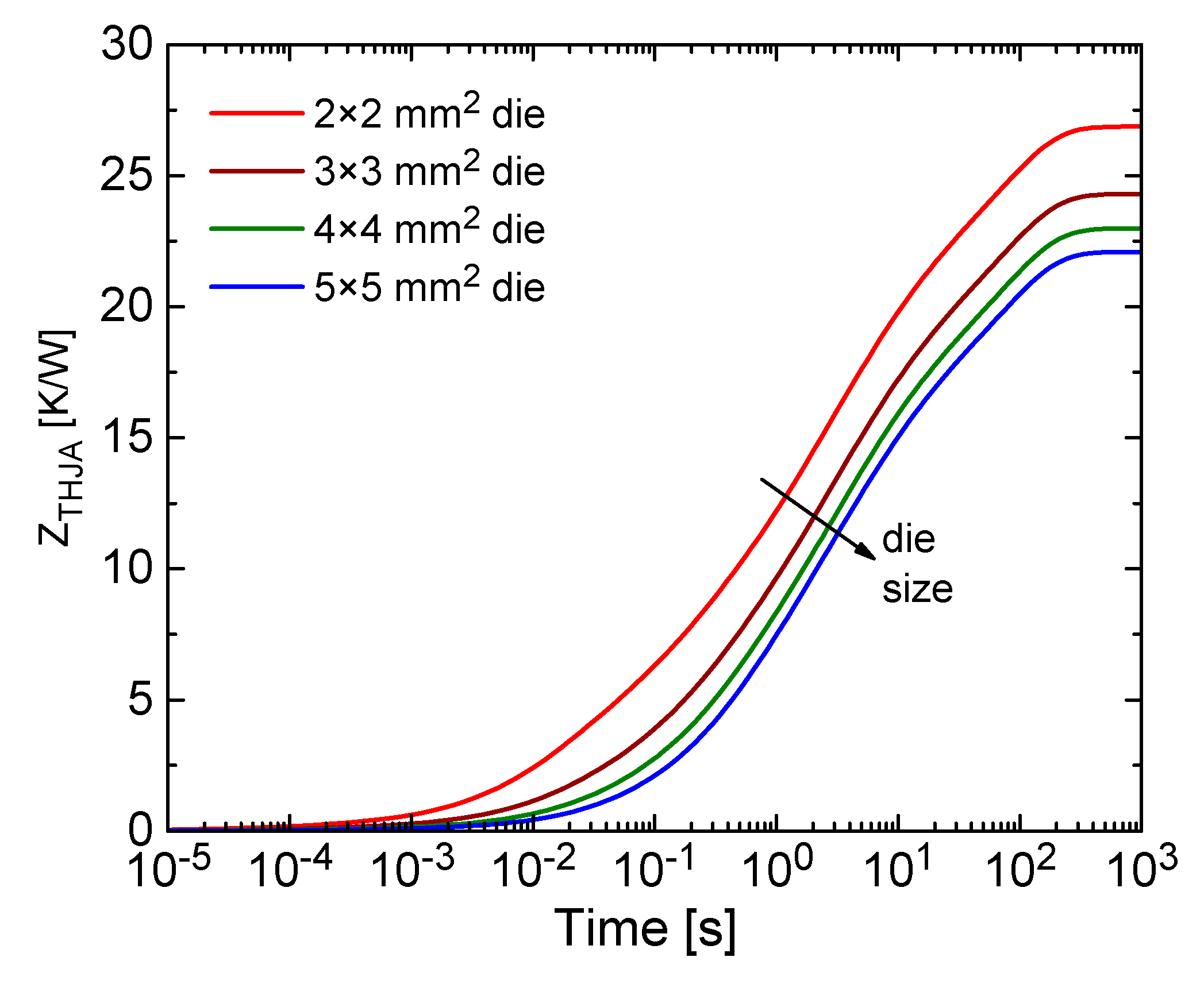

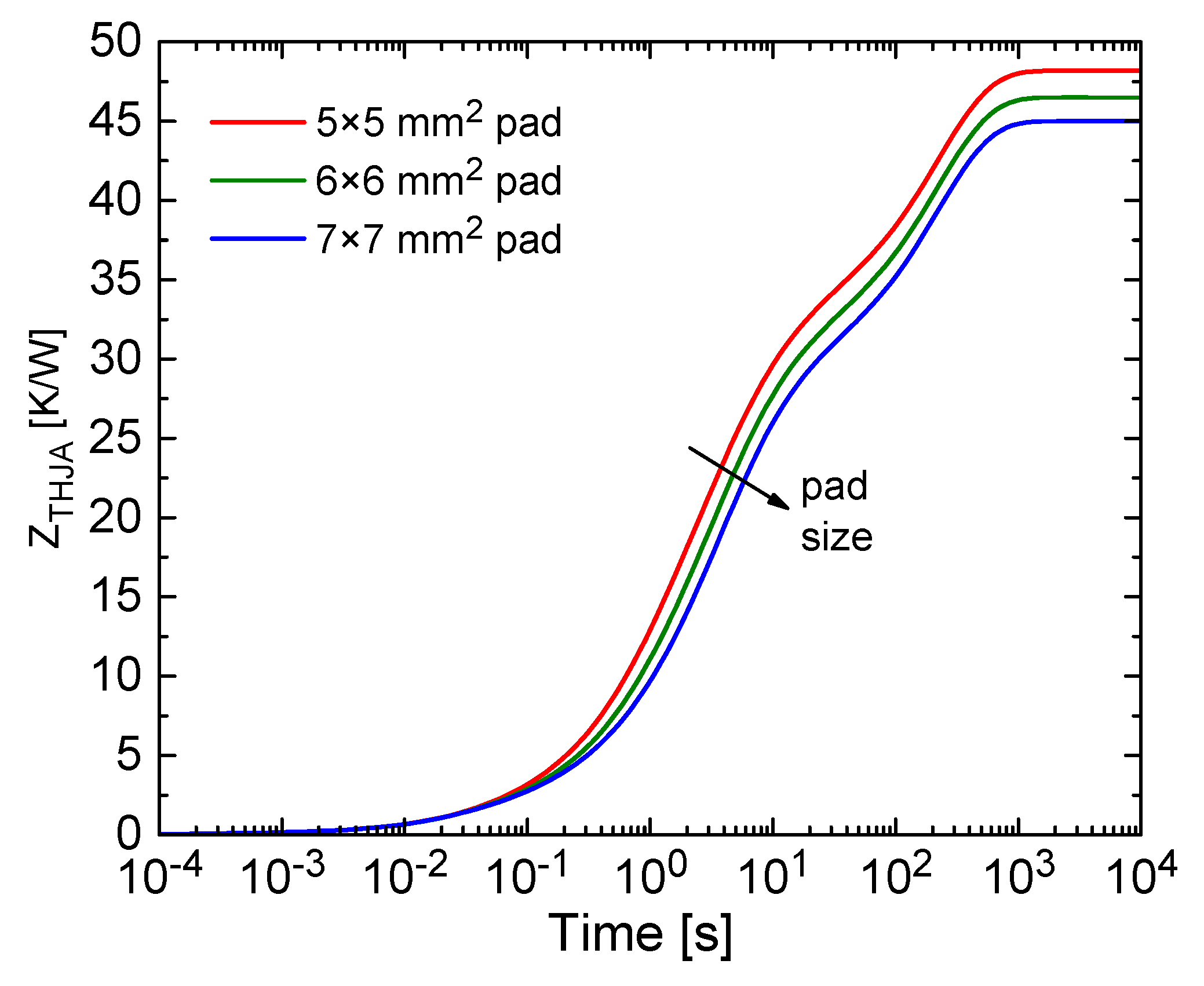

4.2. Thermal Impedances

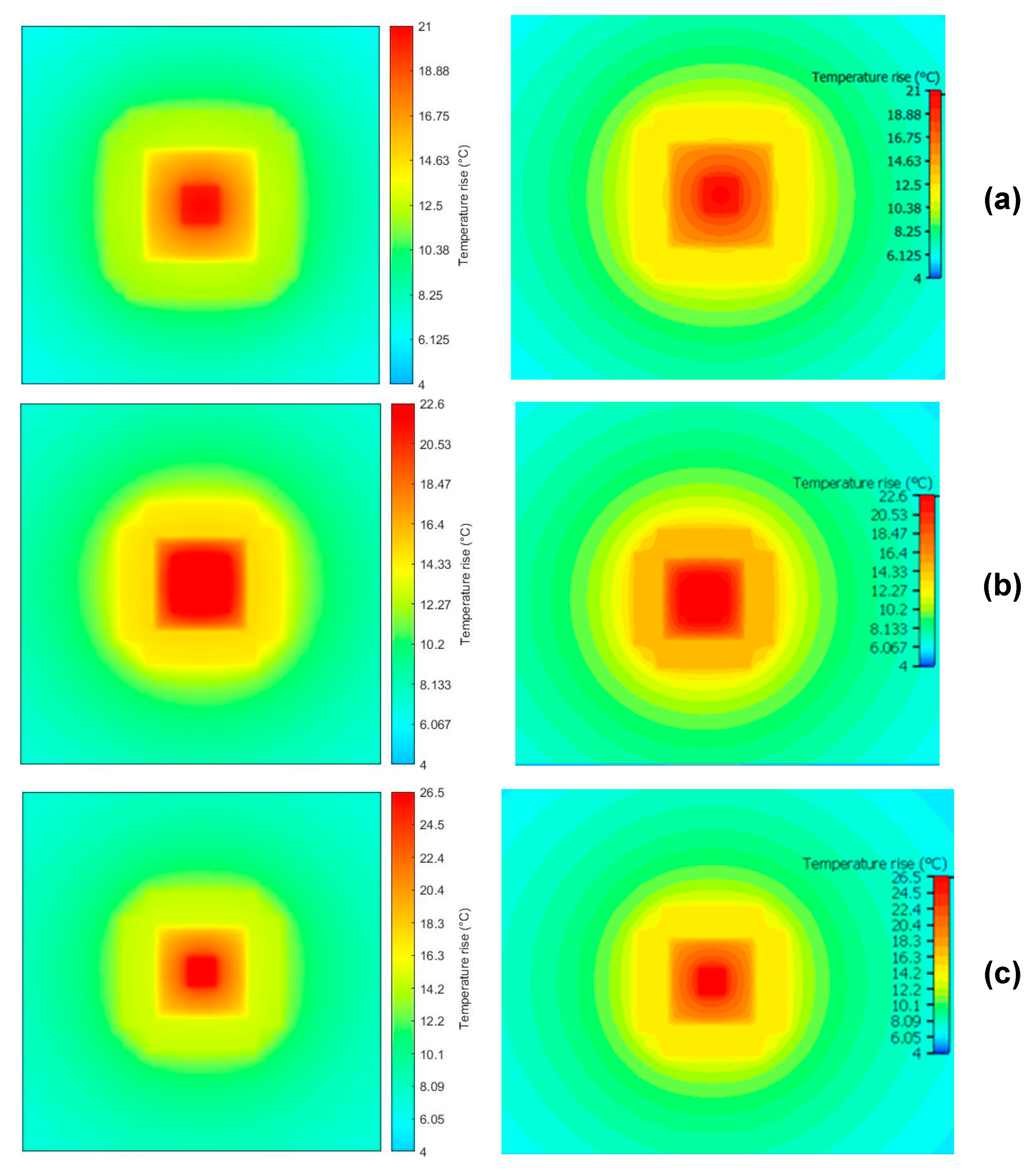

4.3. Comparison with FloTHERM

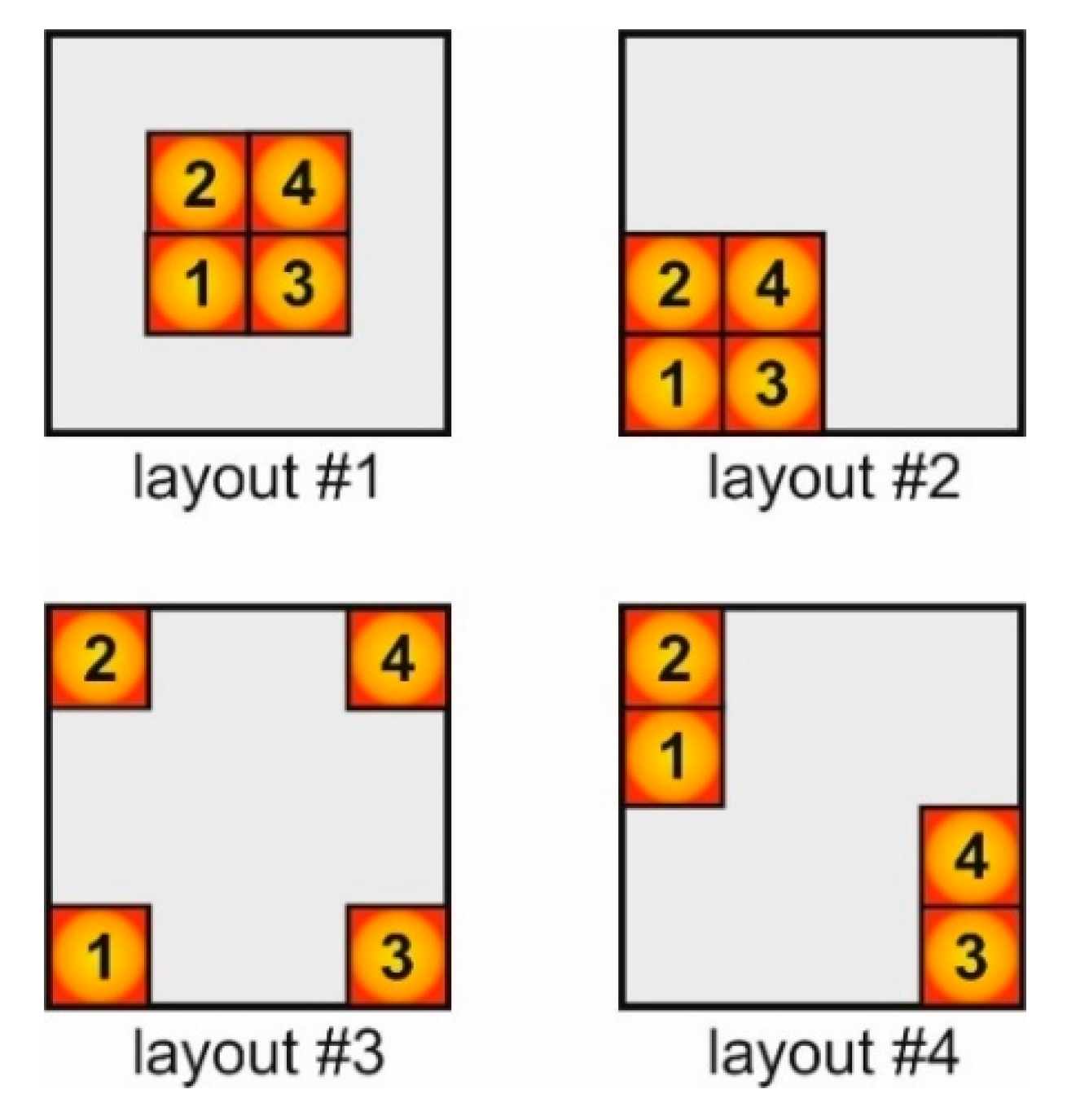

4.4. Multi-Source Analysis

4.5. ABS Source Profile

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

Nomenclature

| TRIC | Thermal Resistance and Impedance Calculator |

| TRAC | Thermal Resistance Advanced Calculator |

| JEDEC | Joint Electron Device Engineering Council |

| thermal resistance (K/W) | temperature increase over a reference temperature taken over a point (or a region) of interest of the component under test, and normalized to the dissipated power; it is a property depending upon geometry and material parameters, and can be reviewed as an indicator of the heat dissipation inaptitude of the component |

| thermal impedance (K/W) | thermal resistance vs. time resulting from the application of a constant power step |

| ϑJA (K/W) | junction-to-ambient thermal resistance |

| ΨJB (K/W) | thermal characterization parameter to report the difference between junction temperature and the temperature of the board measured at the top surface of the board |

| ΨJCtop (K/W) | thermal characterization parameter to report the difference between junction temperature and the temperature at the top center of the outside surface of the component package |

| ϑJB (K/W) | junction-to-board thermal resistance |

| ϑJCtop (K/W) | junction-to-case top thermal resistance |

| ϑJCbottom (K/W) | junction-to-case bottom thermal resistance |

| ZTHJA (K/W) | junction-to-ambient thermal impedance |

| BC | boundary condition |

| BCI | boundary condition independent |

| MOR | model-order reduction |

| CTM | compact thermal model |

| DTM | detailed thermal model |

| pDTM | parametric DTM |

| FV | finite volume |

| DoF | degree of freedom |

| HS | heat source |

| CPU | central processing unit |

| epad | exposed pad |

| QFP | quad flat package |

| eLQFP | exposed-pad low-profile (thick) QFP |

| eTQFP | exposed-pad thin QFP |

| pLQFP | full-plastic low-profile (thick) QFP |

| QFN | quad flat no-leads package |

| eQFN | exposed-pad QFN |

| eQFN-mr | multi-row eQFN |

| PowerSSO | package belonging to the Small Outline family |

| ABS | antilock braking system |

References

- Smy, T.; Walkey, D.; Dew, S.K. A 3D thermal simulation tool for integrated devices-Atar. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2001, 20, 105–115. [Google Scholar] [CrossRef]

- Huang, W.T.; Ghosh, S.; Sankaranarayanan, K.; Skadron, K.; Stan, M.R. Hotspot: Thermal modeling for CMOS VLSI systems. IEEE Trans. Large Scale Integr. VLSI Syst. 2006, 14, 501–513. [Google Scholar] [CrossRef]

- Ziabari, A.; Park, J.H.; Ardestani, E.K.; Renau, J.; Kang, S.M.; Shakouri, A. Power blurring: Fast static and transient thermal analysis method for packaged integrated circuits and power devices. IEEE Trans. Large Scale Integr. VLSI Syst. 2014, 22, 2366–2379. [Google Scholar] [CrossRef]

- Bar-Cohen, A.; Elperin, T.; Eliasi, R. ϑJC characterization of chip packages – justification, limitations, and future. IEEE Trans. Compon. Hybrids Manuf. Technol. 1989, 12, 724–731. [Google Scholar] [CrossRef]

- Lasance, C.J.M.; Vinke, H.; Rosten, H. Thermal characterization of electronic devices with boundary condition independent compact models. IEEE Trans. Compon. Packag. Manuf. Technol. Part A 1995, 18, 723–731. [Google Scholar] [CrossRef]

- Pape, H.; Schweitzer, D.; Janssen, J.H.J.; Morelli, A.; Villa, C.M. Thermal transient modeling and experimental validation in the European project PROFIT. IEEE Trans. Compon. Packag. Technol. 2004, 27, 530–538. [Google Scholar] [CrossRef]

- Sabry, M.N. Flexible profile compact thermal models for practical geometries. J. Electr. Packag. 2007, 129, 256–259. [Google Scholar] [CrossRef]

- Lasance, C.J.M. Ten years of boundary-condition-independent compact thermal modeling of electronic parts: A review. Heat Transf. Eng. 2008, 29, 149–169. [Google Scholar] [CrossRef]

- JESD51-12. Guidelines for Reporting and Using Electronic Package Thermal Information; JEDEC: Arlington, VA, USA, May 2005. [Google Scholar]

- Codecasa, L.; Race, S.; d’Alessandro, V.; Gualandris, D.; Morelli, A.; Villa, C.M. Thermal resistance advanced calculator (TRAC). In Proceedings of the International Workshop on THERMal INvestigation of ICs and Systems (THERMINIC), Stockholm, Sweden, 26–28 September 2018. [Google Scholar]

- Codecasa, L.; Race, S.; d’Alessandro, V.; Gualandris, D.; Morelli, A.; Villa, C.M. TRAC: A thermal resistance advanced calculator for electronic packages. Energies 2019, 12, 1050. [Google Scholar] [CrossRef]

- Codecasa, L.; D’Amore, D.; Maffezzoni, P. Modeling the thermal response of semiconductor devices through equivalent electrical networks. IEEE Trans. Circuits Syst. I Fundam. Theory Appl. 2002, 49, 1187–1197. [Google Scholar] [CrossRef]

- Codecasa, L.; D’Amore, D.; Maffezzoni, P. Compact modeling of electrical devices for electrothermal analysis. IEEE Trans. Circuits Syst. I Fundam. Theory Appl. 2003, 50, 465–476. [Google Scholar] [CrossRef]

- Codecasa, L.; D’Amore, D.; Maffezzoni, P. Multipoint moment matching reduction from port responses of dynamic thermal networks. IEEE Trans. Compon. Packag. Technol. 2005, 28, 605–614. [Google Scholar] [CrossRef]

- Codecasa, L.; d’Alessandro, V.; Magnani, A.; Rinaldi, N.; Zampardi, P.J. FAst novel thermal analysis simulation tool for integrated circuits (FANTASTIC). In Proceedings of the International Workshop on THERMal INvestigation of ICs and systems (THERMINIC), London, UK, 24–26 September 2014. [Google Scholar]

- Codecasa, L.; d’Alessandro, V.; Magnani, A.; Rinaldi, N. Parametric compact thermal models by moment matching for variable geometry. In Proceedings of the International Workshop on THERMal INvestigation of ICs and systems (THERMINIC), London, UK, 24–26 September 2014. [Google Scholar]

- Magnani, A.; d’Alessandro, V.; Codecasa, L.; Zampardi, P.J.; Moser, B.; Rinaldi, N. Analysis of the influence of layout and technology parameters on the thermal impedance of GaAs HBT/BiFET using a highly-efficient tool. In Proceedings of the IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS), La Jolla, CA, USA, 19–22 October 2014. [Google Scholar]

- Codecasa, L.; d’Alessandro, V.; Magnani, A.; Rinaldi, N. Matrix reduction tool for creating boundary condition independent dynamic compact thermal models. In Proceedings of the International Workshop on THERMal INvestigation of ICs and Systems (THERMINIC), Paris, France, 30 September–2 October 2015. [Google Scholar]

- Janssen, J.H.J.; Codecasa, L. Why matrix reduction is better than objective function based optimization in compact thermal model creation. In Proceedings of the International Workshop on THERMal Investigation of ICs and Systems (THERMINIC), Paris, France, 30 September–2 October 2015. [Google Scholar]

- Codecasa, L.; d’Alessandro, V.; Magnani, A.; Rinaldi, N. Structure preserving approach to parametric dynamic compact thermal models of nonlinear heat conduction. In Proceedings of the International Workshop on THERMal INvestigation of ICs and Systems (THERMINIC), Paris, France, 30 September–2 October 2015. [Google Scholar]

- Codecasa, L.; d’Alessandro, V.; Magnani, A.; Irace, A. Circuit-based electrothermal simulation of power devices by an ultrafast nonlinear MOS approach. IEEE Trans. Power Electron. 2016, 31, 5906–5916. [Google Scholar] [CrossRef]

- Rogié, B.; Codecasa, L.; Monier-Vinard, E.; Bissuel, V.; Laraqi, N.; Daniel, O.; D’Amore, D.; Magnani, A.; d’Alessandro, V.; Rinaldi, N. Delphi-like dynamical compact thermal models using model order reduction. In Proceedings of the International Workshop on THERMal INvestigation of ICs and Systems (THERMINIC), Amsterdam, The Netherlands, 27–29 September 2017. (best paper award). [Google Scholar]

- Codecasa, L.; d’Alessandro, V.; Magnani, A.; Rinaldi, N. Novel approach for the extraction of nonlinear compact thermal models. In Proceedings of the International Workshop on THERMal INvestigation of ICs and systems (THERMINIC), Amsterdam, The Netherlands, 27–29 September 2017. [Google Scholar]

- Codecasa, L.; De Viti, F.; Race, S.; d’Alessandro, V.; Gualandris, D.; Morelli, A.; Villa, C.M. Thermal Resistance and Impedance Calculator (TRIC). In Proceedings of the International Workshop on THERMal INvestigation of ICs and Systems (THERMINIC), Lecco, Italy, 25–27 September 2019. [Google Scholar]

- FloTHERM® v12.2. User’s Guide; Mentor Graphics: Wilsonville, OR, USA, 2018. [Google Scholar]

| ΔT1 | ΔT2 | ΔT3 | ΔT4 | ΔTcenter | ΔTmax | |

|---|---|---|---|---|---|---|

| Layout #1 | 56.31 | 56.31 | 56.31 | 56.31 | 57.06 | 57.06 |

| Layout #2 | 59.56 | 58.20 | 58.20 | 57.05 | 54.13 | 59.58 |

| Layout #3 | 54.89 | 54.89 | 54.89 | 54.89 | 52.25 | 55.15 |

| Layout #4 | 55.77 | 56.12 | 56.12 | 55.77 | 52.70 | 56.35 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Codecasa, L.; De Viti, F.; d’Alessandro, V.; Gualandris, D.; Morelli, A.; Villa, C.M. TRIC: A Thermal Resistance and Impedance Calculator for Electronic Packages. Energies 2020, 13, 2252. https://doi.org/10.3390/en13092252

Codecasa L, De Viti F, d’Alessandro V, Gualandris D, Morelli A, Villa CM. TRIC: A Thermal Resistance and Impedance Calculator for Electronic Packages. Energies. 2020; 13(9):2252. https://doi.org/10.3390/en13092252

Chicago/Turabian StyleCodecasa, Lorenzo, Francesca De Viti, Vincenzo d’Alessandro, Donata Gualandris, Arianna Morelli, and Claudio Maria Villa. 2020. "TRIC: A Thermal Resistance and Impedance Calculator for Electronic Packages" Energies 13, no. 9: 2252. https://doi.org/10.3390/en13092252

APA StyleCodecasa, L., De Viti, F., d’Alessandro, V., Gualandris, D., Morelli, A., & Villa, C. M. (2020). TRIC: A Thermal Resistance and Impedance Calculator for Electronic Packages. Energies, 13(9), 2252. https://doi.org/10.3390/en13092252