1. Introduction

Recently, with new technologies such as smart grid and DC distribution, SST have emerged. SST connects directly to the grid instead of the traditional transformers to perform a variety of roles such as power factor correction and DC distribution. Therefore, SST should be able to cope with the high voltage of the grid, so that the various studies can be conducted [

1,

2,

3,

4,

5,

6,

7,

8]. To cope with high voltage, a multi-module converter (MMC) or a series-connected switching devices method has been studied.

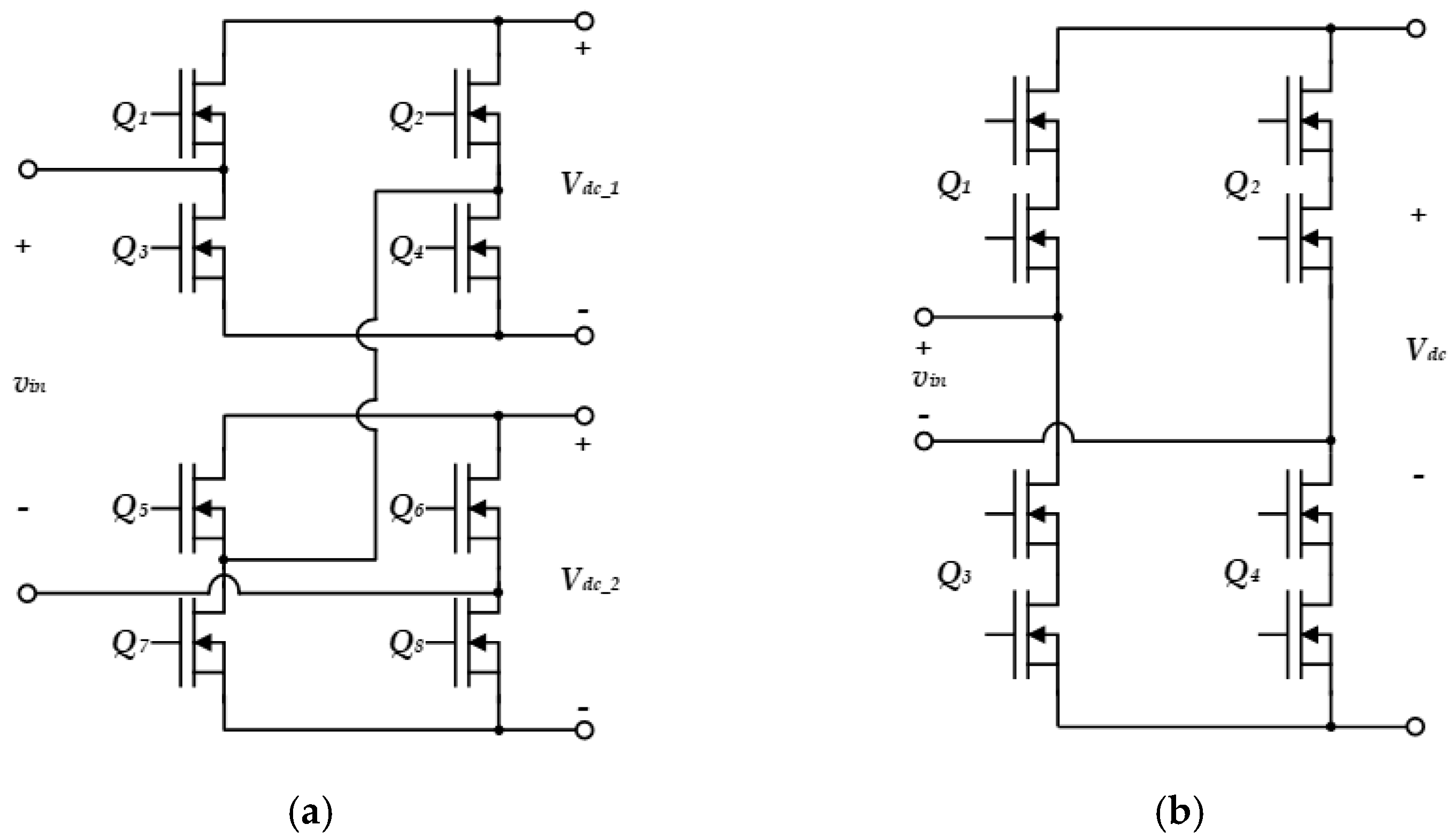

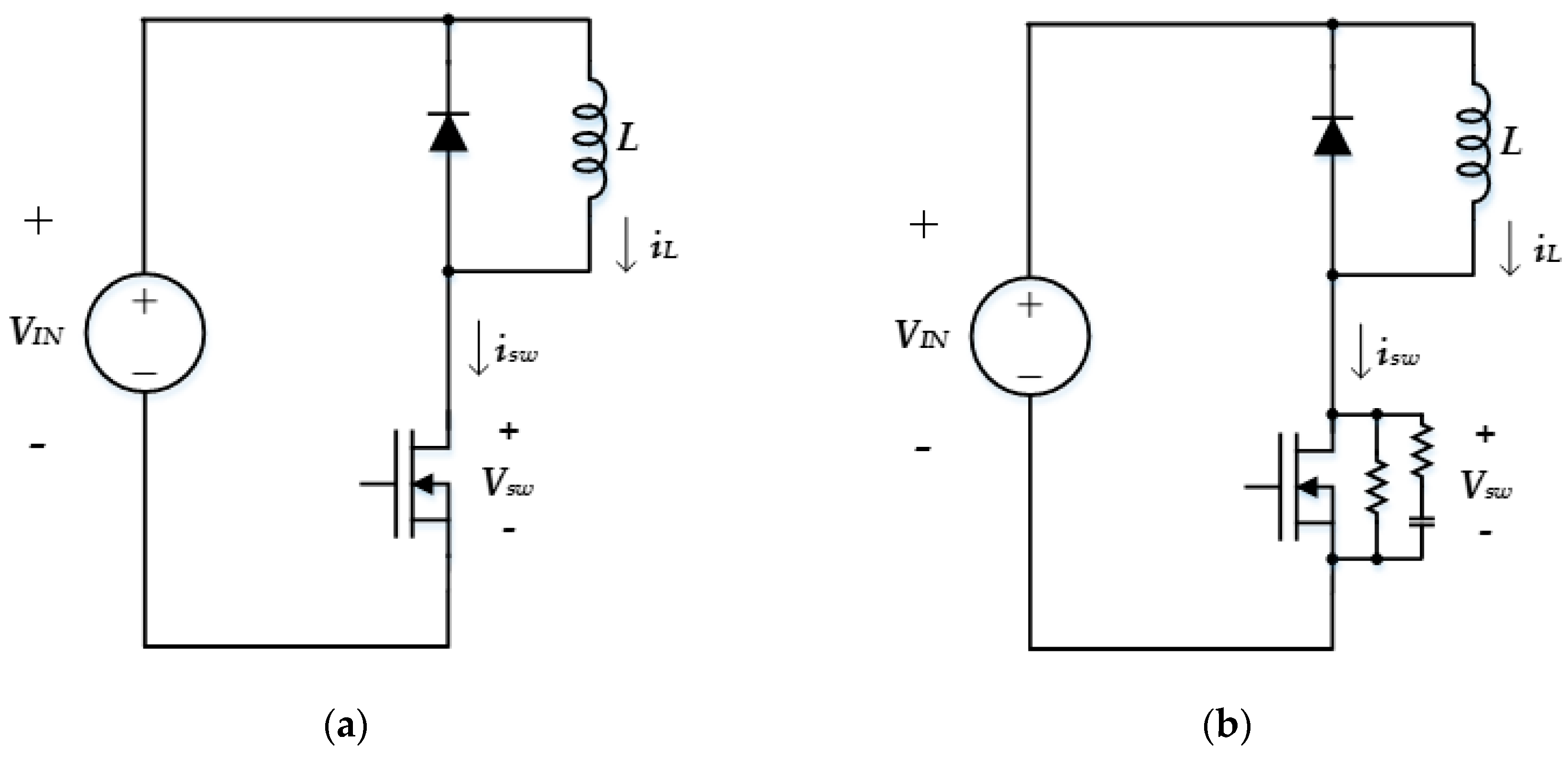

Figure 1 shows the difference between MMC and the series-connected device method.

MMC is a structure that increases the front of the circuit by stacking the circuit in series, which is relatively easy to expand, and has the advantage of reducing filter size by increasing the Power Conversion System (PCS) voltage level. But, since there is a separated DC link voltage, it is necessary to control and balance the separated DC link voltage. In addition, all individual devices should be controlled as the number of modules increases, which requires a digital computing device with many Pulse Width Modulation (PWM) channels. On the other hand, the series-connected devices behave like a single device, so even if many devices are connected in series, no digital computing device with many PWM channels is required. Furthermore, due to the series-connected devices, PCS does not have the separated DC link voltage. No additional control method is needed for DC link voltage balancing. On the other hand, because the output voltage level of series-connected devices based on PCS decreases, the filter size is larger than the MMC method. In addition, there is an issue with a switch voltage imbalance between the series-connected switches.

According to References [

9,

10,

11,

12,

13,

14,

15,

16], there are various reasons for causing a voltage imbalance. The first reason is the error of the gate driver. The gate driver is composed of various passive components and semiconductor devices like Negative, Positive, Negative (NPN) and Positive, Negative, Positive (PNP) transistors. Errors in devices of the gate driver cause an unbalance in the gate signal, which causes an imbalance in the voltage across the series-connected devices. The second reason is the error of parasitic components of the device itself. The error of the output capacitor of devices affects the switching speed and causes a voltage imbalance. The third reason is the parasitic capacitor from gate to ground of each device.

To solve voltage imbalance, various studies have been conducted [

9,

10,

11,

12,

13,

14,

15,

16]. In Reference [

9], Active Gate Driver using Field Programmable Gate Array (FPGA) with RCD (Resistor, Capacitor and Diode) snubbers across each device method for balancing was proposed and tested. In the documents, the three-phase half-bridge inverter was built in 12-series connected Insulated Gage Bipolar Transistor (IGBT) and verified at a rated current within

10 kV DC-link. In Reference [

12], an active gate driver using a current mirror with a steady-state balancing resistor was proposed and performed. The steady-state voltage imbalance is reduced by the balancing resistor, and the transient imbalance was solved by the analog gate controller used a current mirror. In Reference [

14], the voltage balancing method with only passive components using a single gate driver unit was proposed. In the documents, experimental verifications were applied to the DC circuit breaker with a 1.2 kV bus voltage. It was confirmed that it is possible to cope with the high voltage system by using a series connection element applied to various methods.

In a high voltage system, like SST, isolated converters are needed to increase the stability of the system and grid. Isolated converters are one of the necessary converters for SST regardless of MMC or series-connected devices. There are many types of isolated converters such as Dual-Active-Bridge (DAB), Quad-Active-Bridge (QAB), and LLC Converter. A fixed-frequency resonant converter conducts zero voltage switching (ZVS) over a wide frequency range and provides the advantages of high efficiency and high-power density.

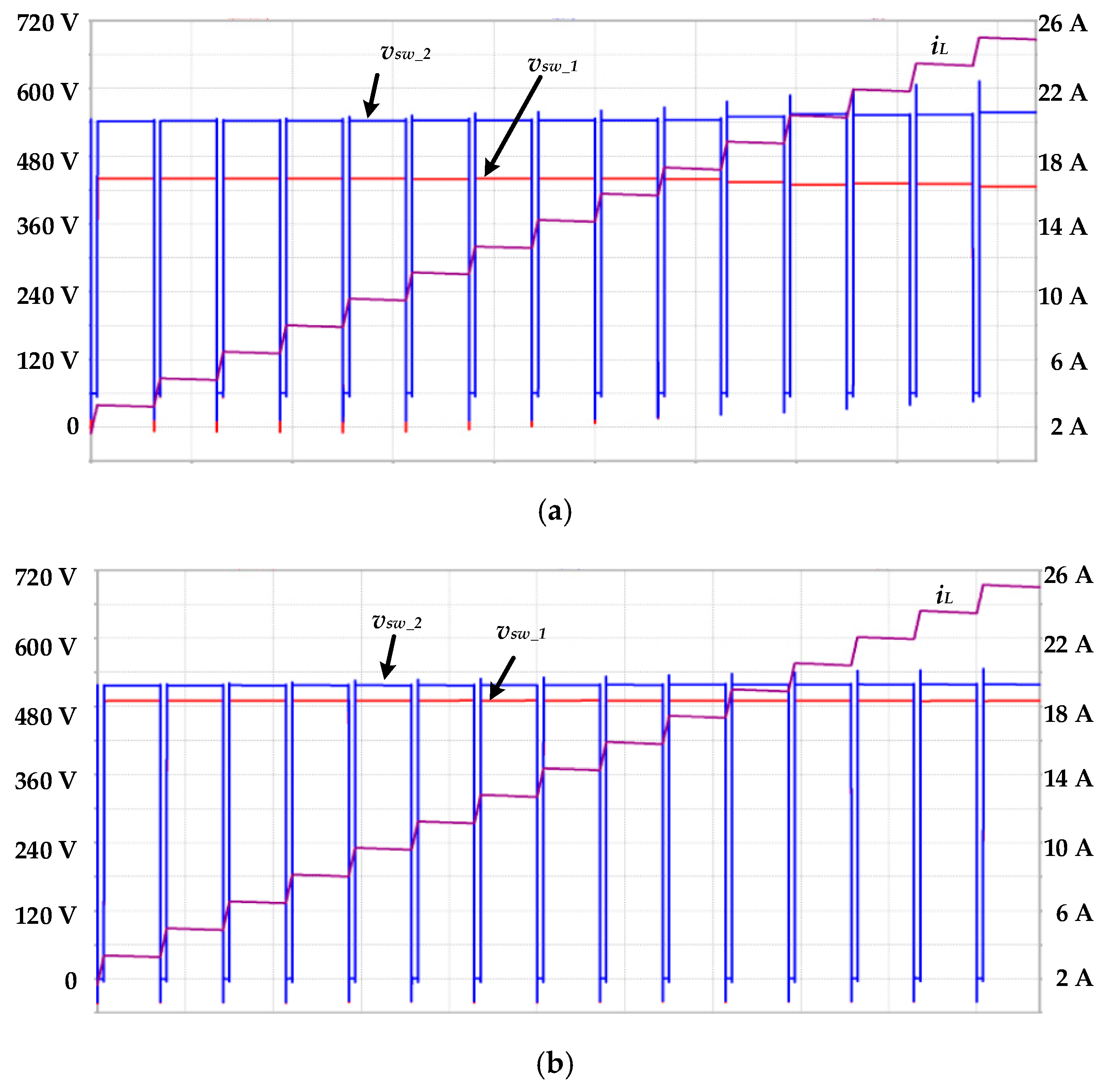

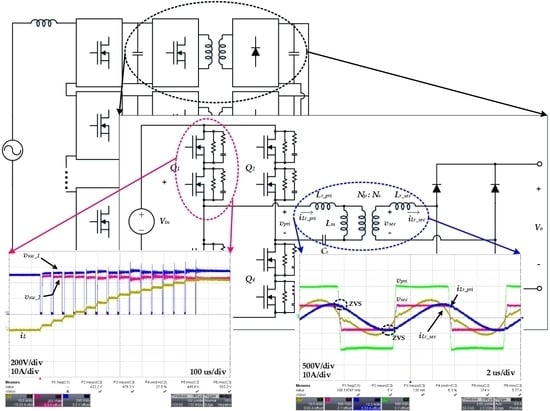

In this paper, fixed-frequency LLC resonant converter-based series-connected devices is proposed. In order to cope with a high voltage, a series-connected device based on PCS was applied and an R-C snubber was applied to solve the voltage imbalance between series-connected devices. In conclusion, this paper examined the effect of R-C snubber applied to the LLC converter to solve the voltage imbalance. The proposed converter consists of a full-bridge inverter. Unlike the usual full-bridge converter, the proposed converter consists of eight devices, as shown in

Figure 1b. The operation of the SCDLLC converter with a balancing circuit is described. This paper is structured as follows. In

Section 2, imbalance factors of series-connected devices are described and a balancing method using passive elements is expressed. In

Section 3, a configuration method of the LLC converter considering series-connected devices is explained. In

Section 4 and

Section 5, a 3-kW prototype model is manufactured to verify the usefulness of the proposed system and the simulations and experiments are performed. Lastly, in

Section 6, we discuss experimental results and conclude the paper.

2. Design of Series-Connected Devices Balancing Circuit

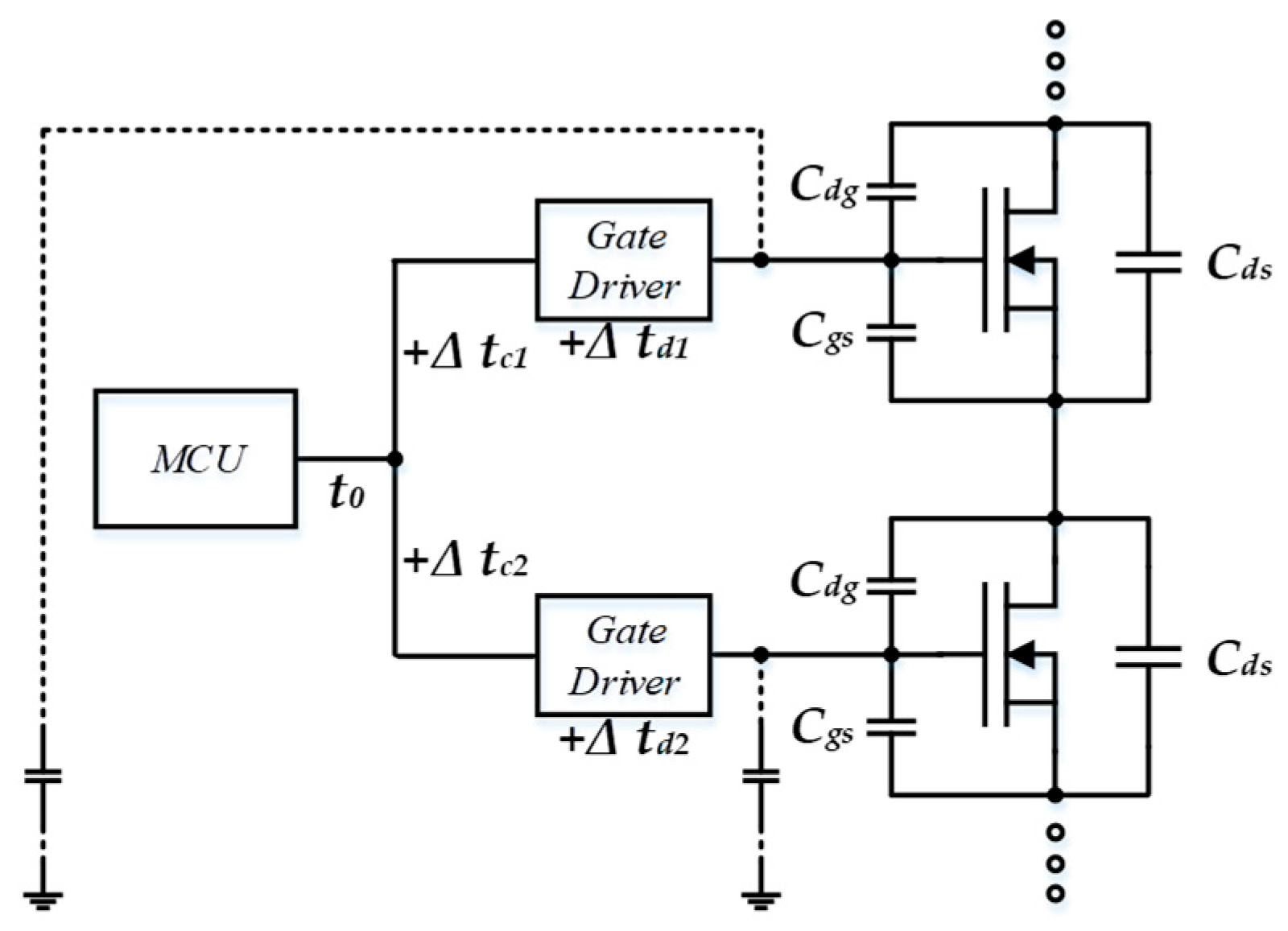

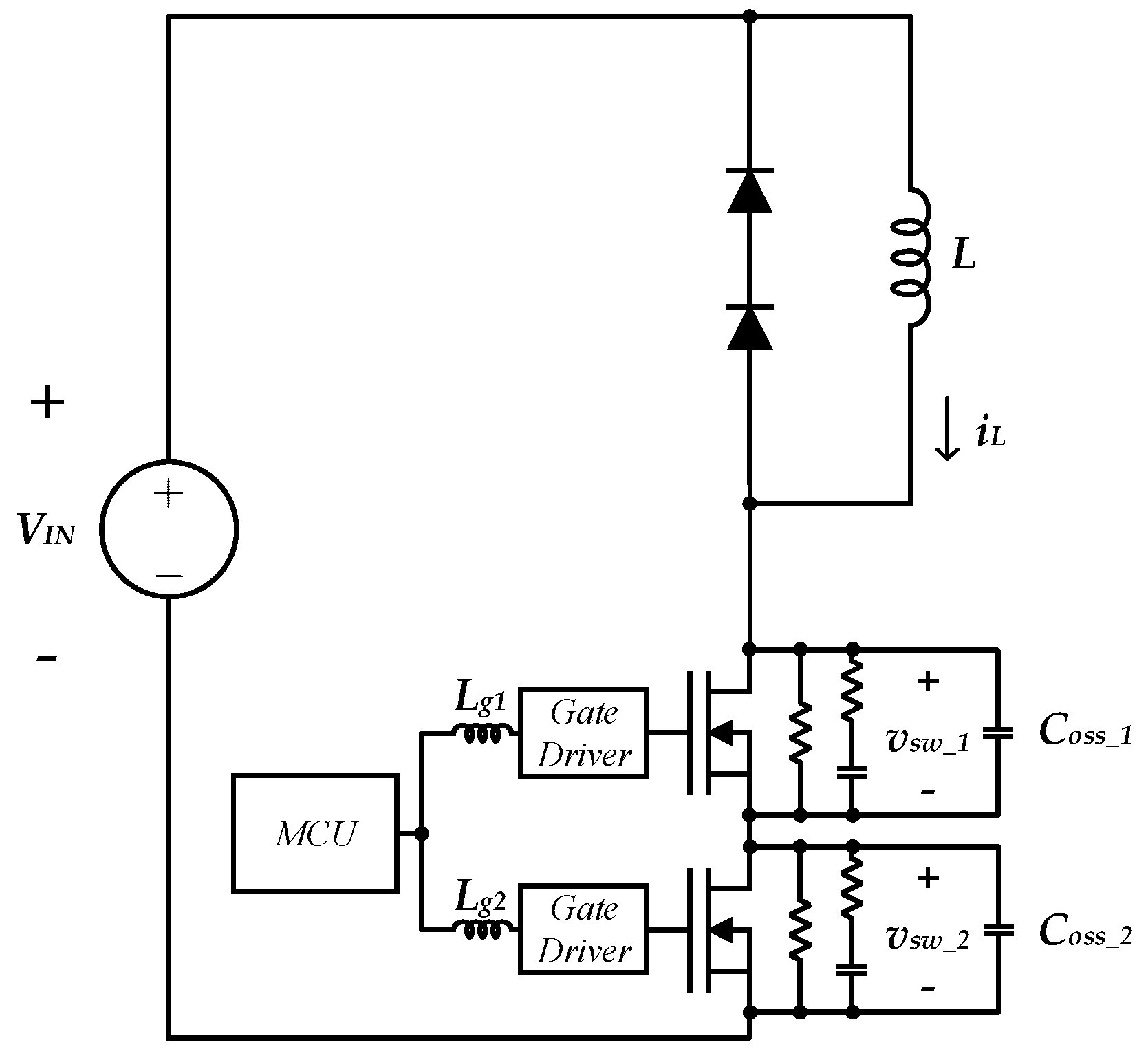

Figure 2 depicts the series-connected device with various factors that cause a voltage imbalance. Gate signal mismatch can occur due to an error of the device’s parasitic capacitor, unbalance of the gate signal due to a gate pattern, and an error of the parasitic capacitor from gate to ground, which causes an unbalance of voltage across the device. Furthermore, the voltage imbalance of devices increases the stress and can cause damage to the device. In this section, in order to prevent damage to the device, the voltage balancing method of the series-connected devices was analyzed using passive components.

Passive snubbers implemented by passive devices (

C,

RC,

RCD, etc.) are used for voltage balancing circuits. Voltage imbalance of devices is somewhat limited by placing the passive snubber circuit between drain to source. The use of passive snubber circuits reduces the switching speed of devices and the voltage imbalance due to a gate signal imbalance.

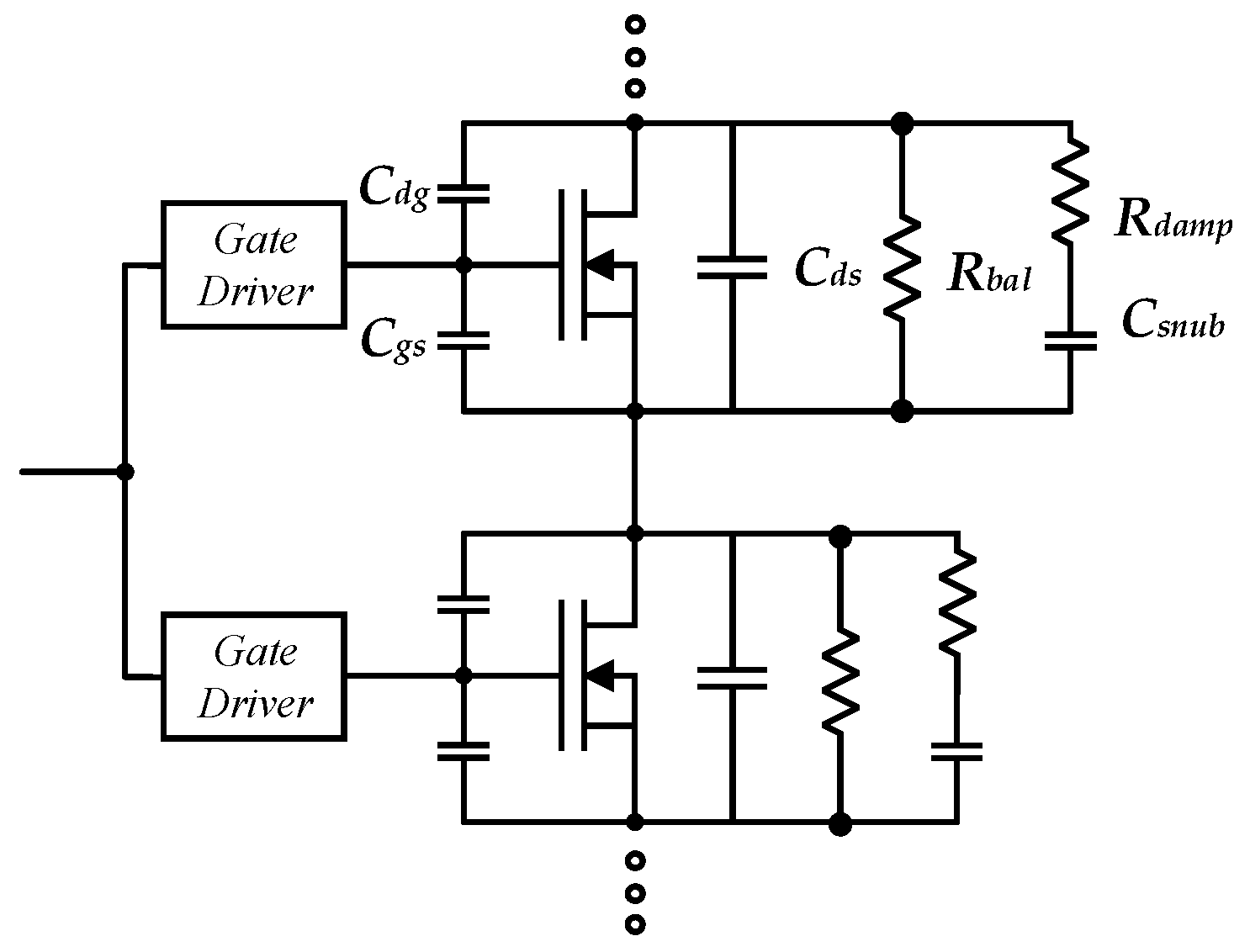

Figure 3 shows series-connected devices with passive balancing circuits. The snubber circuit composed of a steady-state balancing resistor (

Rbal) and a transient state balancing capacitor (

Csnub,

Rdamp).

The steady-state balancing resistors operate when the switch is fully turned-off. If the steady-state balancing resistors are small, the devices are well balanced. However, the power dissipation of balancing resistors increased, which requires the use of higher-rated resistors. Conversely, If the balancing resistors are big, the power dissipation of balancing resistors decrease. However, there is a high probability that voltage balancing between series-connected devices will fail. Therefore, when designing the balancing resistor, the leakage current of the device should be considered. Steady-state resistance are calculated below.

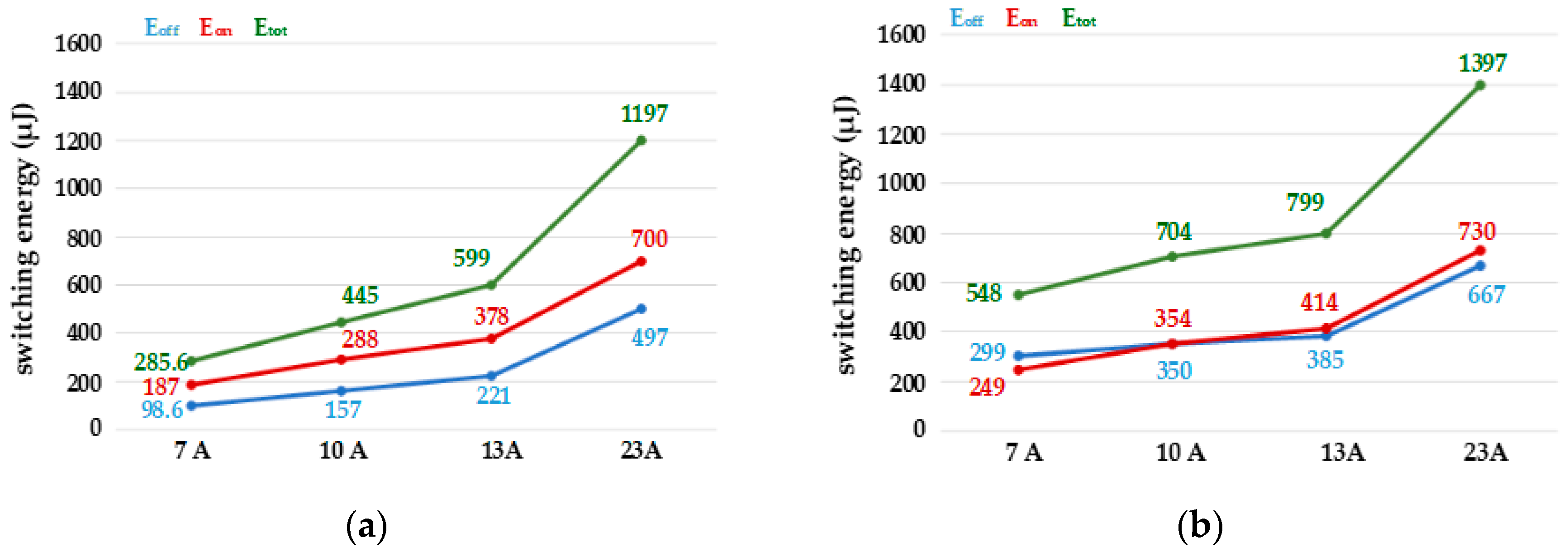

The transient state balancing circuit (Csnub, Rdamp) operates when the switch is a turn-on state and a turn-off state. Csnub is selected considering the parasitic capacitor of the device. To avoid imbalance by parasitic capacitor errors of the devices, attach a balancing capacitor with negligible parasitic capacitors of a device. If snubber capacitance is big, voltage unbalance during the transient will be stabilized, but switching speed will decrease and switching loss will increase. If the snubber capacitance is small, the snubber capacitors cannot perform proper balancing. Rsnub works as a damping resistor. The inrush current of the snubber capacitor at the switching state is limited by Rsnub. Therefore, Rsnub is selected by the current rating of the snubber capacitor. In addition, when calculating the Rsnub value, a time constant () and switching frequency (fsw) should be considered. A large time constant reduces the switching speed, increases switching losses, and also hinders soft switching of the LLC converter.

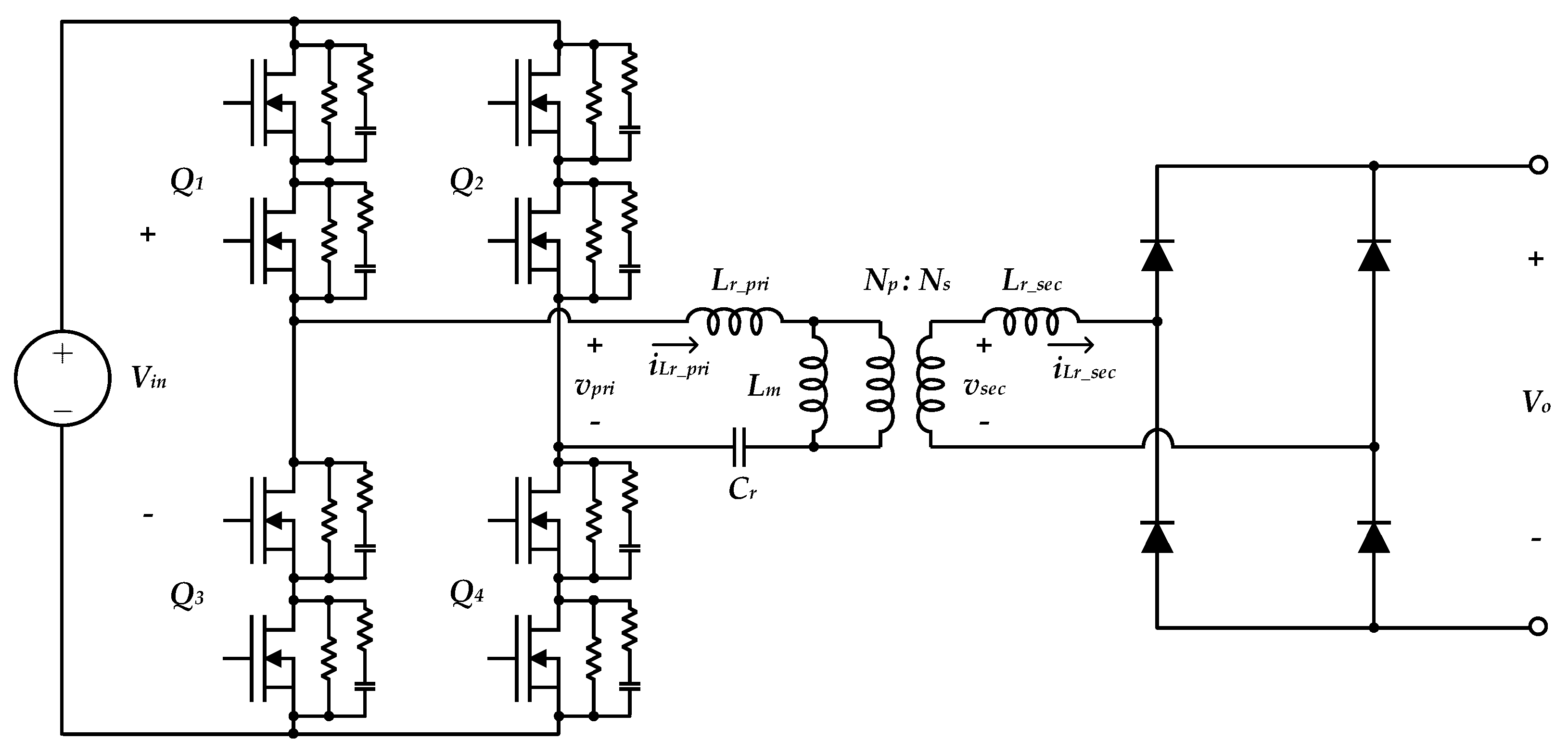

3. Design of LLC Converter

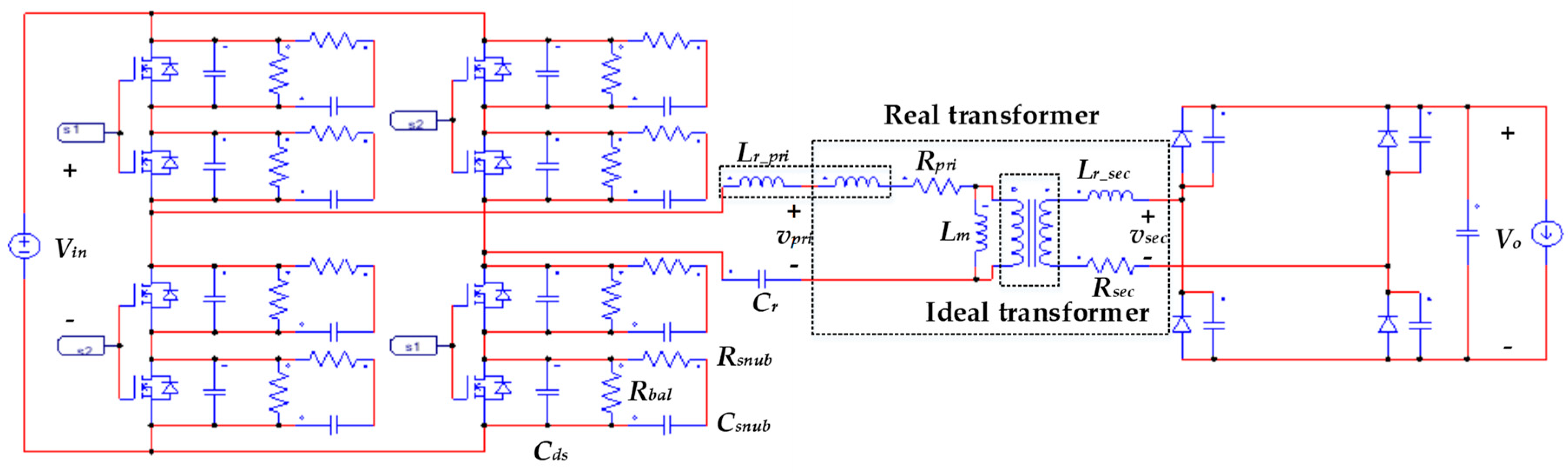

Figure 4 depicts the series-connected SiC MOSFETs LLC Converter with voltage balancing circuits. Generally, the output capacitance of the switching device should be considered in the design process. However, in this case, Snubber capacitors are added in parallel with the series-connected devices for voltage balancing. The output capacitor should be discharged during deadtime for a sufficient Zero Voltage Switching (ZVS) effect. Therefore, the snubber capacitor should be considered when designing an LLC converter. Except for the snubber capacitor, the others process of the designed LLC converter are followed by the general LLC converter design process in References [

17,

18].

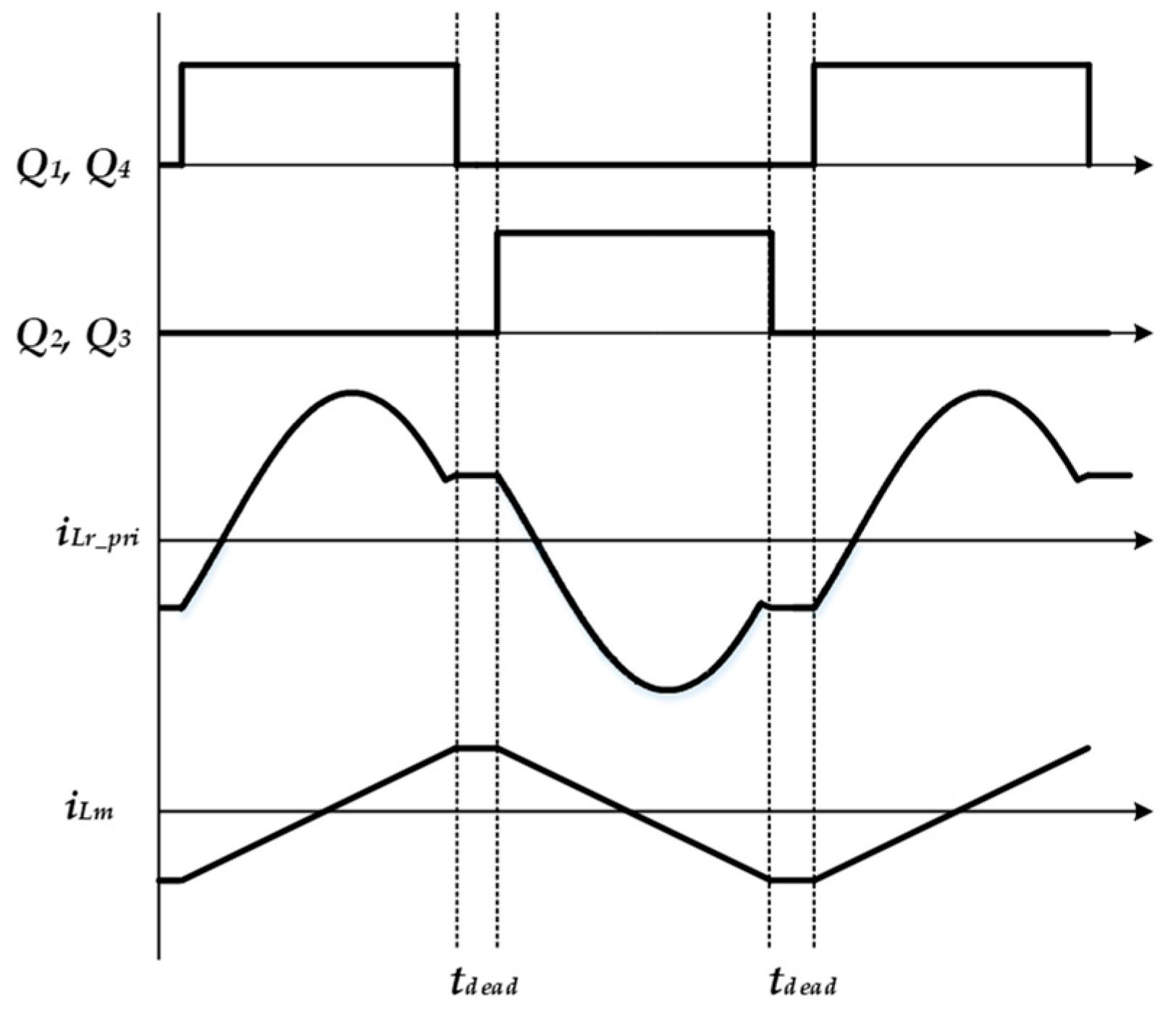

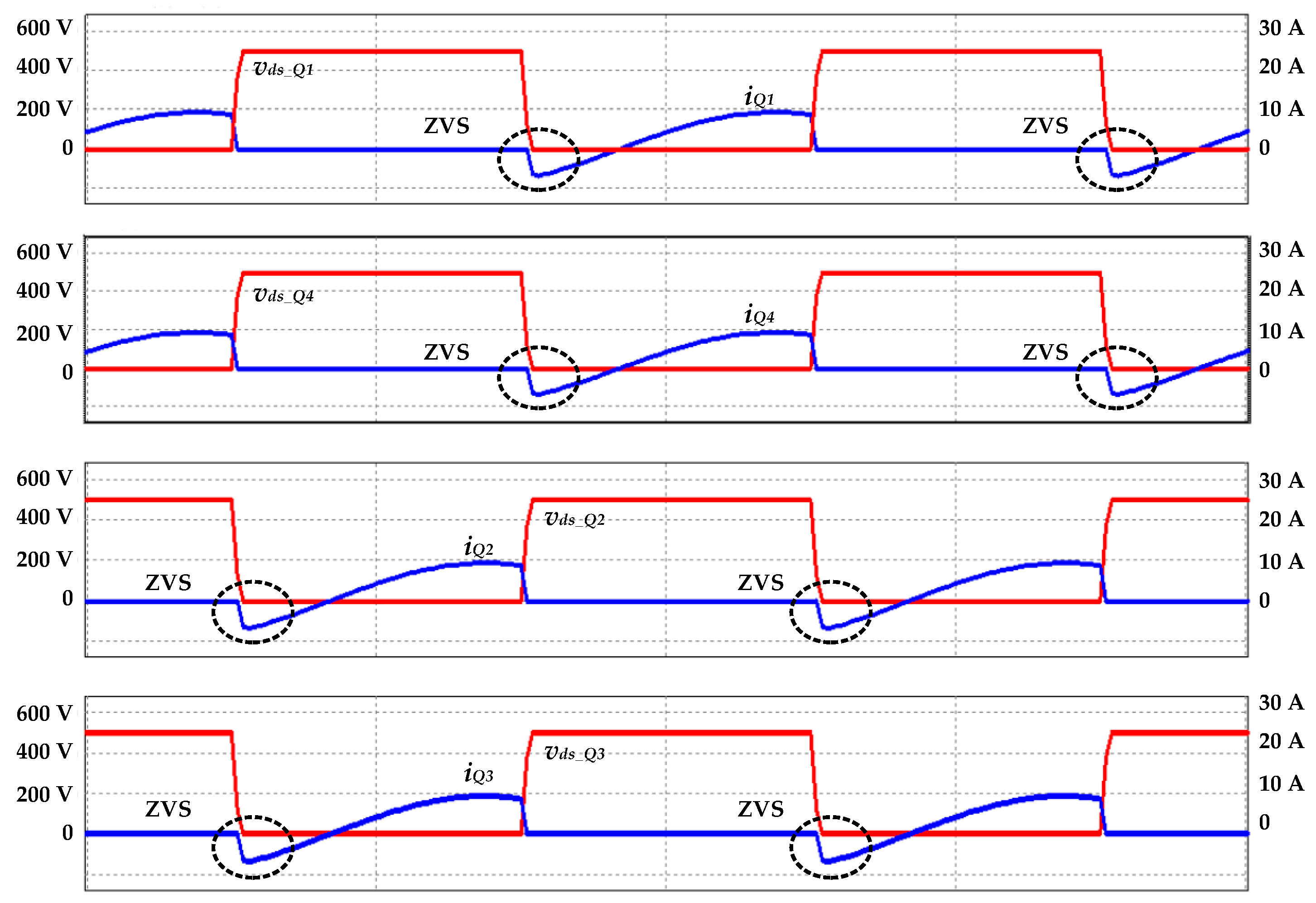

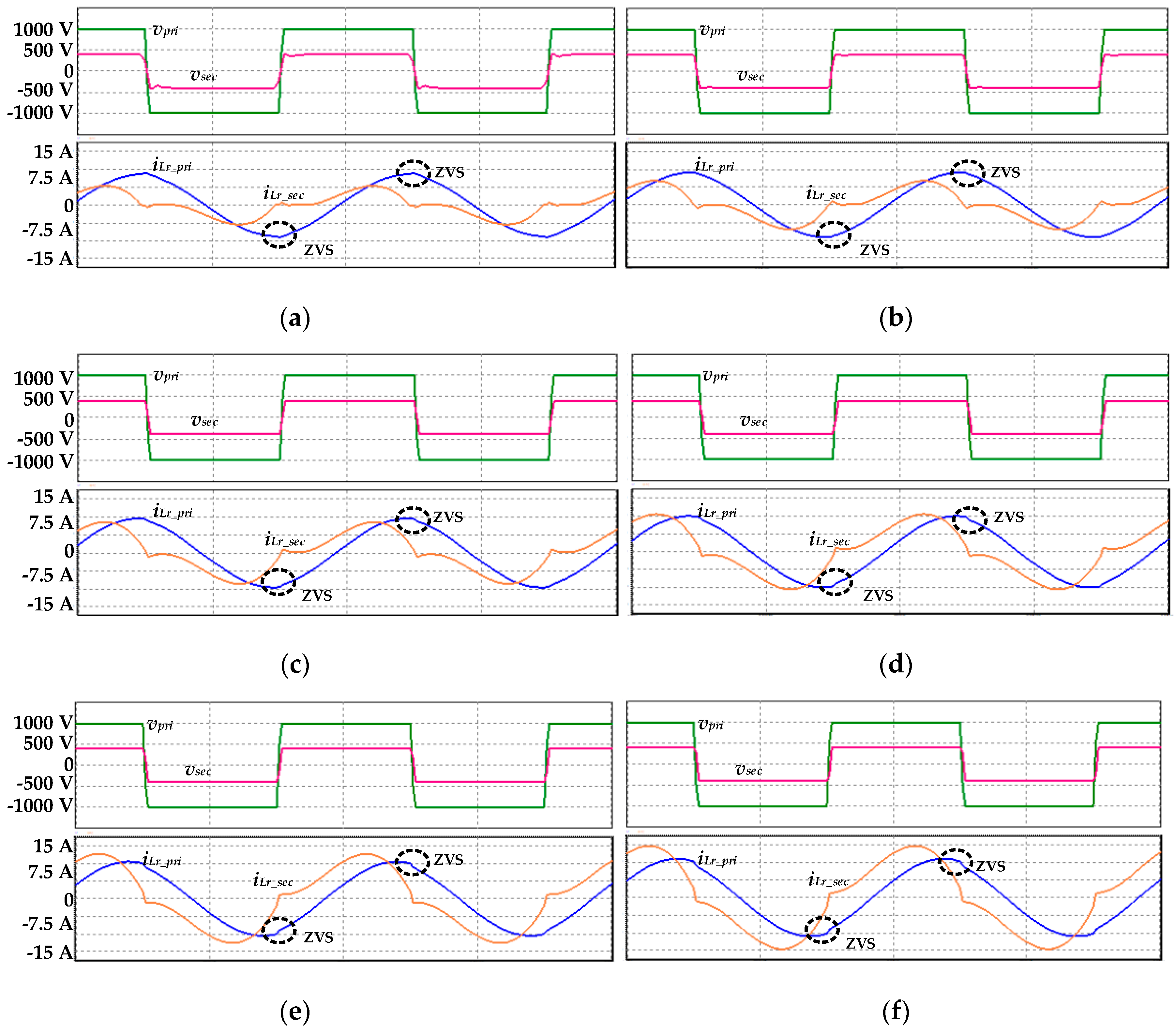

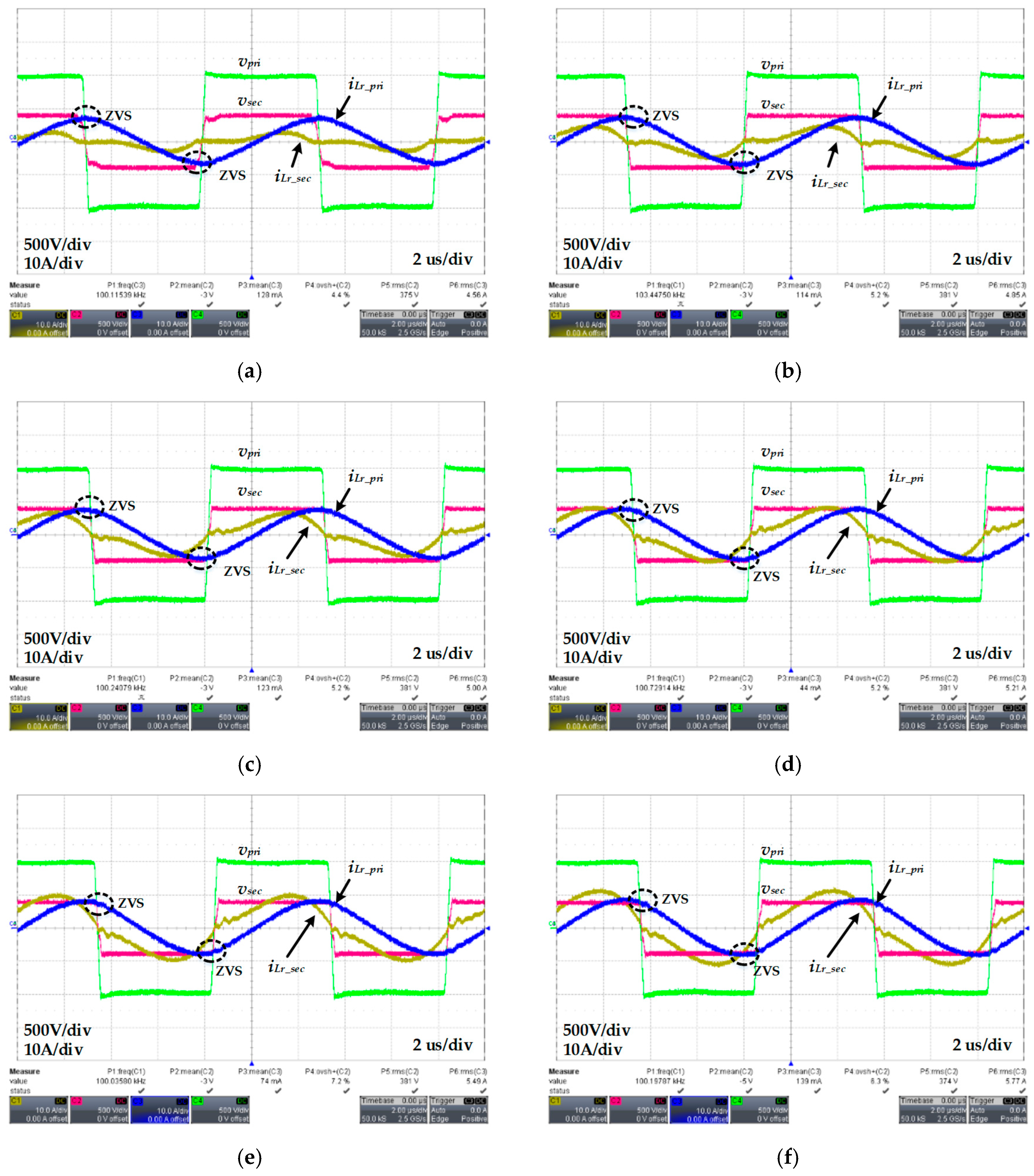

Figure 5 shows theoretical waveforms of the conventional LLC converter. For simplifying it to analyze, some assumptions are made as follows.

There is no error of parasitic elements of a switching device;

Gate drivers are all ideal, and there is no time delay between series-connected devices due to the gate driver.

The gate signals of devices are off during the deadtime (

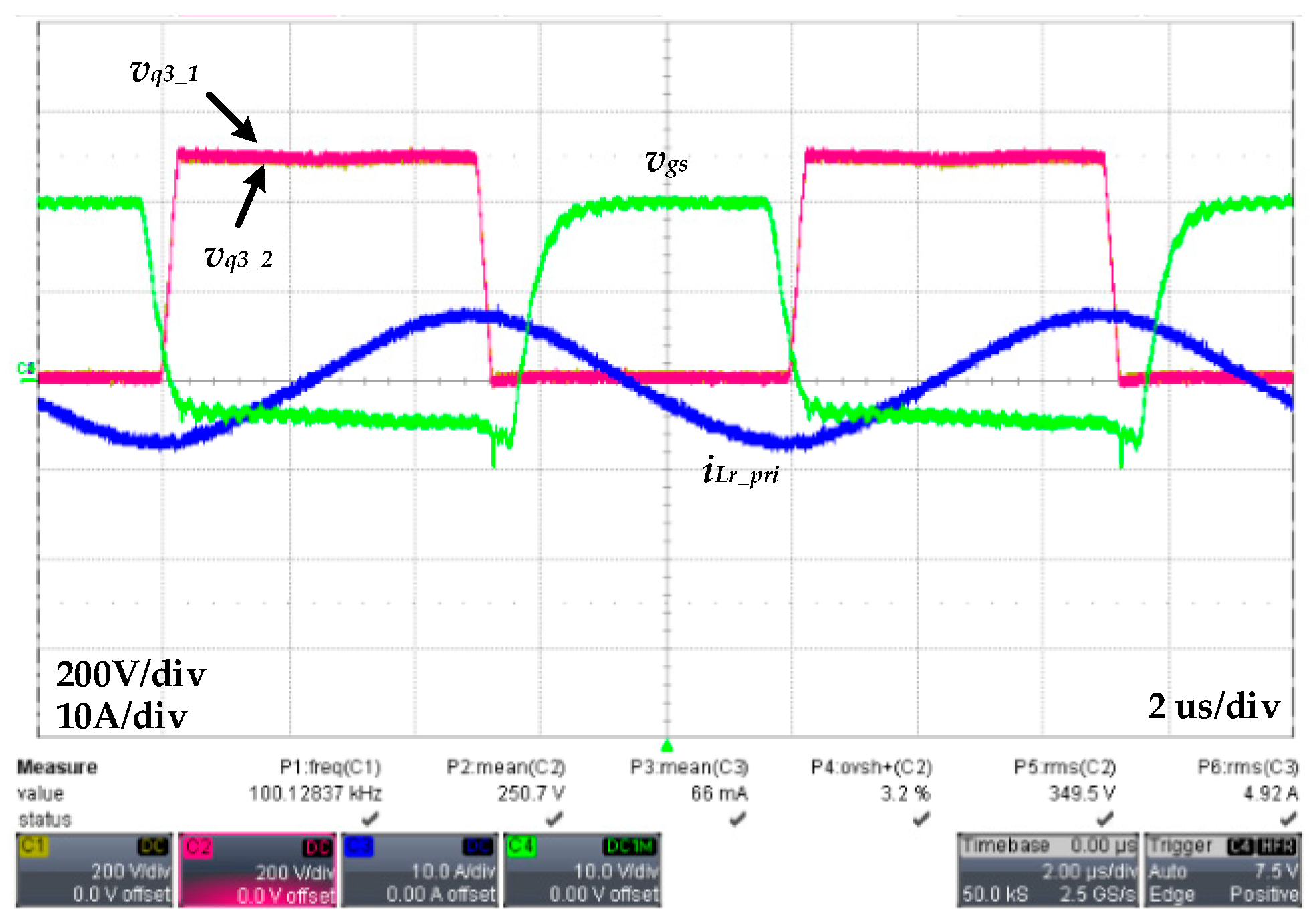

tdead) interval. The magnetizing current and resonant current become the same during the deadtime. During the deadtime, inductor current flows through the antiparallel diode of the switch and discharges the parasitic output capacitor of the switch. Then, the switch turns on after zero voltage is formed by the discharged output capacitor so that soft switching is possible. The equation of minimum deadtime and magnetizing inductance for soft switching is calculated below.

Equation (2) represents that the ZVS is related to the magnetizing inductance of the high frequency transformer (HF transformer) and the output capacitance of the switch. As mentioned in the previous section, Snubber capacitors are required for voltage balance between series-connected devices. Therefore, when manufacturing the LLC converter with balancing circuits that are connected in parallel to each device, balancing circuits should be considered. This is not a parasitic component of the switch. After that, the rest process design of an LLC converter follows the conventional design process.

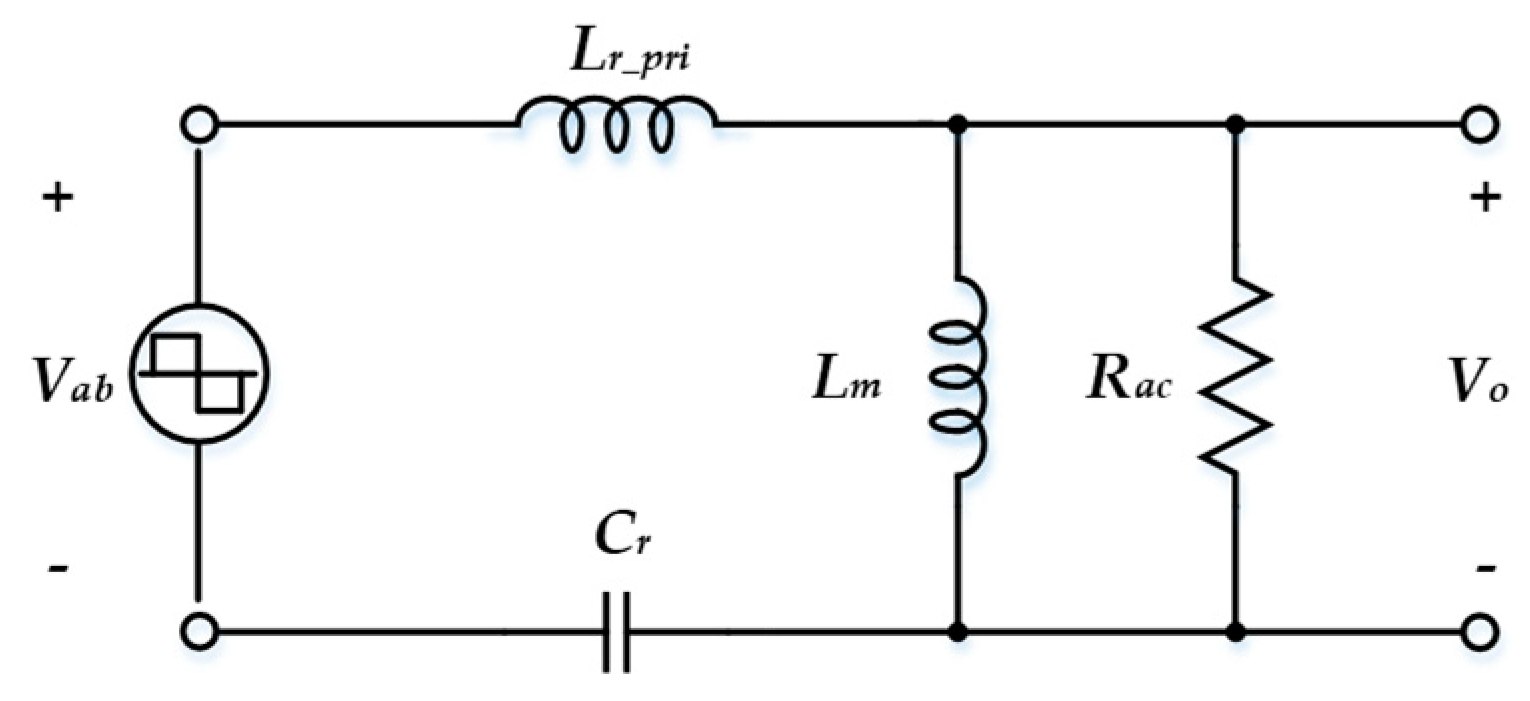

Figure 6 shows the equivalent circuit of an LLC converter. To design LLC, the converter is described as follows [

3,

4,

5,

6,

7,

8,

9].

where

Np and

Ns means the turn ratio of the transformer and

Ro is the load resistance. Furthermore,

fsw is the switching frequency,

fr is the resonant frequency, and the

Rac is the reflected load resistance. Therefore, the voltage gain of the resonant tank is defined below.

where

Vo_ac (s),

Vin_ac (s),

Q,

m, and

Fx are the

vin_ac,

vo_ac, the quality factor, the ratio of the total primary inductance to resonant inductance, and the normalized switching frequency, respectively.

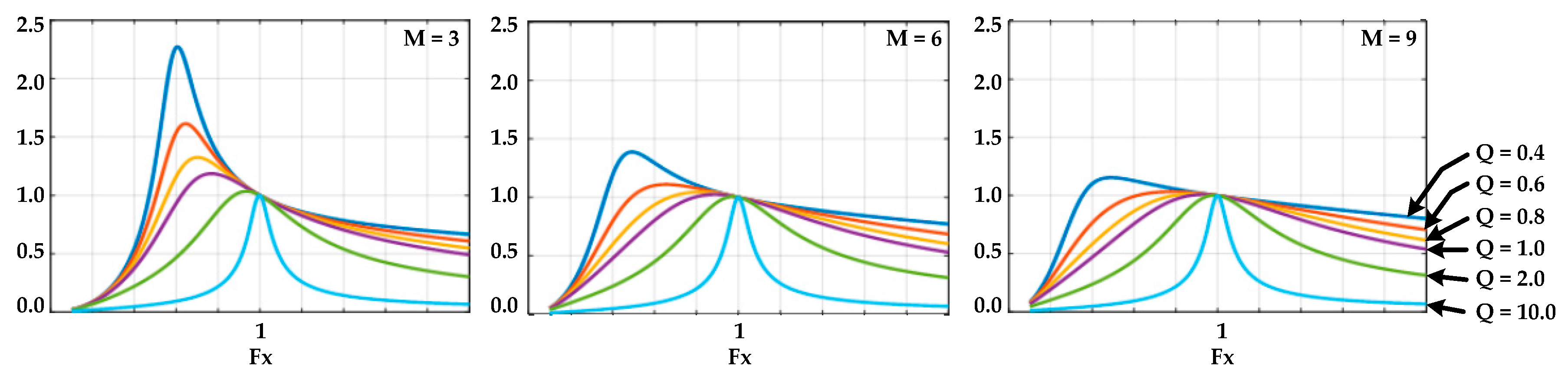

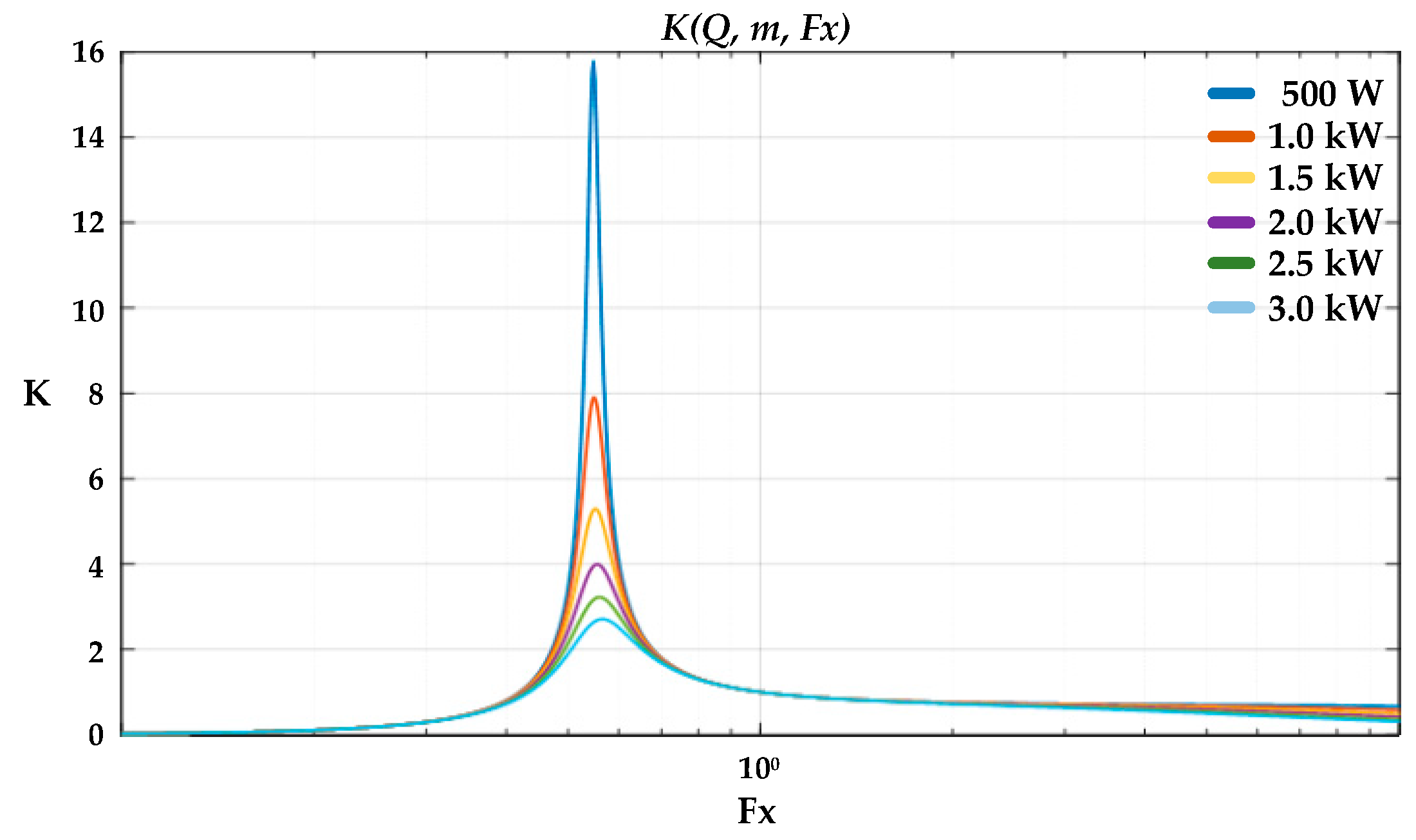

Figure 7 shows voltage gain according to different

m and

Q factors. In the figure, as the

m factor decreases, the voltage conversion ratio is extended. However, according to Equation (4), a low

m factor requires low magnetizing inductance

Lm. Thus, magnetizing current increases. It means that the conduction loss of magnetic components is increased. In terms of the

Q factor, the

Q factor is related to the load. The high

Q value means heavy load conditions and the low

Q value means light load conditions. Therefore, it is important to set the

Q value at the rated load. Thus, a voltage gain of an LLC converter is related to

m and

Q factors.

6. Conclusions

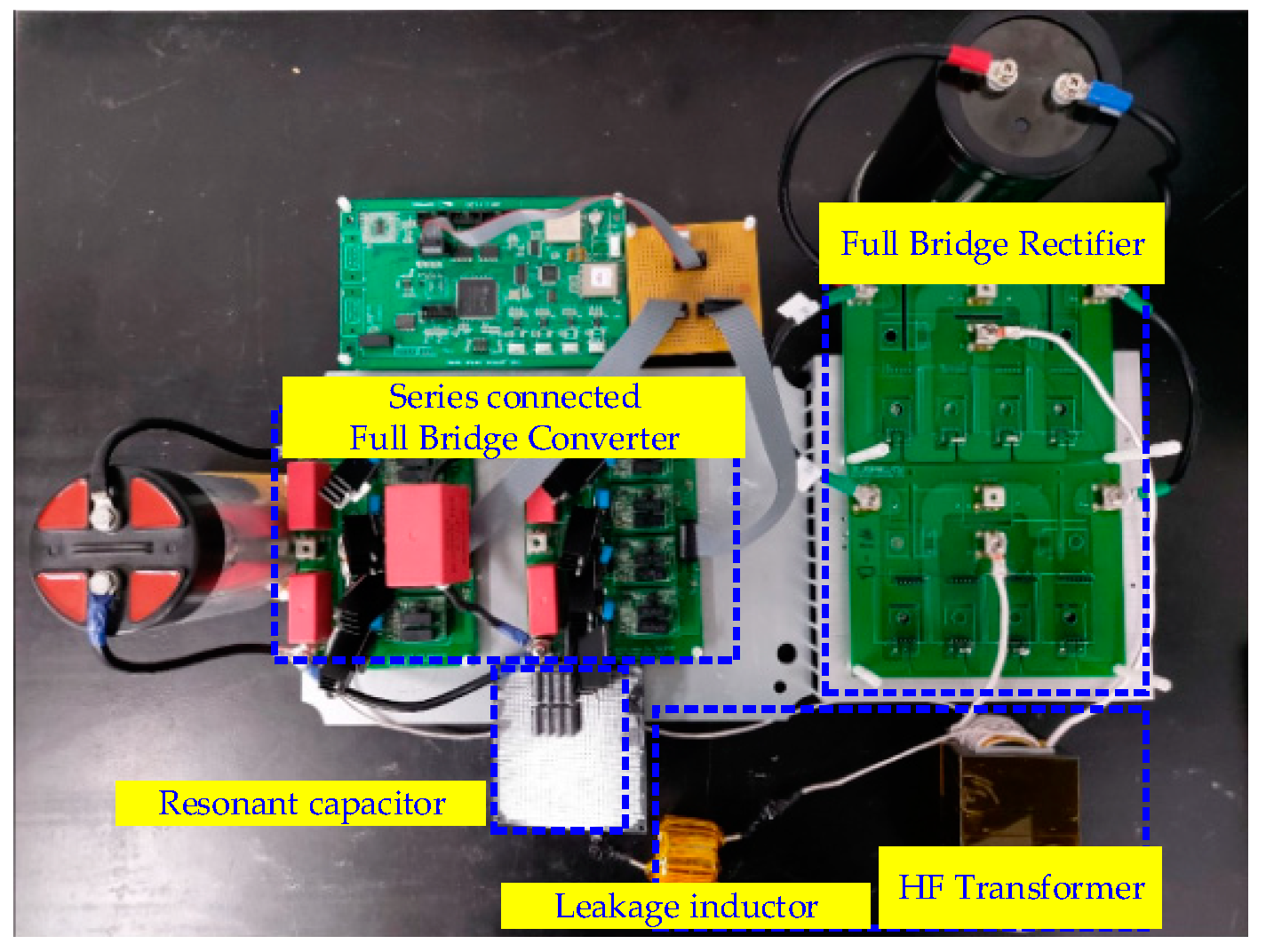

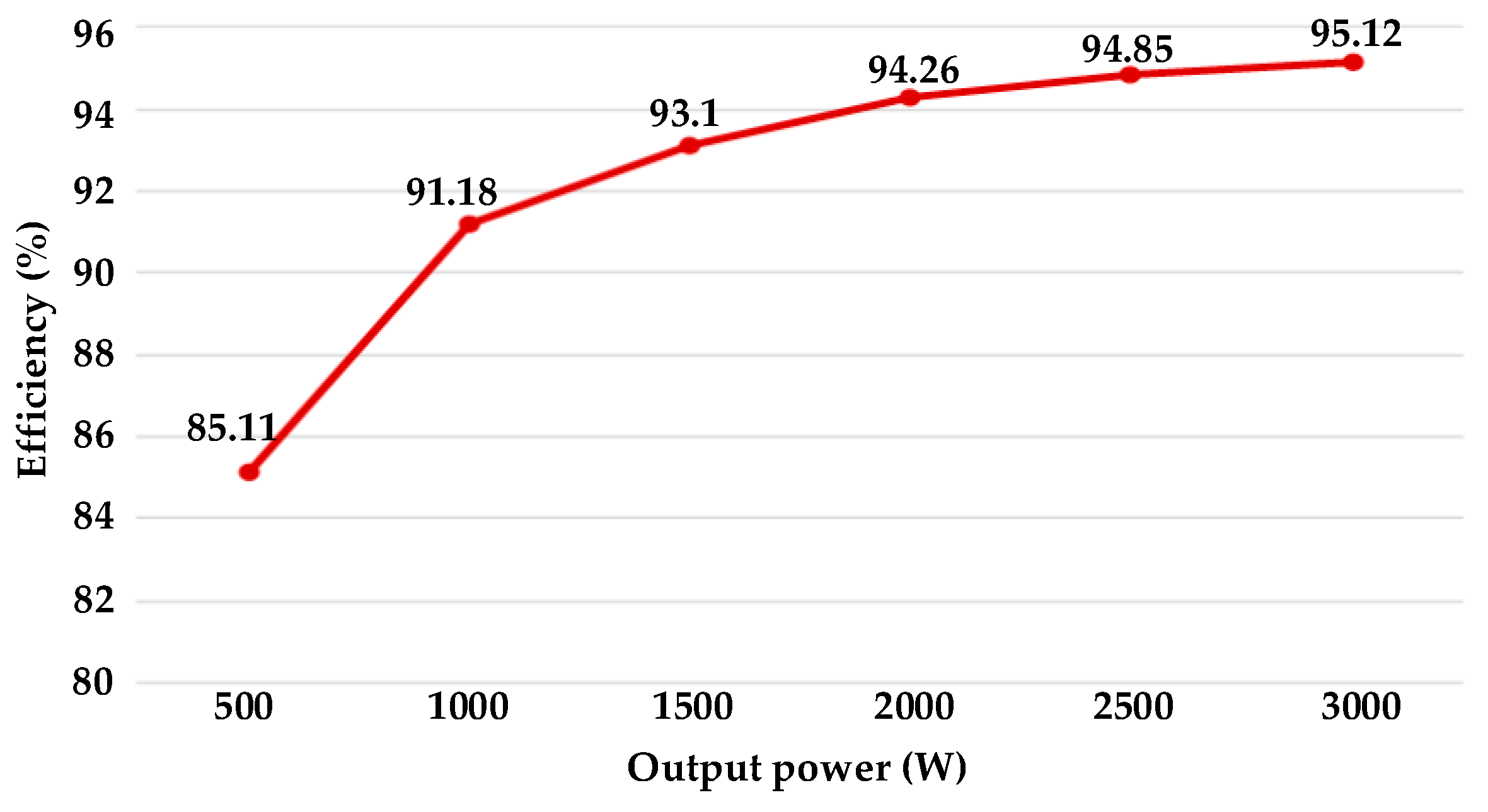

This paper describes the design consideration of the fixed frequency LLC converter considered balancing circuit of series-connected devices circuit. In the introduction, the reason for the imbalance voltage across the series-connected devices was described and discussed the need of an LLC converter. The proposed converter consists of a series-connected devices-based LLC converter.

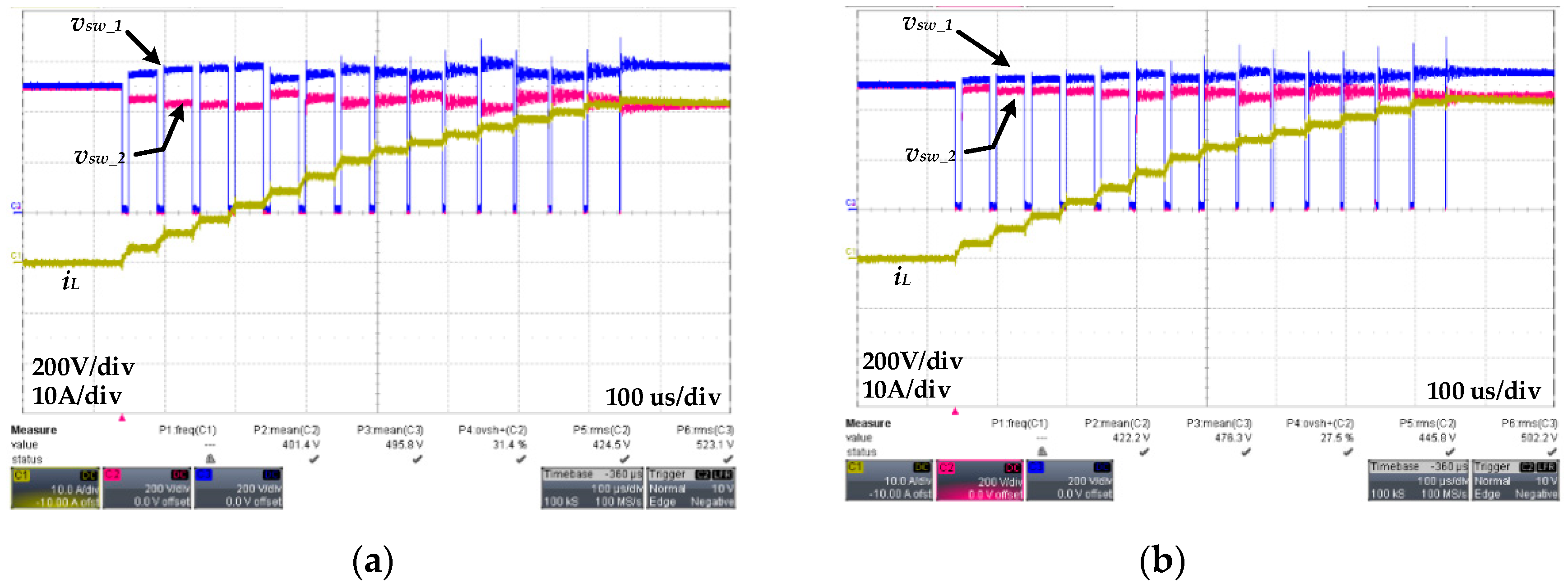

In order to verify the proposed converter, a series-connected devices-based voltage balancing experiment and the series-connected devices-based LLC converter was performed. The snubber circuit, which is the simplest method among the various methods for voltage balancing, was applied and the switching loss comparison and voltage balancing test was performed according to snubber circuits. Furthermore, based on the snubber circuits-designed simulation and experiments, 3 kW series-connected devices-based LLC converter was fabricated and verified. Through the experiments, the voltage balancing between series-connected devices and soft switching operation of the proposed converter are verified. The efficiency of a fabricated converter was measured 95.12% at 3 kW load. When the series-connected based LLC converter is fabricated with balancing snubber circuits, it is confirmed that the LLC converter design is necessary considering the balancing snubber, and the experimental results confirm that the consideration is valid.