Hybrid Multilevel Converters: Topologies, Evolutions and Verifications

Abstract

1. Introduction

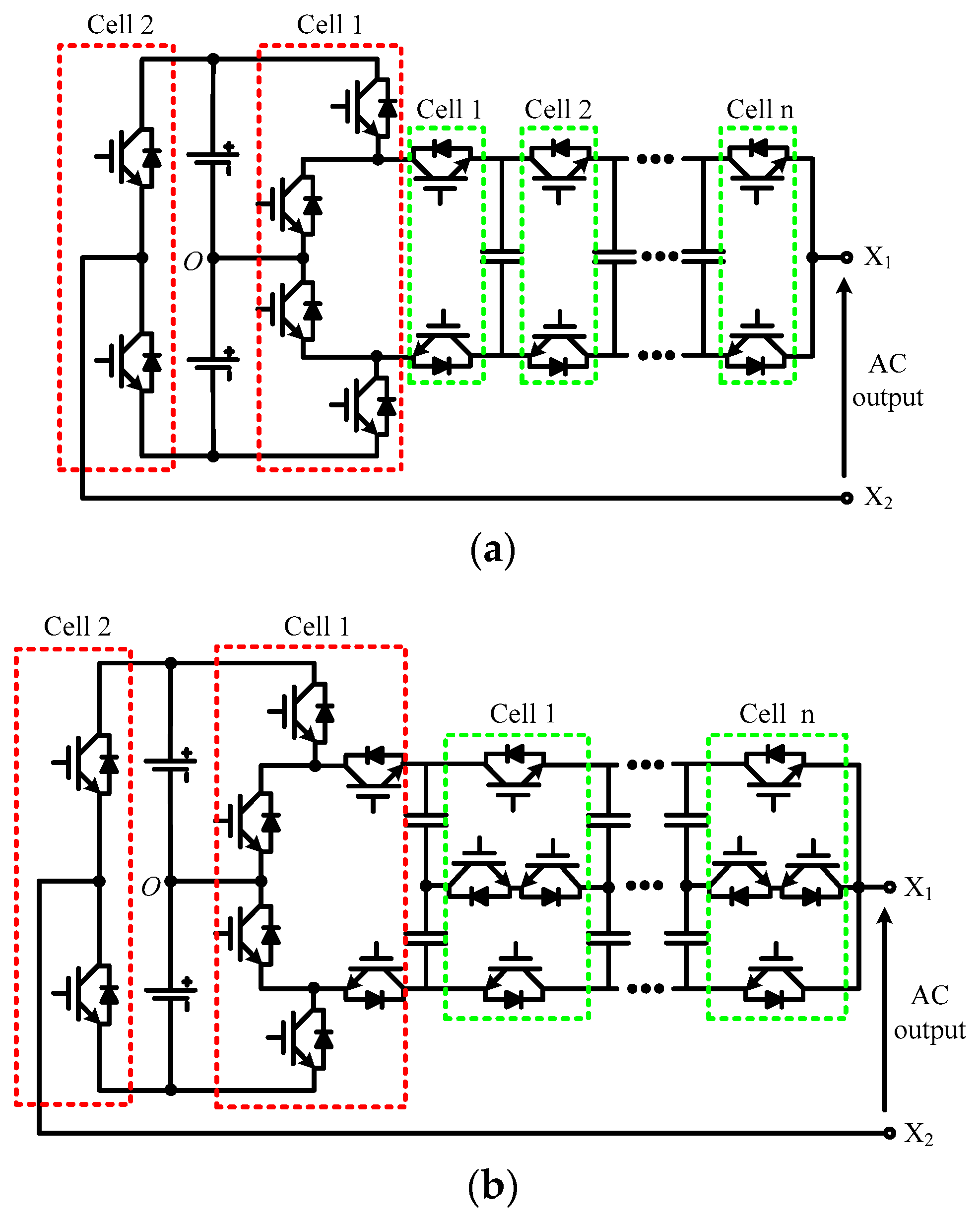

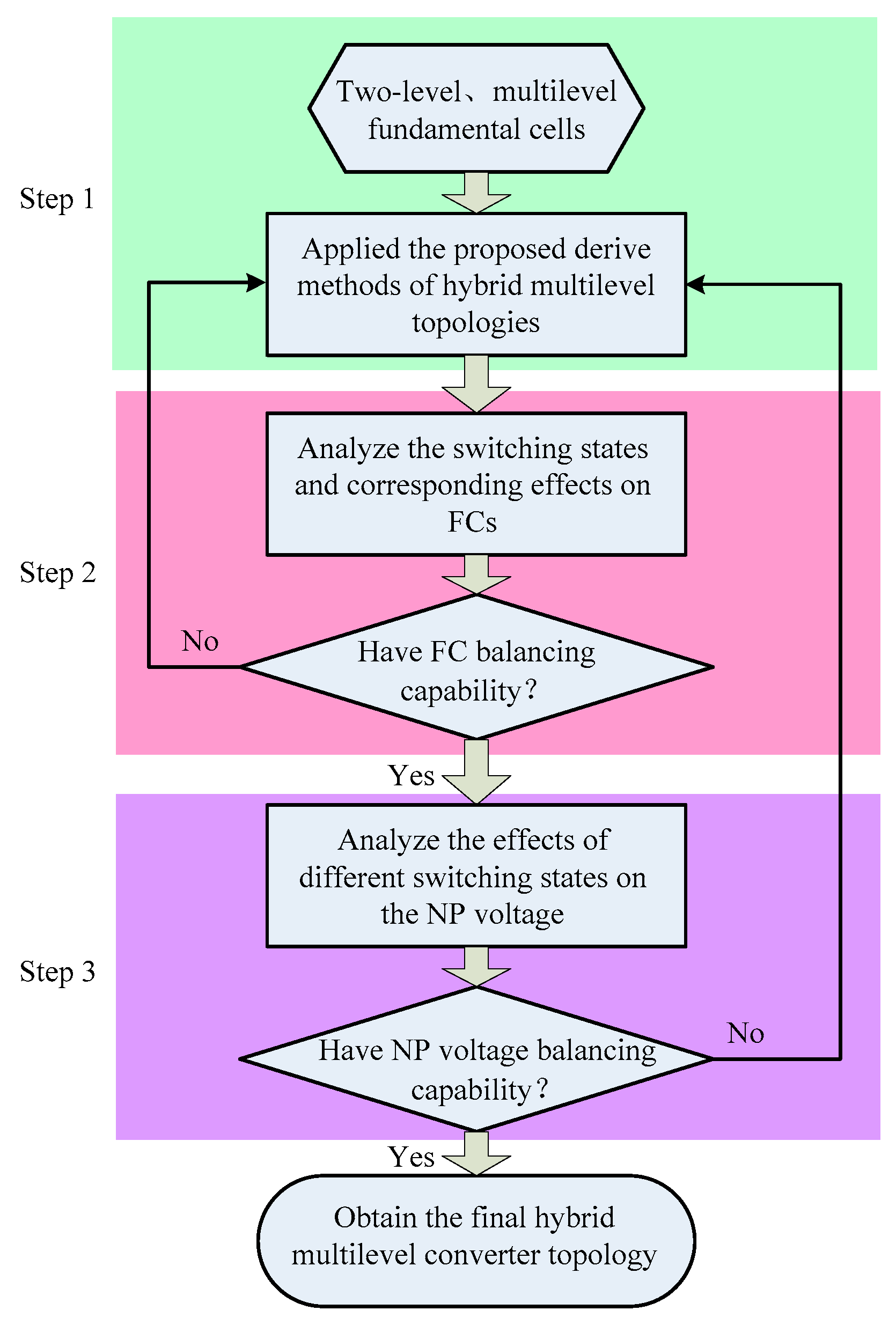

2. Hybrid Stacked Multicell Converters

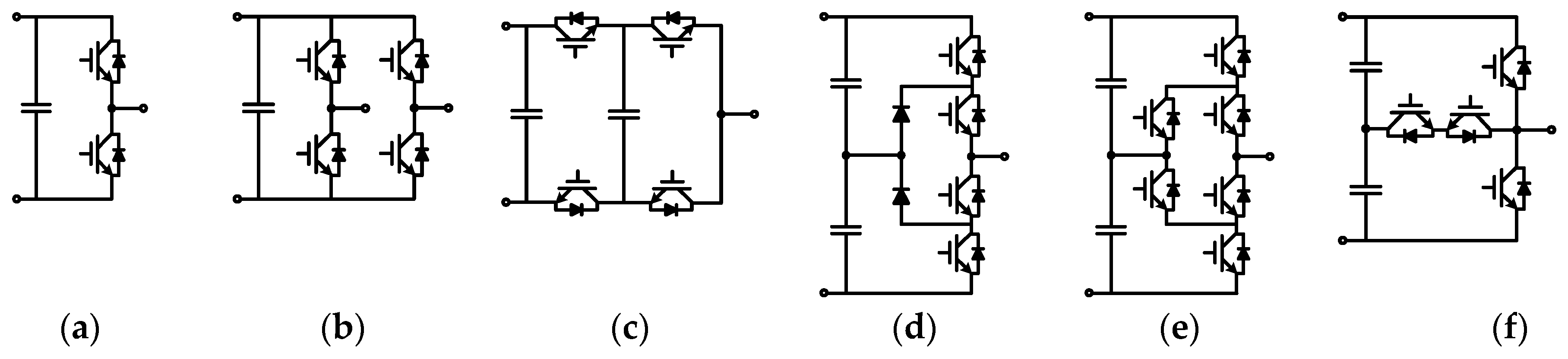

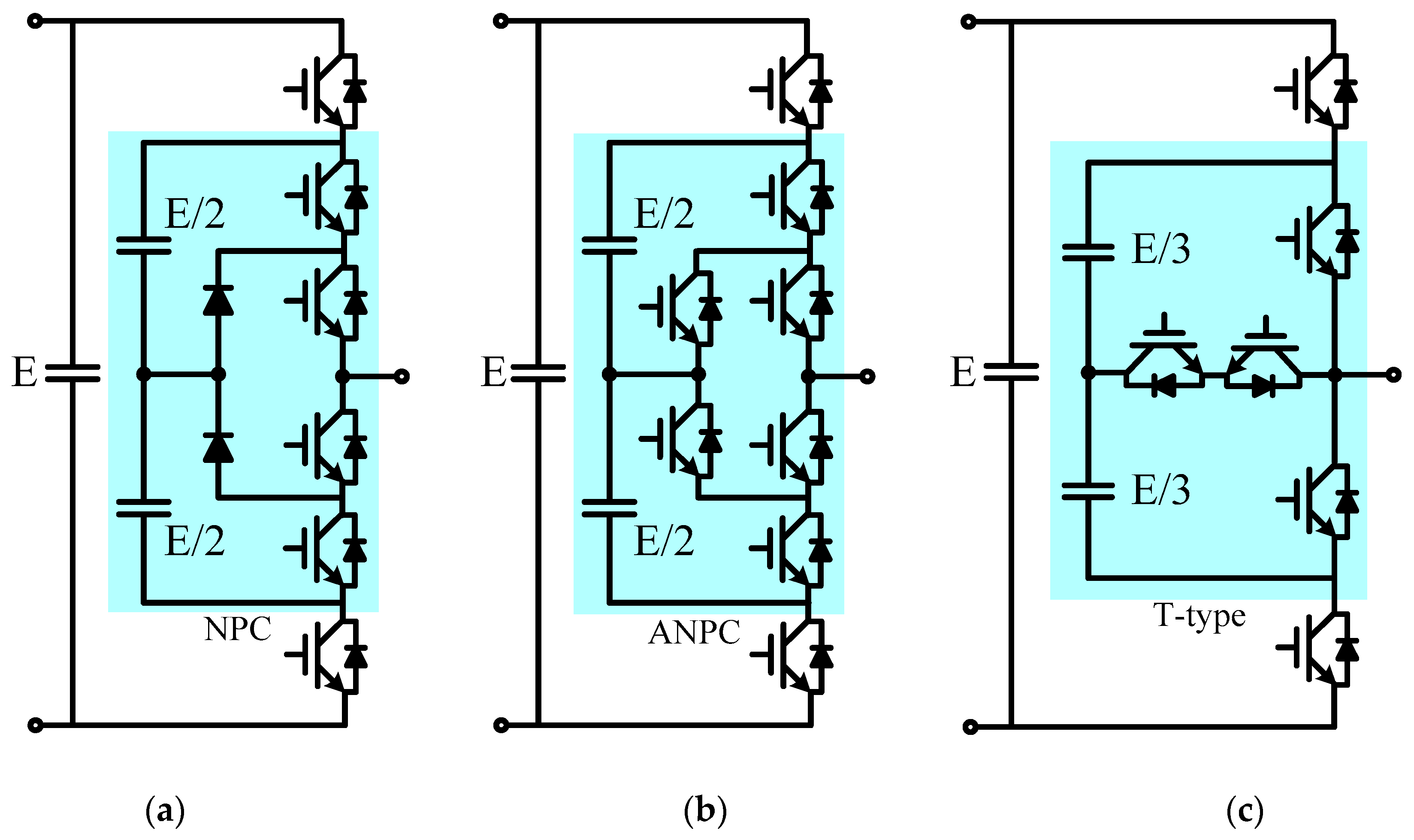

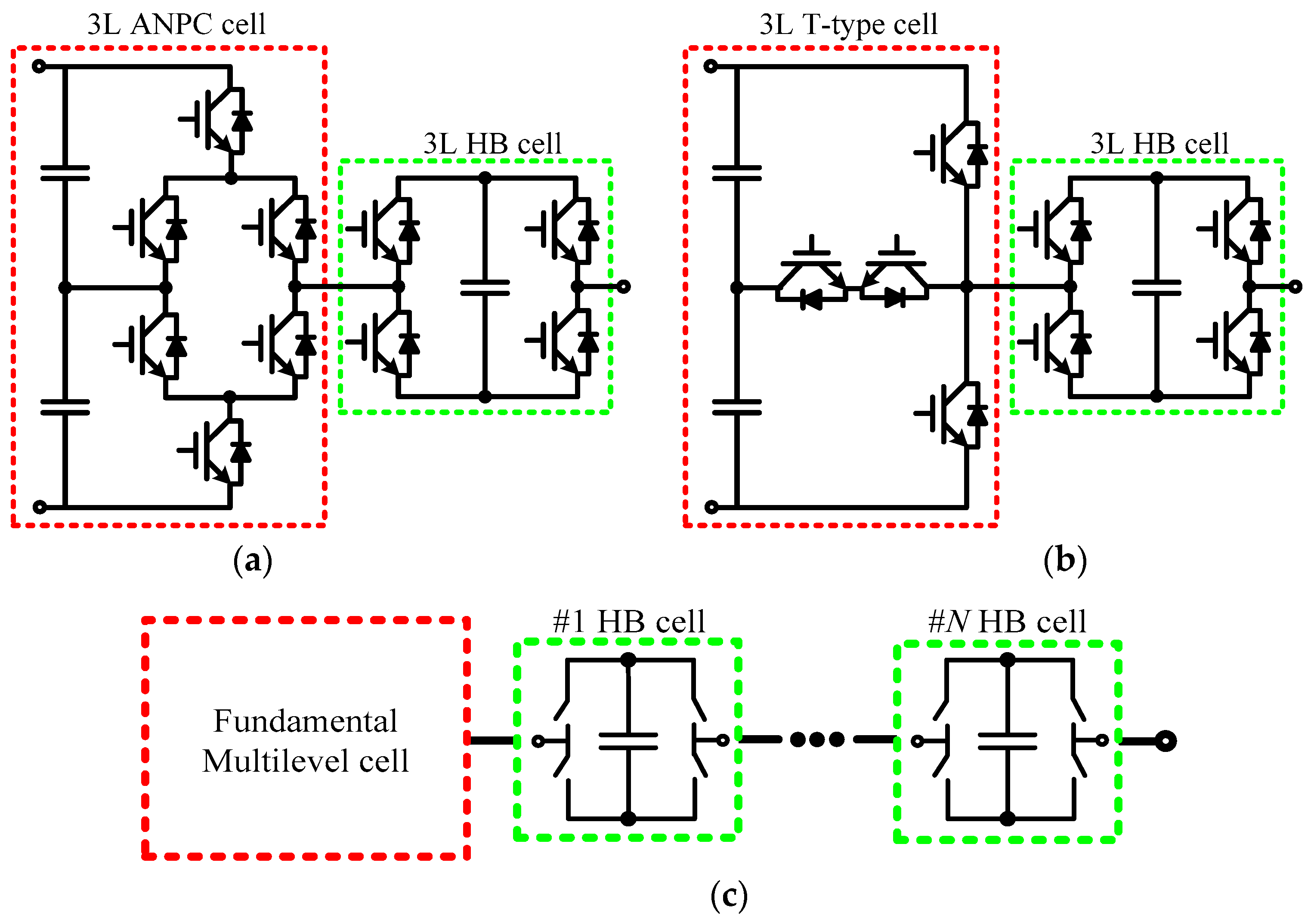

2.1. Basic Switching Cells

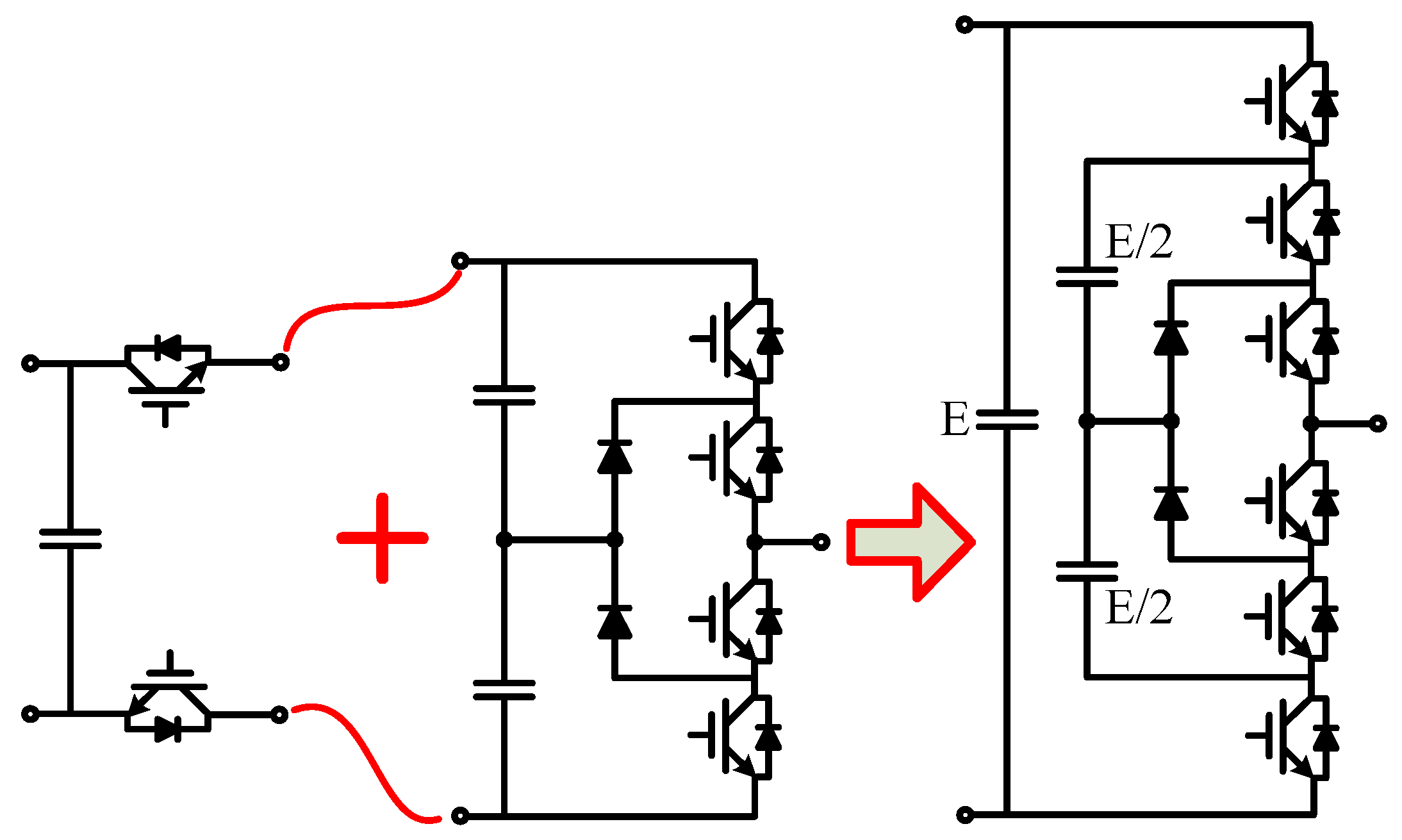

2.2. Hybrid Clamped Multilevel Converters

2.3. Hybrid Cascaded Multilevel Converters

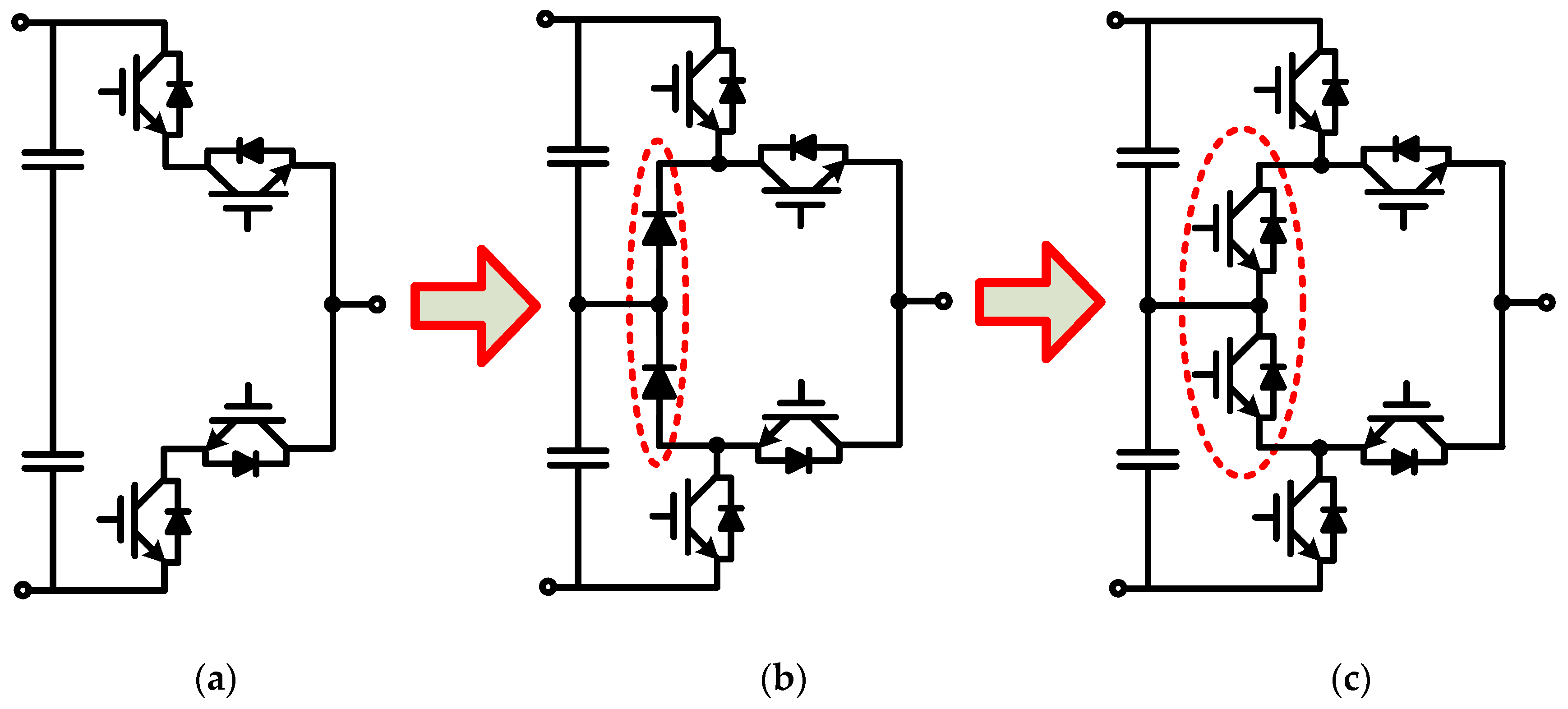

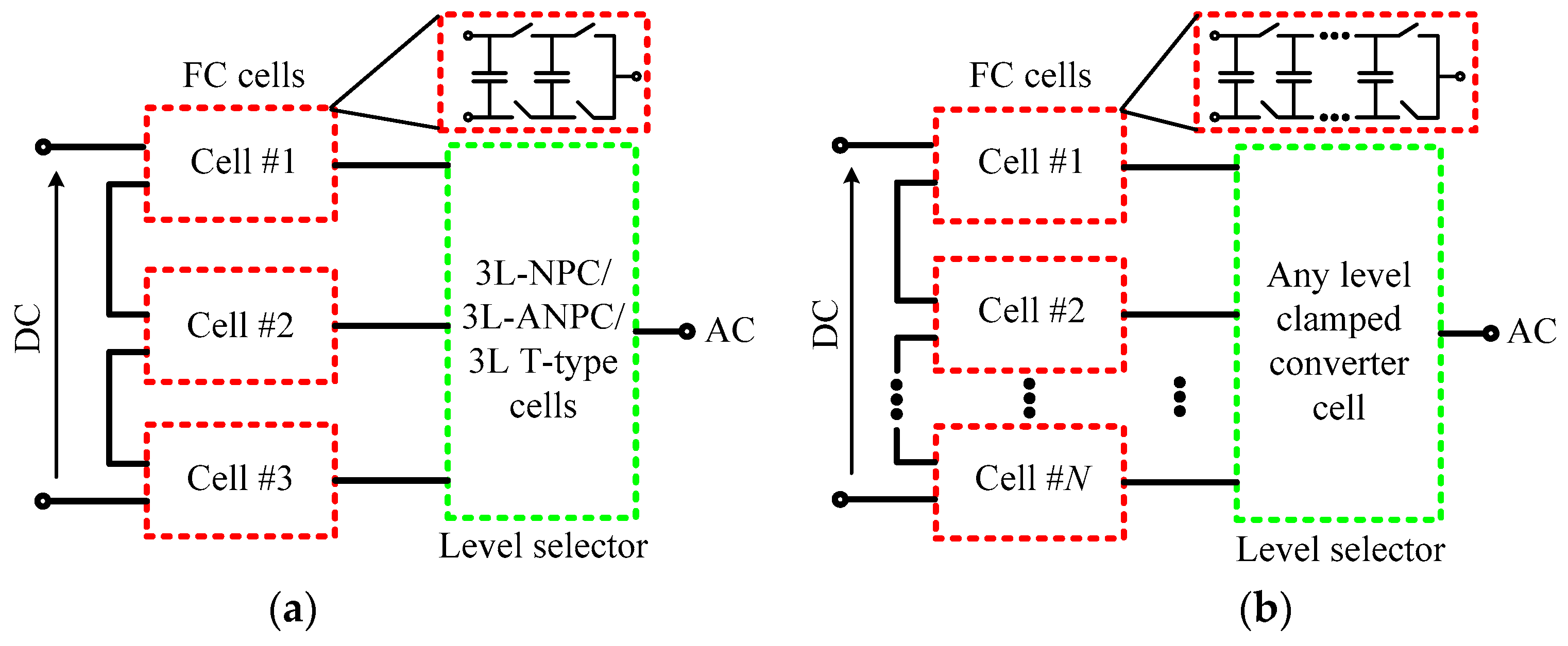

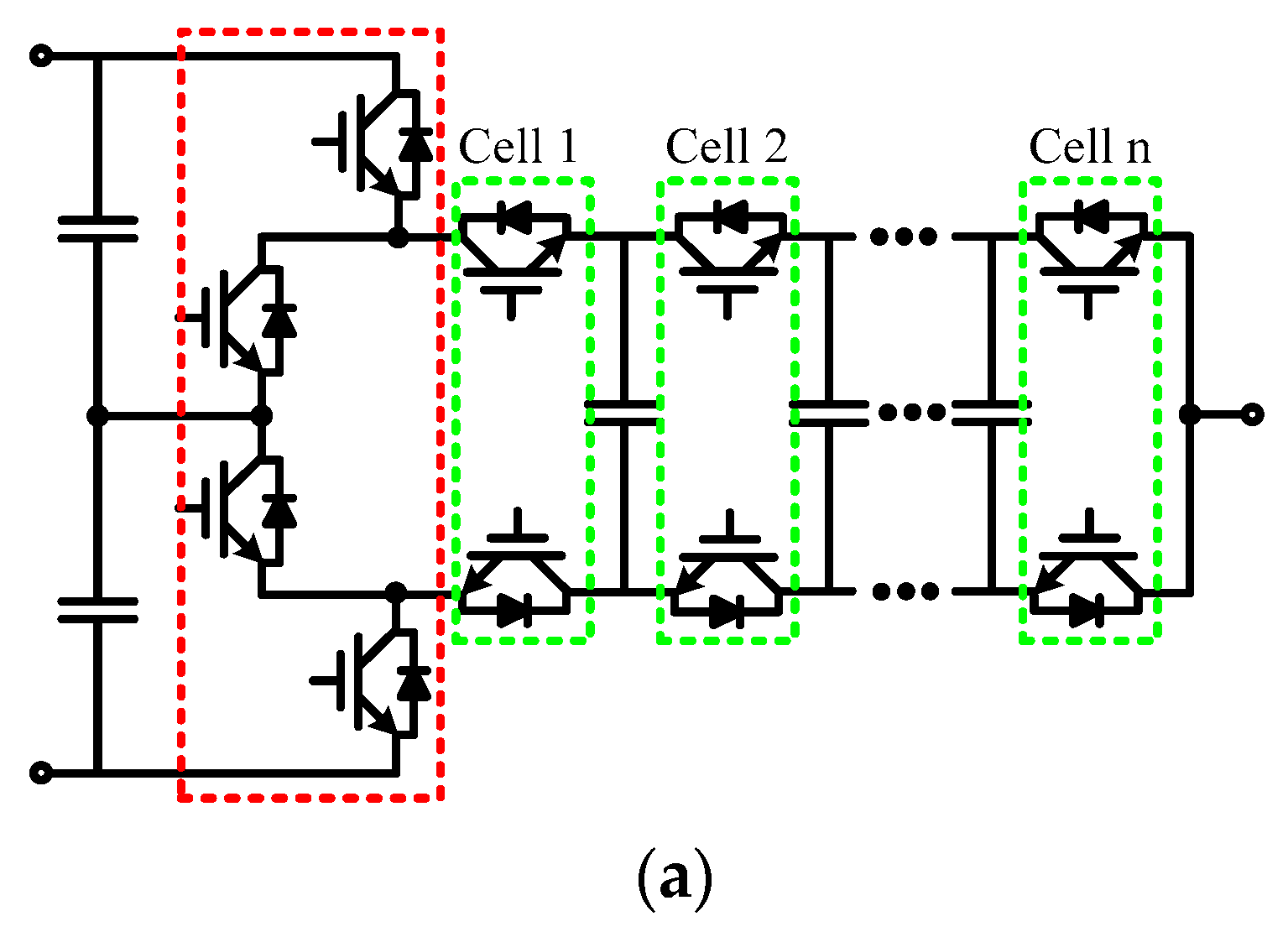

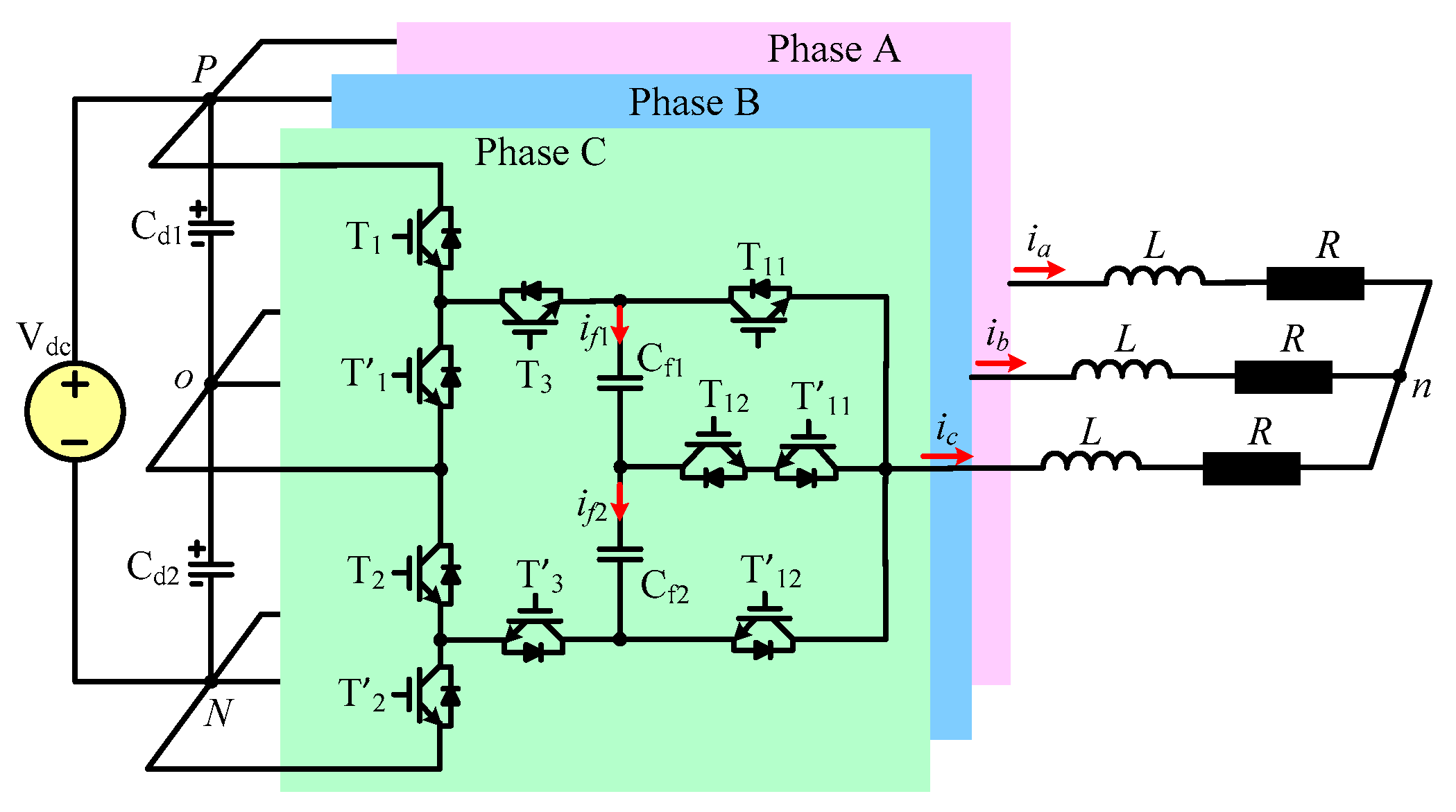

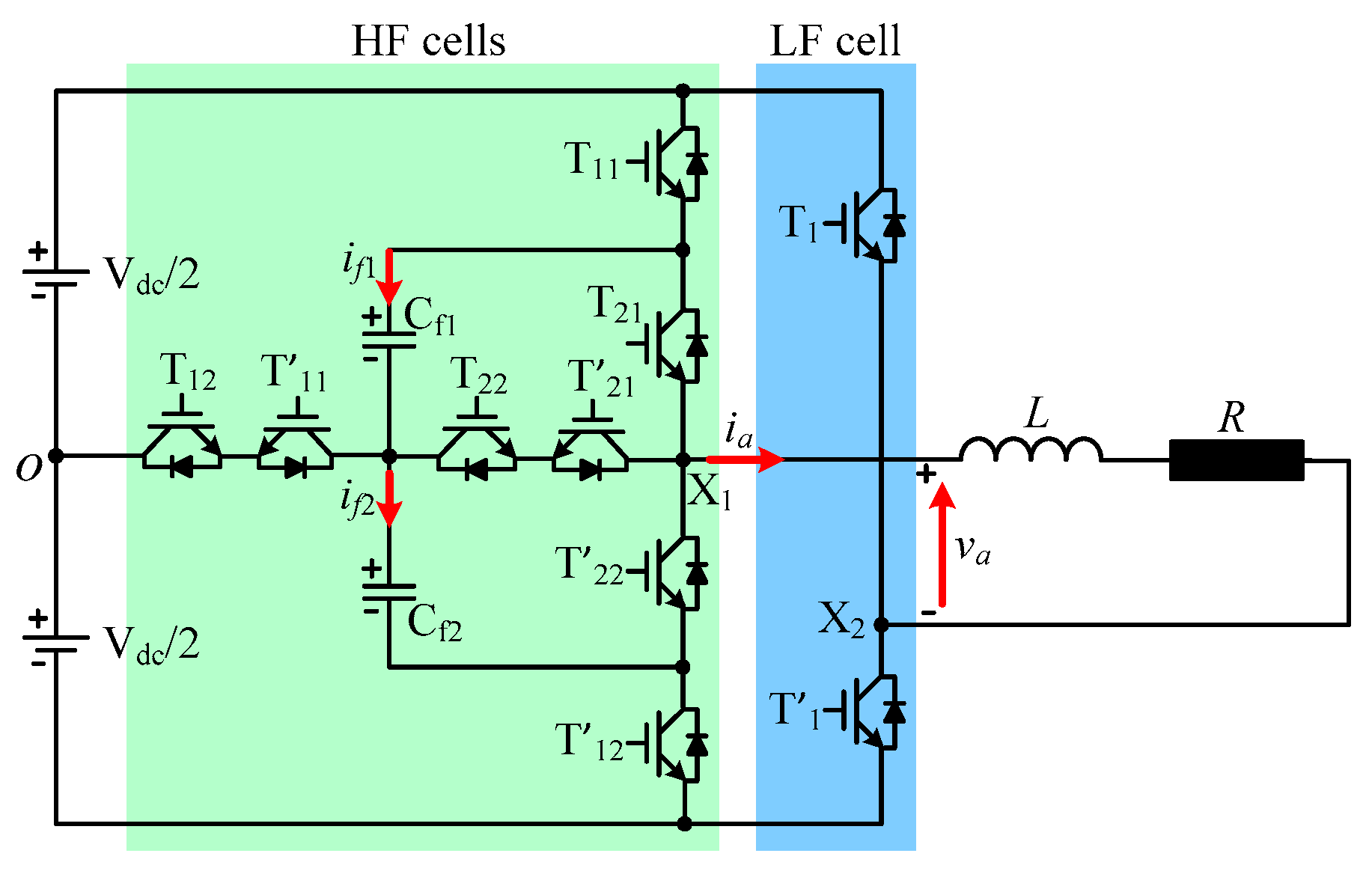

2.4. Hybrid FC-based ANPC Multilevel Converters

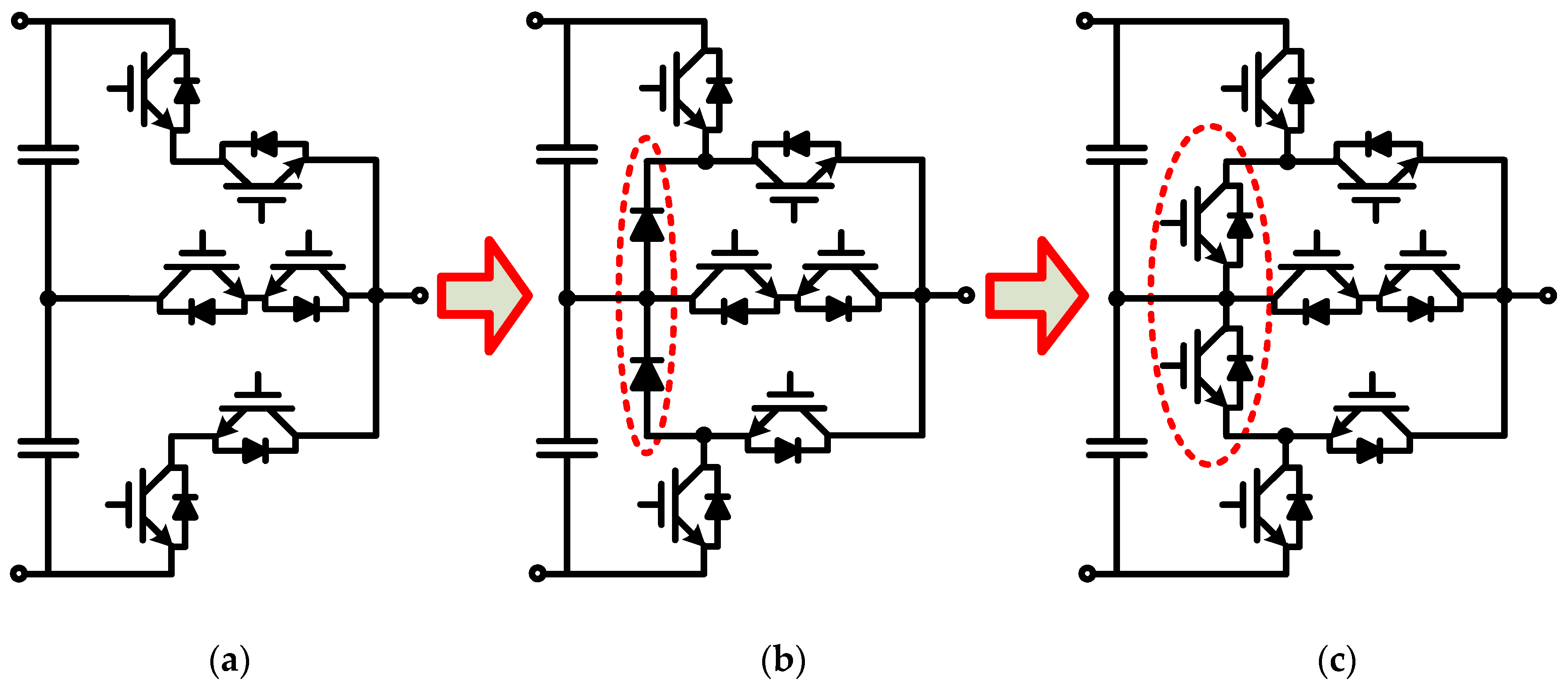

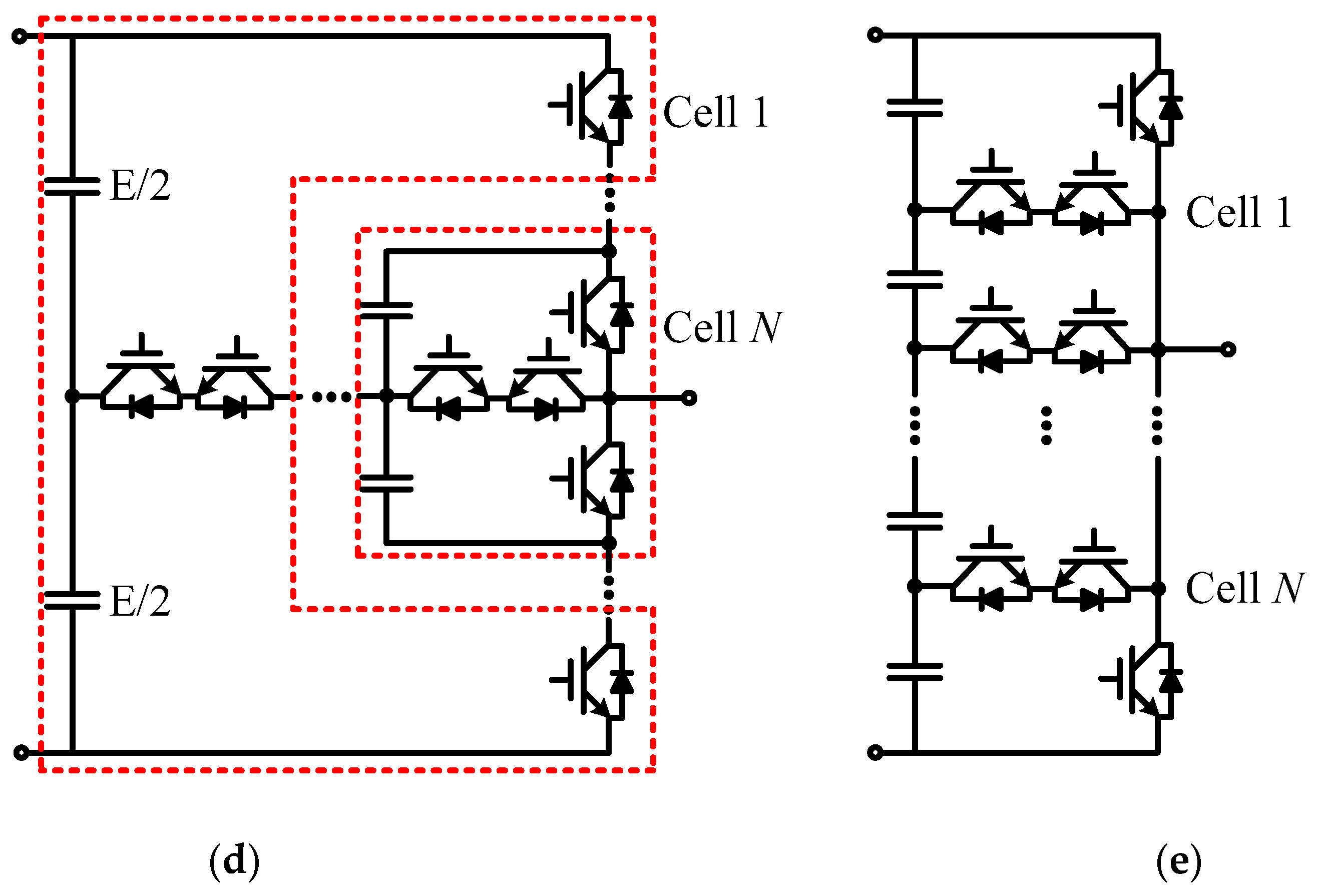

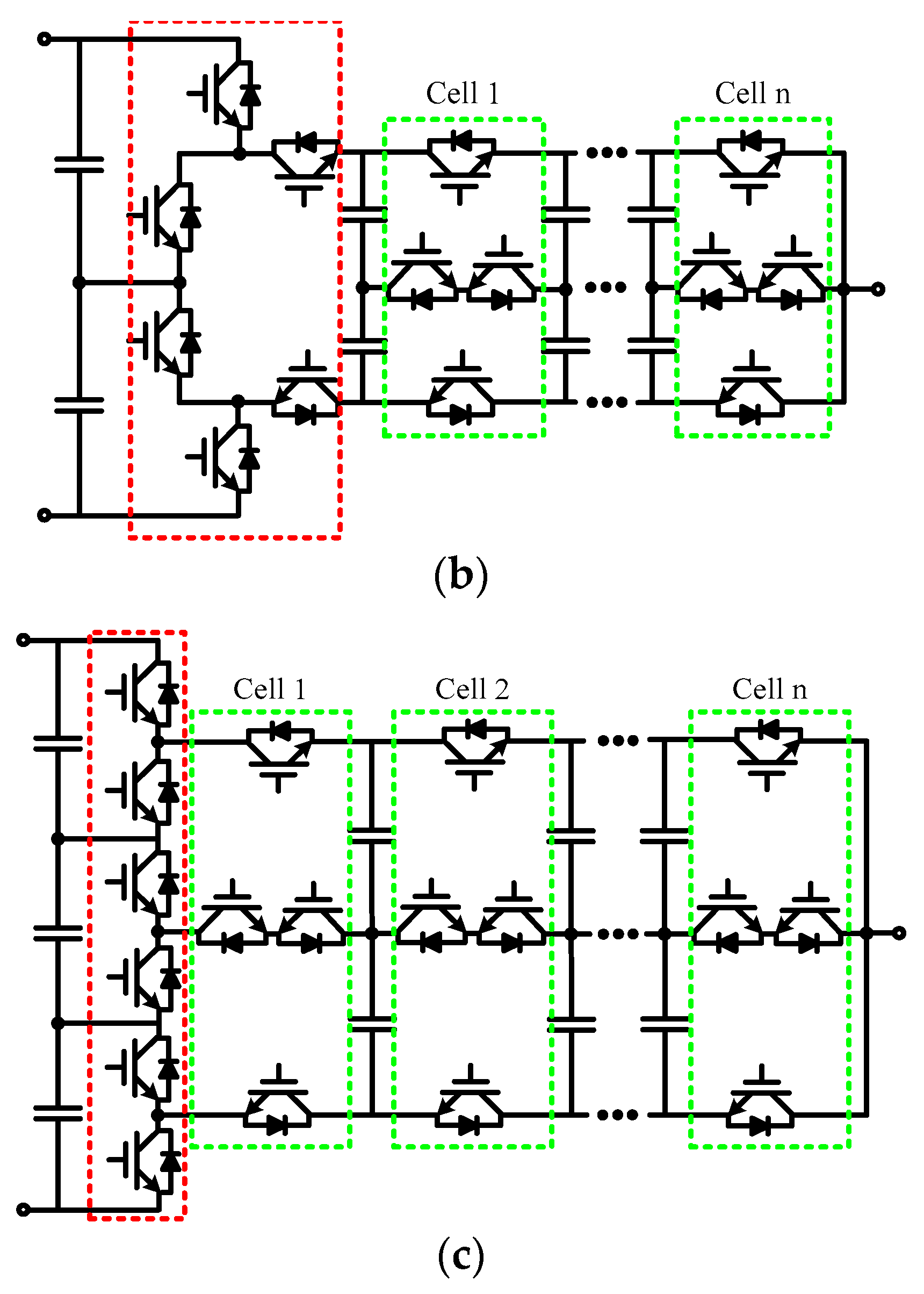

2.5. Hybrid FC-Based Multicell Converters

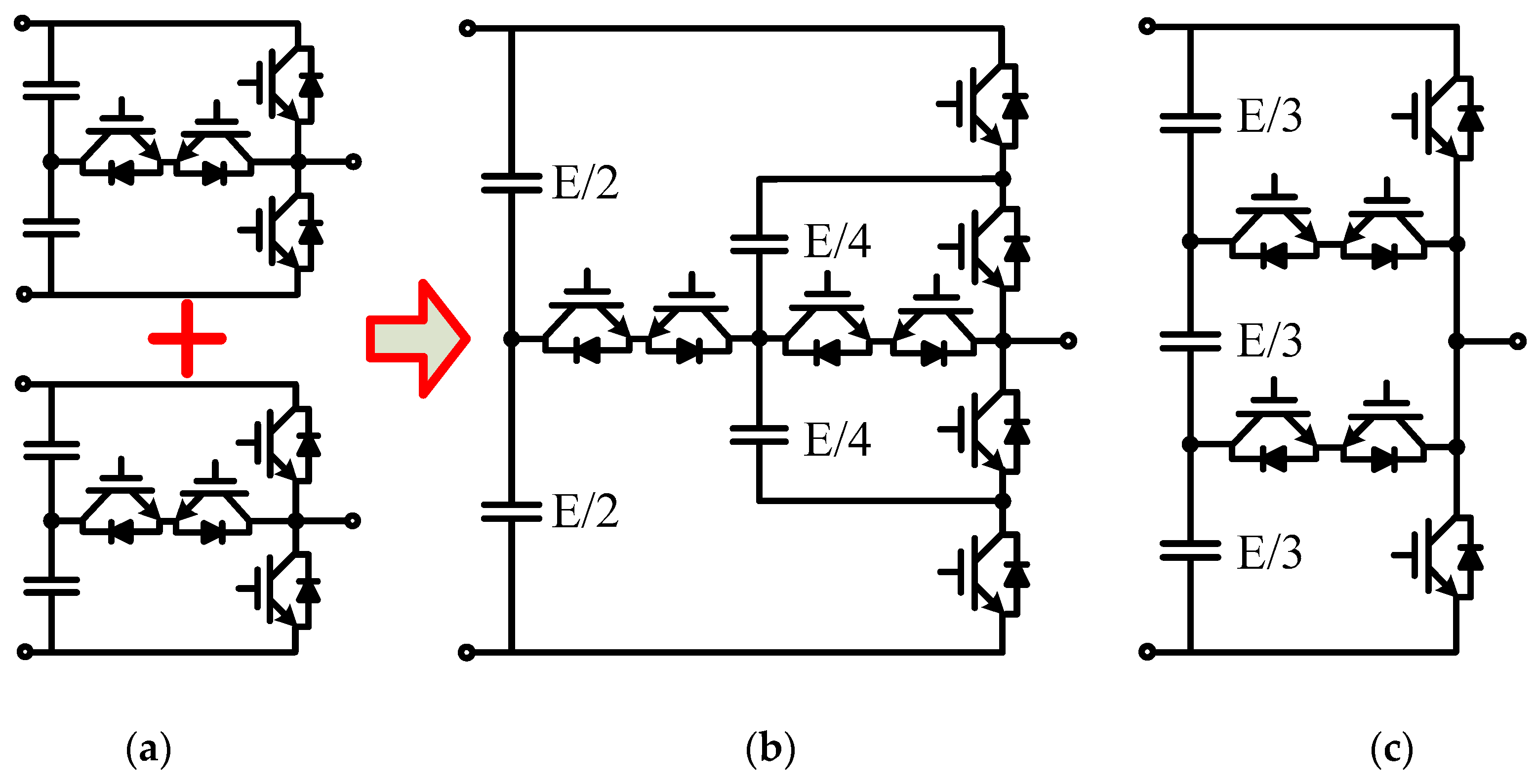

2.6. Hybrid Sub-Module Multilevel Converters

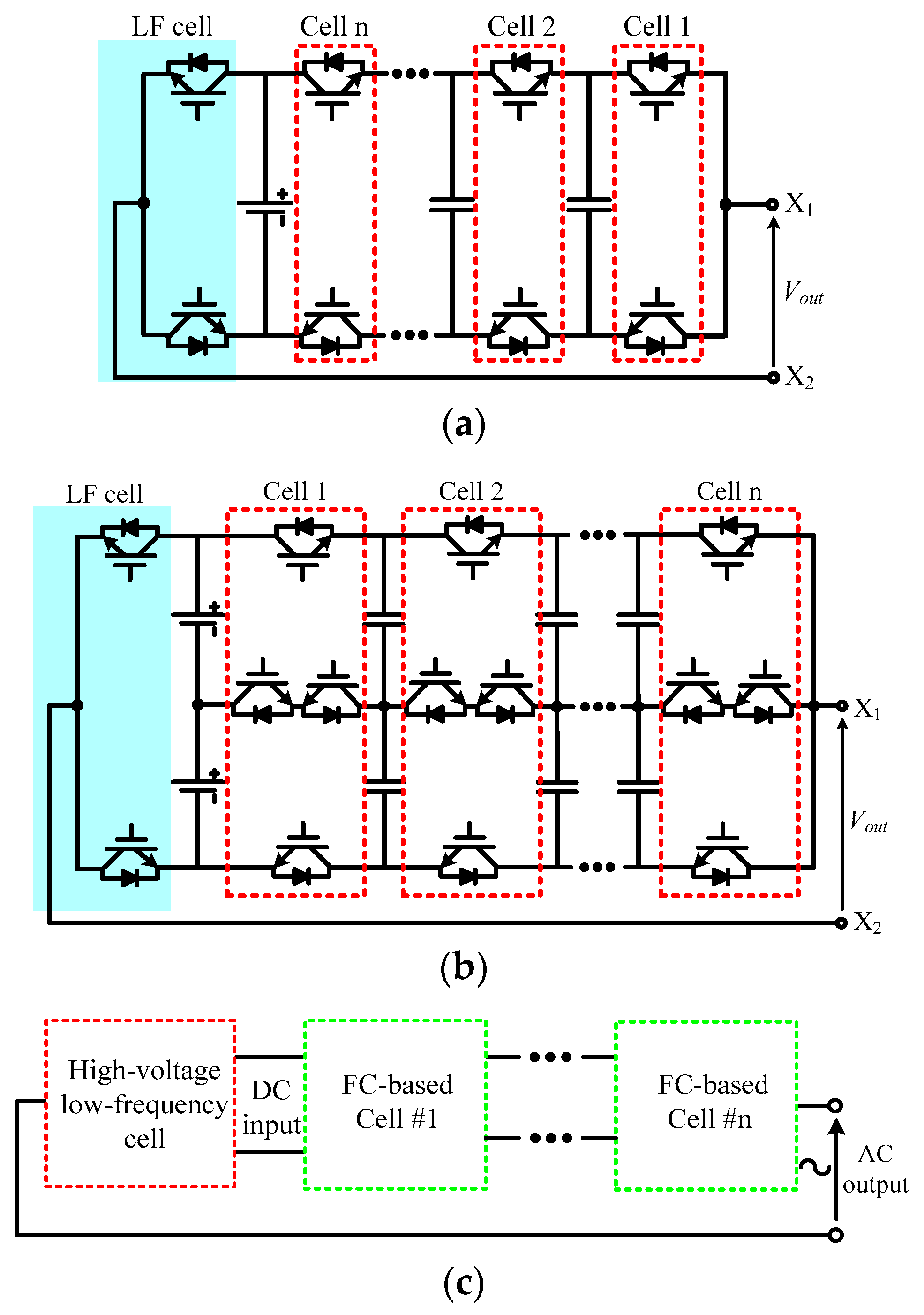

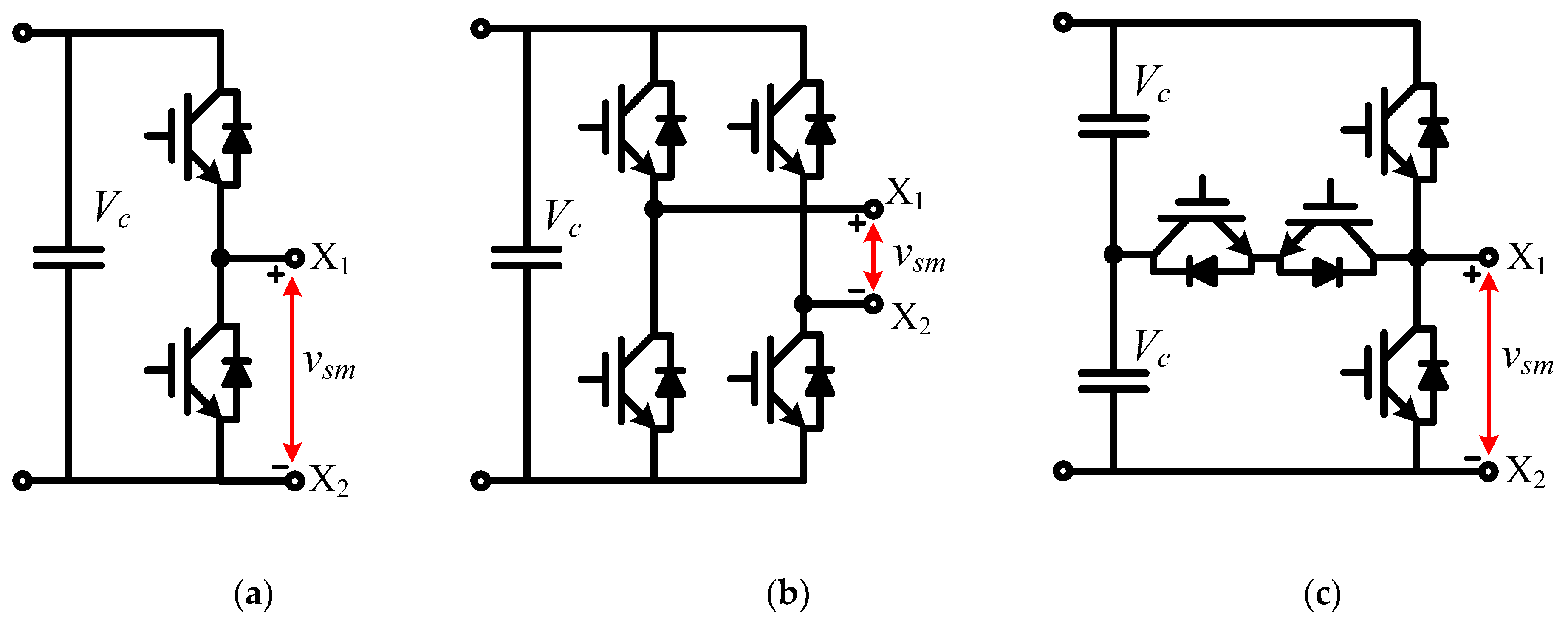

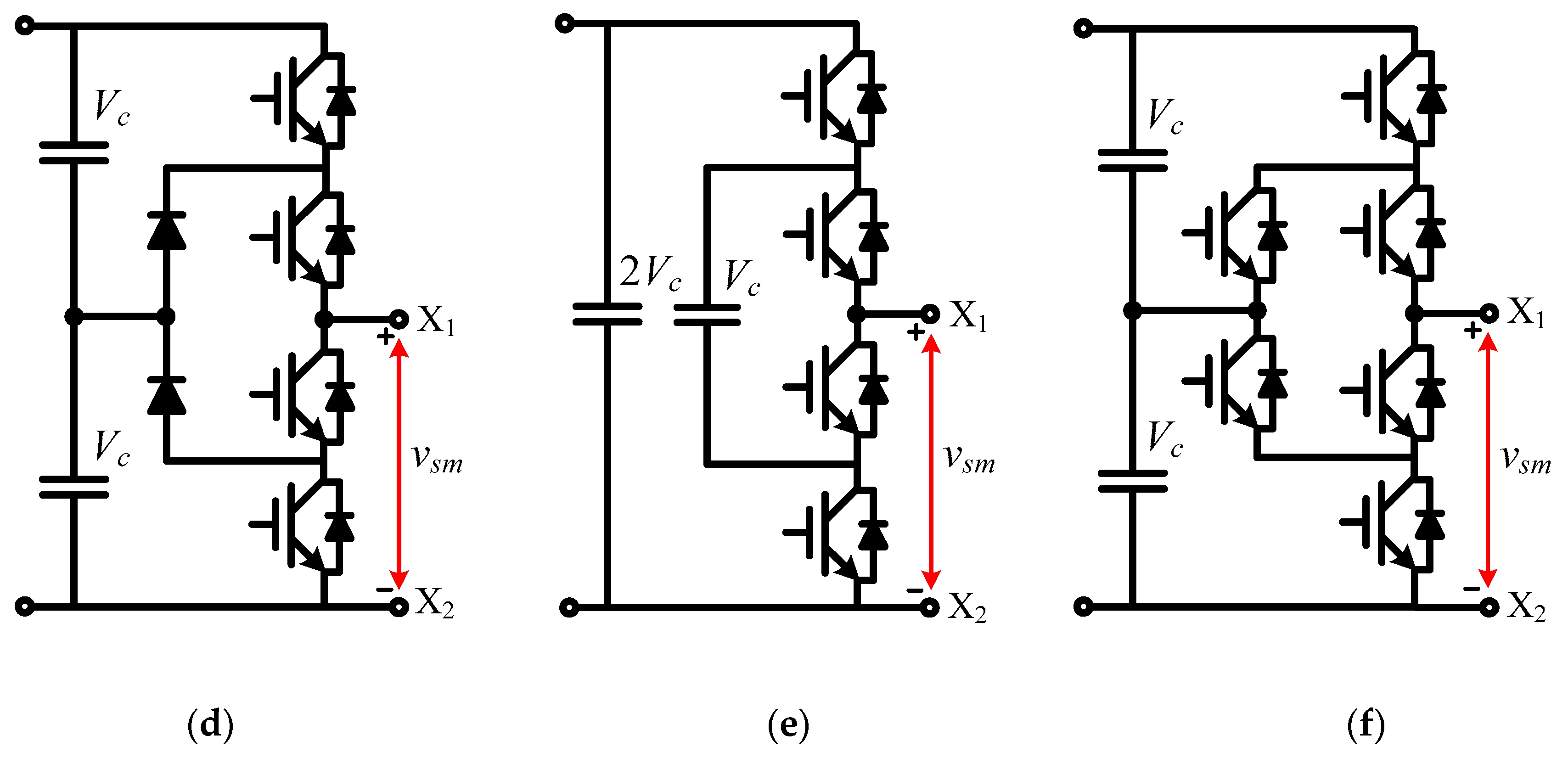

2.6.1. Basic Cells

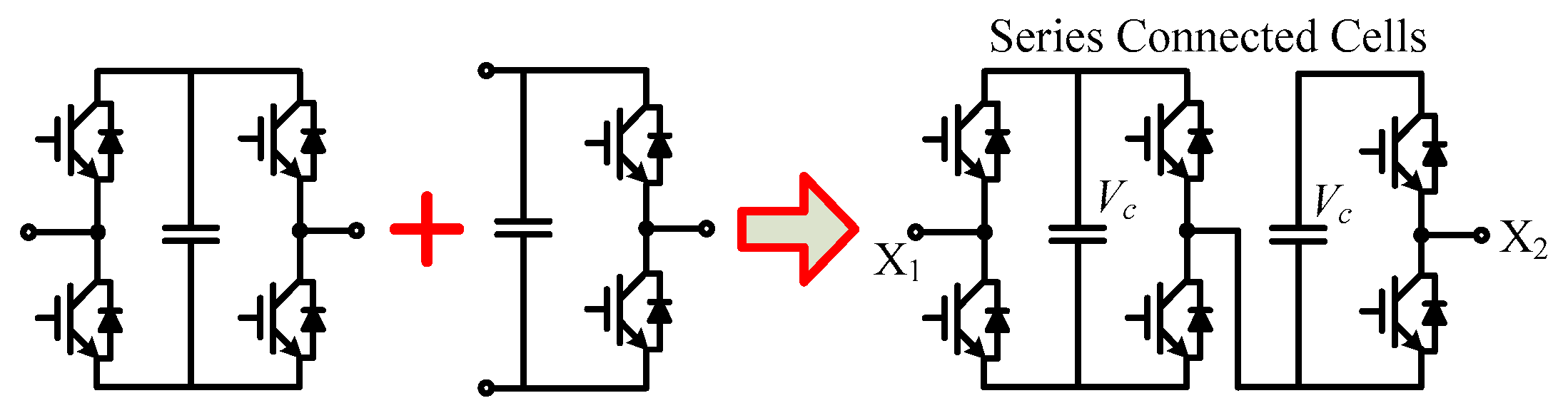

2.6.2. Hybrid Sub-Modules

3. Performance Evaluations of Hybrid FC-Based Multilevel Converters

4. Modulation and Control Strategies

4.1. General Operation and Control Structure

4.2. Pulse Width Modulation Algorithms

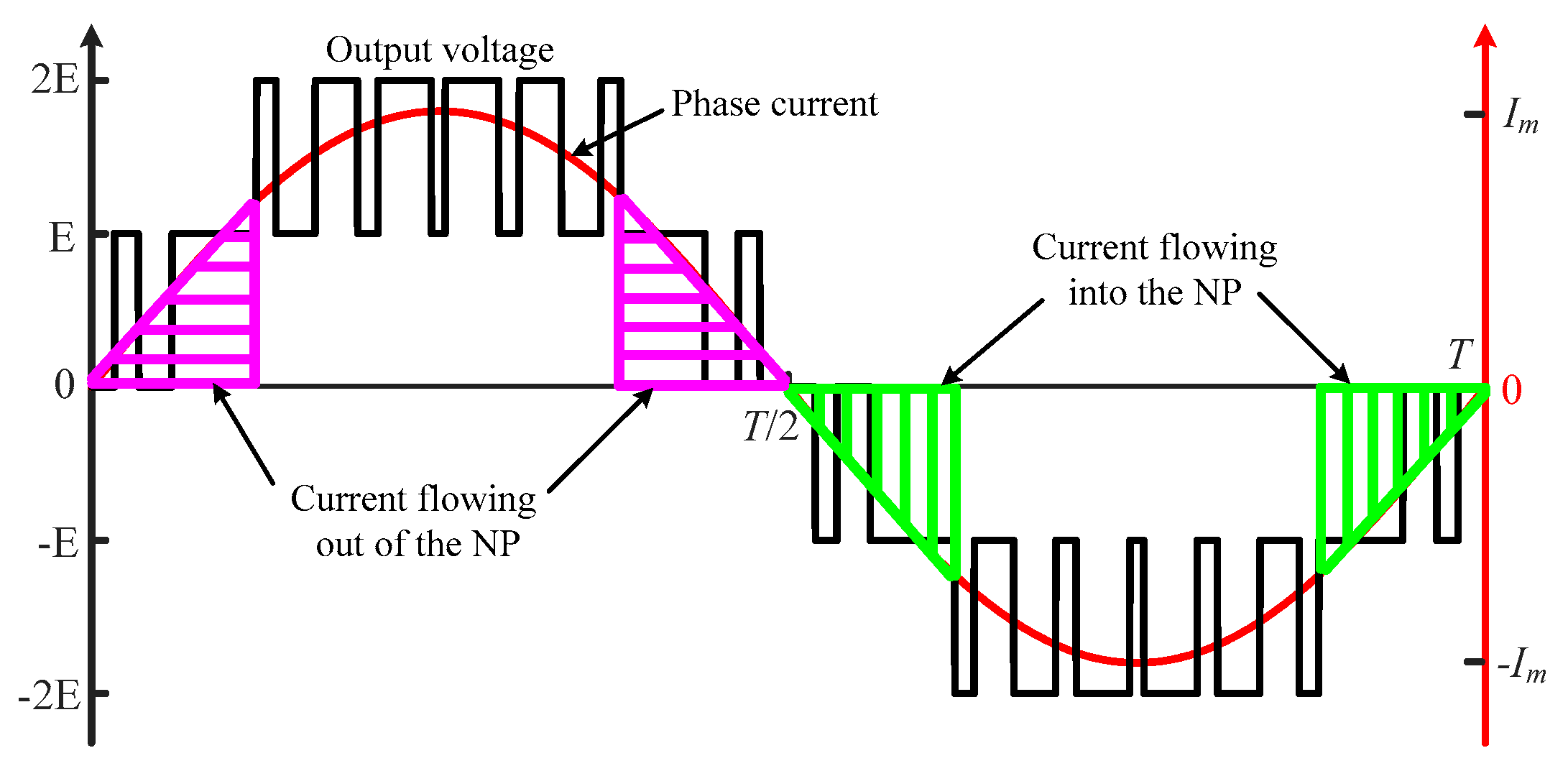

4.3. DC-Link NP Voltage Control

4.4. FC Voltage Balancing Control

5. Operation of Derived HMCs

6. Experimental Validations

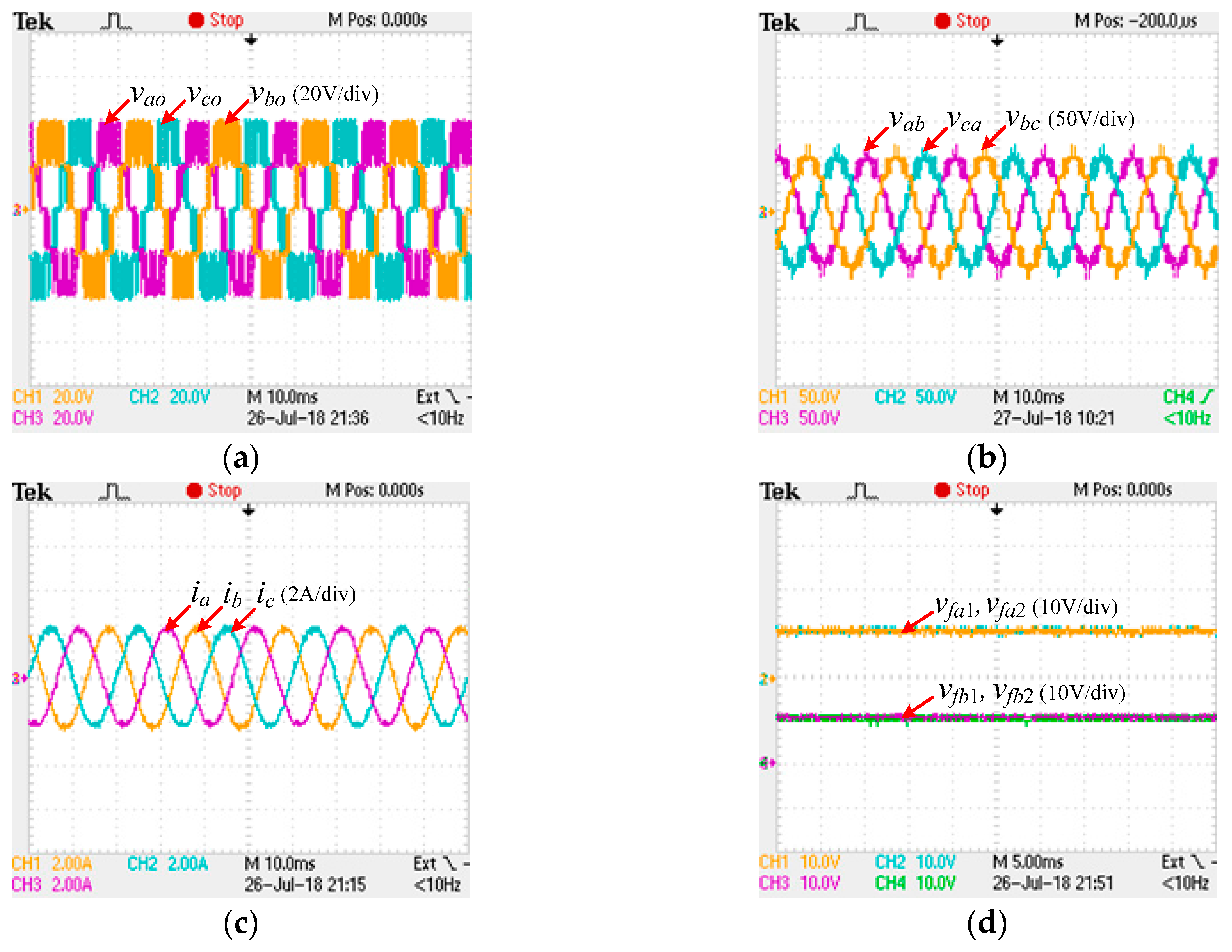

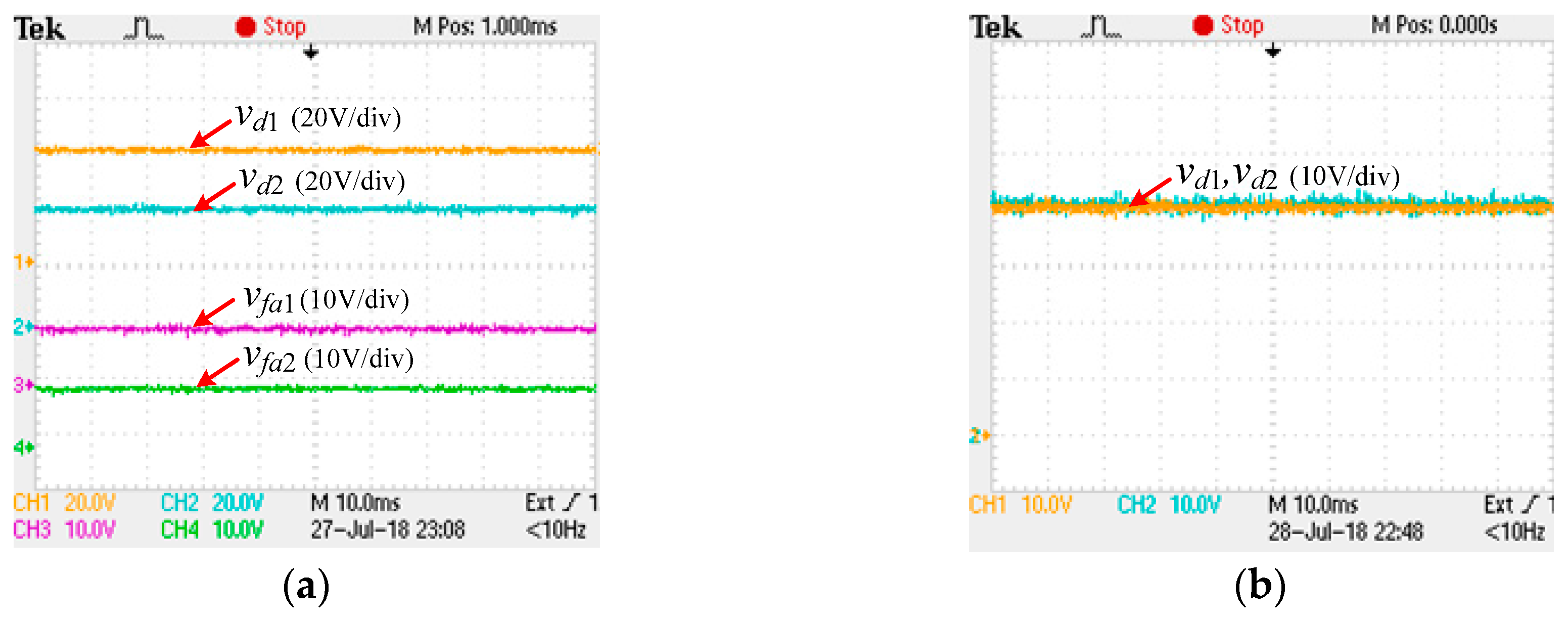

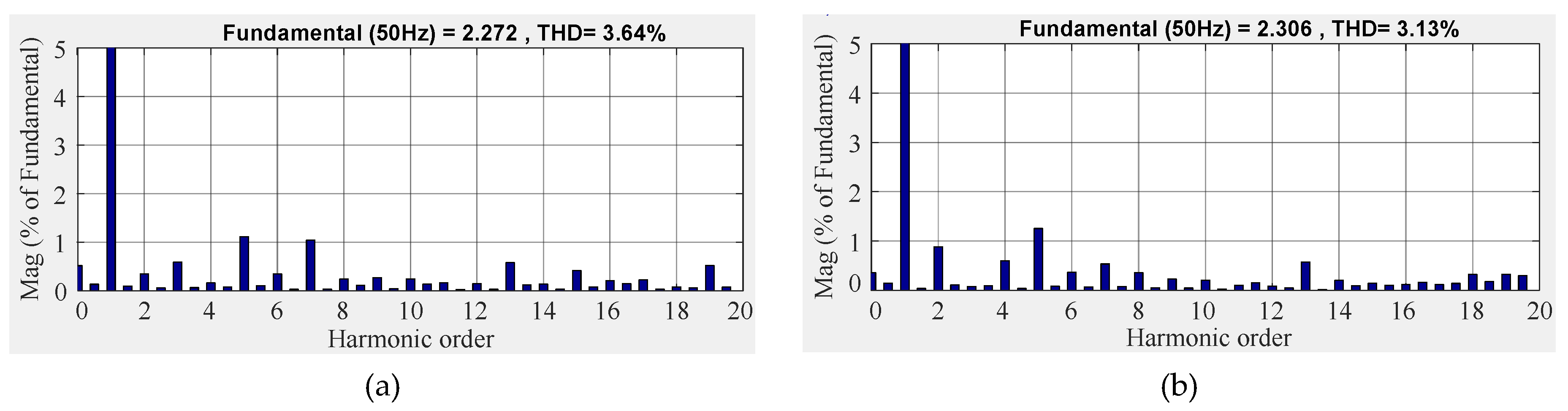

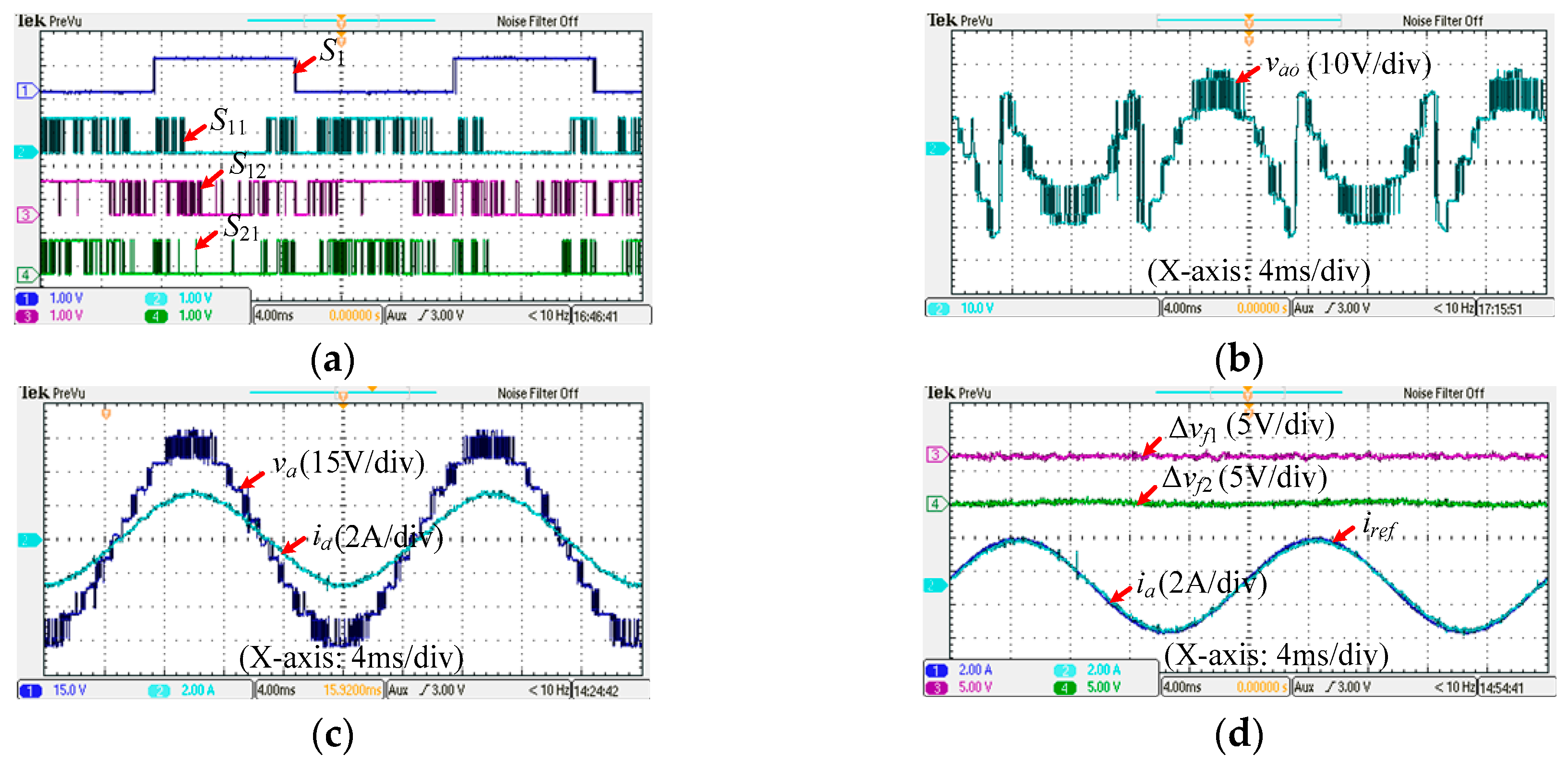

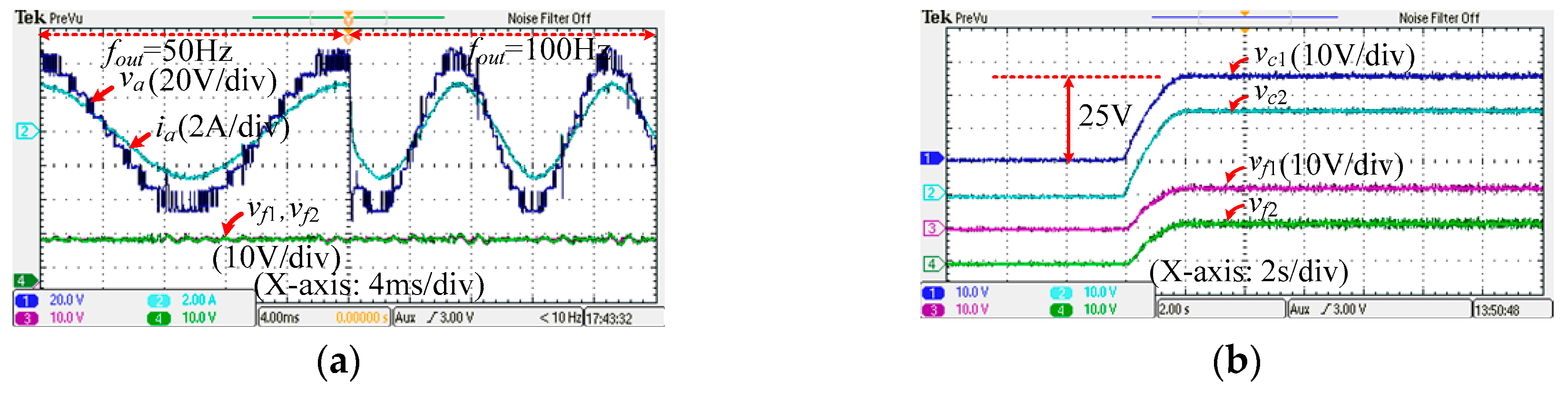

6.1. Five-Level Hybrid T-ANPC Converter

6.2. Seven-Level Hybrid T-ANPC Converter

6.3. Nine-Level Hybrid Stacked Multicell Converter

7. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Rodriguez, J.; Lai, J.S.; Peng, F.Z. Multilevel inverters: A survey of topologies, controls, and applications. IEEE Trans. Ind. Electron. 2002, 49, 724–738. [Google Scholar] [CrossRef]

- Kouro, S.; Malinowski, M.; Gopakumar, K.; Pou, J.; Franquelo, L.G.; Wu, B.; Rodriguez, J.; Perez, M.A.; Leon, J.I. Recent advances and industrial applications of multilevel converters. IEEE Trans. Ind. Electron. 2010, 57, 2553–2580. [Google Scholar] [CrossRef]

- Teichmann, R.; Bernet, S. A comparison of three-level converters versus two-level converters for low-voltage drives, traction, and utility applications. IEEE Trans. Ind. Appl. 2005, 41, 855–865. [Google Scholar] [CrossRef]

- Yuan, X. Derivation of voltage source multilevel converter topologies. IEEE Trans. Ind. Electron. 2017, 64, 966–976. [Google Scholar] [CrossRef]

- Nabae, A.; Takahashi, I.; Akagi, H. A new neutral-point-clamped PWM inverter. IEEE Trans. Ind. Appl. 1981, IA-17, 518–523. [Google Scholar] [CrossRef]

- Rodriguez, J.; Bernet, S.; Steimer, P.K.; Lizama, I.E. A survey on neutral-point-clamped inverters. IEEE Trans. Ind. Electron. 2010, 57, 2219–2230. [Google Scholar] [CrossRef]

- Meynard, T.A.; Foch, H. Multi-level choppers for high voltage applications. EPE J. 1992, 2, 45–50. [Google Scholar] [CrossRef]

- Hammond, P.W. A new approach to enhance power quality for medium voltage ac drives. IEEE Trans. Ind. Appl. 1997, 33, 202–208. [Google Scholar] [CrossRef]

- Malinowski, M.; Gopakumar, K.; Rodriguez, J.; Perez, M.A. A survey on cascaded multilevel inverters. IEEE Trans. Ind. Electron. 2010, 57, 2197–2206. [Google Scholar] [CrossRef]

- Manjrekar, M.D.; Steimer, P.K.; Lipo, T.A. Hybrid multilevel power conversion system: A competitive solution for high-power applications. IEEE Trans. Ind. Appl. 2000, 36, 834–841. [Google Scholar] [CrossRef]

- Hagiwara, M.; Akagi, H. Control and experiment of pulsewidth-modulated modulated multilevel converters. IEEE Trans. Power Electron. 2009, 24, 1737–1746. [Google Scholar] [CrossRef]

- Rech, C.; Pinheiro, J.R. Hybrid multilevel converters: Unified analysis and design considerations. IEEE Trans. Ind. Electron. 2007, 54, 1092–1104. [Google Scholar] [CrossRef]

- Barbosa, P.; Steimer, P.; Steinke, J.; Winkelnkemper, M.; Celanovic, N. Active-neutral-point-clamped (ANPC) multilevel converter technology. In Proceedings of the 2005 European Conference on Power Electronics and Applications, Dresden, Germany, 11–14 September 2005; pp. 1–10. [Google Scholar]

- Bruckner, T.; Bernet, S.; Guldner, H. The active NPC converter and its loss-balancing control. IEEE Trans. Ind. Electron. 2005, 54, 855–868. [Google Scholar] [CrossRef]

- Pulikanti, S.R.; Agelidis, V.G. Hybrid flying-capacitor-based active-neutral-point-clamped five-level converter operated with SHE-PWM. IEEE Trans. Ind. Electron. 2011, 58, 4643–4653. [Google Scholar] [CrossRef]

- Wang, H.; Kou, L.; Liu, Y.-F.; Sen, P.C. A new six-switch five-level active neutral point clamped inverter for PV applications. IEEE Trans. Power Electron. 2017, 32, 6700–6715. [Google Scholar] [CrossRef]

- Naderi, R.; Smedley, K. A new hybrid active neutral point clamped flying capacitor multilevel inverter. In Proceedings of the 2015 IEEE Applied Power Electronics Conference and Exposition (APEC), Charlotte, NC, USA, 15–19 March 2015; pp. 1048–2334. [Google Scholar]

- Holtz, J. Self-communtated inverters with staircase output voltage for large power and high frequency. Siemens Res. Dev. Rep. 1977, 6, 164–171. (In German) [Google Scholar]

- Narimani, M.; Wu, B.; Cheng, Z.; Zargari, N.R. A new nested neutral point-clamped (NNPC) converter for medium-voltage (MV) power conversion. IEEE Trans. Power Electron. 2014, 29, 6375–6382. [Google Scholar] [CrossRef]

- Narimani, M.; Wu, B.; Zargari, N.R. A novel five-level voltage source inverter with sinusoidal pulse width modulator for medium-voltage applications. IEEE Trans. Power Electron. 2016, 31, 1959–1967. [Google Scholar] [CrossRef]

- Narimani, M.; Wu, B.; Zargari, N.R. A novel seven-level voltage source converter for medium-voltage (MV) applications. In Proceedings of the 2015 IEEE Energy Conversion Congress and Exposition (ECCE), Montreal, QC, Canada, 20–24 September 2015; pp. 4277–4282. [Google Scholar]

- Bahrami, A.; Narimani, M. A sinusoidal pulse width modulation (SPWM) technique for capacitor voltage balancing of nested T-type four-level inverter. IEEE Trans. Power Electron. 2019, 34, 1008–1012. [Google Scholar] [CrossRef]

- Schweizer, M.; Kolar, J.W. Design and implementation of a highly efficient three-level T-type converter for low voltage applications. IEEE Trans. Power Electron. 2013, 28, 899–907. [Google Scholar] [CrossRef]

- Xu, S.; Zhang, J.; Hang, J. Investigation of a fault-tolerant three-level T-type inverter system. IEEE Trans. Ind. Appl. 2017, 53, 4613–4623. [Google Scholar] [CrossRef]

- Rodriguez, J.; Bernet, S.; Wu, B.; Point, J.O.; Kouro, S. Multilevel voltage-source-converter topologies for industrial medium-voltage drives. IEEE Trans. Ind. Electron. 2007, 54, 2930–2945. [Google Scholar] [CrossRef]

- Leon, J.I.; Vazquez, S.; Franquelo, L.G. Multilevel converters: Control and modulation techniques for their operation and industrial applications. Proc. IEEE. 2017, 105, 2066–2081. [Google Scholar] [CrossRef]

- Abu-Rub, H.; Holtz, J.; Rodriguez, J.; Baoming, G. Medium-voltage multilevel converters-State of the art, challenges, and requirements in industrial applications. IEEE Trans. Ind. Electron. 2010, 57, 2581–2596. [Google Scholar] [CrossRef]

- Meynard, T.A.; Foch, H.; Forest, F.; Turpin, C. Multicell converters: Derived topologies. IEEE Trans. Ind. Electron. 2002, 49, 978–987. [Google Scholar] [CrossRef]

- Floricau, D.; Gateau, G.; Dumitrescu, M.; Teodorescu, R. A new stacked NPC converter: 3L-topology and control. In Proceedings of the 2007 European Conference on Power Electronics and Applications, Aalborg, Denmark, 2–5 September 2007; pp. 1–10. [Google Scholar]

- Floricau, D.; Gateau, G.; Leredde, A. New active stacked NPC multilevel converter: Operation and features. IEEE Trans. Ind. Electron. 2010, 57, 2272–2278. [Google Scholar] [CrossRef]

- Yuan, X. A four-level π-type converter for low-voltage applications. In Proceedings of the 2015 17th European Conference on Power Electronics and Applications (EPE’15 ECCE-Europe), Geneva, Switzerland, 8–10 September 2015; pp. 1–10. [Google Scholar]

- Naderi, R.; Sadigh, A.K.; Smedley, K.M. Dual flying capacitor active-neutral-point-clamped multilevel converter. IEEE Trans. Power Electron. 2016, 31, 6476–6484. [Google Scholar] [CrossRef]

- Wang, K.; Zheng, Z.; Wei, D.; Fan, B.; Li, Y. Topology and capacitor voltage balancing control of symmetrical hybrid nine-level inverter for high-speed motor drives. IEEE Trans. Ind. Appl. 2017, 53, 5563–5572. [Google Scholar] [CrossRef]

- Viju, N.R.; Arun, R.S.; Kaarthik, R.S.; Kshirsagar, A.; Gopakumar, K. Generation of higher number of voltage levels by stacking inverters of lower multilevel structures with low voltage devices for drives. IEEE Trans. Power Electron. 2017, 32, 52–59. [Google Scholar]

- Veenstra, M.; Rufer, A. Control of a hybrid asymmetric multilevel inverter for competitive medium-voltage industrial drives. IEEE Trans. Ind. Appl. 2005, 41, 655–664. [Google Scholar] [CrossRef]

- Yu, H.; Chen, B.; Yao, W.; Lu, Z. Hybrid seven-level converter based on T-type converter and H-bridge cascaded under SPWM and SVM. IEEE Trans. Power Electron. 2018, 33, 689–702. [Google Scholar] [CrossRef]

- Li, J.; Bhattacharya, S.; Huang, A.Q. A new nine-level active NPC (ANPC) converter for grid connection of large wind turbines for distributed generation. IEEE Trans. Power Electron. 2011, 26, 961–972. [Google Scholar] [CrossRef]

- Kumar, P.R.; Kaarthik, R.S.; Gopakumar, K.; Leon, J.I.; Franquelo, L.G. Seventeen-level inverter formed by cascading flying capacitor and floating capacitor H-bridges. IEEE Trans. Power Electron. 2015, 30, 3471–3478. [Google Scholar] [CrossRef]

- Burguete, E.; López, J.; Zabaleta, M. New five-level active neutral-point-clamped converter. IEEE Trans. Ind. Appl. 2015, 51, 440–447. [Google Scholar] [CrossRef]

- Xu, S.; Zhang, J.; Hu, X.; Jiang, Y. A novel hybrid five-level voltage source converter based on T-type topology for high-efficiency applications. IEEE Trans. Ind. Appl. 2017, 53, 4730–4743. [Google Scholar] [CrossRef]

- Saeedifard, M.; Barbosa, P.M.; Steimer, P.K. Operation and control of a hybrid seven-level converter. IEEE Trans. Power Electron. 2012, 27, 652–660. [Google Scholar] [CrossRef]

- Sadigh, A.K.; Dargahi, V.; Pahlavani, M.R.A.; Shoulaie, A. Elimination of one dc voltage source in stacked multicell converters. IET Power Electron. 2012, 5, 644–658. [Google Scholar] [CrossRef]

- Hosseini, S.H.; Khoshkbar Sadigh, A.; Sabahi, M. New configuration of stacked multicell converter with reduced number of dc voltage sources. In Proceedings of the 5th IET International Conference on Power Electronics, Machines and Drives (PEMD 2010), Brighton, UK, 19–21 April 2010; pp. 1–6. [Google Scholar]

- Sadeghi, M.; Hosseini, S.H.; Alizadeh, R.; Banaei, M.R. New mixed stacked multicell converter with interesting advantages. IET Power Electron. 2012, 5, 1298–1304. [Google Scholar] [CrossRef]

- Sadigh, A.K.; Hosseini, S.H.; Sabahi, M.; Gharehpetian, G.B. Double flying capacitor multicell converter based on modified phase-shifted pulsewidth modulation. IEEE Trans. Power Electron. 2010, 25, 1517–1526. [Google Scholar] [CrossRef]

- Hosseini, S.H.; Sadeghi, M. Reduced stacked multicell converter with minimized stored energy of flying capacitors. In Proceedings of the 2011 2nd IEEE PES International Conference and Exhibition on Innovative Smart Grid Technologies, Manchester, UK, 5–7 December 2011; pp. 1–5. [Google Scholar]

- Ebrahimi, J.; Karshenas, H.R. A new reduced-component hybrid flying capacitor multicell converter. IEEE Trans. Ind. Electron. 2017, 64, 912–921. [Google Scholar] [CrossRef]

- Sandeep, N.; Yaragatti, U.R. Operation and control of a nine-level modified ANPC inverter topology with reduced part count for grid-connected applications. IEEE Trans. Ind. Electron. 2018, 65, 4810–4818. [Google Scholar] [CrossRef]

- Dargahi, V.K.; Corzine, A.; Enslin, J.H.; Abarzadeh, M.; Sadigh, A.K.; Rodriguez, J.; Blaabjerg, F. Duo-active-neutral-point-clamped multilevel converter: An exploration of the fundamental topology and experimental verification. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition (APEC), San Antonio, TX, USA, 4–8 March 2018; pp. 2642–2649. [Google Scholar]

- Zheng, Z.; Wang, K.; Xu, L.; Li, Y. A hybrid cascaded multilevel converter for battery energy management applied in electric vehicles. IEEE Trans. Power Electron. 2014, 29, 3537–3546. [Google Scholar] [CrossRef]

- Peng, F.Z.; Lai, J.S.; McKeever, J.W.; VanCoevering, J. A multilevel voltage-source inverter with separate DC sources for static VAr generation. IEEE Trans. Ind. Appl. 1996, 32, 1130–1138. [Google Scholar] [CrossRef]

- Nami, A.; Liang, J.; Dijkhuizen, F.; Demetriades, G.D. Modular multilevel converters for HVDC applications: Review on converter cells and functionalities. IEEE Trans. Power Electron. 2015, 30, 18–36. [Google Scholar] [CrossRef]

- Hiller, M. Method for Controlling a Polyphase Converter with Distributed Energy Stores. U.S. Patent 12/067, 555, 20 March 2008. [Google Scholar]

- Ilves, K.; Taffner, F.; Norrga, S.; Antonopoulos, A.; Harnefors, L.; Nee, H.-P. A submodule implementation for parallel connection of capacitors in modular multilevel converters. IEEE Trans. Power Electron. 2015, 30, 3518–3527. [Google Scholar] [CrossRef]

- Farhadi, M.; Babaei, E. Cross-switched multilevel inverter: An innovative topology. IET Trans. Power Electron. 2013, 6, 642–651. [Google Scholar] [CrossRef]

- Mathew, E.C.; Ghat, M.B.; Shukla, A. A generalized cross-connected submodule structure for hybrid multilevel converters. IEEE Trans. Ind. Appl. 2016, 52, 3159–3170. [Google Scholar] [CrossRef]

- Wang, Y.; Marquardt, R. Future HVDC-grids employing modular multilevel converters and hybrid DC-breakers. In Proceedings of the 2013 15th European Conference on Power Electronics and Applications (EPE), Lille, France, 3–5 September 2013. [Google Scholar]

- Marquardt, R. Modular multilevel converter topologies with DC-short circuit current limitation. In Proceedings of the 8th International Conference on Power Electronics—ECCE Asia, Jeju, South Korea, 30 May–3 June 2011; pp. 1425–1431. [Google Scholar]

- Li, X.; Song, Q.; Liu, W.; Zhu, Z.; Xu, S. Experiment on DC-fault ride through of MMC using a half-voltage clamp submodule. IEEE J. Emerg. Sel. Top. Power Electron. 2018, 6, 1273–1279. [Google Scholar] [CrossRef]

- Elserougi, A.A.; Massoud, A.M.; Ahmed, S. A switched-capacitor submodule for modular multilevel HVDC converters with DC-fault blocking capability and a reduced number of sensors. IEEE Trans. Power Del. 2016, 31, 313–322. [Google Scholar] [CrossRef]

- Qin, J.; Saeedifard, M.; Rockhill, A.; Zhou, R. Hybrid design of modular multilevel converters for HVDC systems based on various submodule circuits. IEEE Trans. Power Del. 2015, 30, 385–394. [Google Scholar] [CrossRef]

- Nami, A.; Wang, L.; Dijkhuizen, F.; Shukla, A. Five level cross connected cell for cascaded converters. In Proceedings of the 2013 15th European Conference on Power Electronics and Applications (EPE), Lille, France, 3–5 September 2013. [Google Scholar]

- Li, R.; Fletcher, J.E.; Xu, L.; Holliday, D.; Williams, B.W. A hybrid modular multilevel converter with novel three-level cells for DC fault blocking capability. IEEE Trans. Power Del. 2015, 30, 1853–1862. [Google Scholar] [CrossRef]

- Hu, X.; Zhang, J.; Xu, S.; Jiang, Y. Investigation of a new modular multilevel converter with DC fault blocking capability. IEEE Trans. Ind. Appl. 2018. [Google Scholar] [CrossRef]

- Chattopadhyay, S.K.; Chakraborty, C. Multilevel inverters with level doubling network: A new topological variation. In Proceedings of the IECON 2013 39th Annual Conference of the IEEE Industrial Electronics Society, Vienna, Austria, 10–13 November 2013; pp. 6263–6268. [Google Scholar]

- Chattopadhyay, S.K.; Chakraborty, C. A new multilevel inverter topology with self-balancing level doubling network. IEEE Trans. Ind. Electron. 2014, 61, 4622–4631. [Google Scholar] [CrossRef]

- Ji, Y.; Chen, G. A novel three-phase seven-level active clamped converter using H-bridge as a level doubling network. In Proceedings of the IEEE 8th International Power Electronics and Motion Control Conference (IPEMC-ECCE Asia), Hefei, China, 22–26 May 2016; pp. 479–484. [Google Scholar]

- Rajesh, V.; Chattopadhyay, S.K.; Chakraborty, C. Full bridge level doubling network assisted multilevel DC link inverter. In Proceedings of the IEEE 7th Power India International Conference (PIICON), Bikaner, India, 25–27 November 2016; pp. 1–6. [Google Scholar]

- Chattopadhyay, S.K.; Chakraborty, C. A new asymmetric multilevel inverter topology suitable for solar PV applications with varying irradiance. IEEE Trans. Sustain. Energy 2017, 8, 1496–1506. [Google Scholar] [CrossRef]

- Hammami, M.; Grandi, G. Input current and voltage ripple analysis in level doubling network (LDN) cells for H-bridge multilevel inverters. IEEE Trans. Ind. Electron. 2019. [Google Scholar] [CrossRef]

- Dewangan, N.K.; Gurjar, V.S.; Ullah, U.; Zafar, S. A level-doubling network (LDN) for cross-connected sources based multilevel inverter (CCS-MLI). In Proceedings of the IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES), Mumbai, India, 16–19 December 2014; pp. 1–4. [Google Scholar]

- Srndovic, M.; Viatkin, A.; Grandi, G. Grid-connected three-phase H-bridge inverter with level doubling network controlled by staircase modulation techniques. In Proceedings of the 10th International Conference on Integrated Power Electronics Systems, Stuttgart, Germany, 20–22 March 2018; pp. 1–7. [Google Scholar]

- Agelidis, V.G.; Demetriades, G.D.; Flourentzou, N. Recent advances in high-voltage direct-current power transmission systems. In Proceedings of the 2006 IEEE International Conference on Industrial Technology, Mumbai, India, 15–17 December 2006; pp. 206–213. [Google Scholar]

- Akagi, H. Classification, terminology, and application of the modular multilevel cascade converter (MMCC). IEEE Trans. Power Electron. 2011, 26, 3119–3130. [Google Scholar] [CrossRef]

- Hu, X.; Zhang, J.; Xu, S.; Jiang, Y. Extended state observer based fault detection and location method for modular multilevel converters. In Proceedings of the IECON 2016–42nd Annual Conference of the IEEE Industrial Electronics Society, Florence, Italy, 23–26 October 2016; pp. 2166–2171. [Google Scholar]

- Perez, M.; Rodriguez, J.; Pontt, J.; Kouro, S. Power distribution in hybrid multi-module converter with nearest level modulation. In Proceedings of the 2007 IEEE International Symposium on Industrial Electronics, Vigo, Spain, 4–7 June 2007; pp. 736–741. [Google Scholar]

- Ebrahimi, J.; Babaei, E.; Gharehpetian, G.B. A new topology of cascaded multilevel converters with reduced number of components for high-voltage applications. IEEE Trans. Power Electron. 2011, 26, 3109–3118. [Google Scholar] [CrossRef]

- Leon, J.I.; Kouro, S.; Franquelo, L.G.; Rodriguez, J.; Wu, B. The essential role and the continuous evolution of modulation techniques for voltage-source inverters in the past, present, and future power electronics. IEEE Trans. Ind. Electron. 2016, 63, 2688–2701. [Google Scholar] [CrossRef]

- Yao, W.; Hu, H.; Lu, Z. Comparisons of space-vector modulation and carrier-based modulation of multilevel inverter. IEEE Trans. Power Electron. 2008, 23, 45–51. [Google Scholar] [CrossRef]

- McGrath, B.P.; Holmes, D.G. Multicarrier PWM strategies for multilevel inverters. IEEE Trans. Ind. Electron. 2002, 49, 858–867. [Google Scholar] [CrossRef]

- Konstantinou, G.S.; Pulikanti, S.R.; Agelidis, V.G. Generalized modulator for the seven-level flying capacitor based active neutral point clamped converter. In Proceedings of the 3rd IEEE International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Aalborg, Denmark, 25–28 June 2012; pp. 586–591. [Google Scholar]

- Pulikanti, S.; Konstantinou, R.G.S.; Agelidis, V.G. Generalisation of flying capacitor-based active-neutral-point-clamped multilevel converter using voltage-level modulation. IET Power Electron. 2012, 5, 456–466. [Google Scholar] [CrossRef]

- Peng, H.; Xie, R.; Wang, K.; Deng, Y.; He, X.; Zhao, R. A capacitor voltage balancing method with fundamental sorting frequency for modular multilevel converters under staircase modulation. IEEE Trans. Power Electron. 2016, 31, 7809–7822. [Google Scholar] [CrossRef]

- Napoles, J.; Leon, J.I.; Portillo, R.L.; Franquelo, G.; Aguirre, M.A. Selective harmonic mitigation technique for high-power converters. IEEE Trans. Ind. Electron. 2010, 57, 2315–2323. [Google Scholar] [CrossRef]

- Vazquez, S.; Rodriguez, J.; Rivera, M.; Franquelo, L.G.; Norambuena, M. Model predictive control for power converters and drives: Advances and trends. IEEE Trans. Ind. Electron. 2017, 64, 935–947. [Google Scholar] [CrossRef]

- Wang, C.; Li, Y. Analysis and calculation of zero-sequence voltage considering neutral-point potential balancing in three-phase NPC converters. IEEE Trans. Ind. Electron. 2010, 57, 2262–2271. [Google Scholar] [CrossRef]

- Pou, J.; Zaragoza, J.; Ceballos, S.; Saeedifard, M.; Boroyevich, D. A carrier-based PWM strategy with zero-sequence voltage injection for a three-level neutral-point-clamped converter. IEEE Trans. Power Electron. 2012, 27, 642–651. [Google Scholar] [CrossRef]

- Tan, L.; Wu, B.; Narimani, M.; Xu, D.; Joos, G. Multicarrier-based PWM strategies with complete voltage balance control for NNPC Inverters. IEEE Trans. Ind. Electron. 2018, 65, 2863–2872. [Google Scholar] [CrossRef]

- Wang, K.; Zheng, Z.; Li, Y.; Liu, K.; Shang, J. Neutral-point potential balancing of a five-level active neutral-point-clamped inverter. IEEE Trans. Ind. Electron. 2013, 60, 1907–1918. [Google Scholar] [CrossRef]

- Li, Y.; Gao, Y.; Hou, X. A general SVM algorithm for multilevel converters considering zero-sequence component control. In Proceedings of the 31st Annual Conference of IEEE Industrial Electronics Society, Raleigh, NC, USA, 6–10 November 2015; pp. 1–6. [Google Scholar]

- Li, J.; Jiang, J. Active capacitor voltage balancing methods based on dynamic model for five-level nested neutral point piloted converter. IEEE Trans. Power Electron. 2018, 33, 6567–6581. [Google Scholar] [CrossRef]

- Smida, M.B.; Ammar, F.B. Modeling and DBC-PSC-PWM control of a three-phase flying-capacitor stacked multilevel voltage source inverter. IEEE Trans. Ind. Electron. 2010, 57, 2231–2239. [Google Scholar] [CrossRef]

- Wilkinson, R.H.; Meynard, T.A.; du Toit Mouton, H. Nature balance of multicell converters: The general case. IEEE Trans. Power Electron. 2006, 21, 1658–1666. [Google Scholar] [CrossRef]

- McGrath, B.P.; Holmes, D.G. Enhanced voltage balancing of a flying capacitor multilevel converter using phase disposition(PD) modulation. IEEE Trans. Power Electron. 2011, 26, 1933–1942. [Google Scholar] [CrossRef]

- Shukla, A.; Ghosh, A.; Joshi, A. Natural balancing of flying capacitor voltages in multicell inverter under PD carrier-based PWM. IEEE Trans. Power Electron. 2011, 26, 1682–1693. [Google Scholar] [CrossRef]

- Li, J.; Jiang, J.; Qiao, S. A space vector pulse width modulation for five-level nested neutral point piloted converter. IEEE Trans. Power Electron. 2017, 32, 5991–6004. [Google Scholar] [CrossRef]

- Ghias, A.M.Y.M.; Pou, J.; Agelidis, V.G. Voltage-balancing method for stacked multicell converters using phase-disposition PWM. IEEE Trans. Ind. Electron. 2015, 62, 4001–4010. [Google Scholar] [CrossRef]

- Ghias, A.M.Y.M.; Pou, J.; Agelidis, V.G. An active voltage-balancing method based on phase-shifted PWM for stacked multicell converters. IEEE Trans. Power Electron. 2016, 31, 1921–1930. [Google Scholar] [CrossRef]

| Topologies | Number of Devices | Output Voltage (p.u) | Total Standing Voltage (p.u) | |||

|---|---|---|---|---|---|---|

| LF Switch | HF Switch | FC | dc Source | |||

| FCC [7] | 0 | 16 | 7 | 1 | 1 | 2 |

| ANPC [13] | 4 | 8 | 3 | 1 | 1 | 3 |

| SM [28,40] | 0 4 | 16 10 | 6 4 | 1 1 | 1 1 | 3 6 |

| [50] | 4 | 8 | 0 | 4 | 2 | 6 |

| [34] | 2 | 12 | 3 | 2 | 1 | 4.5 |

| [37] | 4 | 8 | 2 | 1 | 1 | 7 |

| [33] | 4 | 8 | 2 | 1 | 1 | 6 |

| HSM [46] | 2 | 8 | 2 | 1 | 2 | 5 |

| Topologies | Stored Energy in Capacitors |

|---|---|

| FCC [7] | |

| ANPC [13] | |

| SM [28] | |

| HSM [46] |

| Topologies | IGBTs | FCs | DC Source | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Vdc | Vdc/2 | Vdc/4 | Vdc/8 | Vdc/4 | Vdc/8 | 3Vdc/8 | Vdc/2 | Vdc | Vdc/2 | Vdc/8 | |

| FCC [7] | 0 | 0 | 0 | 16 | 0 | 28 | 0 | 0 | 1 | 0 | 0 |

| ANPC [13] | 0 | 4 | 0 | 8 | 1 | 1 | 1 | 0 | 0 | 2 | 0 |

| SM [28] | 0 | 0 | 8 | 16 | 2 | 2 | 2 | 0 | 0 | 2 | 0 |

| HSM [46] | 2 | 4 | 4 | 0 | 2 | 0 | 0 | 2 | 0 | 2 | 0 |

| Topologies | FC cell | Number of Devices | ||

|---|---|---|---|---|

| LF switch | HF switch | FC | ||

| FCC [7] | n − 1 | 0 | 2(n − 1) | n − 2 |

| SM [28] | n − 1 | 0 | 2(n − 1) | n − 3 |

| [40] | (n − 1)/2 | 6 | n − 1 | (n − 1)/2 |

| [41] | 2[log2(n − 1)/3] + 2 | 6 | 4[log2(n − 1)/3] + 4 | 2[log2(n − 1)/3] |

| HSM [46] | (n − 1)/2 | 2 | n − 1 | (n − 5)/2 |

| Topology | Advantage | Disadvantage | Modulation Technique | Commercial Products |

|---|---|---|---|---|

| NPC [1,2,3,4,5,6] | ① Simple structure; ② Equalized blocking voltage of power switches. | ① Unequal distribution of power losses; ② DC-link voltage balance limits the converter to three-level topology. | ① PWM carrier modulation (based zero-sequence injection); ② SVPWM method (based space vector selection). | SM150 (Siemens), ACS1000 (ABB) FACTs, motor driver. |

| FCC [7,25,26,27,28] | ① Modular structure; ② Owning a high number of redundant states. | ① The poor dynamic response of dc voltage balancing; ② Large amounts of flying capacitors reduce the system reliability. | ① Phase-shifted carrier PWM (achieves neutral balancing of flying capacitors). | ALSPA VDM6000 (Alstom) FACTs, motor driver. |

| CHB [8,9] | ① Modular structure; ②. Owning fault tolerant capability. | ① Require independent dc source; ② Isolated transformers increase the system volume. | ① Phase-shifted carrier PWM (achieves equalization of power losses). | GH180 (Siemens), PCS6000 (ABB) FACTs, motor driver. |

| MMC [52,53,54,55,56,57,58,59,60,61,62,63,64,65,66,67,68,69,70,71,72,73,74,75] | ① Modular structure; ② Easy to achieve fault tolerant operation. | ① Low frequency voltage oscillation of floating capacitors; ②. Complex data acquisition and communication for each power cell. | ① Nearest level modulation (achieves equalization of power losses and dc voltage balance). | SM120 (Siemens) HVDC, wind power application. |

| T-type NPC [18,23,24,25,26,27] | ① Simple structure; ② Low conduction losses. | ① Outer switches have to withstand the entire dc-link voltage; ② Not suitable for a high-voltage range | ① PWM carrier modulation (based zero-sequence injection); ② SVPWM method (based space vector selection). | Solar Ware Samuri (TMEIC) PV application. |

| NNPP (SM converter) [28,42,43,44] | ① Modular structure; ② Owning a high number of redundant states. | ① Unequal blocking voltage of switches. ② Large amounts of flying capacitors reduce the system reliability. | ① Phase-shifted carrier PWM (achieves neutral balancing of flying capacitors). | MV6 (GE) Motor driver. |

| Active NPC [13,14,15,16,17] | ① Simple structure; ② Easily extendable to a higher level by stacking flying capacitor cells. | ① Unequal usage of switches and flying capacitors. ② Require series switches to handle high voltage. | ① Hybrid phase-shifted PWM (low frequency for high voltage switches and high frequency for flying capacitor cells) | ACS2000 (ABB) Motor driver. |

| Switching State | LF Switches | HF Switches | Output Voltage vao | if1 | if2 | Cf1, Cf2 (ia > 0) | |

|---|---|---|---|---|---|---|---|

| S1 S2 | S3 S11 S12 | ||||||

| V1 | 1 1 | 1 1 1 | Vdc/2 | — | — | — | — |

| V2 | 1 1 | 1 0 1 | Vdc/4 | ia | — | C | — |

| V3 | 1 1 | 0 0 1 | Vdc/4 | — | −ia | — | D |

| V4 | 1 1 | 1 0 0 | 0 | ia | ia | C | C |

| V5 | 1 1 | 0 0 0 | 0 | — | — | — | — |

| V6 | 0 0 | 1 1 1 | 0 | — | — | — | — |

| V7 | 0 0 | 0 1 1 | 0 | −ia | −ia | D | D |

| V8 | 0 0 | 0 0 1 | −Vdc/4 | — | −ia | — | D |

| V9 | 0 0 | 1 0 1 | −Vdc/4 | ia | — | C | — |

| V10 | 0 0 | 0 0 0 | −Vdc/2 | — | — | — | — |

| Switching State | LF Switches | HF Switches | Output Voltage vao | if1 | if2 | Cf1, Cf2 (ia > 0) | |

|---|---|---|---|---|---|---|---|

| S1 S2 | S3 S11 S12 | ||||||

| V1 | 1 1 | 1 1 1 | Vdc/2 | — | — | — | — |

| V2 | 1 1 | 1 0 1 | Vdc/3 | ia | — | C | — |

| V3 | 1 1 | 0 1 1 | Vdc/3 | −ia | −ia | D | D |

| V4 | 1 1 | 1 0 0 | Vdc/6 | ia | ia | C | C |

| V5 | 1 1 | 0 0 1 | Vdc/6 | — | −ia | — | D |

| V6 | 1 1 | 0 0 0 | 0 | — | — | — | — |

| V7 | 0 0 | 1 1 1 | 0 | — | — | — | — |

| V8 | 0 0 | 0 1 1 | −Vdc/6 | −ia | −ia | D | D |

| V9 | 0 0 | 1 0 1 | −Vdc/6 | ia | — | C | — |

| V10 | 0 0 | 1 0 0 | −Vdc/3 | ia | ia | C | C |

| V11 | 0 0 | 0 0 1 | −Vdc/3 | — | −ia | — | D |

| V12 | 0 0 | 0 0 0 | −Vdc/2 | — | — | — | — |

| Switching State | LF-Cell Switch | HF-Cell Switches | Output Voltage va | if1, if2 | Cf1, Cf2 (ia > 0) | ||

|---|---|---|---|---|---|---|---|

| S1 | S11 S12 S21 S22 | ||||||

| V1 V2 | 0 0 | 1 1 1 1 1 1 0 1 | Vdc 3Vdc/4 | — ia | — — | — C | — — |

| V3 V4 | 0 0 | 0 1 1 1 0 1 0 1 | 3Vdc/4 Vdc/2 | −ia — | — — | D — | — — |

| V5 V6 | 0 0 | 0 0 1 1 1 1 0 0 | Vdc/2 Vdc/2 | −ia ia | −ia ia | D C | D C |

| V7 V8 | 0 0 | 0 1 0 0 0 0 0 1 | Vdc/4 Vdc/4 | — — | ia −ia | — — | C D |

| V9 V10 | 0 1 | 0 0 0 0 1 1 1 1 | 0 0 | — — | — — | — — | — — |

| V11 V12 | 1 1 | 0 1 1 1 1 1 0 1 | −Vdc/4 −Vdc/4 | −ia ia | — — | D C | — — |

| V13 V14 | 1 1 | 0 1 0 1 1 1 0 0 | −Vdc/2 −Vdc/2 | — ia | — ia | — C | — C |

| V15 V16 | 1 1 | 0 0 1 1 0 0 0 1 | −Vdc/2 −3Vdc/4 | −ia — | −ia −ia | D — | D D |

| V17 V18 | 1 1 | 0 1 0 0 0 0 0 0 | −3Vdc/4 −Vdc | — — | ia — | — — | C — |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, J.; Xu, S.; Din, Z.; Hu, X. Hybrid Multilevel Converters: Topologies, Evolutions and Verifications. Energies 2019, 12, 615. https://doi.org/10.3390/en12040615

Zhang J, Xu S, Din Z, Hu X. Hybrid Multilevel Converters: Topologies, Evolutions and Verifications. Energies. 2019; 12(4):615. https://doi.org/10.3390/en12040615

Chicago/Turabian StyleZhang, Jianzhong, Shuai Xu, Zakiud Din, and Xing Hu. 2019. "Hybrid Multilevel Converters: Topologies, Evolutions and Verifications" Energies 12, no. 4: 615. https://doi.org/10.3390/en12040615

APA StyleZhang, J., Xu, S., Din, Z., & Hu, X. (2019). Hybrid Multilevel Converters: Topologies, Evolutions and Verifications. Energies, 12(4), 615. https://doi.org/10.3390/en12040615