An Output Capacitor-Less Low-Dropout Regulator with 0–100 mA Wide Load Current Range

Abstract

1. Introduction

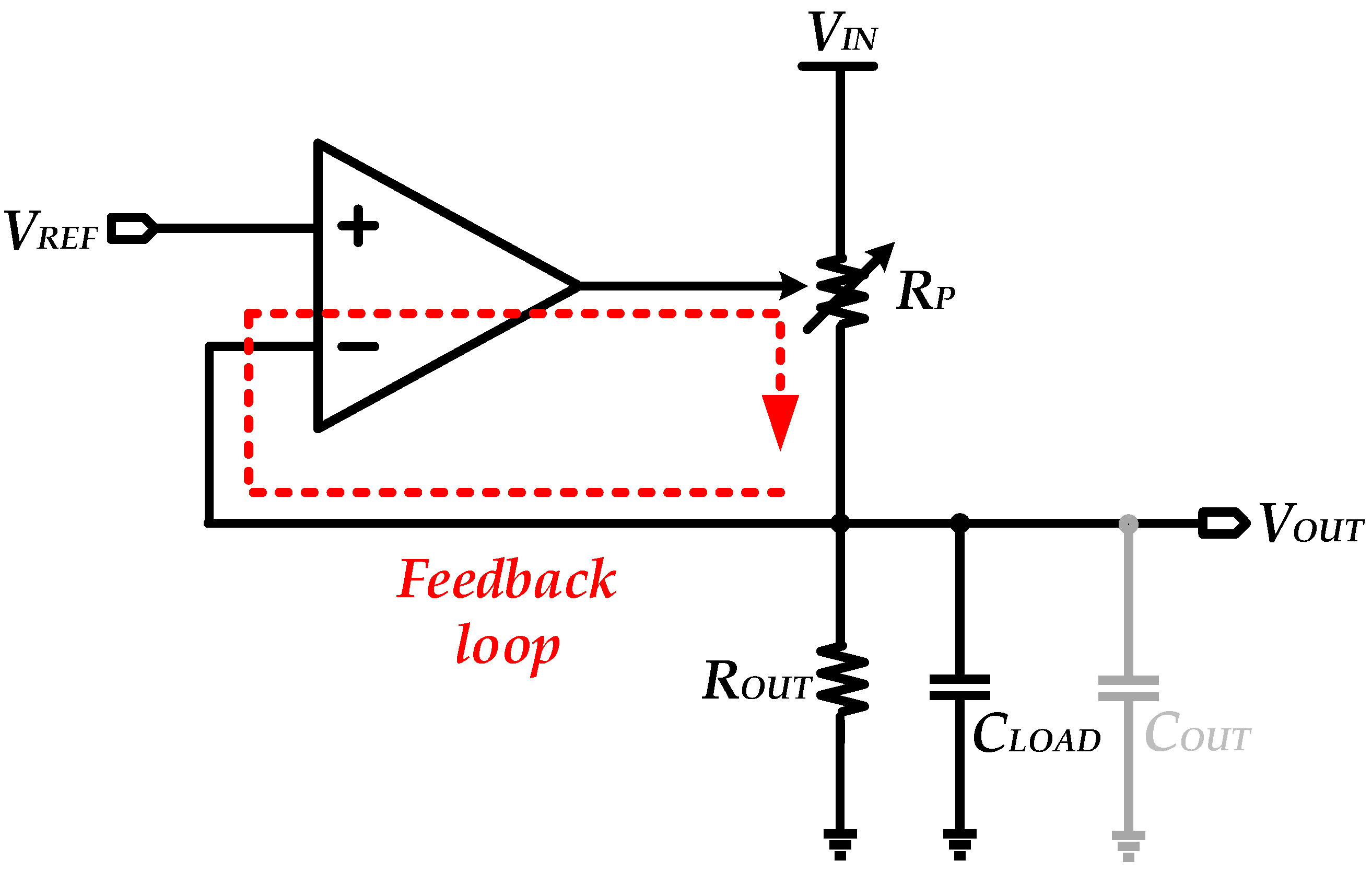

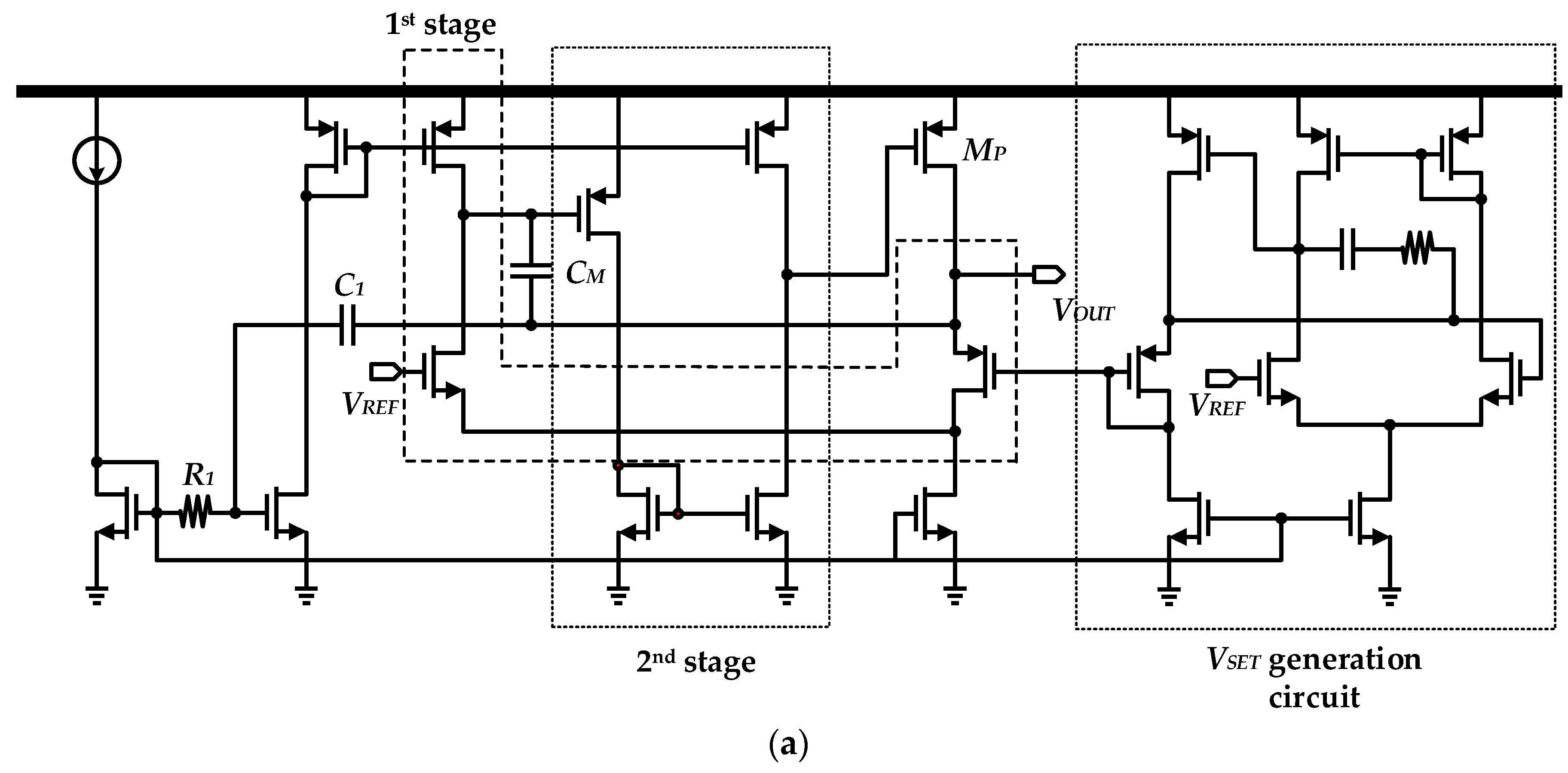

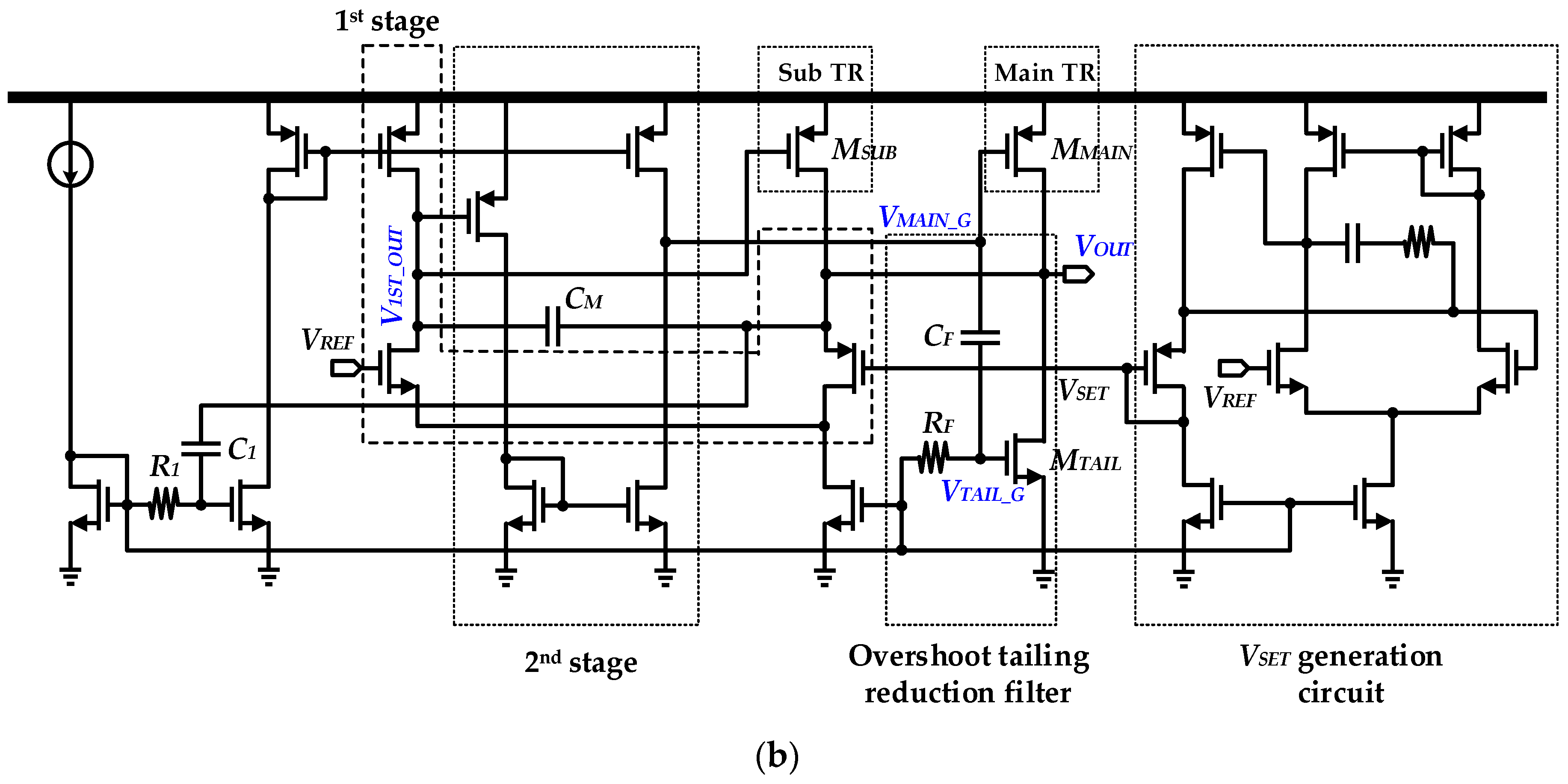

2. Conventional LDO Regulators

2.1. Output Capacitor-Less LDO Regulator

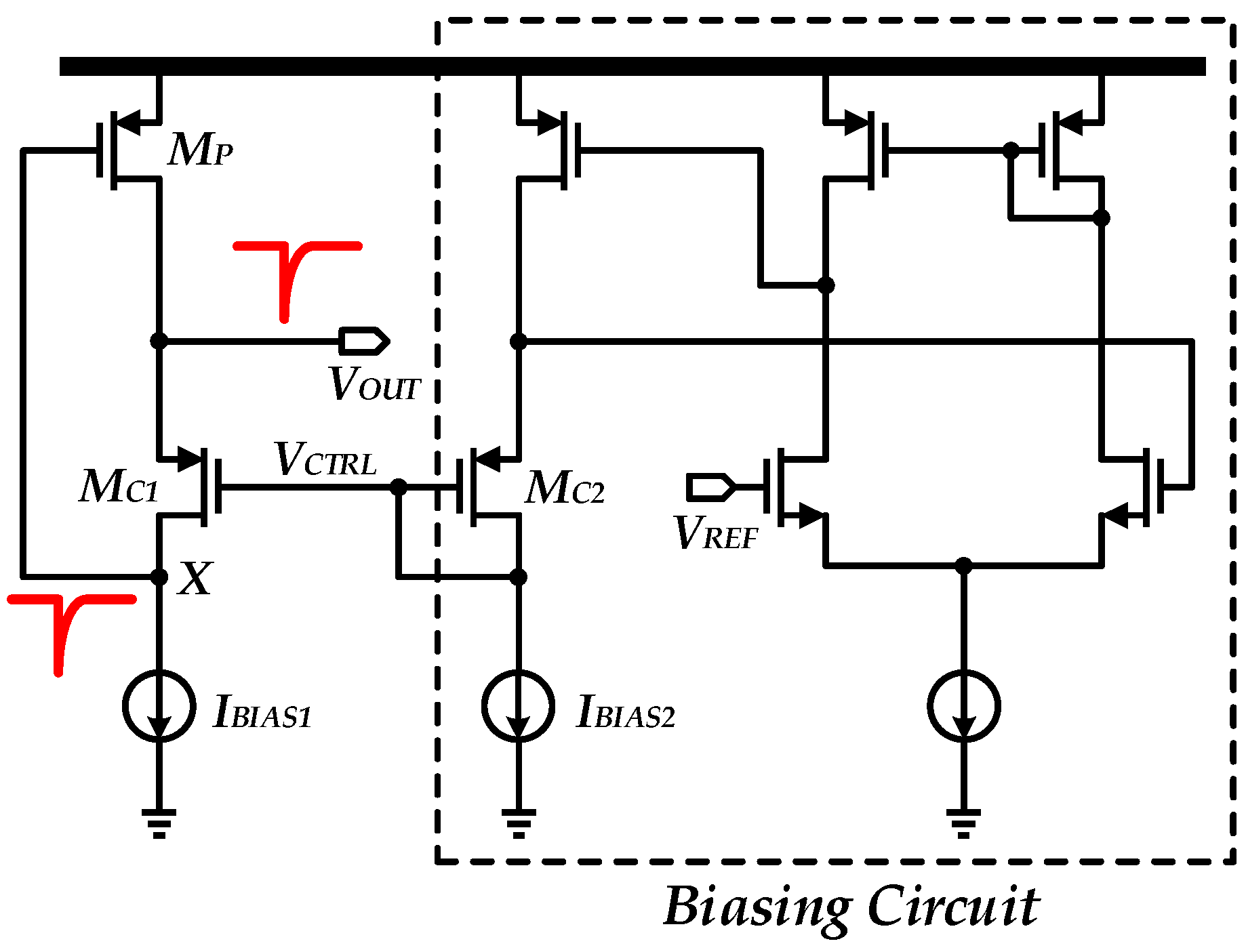

2.2. FVF-Based LDO Regulator

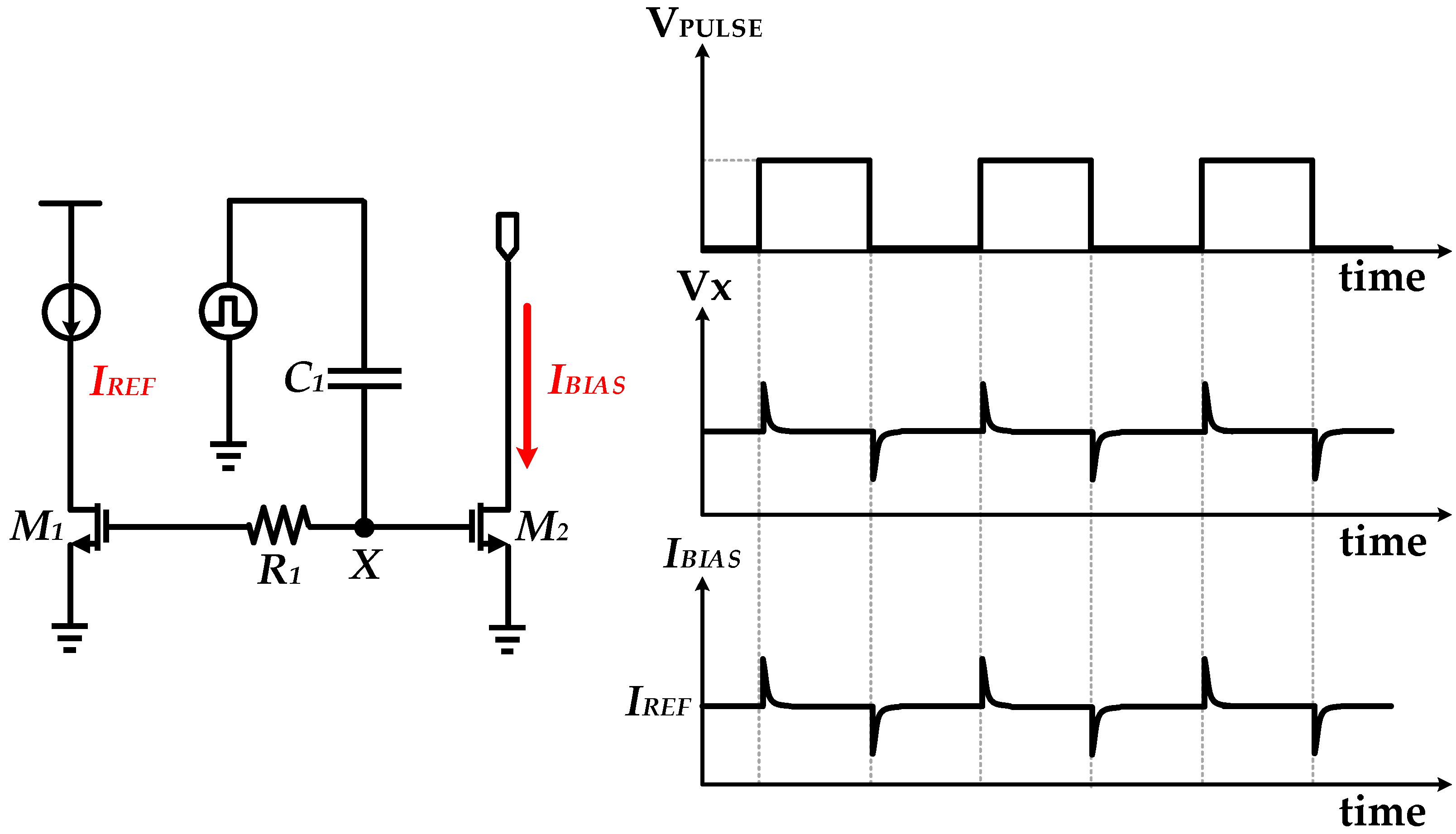

2.3. Voltage Spike Detection of FVF-Based LDO Regulator

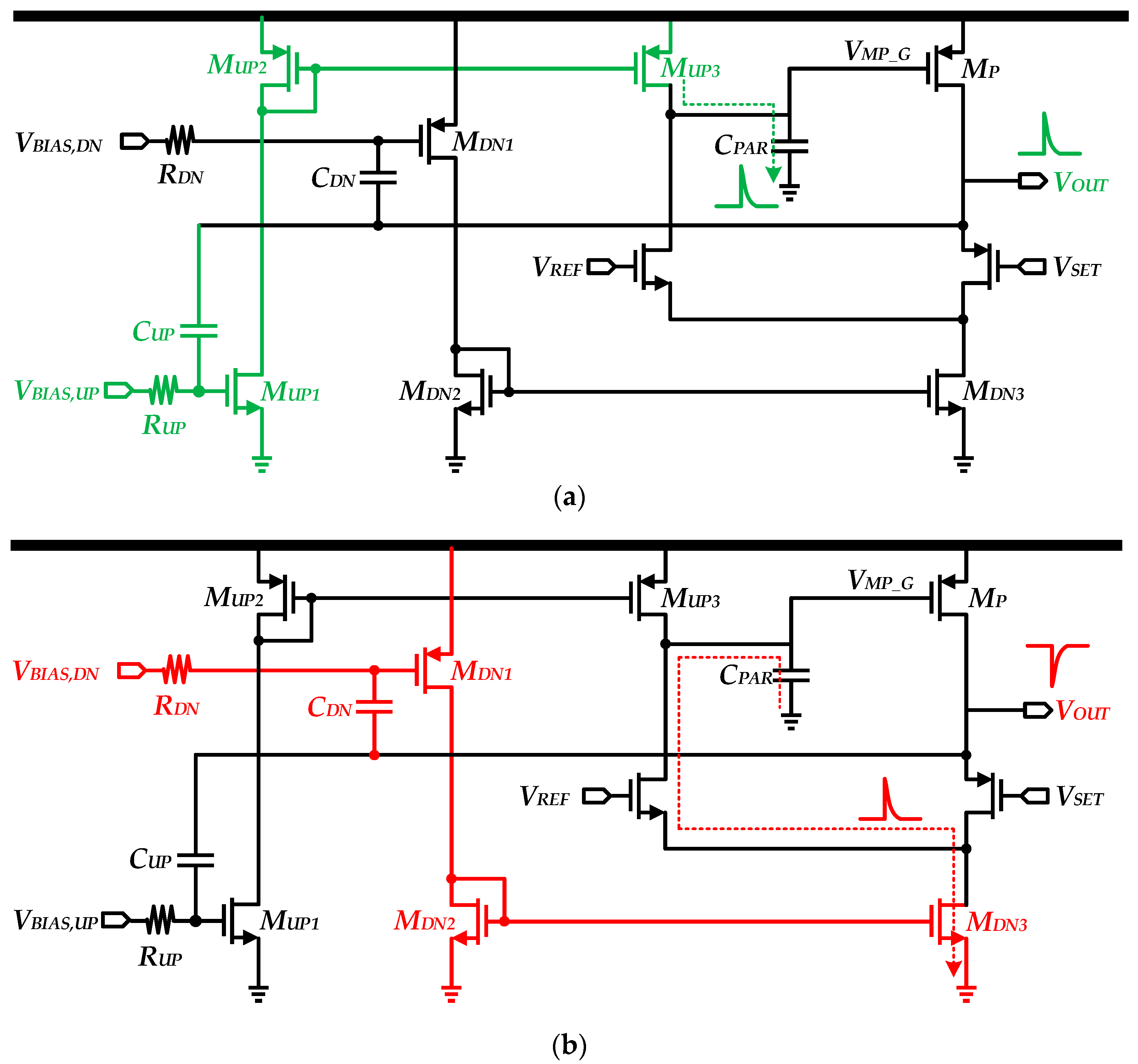

2.4. Loop-Gain-Enhanced FVF-Based LDO Regulator

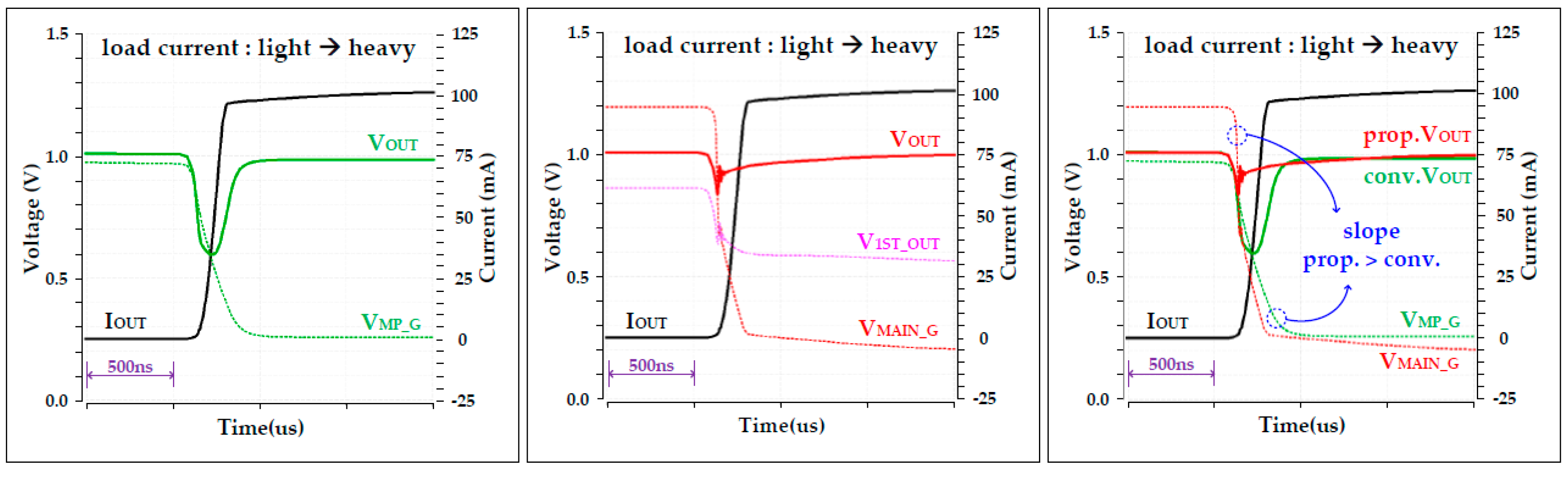

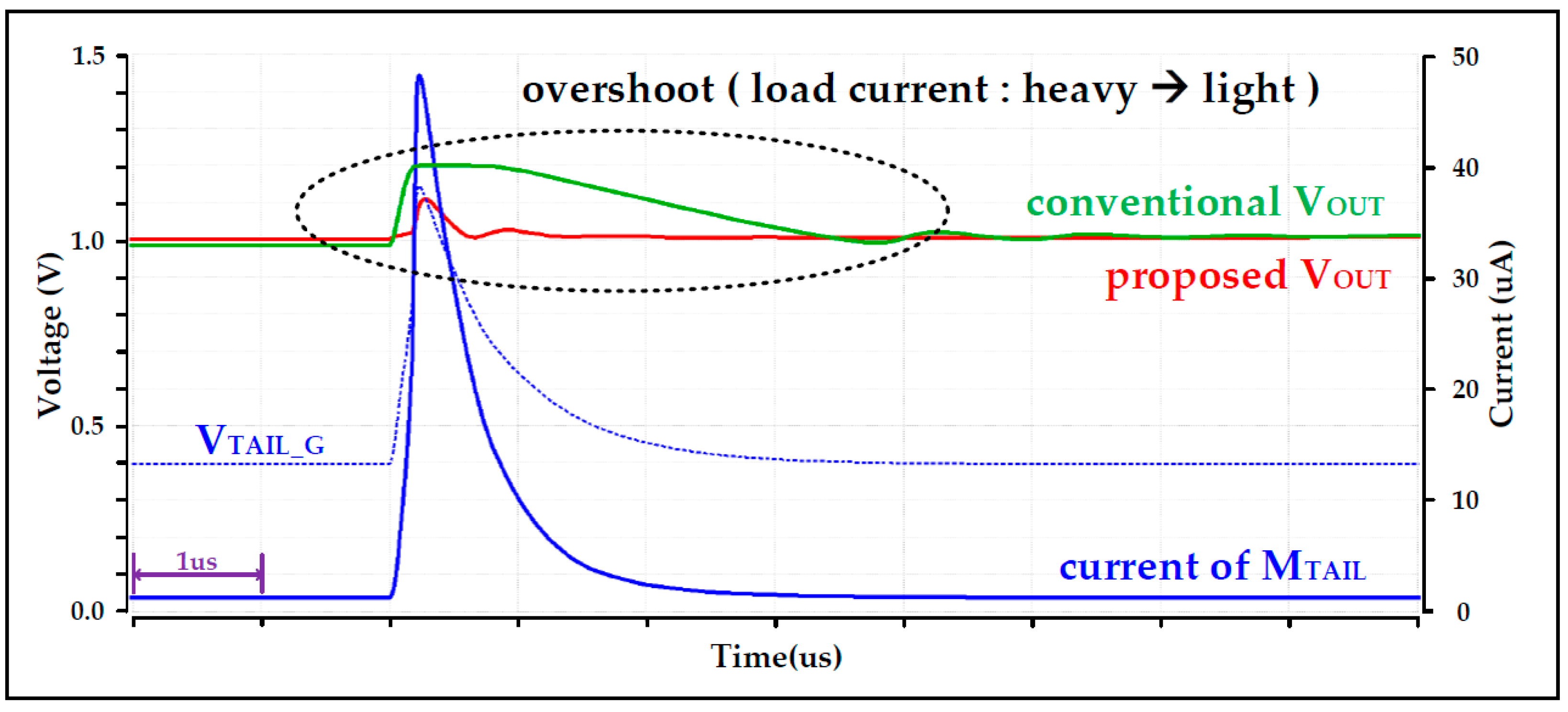

3. Proposed LDO Regulator

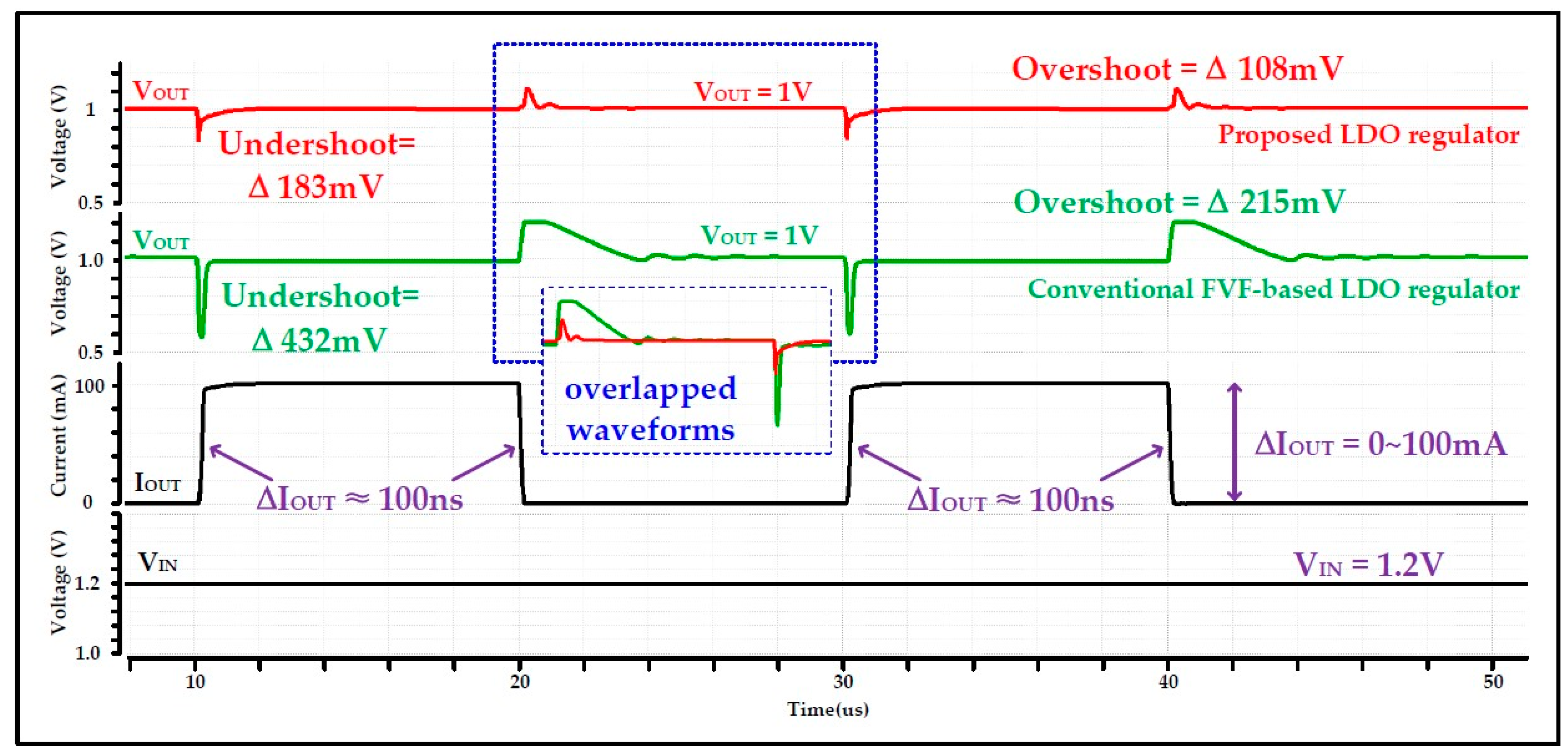

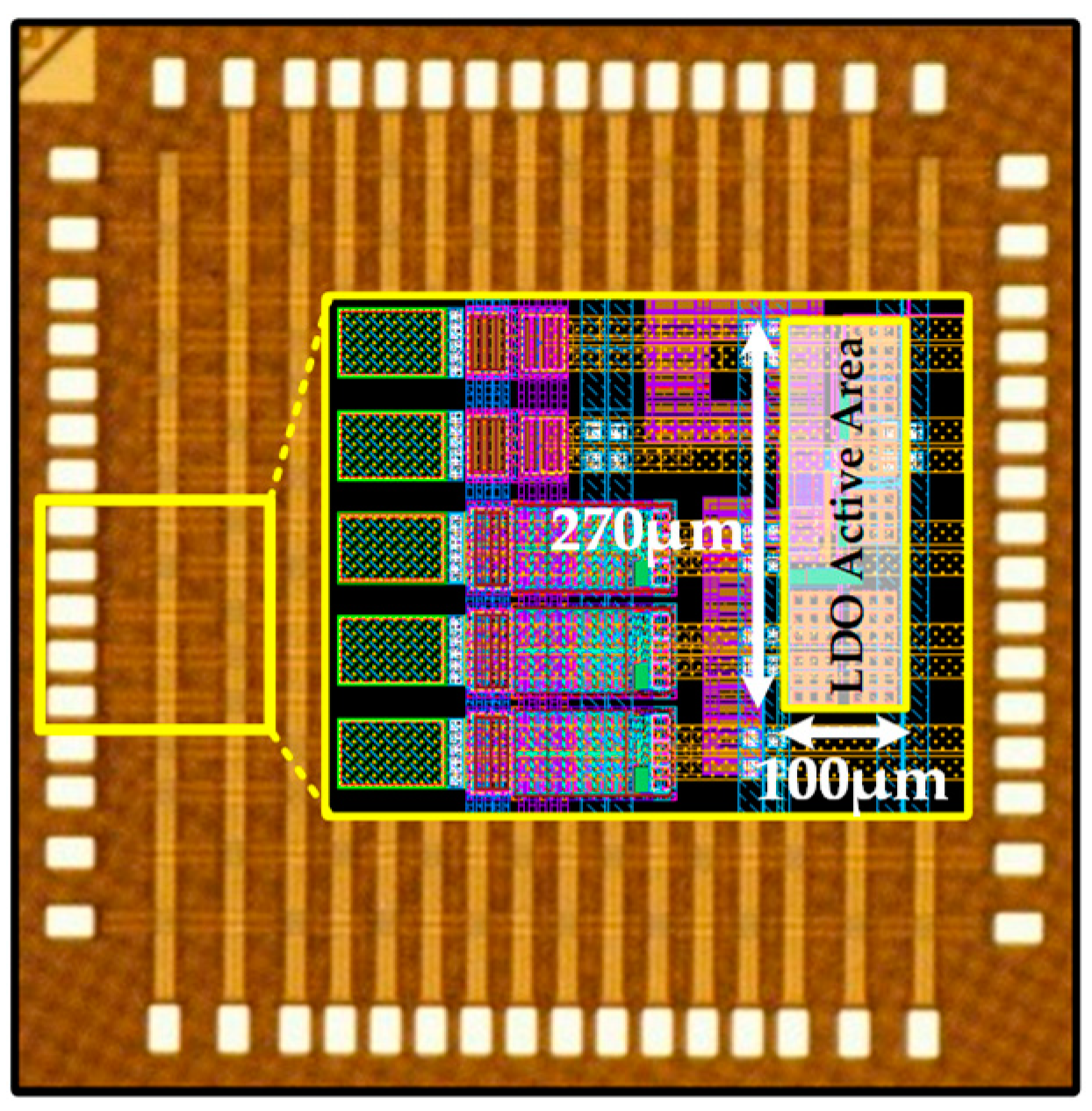

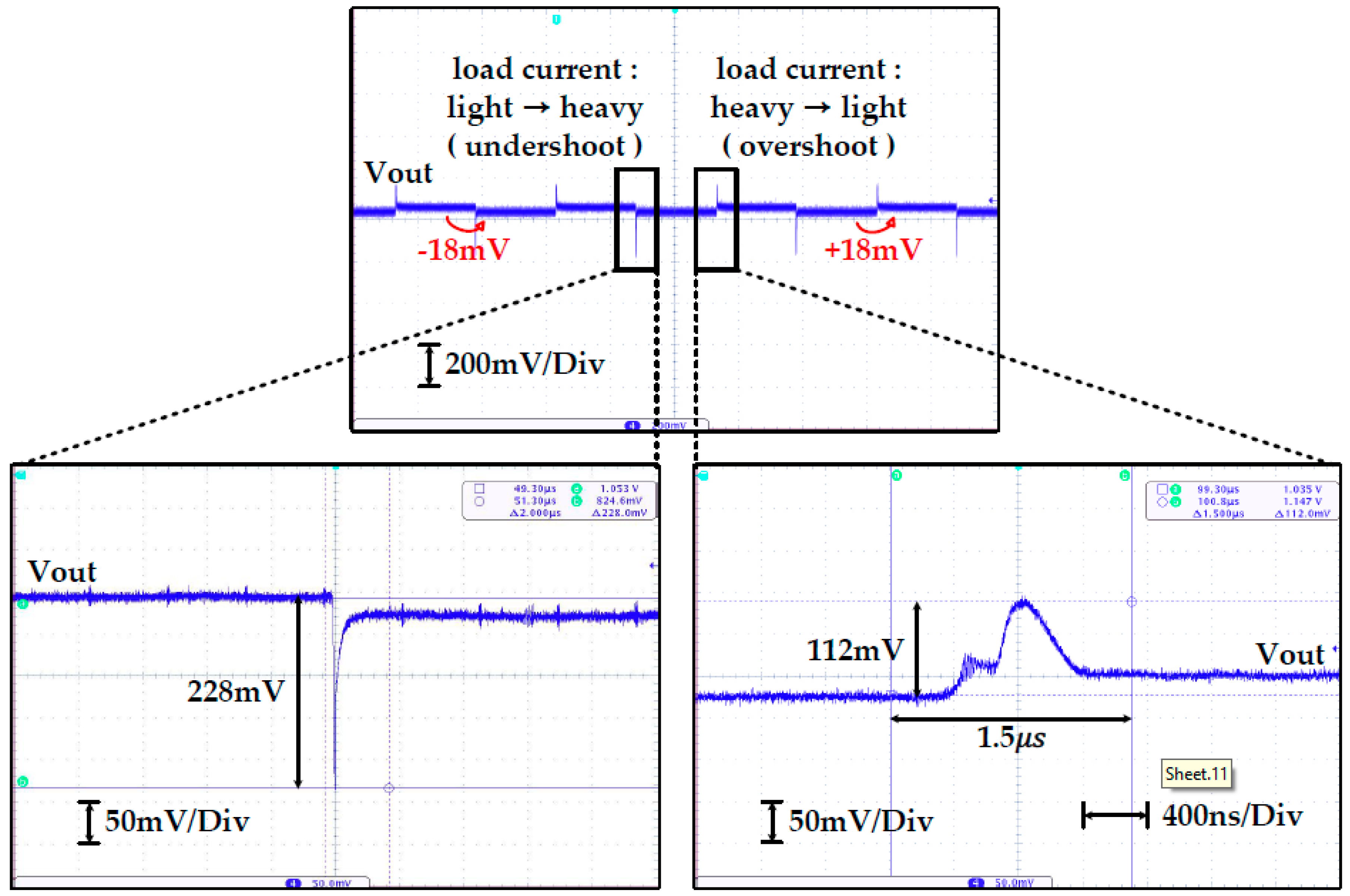

4. Measurement Results and Comparison

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Tsiropoulou, E.E.; Katsinis, G.K.; Papavassiliou, S. Utility-based Power Control via Convex Pricing for the Uplink in CDMA Wireless Networks. In Proceedings of the 2010 European Wireless Conference (EW), Lucca, Italy, 12–15 April 2010. [Google Scholar]

- Tefek, U.; Lim, T.J. Clustering and Radio Resource Partitioning for Machine-Type Communications in Cellular Networks. In Proceedings of the 2016 IEEE Wireless Communications and Networking Conference, Doha, Qatar, 3–6 April 2016. [Google Scholar]

- Kastrinogiannis, T.; Tsiropoulou, E.E.; Papavassiliou, S. Utility-Based Uplink Power Control in CDMA Wireless Networks with Real-Time Services. In International Conference on Ad-Hoc Networks and Wireless; Springer: Berlin/Heidelberg, Germany, 2008; pp. 307–320. ISBN 978-3-540-85208-7. [Google Scholar]

- Tsai, Y.D.; Song, C.Y.; Hsieh, H.Y. Joint Optimization of Clustering and Scheduling for Machine-to-Machine Communications in Cellular Wireless Networks. In Proceedings of the 2015 IEEE 81st Vehicular Technology Conference (VTC Spring), Glasgow, UK, 11–14 May 2015. [Google Scholar]

- Kim, W.; Brooks, D.; Wei, G.Y. A Fully-Integrated 3-Level DC-DC Converter for Nanosecond-Scale DVFS. IEEE J. Solid-State Circuits 2012, 47, 206–219. [Google Scholar] [CrossRef]

- Lee, Y.H.; Chiu, C.C.; Peng, S.Y.; Chen, K.H.; Lin, Y.H.; Lee, C.C.; Huang, C.C.; Tsai, T.Y. A Near-Optimum Dynamic Voltage Scaling (DVS) in 65-nm Energy-Efficient Power Management With Frequency-Based Control (FBC) for SoC System. IEEE J. Solid-State Circuits 2012, 47, 2563–2575. [Google Scholar] [CrossRef]

- Lee, Y.H.; Peng, S.Y.; Chiu, C.C.; Wu, A.C.H.; Chen, K.H.; Lin, Y.H.; Wang, S.W.; Tsai, T.Y.; Huang, C.C.; Lee, C.C. A Low Quiescent Current Asynchronous Digital-LDO With PLL-Modulated Fast-DVS Power Management in 40 nm SoC for MIPS Performance Improvement. IEEE J. Solid-State Circuits 2013, 48, 1018–1030. [Google Scholar] [CrossRef]

- Kim, S.T.; Shih, Y.C.; Mazumdar, K.; Jain, R.; Ryan, J.F.; Tokunaga, C.; Augustine, C.; Kulkarni, J.P.; Ravichandran, K.; Tschanz, J.W.; et al. Enabling Wide Autonomous DVFS in a 22 nm Graphics Execution Core Using a Digitally Controlled Fully Integrated Voltage Regulator. IEEE J. Solid-State Circuits 2016, 51, 18–30. [Google Scholar] [CrossRef]

- Hazucha, P.; Karnik, T.; Bloechel, B.A.; Parsons, C.; Finan, D.; Borkar, S. Area-Efficient Linear Regulator With Ultra-Fast Load Regulation. IEEE J. Solid-State Circuits 2005, 40, 933–940. [Google Scholar] [CrossRef]

- Milliken, R.J.; Silva-Martinez, J.; Sanchez-Sinencio, E. Full On-Chip CMOS Low-Dropout Voltage Regulator. IEEE Trans. Circuits Syst. I 2007, 54, 1879–1890. [Google Scholar] [CrossRef]

- Chong, S.S.; Chan, P.K. A 0.9-μA Quiescent Current Output-Capacitorless LDO Regulator With Adaptive Power Transistors in 65-nm CMOS. IEEE Trans. Circuits Syst. I 2013, 60, 1072–1081. [Google Scholar] [CrossRef]

- Man, T.Y.; Leung, K.N.; Leung, C.Y.; Mok, P.K.T.; Chan, M. Development of Single-Transistor-Control LDO Based on Flipped Voltage Follower for SoC. IEEE Trans. Circuits Syst. I 2008, 55, 1392–1401. [Google Scholar] [CrossRef]

- Chen, H.; Leung, K.N. A Fast-Transient LDO Based on Buffered Flipped Voltage Follower. In Proceedings of the 2010 IEEE International Conference of Electron Devices and Solid-State Circuits (EDSSC), Hong Kong, China, 15–17 December 2010. [Google Scholar]

- Or, P.Y.; Leung, K.N. An Output-Capacitorless Low-Dropout Regulator With Direct Voltage-Spike Detection. IEEE J. Solid-State Circuits 2010, 45, 458–466. [Google Scholar] [CrossRef]

- Guo, J.; Leung, K.N. A 6-μW Chip-Area-Efficient Output-Capacitorless LDO in 90-nm CMOS Technology. IEEE J. Solid-State Circuits 2010, 45, 1896–1905. [Google Scholar] [CrossRef]

- Lu, Y.; Wang, Y.; Pan, Q.; Ki, W.-H.; Yue, C.P. A Fully-Integrated Low-Dropout Regulator With Full-Spectrum Power Supply Rejection. IEEE Trans. Circuits Syst. I 2015, 62, 707–716. [Google Scholar] [CrossRef]

| Parameters | TCAS-I 2008 [12] | JSSC 2010 [15] | TCAS-I 2015 [16] | This Work |

|---|---|---|---|---|

| Process [nm] | 350 | 90 | 65 | 65 |

| LDO Type | Analog | Analog | Analog | Analog |

| Input Voltage [V] | 1.2 | 0.75–1.2 | 1.2 | 1.2 |

| Output Voltage [V] | 1 | 0.5–1 | 1 | 1 |

| Load Current Range [mA] | 0–50 | 3–100 | 0–10 | 0–100 |

| Max Load Current, IMAX [mA] | 50 | 100 | 10 | 100 |

| Quiescent Current, IQ [μA] | 95 | 8 | 50–90 | 30 |

| Peak Current Efficiency [%] | 99.81 | 99.99 | n/a | 99.97 |

| PSR [dB] @ 10 MHz | n/a | 25 @ 10 kHz | <20 | 26 |

| ∆V [mV] @ Load Step [mA] | 164 @ 50 | 114 @ 97 | 82 @ 10 | 228 @ 100 |

| Response Time, TR [ns] 1 | 3.28 | 0.057 | 1.15 | 0.228 |

| Settling Time [ns] | <300 | 5000 | >100 | <2000 |

| Load Regulation [mV/mA] | 0.28 | 0.1 | 1.1 | 0.18 |

| Total On-chip Capacitor [nF] | Not required | Not required | 0.14 | Not required |

| Active Area [mm2] | 0.0448 | 0.019 | 0.023 | 0.027 |

| FOM1 [ps] 2 | 6.232 | 0.005 | 5.74 | 0.068 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Park, J.; Ko, W.-J.; Kang, D.-S.; Lee, Y.; Chun, J.-H. An Output Capacitor-Less Low-Dropout Regulator with 0–100 mA Wide Load Current Range. Energies 2019, 12, 211. https://doi.org/10.3390/en12020211

Park J, Ko W-J, Kang D-S, Lee Y, Chun J-H. An Output Capacitor-Less Low-Dropout Regulator with 0–100 mA Wide Load Current Range. Energies. 2019; 12(2):211. https://doi.org/10.3390/en12020211

Chicago/Turabian StylePark, Jihoon, Woong-Joon Ko, Dong-Seok Kang, Yoonmyung Lee, and Jung-Hoon Chun. 2019. "An Output Capacitor-Less Low-Dropout Regulator with 0–100 mA Wide Load Current Range" Energies 12, no. 2: 211. https://doi.org/10.3390/en12020211

APA StylePark, J., Ko, W.-J., Kang, D.-S., Lee, Y., & Chun, J.-H. (2019). An Output Capacitor-Less Low-Dropout Regulator with 0–100 mA Wide Load Current Range. Energies, 12(2), 211. https://doi.org/10.3390/en12020211