Seven-Level Active Power Filter Based on a Novel H-Bridge Power Topology Structure

Abstract

:1. Introduction

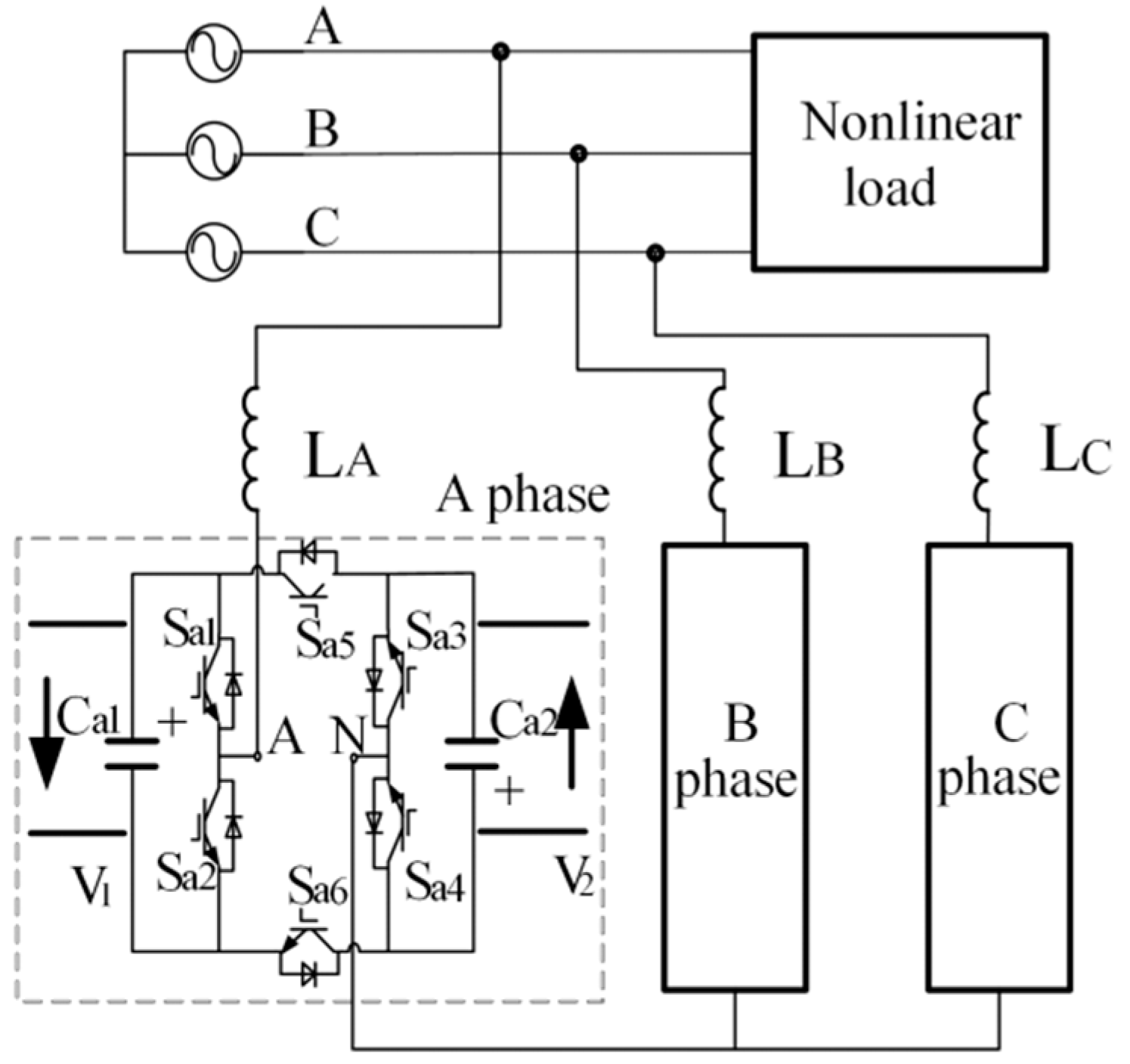

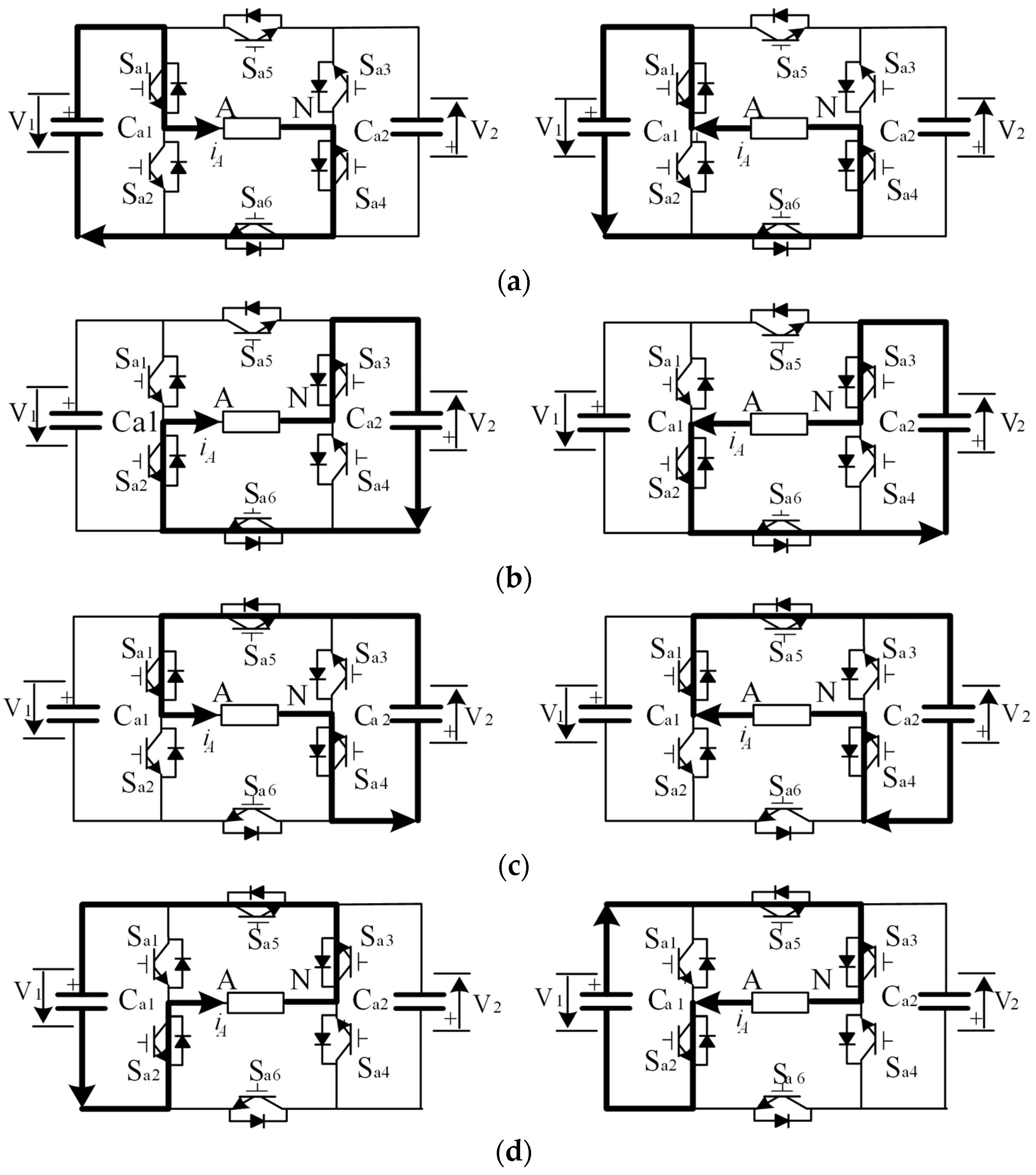

2. Analysis of the Novel Seven-Level Topology

2.1. The Structure and Working Mechanism of the Novel Seven-Level H-Bridge Topology

2.2. Comparison with Other Seven-Level Structures

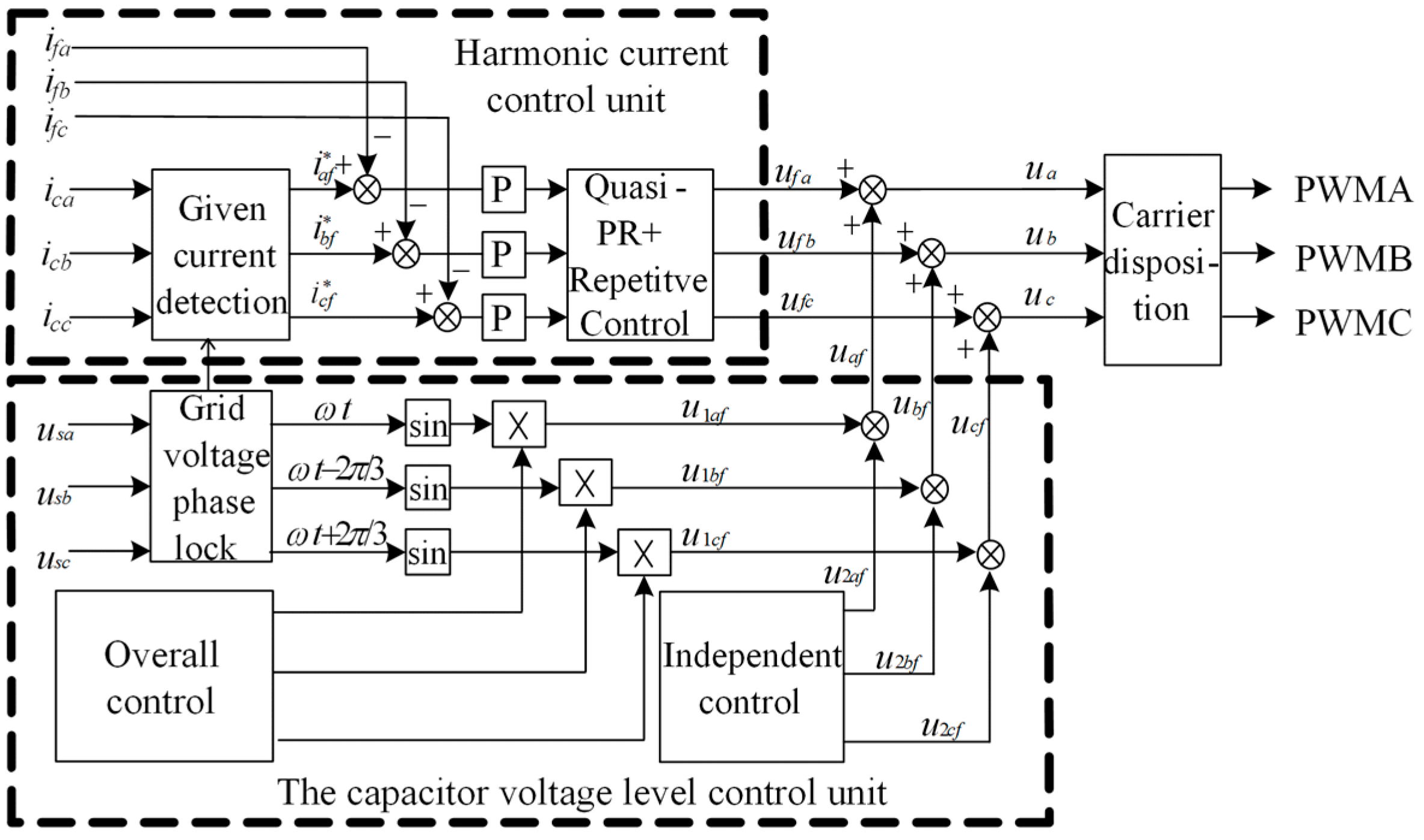

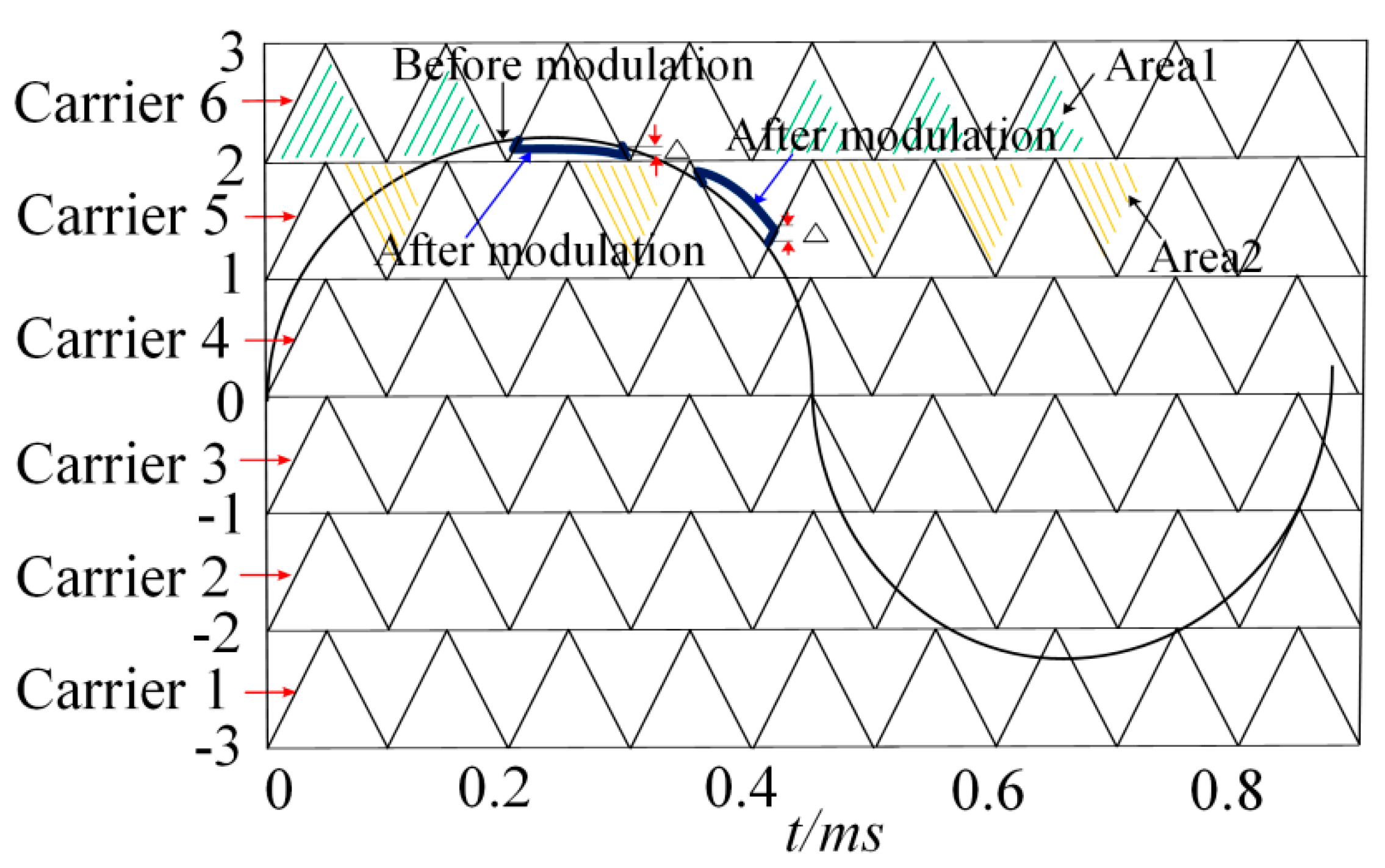

3. APF Control Method Based on Novel Topology Structure

3.1. Overall Control Strategy of the System

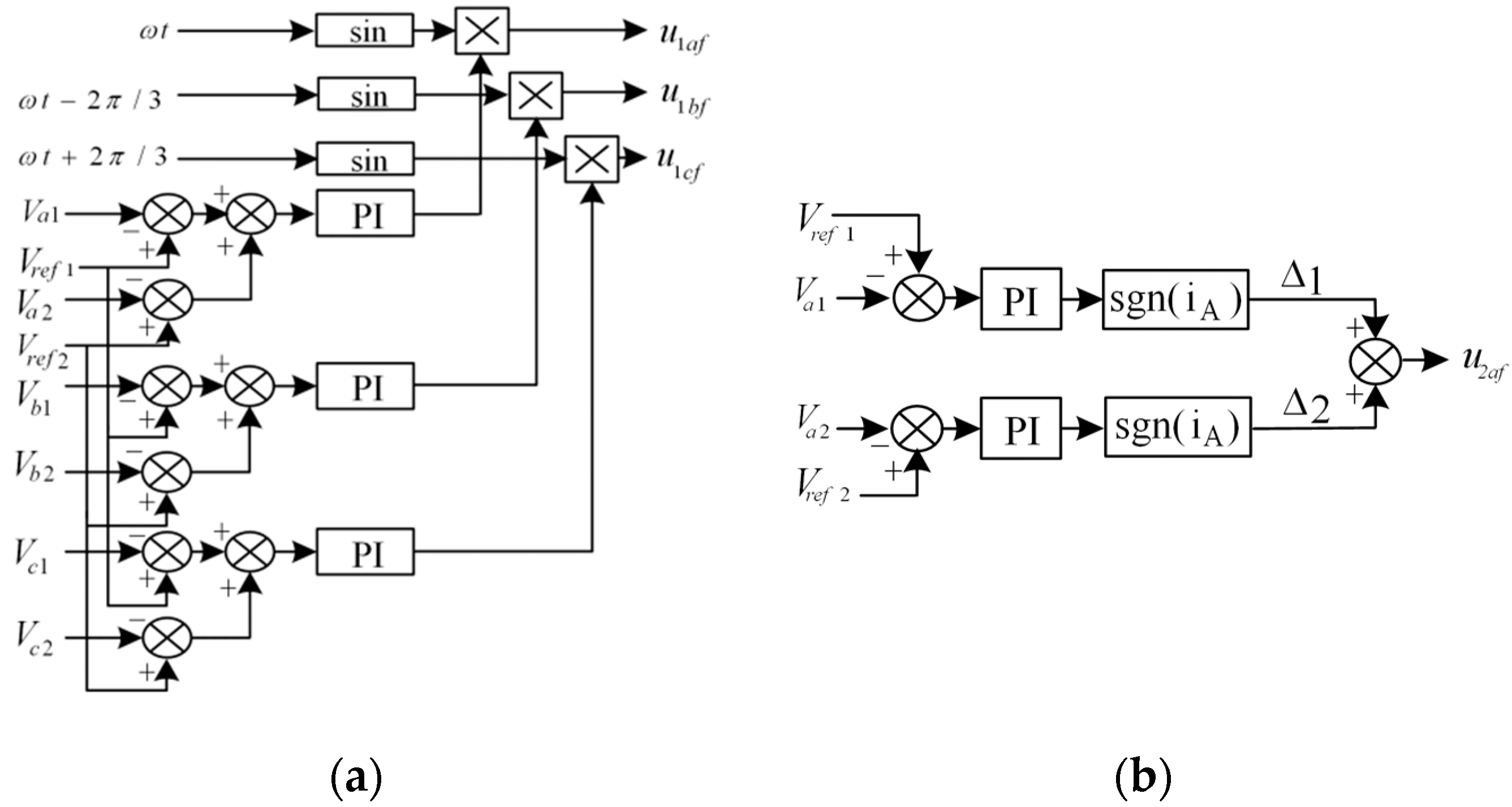

3.2. First-Stage Control Strategy of the Capacitor Voltage

3.3. Second-Stage Control Strategy of the Capacitor Voltage

3.3.1. Determination of Charge and Discharge Status

3.3.2. Control Strategy of Charge and Discharge

3.4. Parameter Calculation of Passive Elements

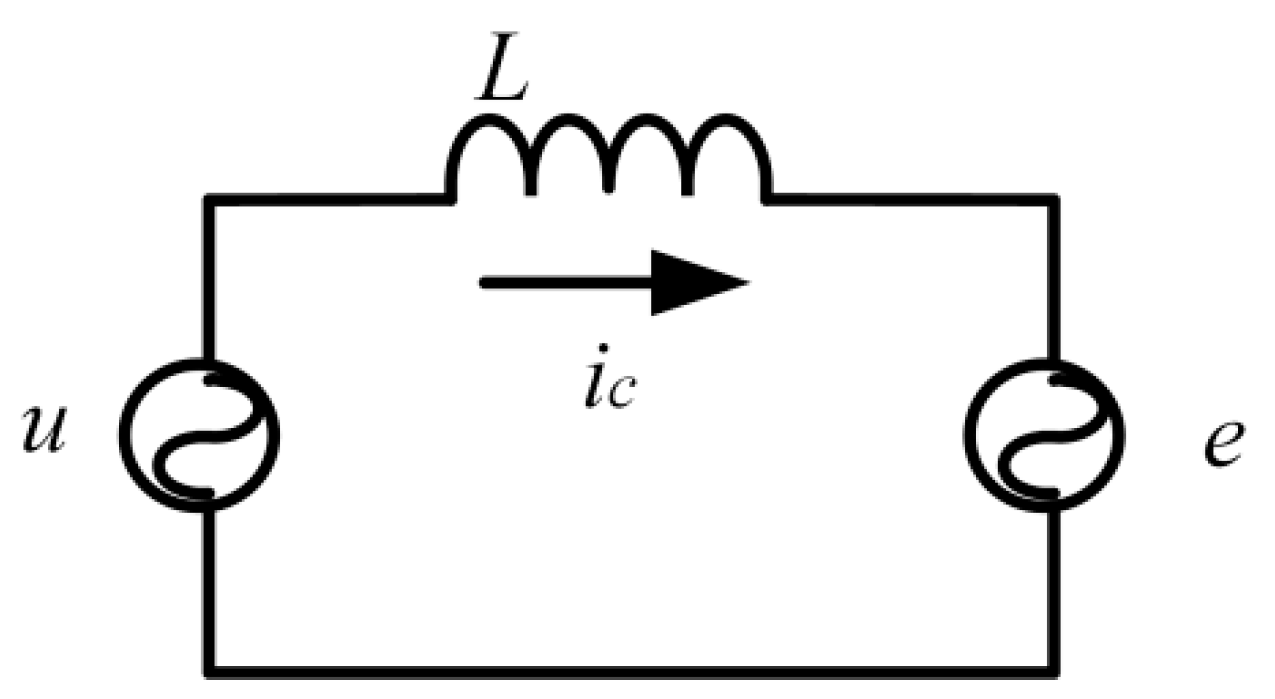

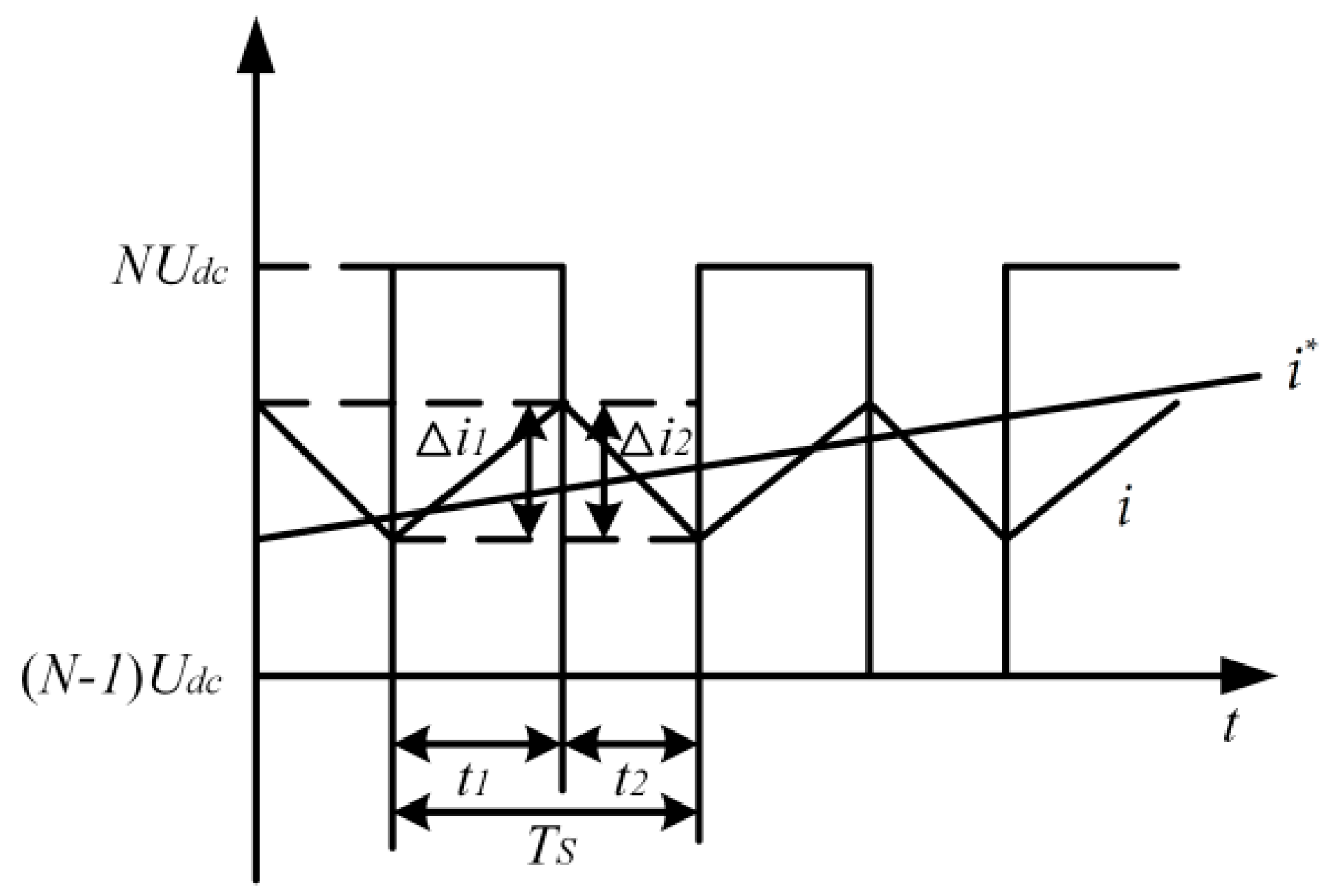

3.4.1. Parameter Calculation of Connected Inductor

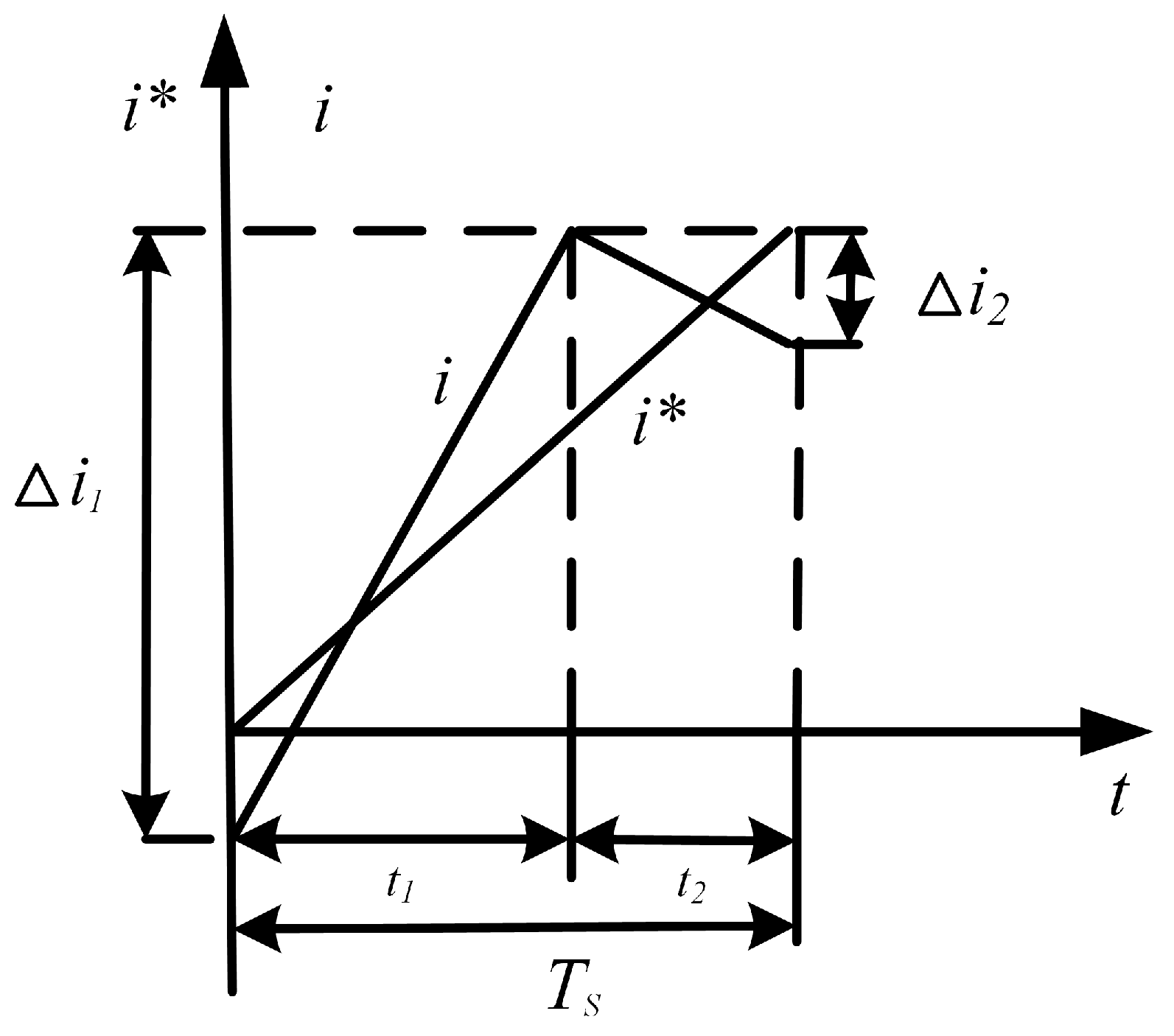

3.4.2. Parameter Calculation of Capacitor

4. System Simulation and Result Analysis

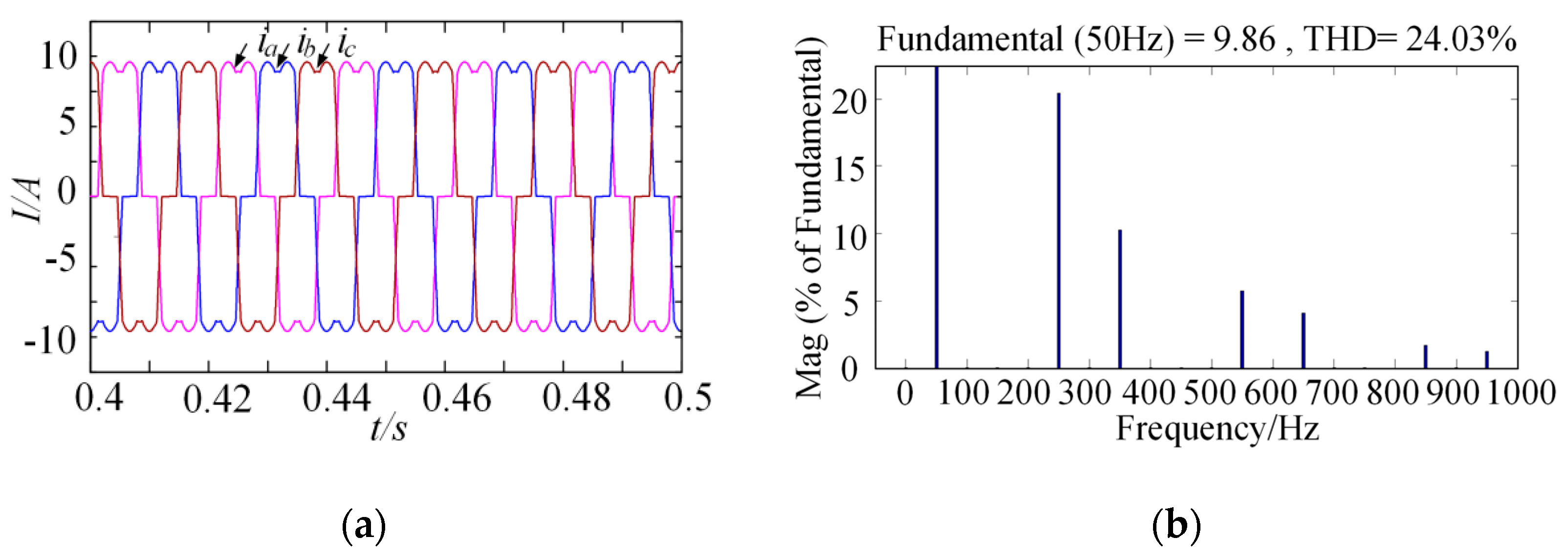

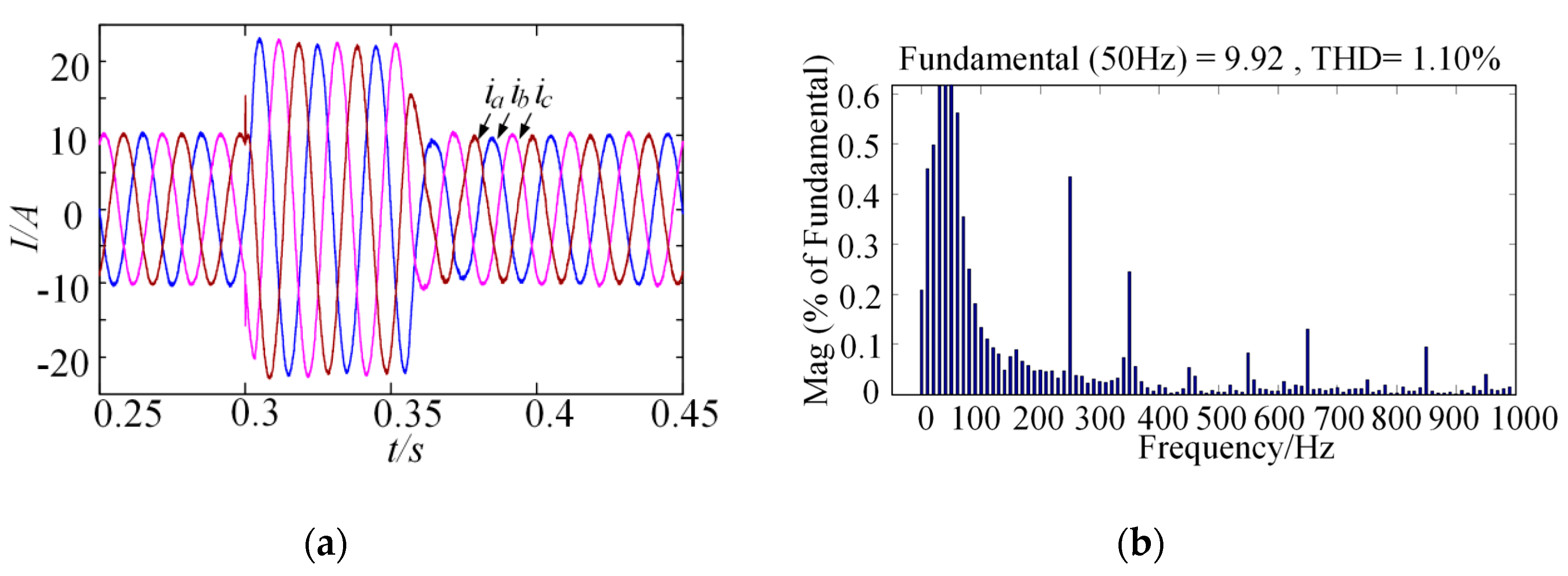

4.1. Under the Conditions of Balanced Grid and Load

4.2. Under the Conditions of Unbalanced Grid and Load

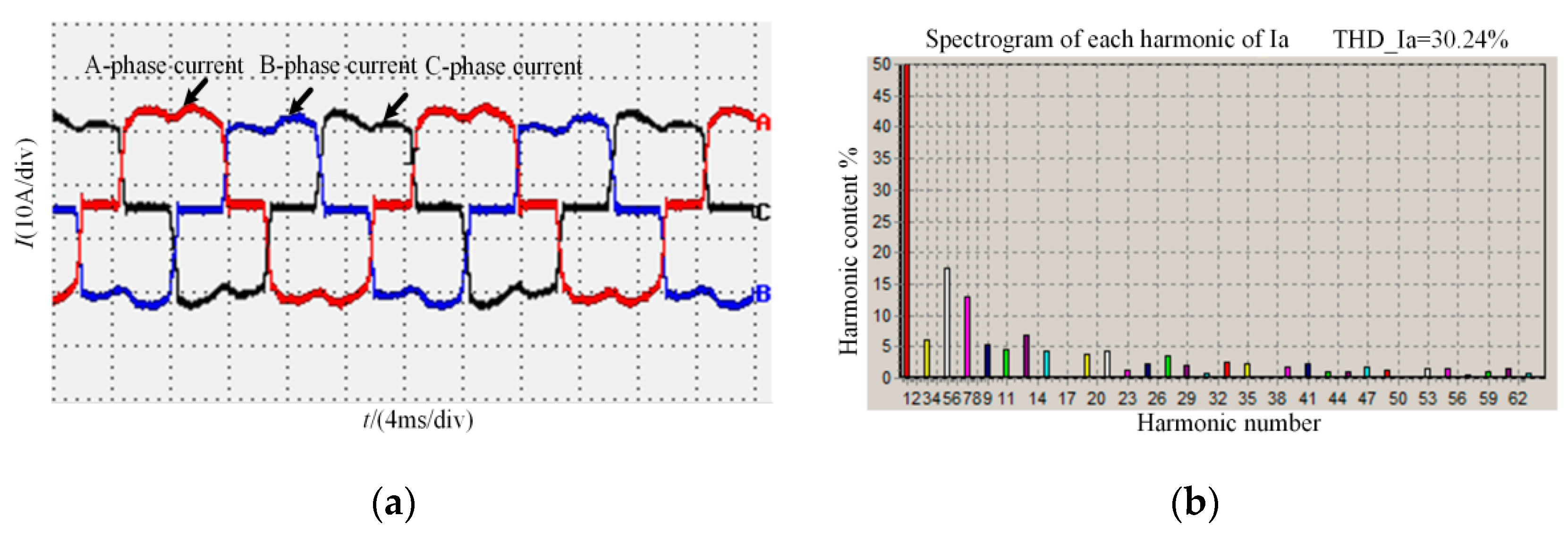

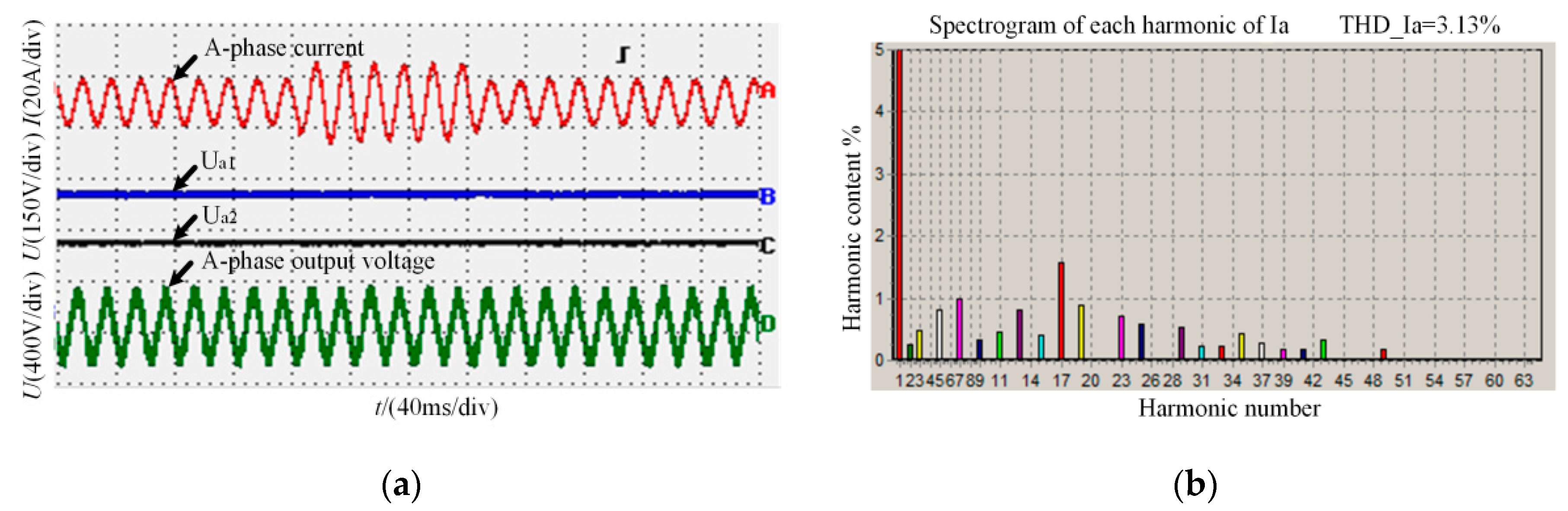

5. Experiment and Result Analysis

5.1. Under the Conditions of Balanced Grid and Load

5.2. Under the Conditions of Unbalanced Grid and Load

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Gadgune, S.Y.; Jadhav, P.T.; Chaudhary, L.R.; Waware, M.M. Implementation of shunt APF based on Diode Clamped and Cascaded H-bridge multilevel inverter. In Proceedings of the International Conference on Electrical, Computer and Communication Technologies (ICECCT), Coimbatore, India, 5–7 March 2015; pp. 1–7. [Google Scholar]

- Choi, W.; Lam, C.; Wong, M.; Han, Y. Analysis of DC link voltage controls in three-phase four-wire hybrid active power filters. IEEE Trans. Power Electron. 2013, 28, 2180–2191. [Google Scholar] [CrossRef]

- Hou, S.; Fei, J. Adaptive fuzzy sliding control with fuzzy sliding term for three-phase active power filter. In Proceedings of the IEEE International Conference on Control and Automation (ICCA), Hangzhou, China, 12–14 June 2013; pp. 1318–1323. [Google Scholar]

- Lam, C.; Wong, M.; Choi, W.; Cui, X.; Mei, H.; Liu, J. Design and performance of an adaptive low-DC-voltage-controlled LC-hybrid active power filter With a neutral inductor in three-phase four-wire power systems. IEEE Trans. Ind. Electron. 2014, 61, 2635–2647. [Google Scholar] [CrossRef]

- Alishah, R.S.; Hosseini, S.H.; Babaei, E.; Sabahi, M. Optimal Design of New Cascaded Switch-Ladder Multilevel Inverter Structure. IEEE Trans. Ind. Electron. 2017, 64, 2072–2080. [Google Scholar] [CrossRef]

- Zhu, H.; Shu, Z.; Gao, F. Five-level diode-clamped active power filter using voltage space vector-based indirect current and predictive harmonic control. IET Power Electron. 2014, 7, 713–723. [Google Scholar] [CrossRef]

- Banaei, M.R.; Jannati Oskuee, M.R.; Khounjahan, H. Reconfiguration of semi-cascaded multilevel inverter to improve systems performance parameters. IET Power Electron. 2014, 7, 1106–1112. [Google Scholar] [CrossRef]

- Babaei, E.; Laali, S.; Bayat, Z. A Single-Phase Cascaded Multilevel Inverter Based on a New Basic Unit With Reduced Number of Power Switches. IEEE Trans. Ind. Electron. 2015, 62, 922–929. [Google Scholar] [CrossRef]

- Chen, Z.; Wang, Z.; Li, M. A hybird cascade H-bridge seven-level converter for active power filter. In Proceedings of the IECON 2014—40th Annual Conference of the IEEE Industrial Electronics Society, Dallas, TX, USA, 29 October–1 November 2014; pp. 1041–1047. [Google Scholar]

- Boora, K.; Kumar, J.; Himanshu. A new general topology for asymmetrical multilevel inverter with reduced number of switching components. In Proceedings of the 2017 Recent Developments in Control, Automation & Power Engineering (RDCAPE), Noida, India, 26–27 October 2017; pp. 66–71. [Google Scholar]

- Hameed, U.; Ali, M.; Sadiq, H.; Khawaja, A.H.; Abdullah Khalid, H. Comparative study of Cascaded H-Bridge Multi-level Inverter using different Phase Shifted PWM Techniques. In Proceedings of the 2018 International Conference on Power Generation Systems and Renewable Energy Technologies (PGSRET), Islamabad, Pakistan, 10–12 September 2018; pp. 1–6. [Google Scholar]

- Singhai, S.; Pandey, A.; Singh, V. New Topology of Asymmtrical Multilevel inverter [15/29 Level]. In Proceedings of the 2018 International Conference on Current Trends towards Converging Technologies (ICCTCT), Coimbatore, India, 1–3 March 2018; pp. 1–6. [Google Scholar]

- Koshti, A.K.; Rao, M.N. A brief review on multilevel inverter topologies. In Proceedings of the 2017 International Conference on Data Management, Analytics and Innovation (ICDMAI), Pune, India, 24–26 February 2017; pp. 187–193. [Google Scholar]

- Sajedi, S.; Basu, M.; Farrell, M. New grid-tied cascaded multilevel inverter topology with reduced number of switches. In Proceedings of the 2017 52nd International Universities Power Engineering Conference (UPEC), Heraklion, Greece, 28–31 August 2017; pp. 1–6. [Google Scholar]

- Amamra, S.; Meghriche, K.; Cherifi, A.; Francois, B. Multilevel Inverter Topology for Renewable Energy Grid Integration. IEEE Trans. Ind. Electron. 2017, 64, 8855–8866. [Google Scholar] [CrossRef]

- Haji-Esmaeili, M.M.; Naseri, M.; Khoun-Jahan, H.; Abapour, M. Fault-tolerant structure for cascaded H-bridge multilevel inverter and reliability evaluation. IET Power Electron. 2017, 10, 59–70. [Google Scholar] [CrossRef]

- Mora, A.; Juliet, J.; Santander, A.; Lezana, P. Dead-Time and Semiconductor Voltage Drop Compensation for Cascaded H-Bridge Converters. IEEE Trans. Ind. Electron. 2016, 63, 7833–7842. [Google Scholar] [CrossRef]

- Dhanamjayulu, C.; Meikandasivam, S. Performance verific-ation of symmetric hybridized cascaded multilevel inverter with reduced number of switches. In Proceedings of the 2017 Innovations in Power and Advanced Computing Technologies (i-PACT), Vellore, India, 21–22 April 2017; pp. 1–5. [Google Scholar]

- Hasan, M.M.; Abu-Siada, A. A novel three phase cascaded multilevel inverter topology. In Proceedings of the 2016 IEEE Industrial Electronics and Applications Conference (IEACon), Kota Kinabalu, Malaysia, 20–22 November 2016; pp. 31–35. [Google Scholar]

- Kangarlu, M.F.; Babaei, E. A Generalized Cascaded Multilevel Inverter Using Series Connection of Submultilevel Inverters. IEEE Trans. Power Electron. 2018, 28, 625–636. [Google Scholar] [CrossRef]

- Srinivas, C.; PhaniSanthoshi, K.; AppaRao, G.V.; Siva, K.N.V. A Novel Seven Level Asymmetrical Inverter Topology to Reduce Total Harmonic Distortion. In Proceedings of the 2018 International Conference on Current Trends towards Converging Technologies (ICCTCT), Coimbatore, India, 1–3 March 2018; pp. 1–4. [Google Scholar]

- Ramya, D.; Mary Antony, A.S. A reconfigurable five/seven level inverter with reduced switching losses. In Proceedings of the 2017 International Conference on Computation of Power, Energy Information and Commuincation (ICCPEIC), Melmaruvathur, India, 22–23 March 2017; pp. 656–659. [Google Scholar]

- Yarlagadda, A.K.; Eate, V.k.; Babu, Y.S.K.; Chakraborti, A. A Modified Seven Level Cascaded H Bridge Inverter. In Proceedings of the 2018 5th IEEE Uttar Pradesh Section International Conference on Electrical, Electronics and Computer Engineering (UPCON), Gorakhpur, India, 2–4 November 2018; pp. 1–6. [Google Scholar]

- Guo, H.F.; Chen, M.; Cao, Y.; Ma, Q.D.; Ling, Z.B. Design of 2MW/10kV cascaded H-bridge power conversion system. In Proceedings of the 2014 International Conference on Power System Technology, Chengdu, China, 20–22 October 2014; pp. 3335–3340. [Google Scholar]

- Kawakami, N.; Ota, S.; Kon, H.; Konno, S.; Akagi, H.; Kobayashi, H.; Okada, N. Development of a 500-kW Modular Multilevel Cascade Converter for Battery Energy Storage Systems. IEEE Trans. Ind. Appl. 2014, 50, 3902–3910. [Google Scholar] [CrossRef]

- Townsend, C.D.; Summers, T.J.; Betzl, R.E. Impact of Practical Issues on the Harmonic Performance of Phase-Shifted Modulation Strategies for a Cascaded H-Bridge StatCom. IEEE Trans. Ind. Electron. 2014, 61, 2655–2664. [Google Scholar] [CrossRef]

- Angulo, M.; Lezana, P.; Kouro, S.; Rodriguez, J.; Wu, B. Level-shifted PWM for Cascaded Multilevel Inverters with Even Power Distribution. In Proceedings of the 2007 IEEE Power Electronics Specialists Conference, Orlando, FL, USA, 17–21 June 2007; pp. 2373–2378. [Google Scholar]

- Sochor, P.; Akagi, H. Theoretical and Experimental Compa-rison Between Phase-Shifted PWM and Level-Shifted PWM in a Modular Multilevel SDBC Inverter for Utility-Scale Photovoltaic Applications. IEEE Trans. Ind. Appl. 2017, 53, 4695–4707. [Google Scholar] [CrossRef]

- Alex Bao Zambra, D. Comparison of Phase-Shift and Step Wave Modulation Technique applied to Symmetrical Cascaded Multilevel Inverter. IEEE Lat. Am. Trans. 2013, 11, 1156–1162. [Google Scholar] [CrossRef]

- Ko, Y.; Andresen, M.; Buticchi, G.; Liserre, M. Power Routing for Cascaded H-Bridge Converters. IEEE Trans. Power Electron. 2017, 32, 9435–9446. [Google Scholar] [CrossRef]

| Switch Status | Output Level | ||

|---|---|---|---|

| Sa1,Sa2 | Sa3,Sa4 | Sa5,Sa6 | |

| 1,0 | 1,0 | 0,1 | +(V1 + V2) |

| 1,0 | 0,1 | 0,1 | +V1 |

| 0,1 | 1,0 | 0,1 | +V2 |

| 1,0 or 0,1 | 1,0 or 0,1 | 1,0 or 0,1 | 0 |

| 1,0 | 0,1 | 1,0 | −V2 |

| 0,1 | 1,0 | 1,0 | −V1 |

| 0,1 | 0,1 | 1,0 | −(V1 + V2) |

| Structure | Diode Clamp | Cascading H-Bridge | New Topology | |

|---|---|---|---|---|

| Category | ||||

| Topology |  |  |  | |

| Number of single-phase power switches | 12 | 12 | 6 | |

| Number of single-phase capacitors | 6 | 3 | 2 | |

| Current | iA > 0 | iA < 0 | |

|---|---|---|---|

| Output Level | |||

| 7: V1 + V2 | - | - | |

| 6: V1 | Ca1 discharge, Ca2 suspend | Ca1 charge, Ca2 suspend | |

| 5: V2 | Ca1 suspend, Ca2 discharge | Ca1 suspend, Ca2 charge | |

| 4: 0 | - | - | |

| 3: −V2 | Ca1 suspend, Ca2 charge | Ca1 suspend, Ca2 discharge | |

| 2: −V1 | Ca1 charge, Ca2 suspend | Ca1 discharge, Ca2 suspend | |

| 1: −(V1 + V2) | - | - | |

| System Parameters | Values |

|---|---|

| The voltage of capacitor Ca1 | 260 V |

| The voltage of capacitor Ca2 | 130 V |

| The capacitor Ca1 | 1000 uF |

| The capacitor Ca2 | 1000 uF |

| The switching frequency fs | 20 kHz |

| The grid frequency f | 50 Hz |

| The inductor LA, LB, LC | 3 mH |

| The balanced grid phase voltages UA, UB, UC | 220 V |

| The balanced resistance load R | 40 Ω |

| The unbalanced grid phase voltages UA, UB, UC | 220 V, 180 V, 180 V |

| A single-phase rectifier load RAB | 10 Ω |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Gao, H.; Zhang, P.; Liu, X.; Feng, S.; Ma, J.; Li, R. Seven-Level Active Power Filter Based on a Novel H-Bridge Power Topology Structure. Energies 2019, 12, 2997. https://doi.org/10.3390/en12152997

Gao H, Zhang P, Liu X, Feng S, Ma J, Li R. Seven-Level Active Power Filter Based on a Novel H-Bridge Power Topology Structure. Energies. 2019; 12(15):2997. https://doi.org/10.3390/en12152997

Chicago/Turabian StyleGao, Hanying, Pengfei Zhang, Xu Liu, Shuai Feng, Junjie Ma, and Ran Li. 2019. "Seven-Level Active Power Filter Based on a Novel H-Bridge Power Topology Structure" Energies 12, no. 15: 2997. https://doi.org/10.3390/en12152997

APA StyleGao, H., Zhang, P., Liu, X., Feng, S., Ma, J., & Li, R. (2019). Seven-Level Active Power Filter Based on a Novel H-Bridge Power Topology Structure. Energies, 12(15), 2997. https://doi.org/10.3390/en12152997