Digital Control of a Buck Converter Based on Input-Output Linearization. An Interpretation Using Discrete-Time Sliding Control Theory

Abstract

1. Introduction

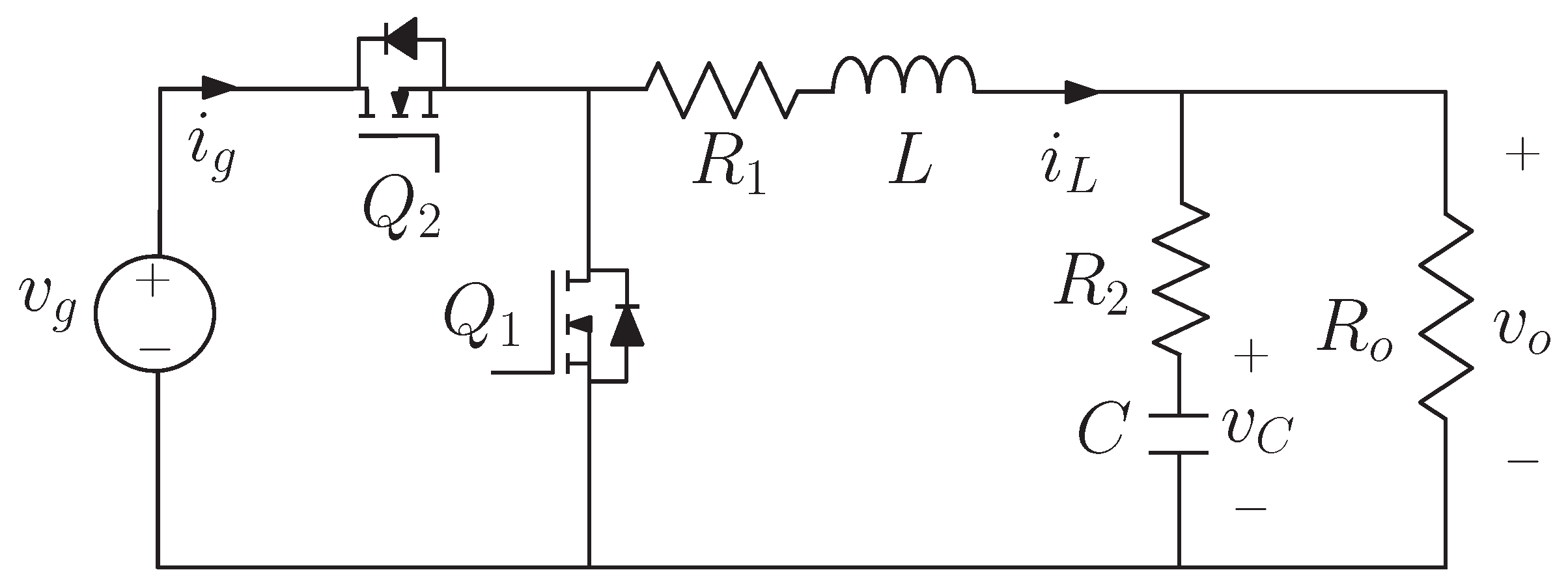

2. Nonlinear Recurrence

3. Current Control Loop Based on Input-Output Linearization

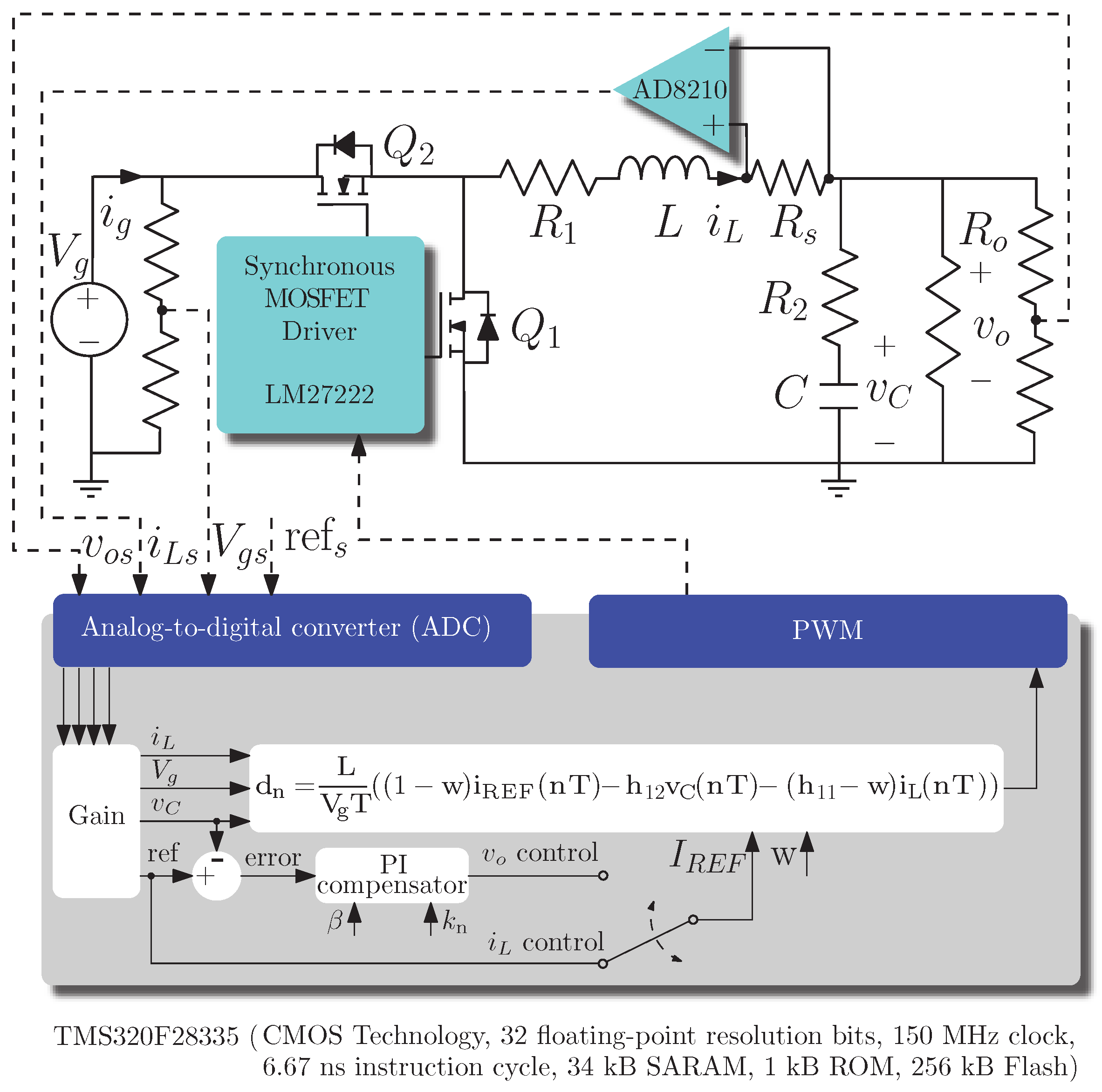

4. Voltage Regulation

5. Experimental Results and Numerical Simulations

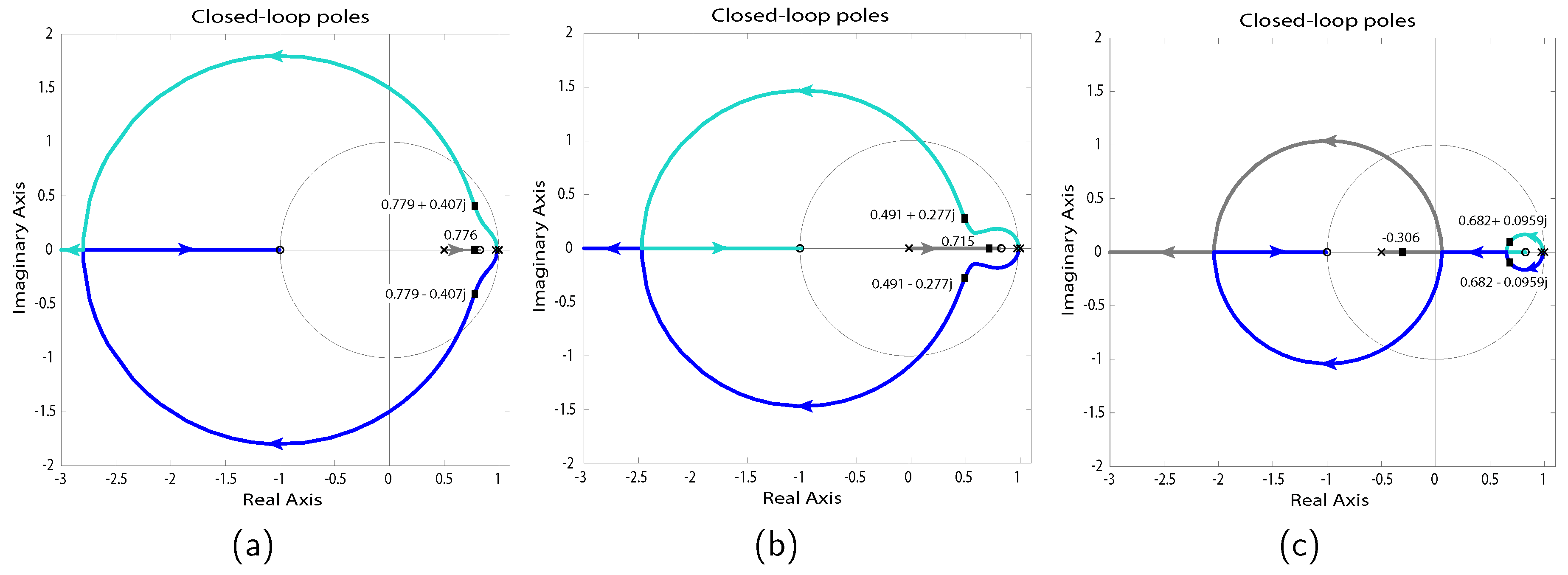

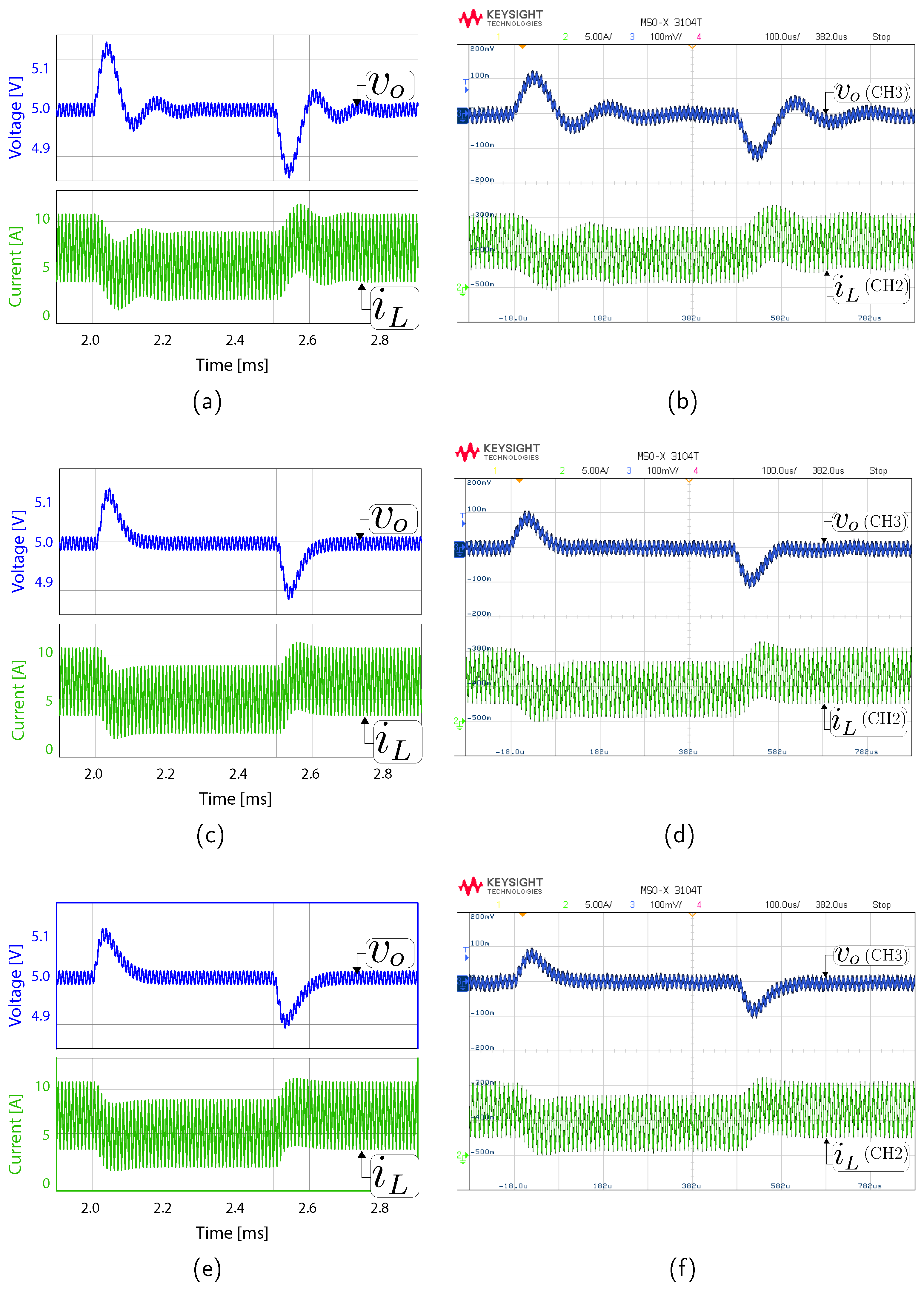

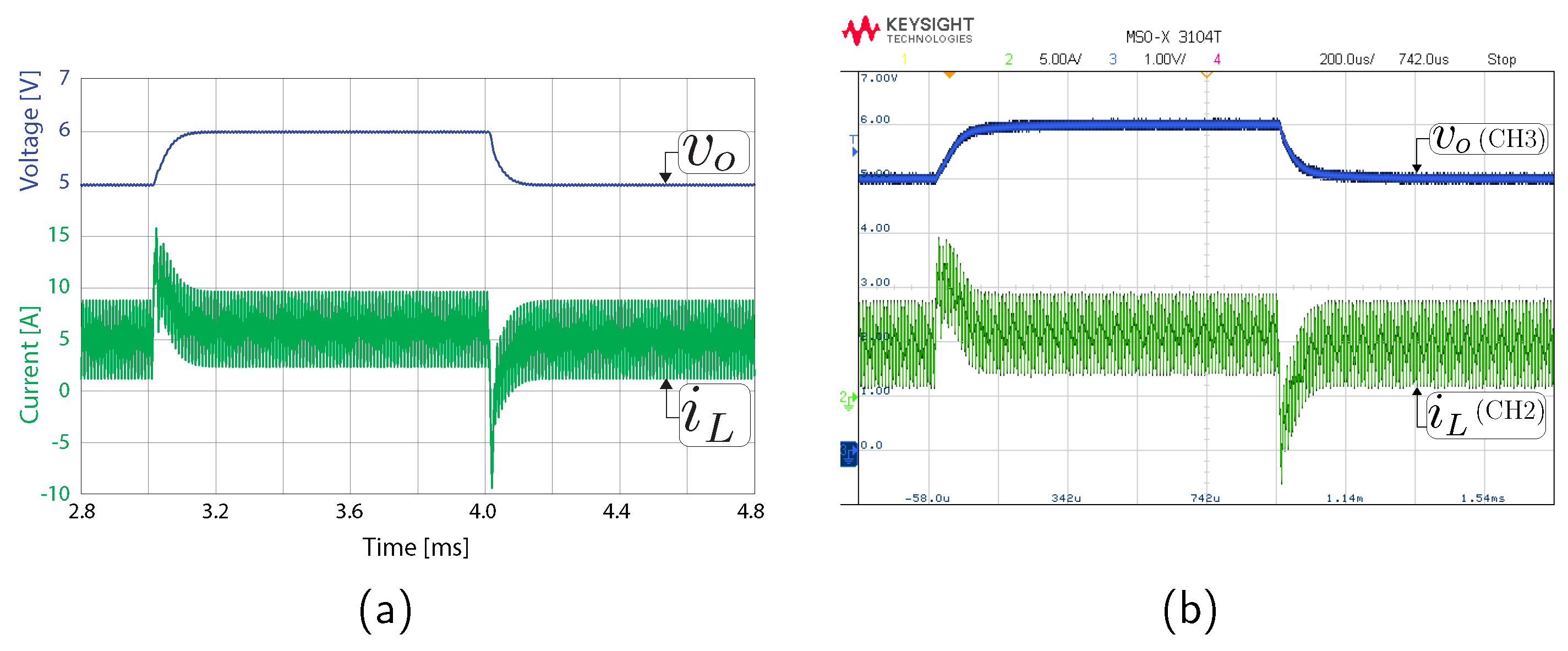

5.1. Inner Current Loop

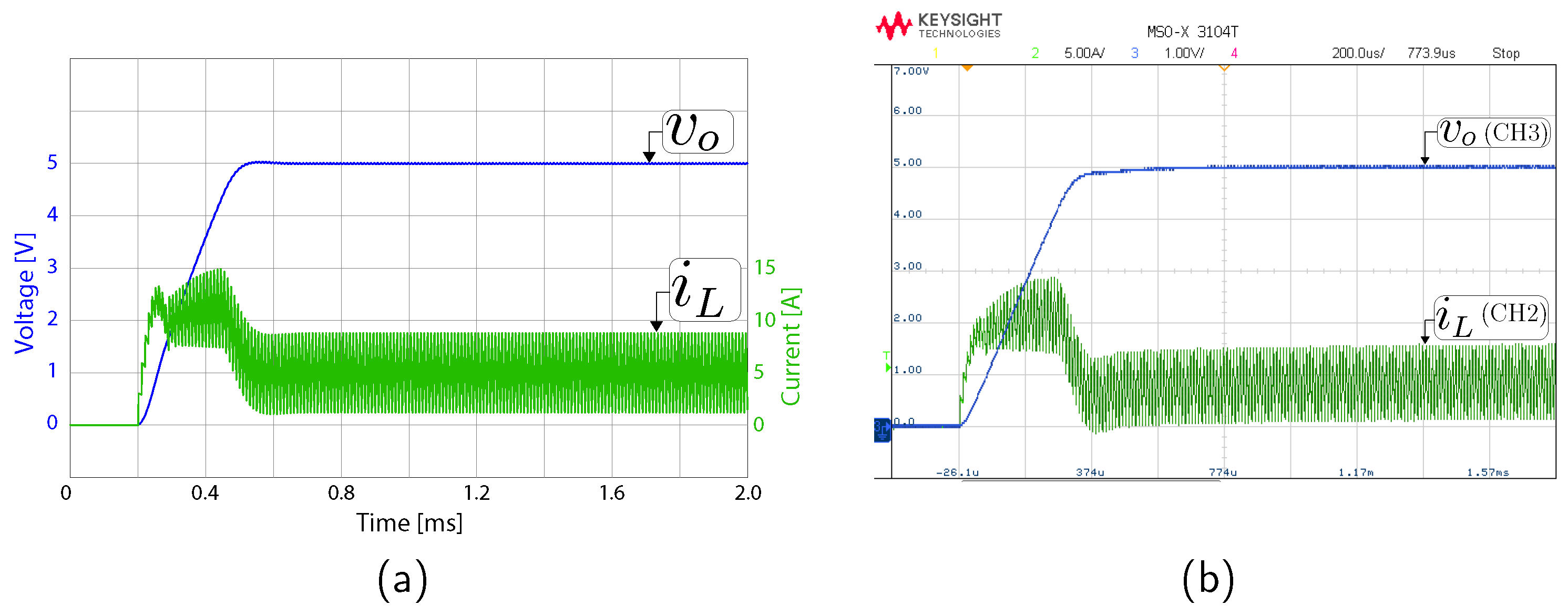

5.2. Voltage Regulation Loop

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Liu, Y.F.; Meyer, E.; Liu, X. Recent Developments in Digital Control Strategies for DC/DC Switching Power Converters. IEEE Trans. Power Electron. 2009, 24, 2567–2577. [Google Scholar] [CrossRef]

- Patella, B.; Prodic, A.; Zirger, A.; Maksimovic, D. High-frequency digital PWM controller IC for DC-DC converters. IEEE Trans. Power Electron. 2003, 18, 438–446. [Google Scholar] [CrossRef]

- Peterchev, A.; Sanders, S. Quantization resolution and limit cycling in digitally controlled PWM converters. IEEE Trans. Ind. Electron. 2003, 18, 301–308. [Google Scholar] [CrossRef]

- Costabeber, A.; Corradini, L.; Mattavelli, P.; Saggini, S. Time optimal, parameters-insensitive digital controller for DC-DC buck converters. In Proceedings of the IEEE Power Electronics Specialists Conference, Rhodes, Greece, 15–19 June 2008; pp. 1243–1249. [Google Scholar] [CrossRef]

- Yousefzadeh, V.; Babazadeh, A.; Ramachandran, B.; Alarcon, E.; Pao, L.; Maksimovic, D. Proximate Time- Optimal Digital Control for Synchronous Buck DC-DC Converters. IEEE Trans. Power Electron. 2008, 23, 2018–2026. [Google Scholar] [CrossRef]

- Yeh, C.A.; Lai, Y.S. Digital Pulsewidth Modulation Technique for a Synchronous Buck DC/DC Converter to Reduce Switching Frequency. IEEE Trans. Ind. Electron. 2012, 59, 550–561. [Google Scholar] [CrossRef]

- Vidal-Idiarte, E.; Carrejo, C.; Calvente, J.; Martínez-Salamero, L. Two-Loop Digital Sliding Mode Control of DC-DC Power Converters Based on Predictive Interpolation. IEEE Trans. Ind. Electron. 2011, 58, 2491–2501. [Google Scholar] [CrossRef]

- York, B.; Yu, W.; Lai, J.S. Hybrid-Frequency Modulation for PWM-Integrated Resonant Converters. IEEE Trans. Power Electron. 2013, 28, 985–994. [Google Scholar] [CrossRef]

- Kapat, S.; Krein, P. Formulation of PID Control for DC-DC Converters Based on Capacitor Current: A Geometric Context. IEEE Trans. Power Electron. 2012, 27, 1424–1432. [Google Scholar] [CrossRef]

- Tsai, C.; Yang, C.; Wu, J. A Digitally Controlled Switching Regulator with Reduced Conductive EMI Spectra. IEEE Trans. Ind. Electron. 2012, 60, 3938–3947. [Google Scholar] [CrossRef]

- Abu Qahouq, J.A.; Arikatla, V. Online Closed-Loop Autotuning Digital Controller for Switching Power Converters. IEEE Trans. Ind. Electron. 2013, 60, 1747–1758. [Google Scholar] [CrossRef]

- Perry, A.; Feng, G.; Liu, Y.F.; Sen, P. A Design Method for PI-like Fuzzy Logic Controllers for DC-DC Converter. IEEE Trans. Ind. Electron. 2007, 54, 2688–2696. [Google Scholar] [CrossRef]

- Pitel, G.E.; Krein, P.T. Minimum-Time Transient Recovery for DC-DC Converters Using Raster Control Surfaces. IEEE Trans. Power Electron. 2009, 24, 2692–2703. [Google Scholar] [CrossRef]

- Radić, A.; Lukić, Z.; Prodić, A.; de Nie, R.H. Minimum-Deviation Digital Controller IC for DC-DC Switch-Mode Power Supplies. IEEE Trans. Power Electron. 2013, 28, 4281–4298. [Google Scholar] [CrossRef]

- Soto, A.; de Castro, A.; Alou, P.; Cobos, J.; Uceda, J.; Lotfi, A. Analysis of the Buck Converter for Scaling the Supply Voltage of Digital Circuits. IEEE Trans. Power Electron. 2007, 22, 2432–2443. [Google Scholar] [CrossRef]

- Meyer, E.; Zhang, Z.; Liu, Y.F. Digital Charge Balance Controller to Improve the Loading/Unloading Transient Response of Buck Converters. IEEE Trans. Power Electron. 2012, 27, 1314–1326. [Google Scholar] [CrossRef]

- Meyer, E.; Liu, Y.F. Digital Charge Balance Controller With an Auxiliary Circuit for Improved Unloading Transient Performance of Buck Converters. IEEE Trans. Power Electron. 2013, 28, 357–370. [Google Scholar] [CrossRef]

- Huerta, S.; Alou, P.; Garcia, O.; Oliver, J.; Prieto, R.; Cobos, J. Hysteretic Mixed-Signal Controller for High-Frequency DC-DC Converters Operating at Constant Switching Frequency. IEEE Trans. Power Electron. 2012, 27, 2690–2696. [Google Scholar] [CrossRef]

- Maksimovic, D.; Zane, R. Small-Signal Discrete-Time Modeling of Digitally Controlled PWM Converters. IEEE Trans. Power Electron. 2007, 22, 2552–2556. [Google Scholar] [CrossRef]

- Brown, A.R.; Middlebrook, R.D. Sampled-data modeling of switching regulators. In Proceedings of the IEEE Power Electronics Specialists Conference, Boulder, CO, USA, 29 June–3 July 1981; pp. 349–369. [Google Scholar]

- Peretz, M.; Ben-Yaakov, S. Time-Domain Design of Digital Compensators for PWM DC-DC Converters. IEEE Trans. Power Electron. 2012, 27, 284–293. [Google Scholar] [CrossRef]

- Vidal-Idiarte, E.; Marcos-Pastor, A.; Giral, R.; Calvente, J.; Martinez-Salamero, L. Direct digital design of a sliding mode-based control of a PWM synchronous buck converter. IET Power Electronics 2017, 10, 1714–1720. [Google Scholar] [CrossRef]

- Ogata, K. Discrete-Time Control Systems; Prentice-Hall, Inc.: Upper Saddle River, NJ, USA, 1995; pp. 242–257. [Google Scholar]

- El Aroudi, A.; Martínez-Treviño, B.; Vidal-Idiarte, E.; Cid-Pastor, A. Fixed Switching Frequency Digital Sliding-Mode Control of DC-DC Power Supplies Loaded by Constant Power Loads with Inrush Current Limitation Capability. Energies 2019, 12, 1055. [Google Scholar] [CrossRef]

- Chen, J.; Prodic, A.; Erickson, R.W.; Maksimovic, D. Predictive digital current programmed control. IEEE Trans. Power Electron. 2003, 18, 411–419. [Google Scholar] [CrossRef]

- Majo, J.; Martinez, L.; Poveda, A.; de Vicuna, L.; Guinjoan, F.; Sanchez, A.; Valentin, M.; Marpinard, J. Large-signal feedback control of a bidirectional coupled-inductor Cuk converter. IEEE Trans. Ind. Electron. 1992, 39, 429–436. [Google Scholar] [CrossRef]

| Component/Parameter | Description | Type/Value |

|---|---|---|

| , | Power MOSFET | IRF3798 |

| C | Ceramic Capacitor | C5750X7R1C476M230KB |

| X7R dielectric | F | |

| 5-V estimated C F | ||

| L | Power Inductor | WE-HCC 7443320330 |

| Ferrite core | L at kHz: H | |

| Series Resistor | Total Resistance: | |

| Current Sensing | SMD | |

| + Inductor DCR | ||

| Load | Aluminium Housed | |

| Power Resistor | ||

| T | Switching period | s |

| Switching frequency | kHz | |

| Inductor peak-to-peak current ripple | A | |

| ( V, V and ) | ||

| Inductor dc current | A | |

| ( V, V and ) | ||

| Output peak-to-peak voltage ripple | mV | |

| ( V, V and ) | (0.54%) | |

| MOSFET Driver | High-speed synchronous MOSFET driver | LM27222 |

| Texas Instruments | ||

| Current monitor | Bidirectional current shunt monitor | AD8210 |

| Analog Devices |

| Theoretical | Simulated | Experimental | ||||

|---|---|---|---|---|---|---|

| w | CF | PM | CF | PM | CF | PM |

| (kHz) | (deg) | (kHz) | (deg) | (kHz) | (deg) | |

| 0.5 | 7.3 | 23.3 | 6.1 | 34.0 | 5.2 | 36.9 |

| 0.0 | 8.4 | 43.4 | 7.3 | 44.2 | 6.2 | 46.4 |

| −0.5 | 8.6 | 53.2 | 7.6 | 48.7 | 7.3 | 47.4 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Vidal-Idiarte, E.; Restrepo, C.; El Aroudi, A.; Calvente, J.; Giral, R. Digital Control of a Buck Converter Based on Input-Output Linearization. An Interpretation Using Discrete-Time Sliding Control Theory. Energies 2019, 12, 2738. https://doi.org/10.3390/en12142738

Vidal-Idiarte E, Restrepo C, El Aroudi A, Calvente J, Giral R. Digital Control of a Buck Converter Based on Input-Output Linearization. An Interpretation Using Discrete-Time Sliding Control Theory. Energies. 2019; 12(14):2738. https://doi.org/10.3390/en12142738

Chicago/Turabian StyleVidal-Idiarte, Enric, Carlos Restrepo, Abdelali El Aroudi, Javier Calvente, and Roberto Giral. 2019. "Digital Control of a Buck Converter Based on Input-Output Linearization. An Interpretation Using Discrete-Time Sliding Control Theory" Energies 12, no. 14: 2738. https://doi.org/10.3390/en12142738

APA StyleVidal-Idiarte, E., Restrepo, C., El Aroudi, A., Calvente, J., & Giral, R. (2019). Digital Control of a Buck Converter Based on Input-Output Linearization. An Interpretation Using Discrete-Time Sliding Control Theory. Energies, 12(14), 2738. https://doi.org/10.3390/en12142738