A Modified Step-Up DC-DC Flyback Converter with Active Snubber for Improved Efficiency

Abstract

1. Introduction

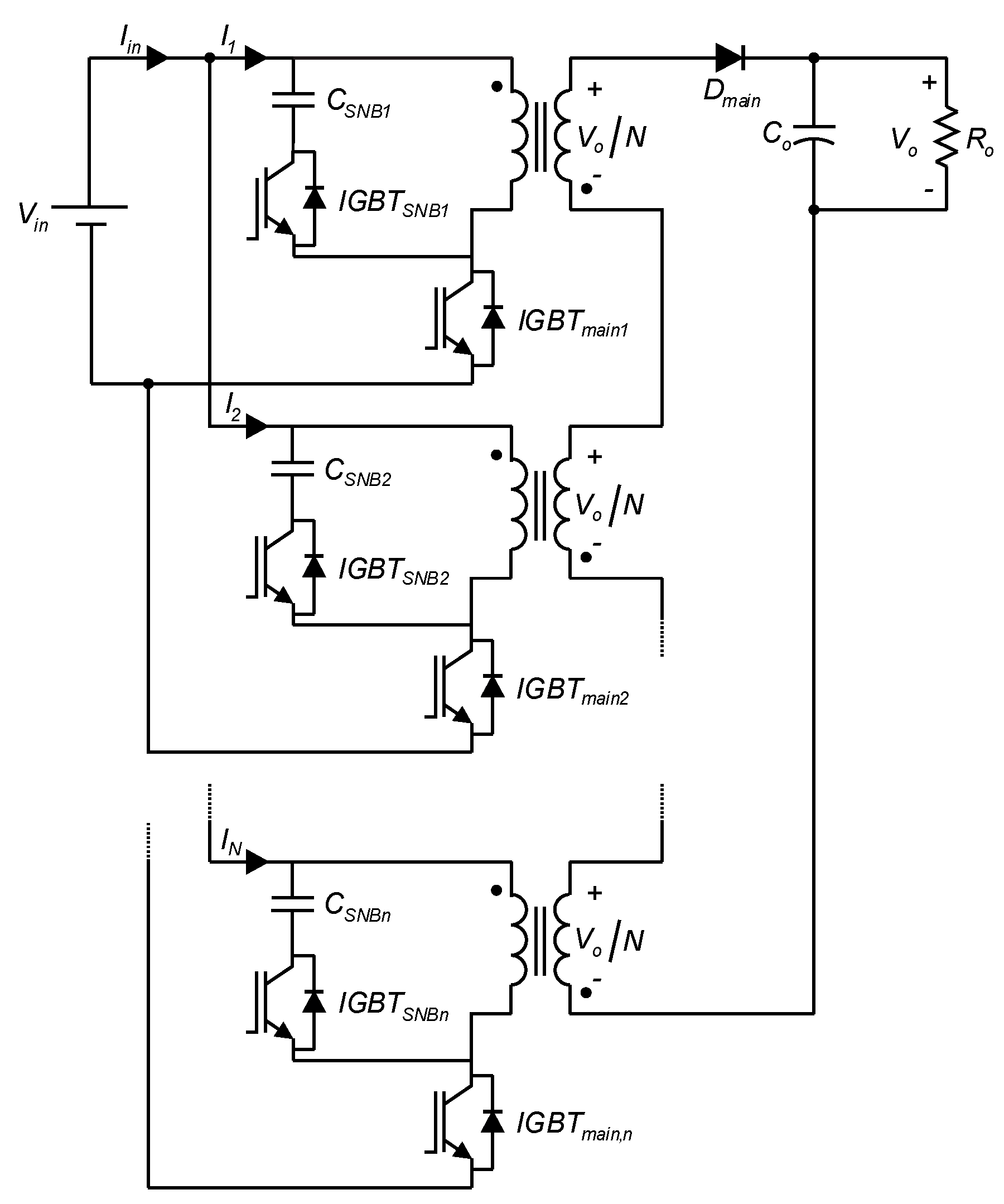

2. Operating Principle

- (1)

- The output voltage has negligible ripple.

- (2)

- The coupled inductors (so called “flyback transformers”) are identical and have unity turns ratio.

- (3)

- The parameters of the flyback transformers are referred to the primary side.

- (4)

- The windings resistances are neglected.

- (5)

- The active snubber circuit returns the energy stored in the leakage inductance back to the supply.

- (6)

- The power semiconductor devices are ideal.

- (7)

- The converter operates in Discontinuous Conduction Mode (DCM).

- (8)

- Main switches and snubber switches cannot be closed at the same time. is the duty cycle for the main switch, and is the duty cycle for the snubber switch.

2.1. Operating Mode 1

2.2. Operating Mode 2

2.3. Operating Mode 3

2.4. Operating Mode 4

2.5. Operating Mode 5

2.6. Operating Mode 6

3. Voltage Transfer Ratio

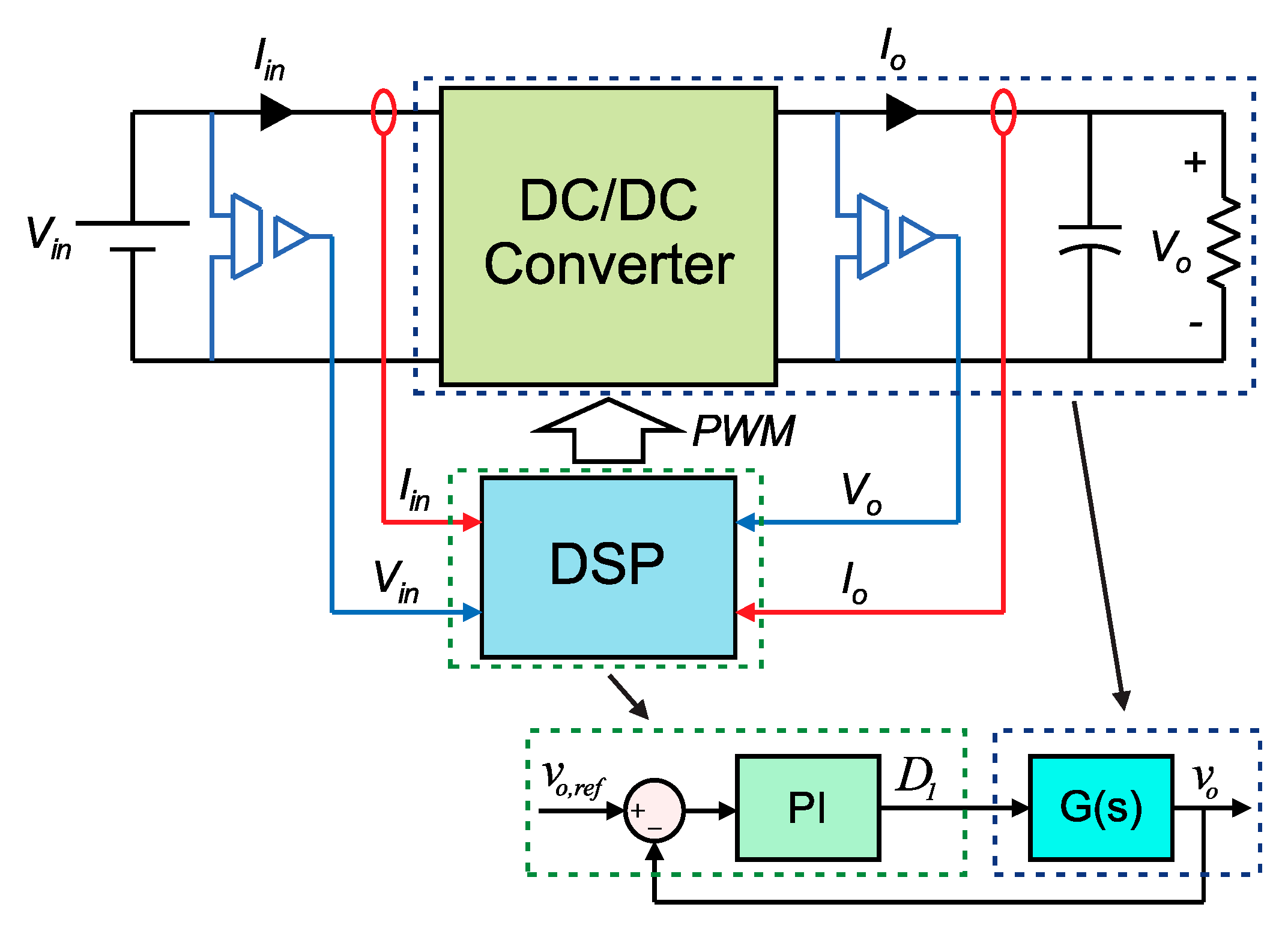

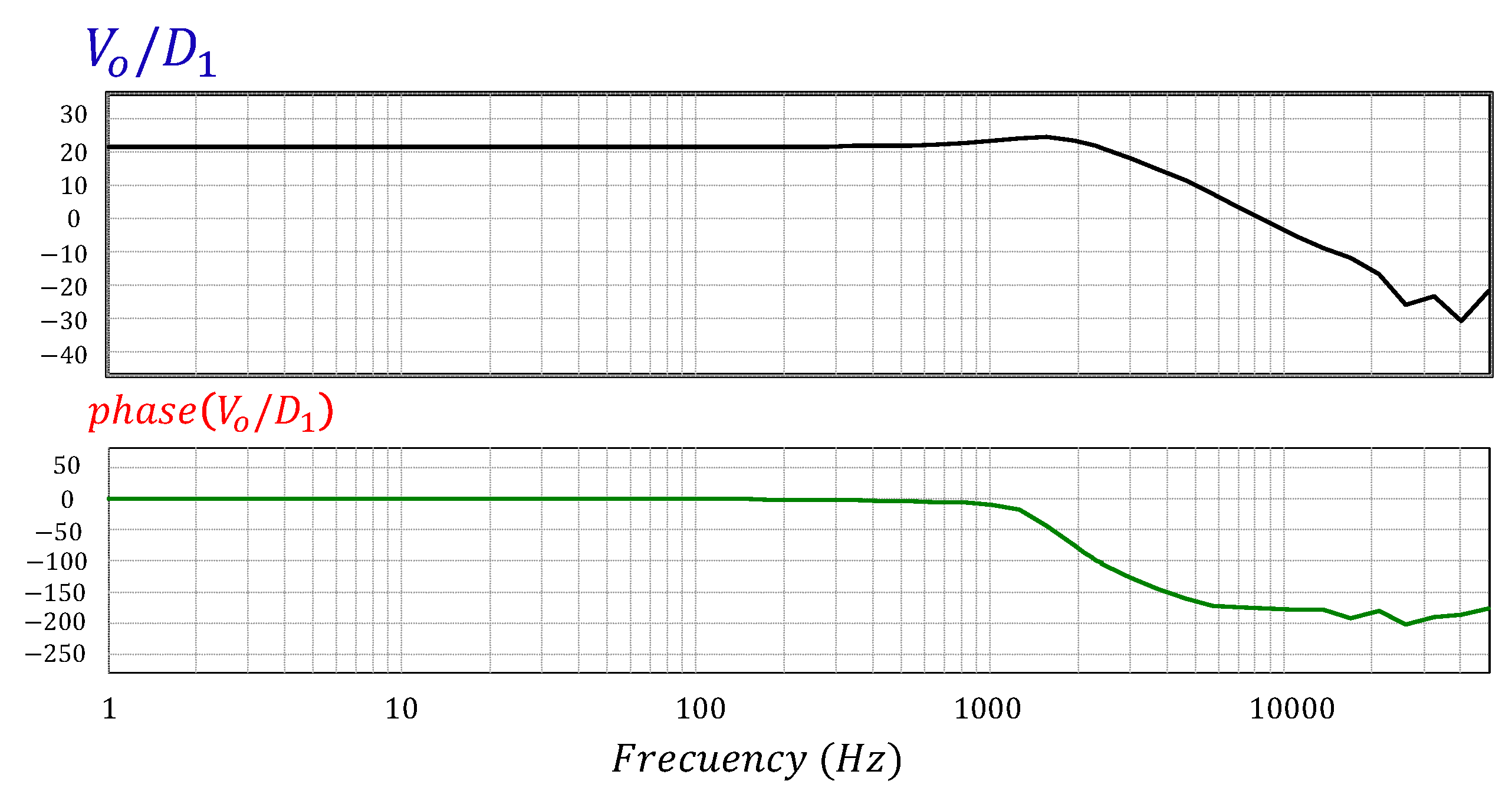

4. Control Scheme

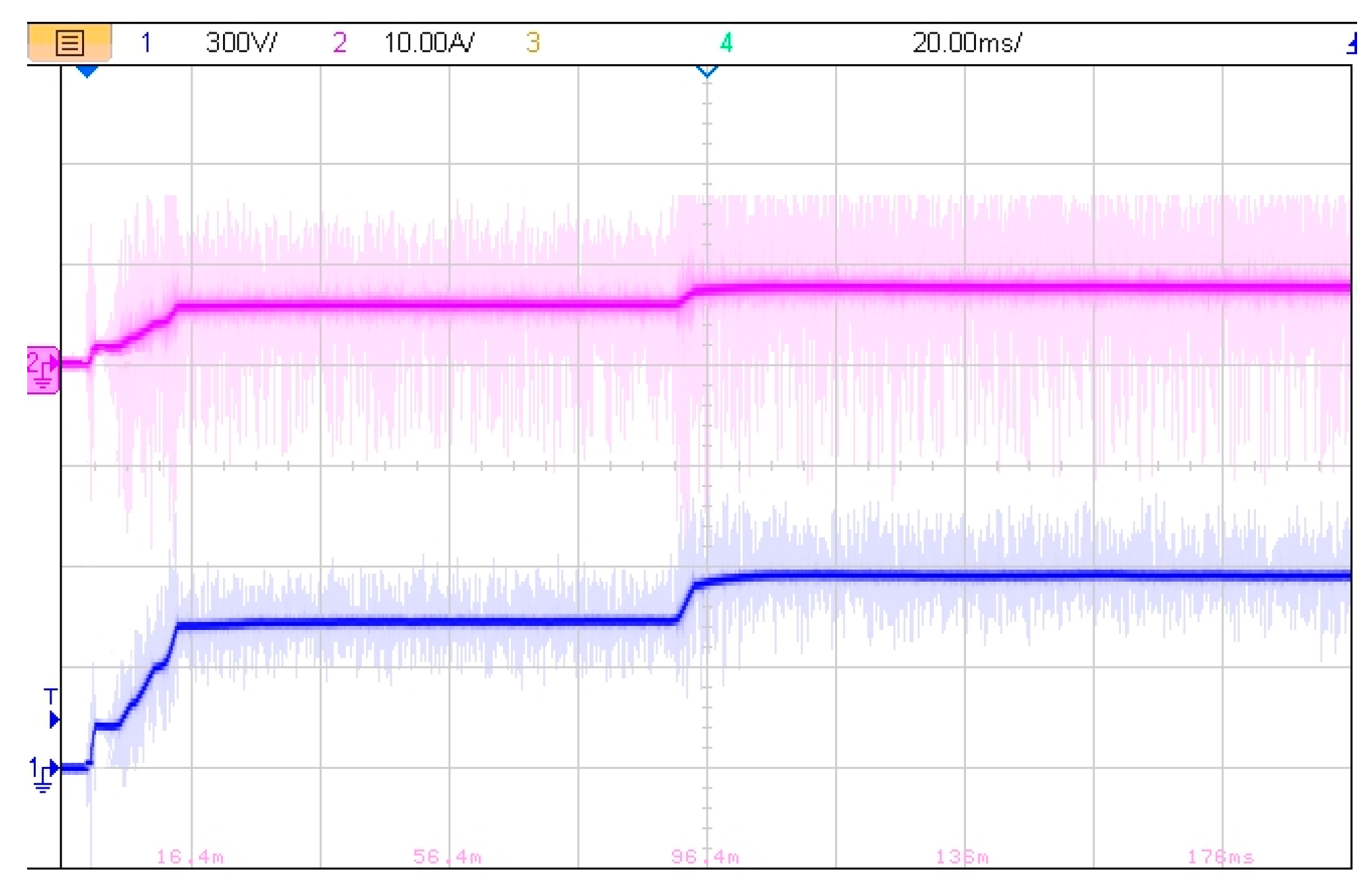

5. Experimental Results

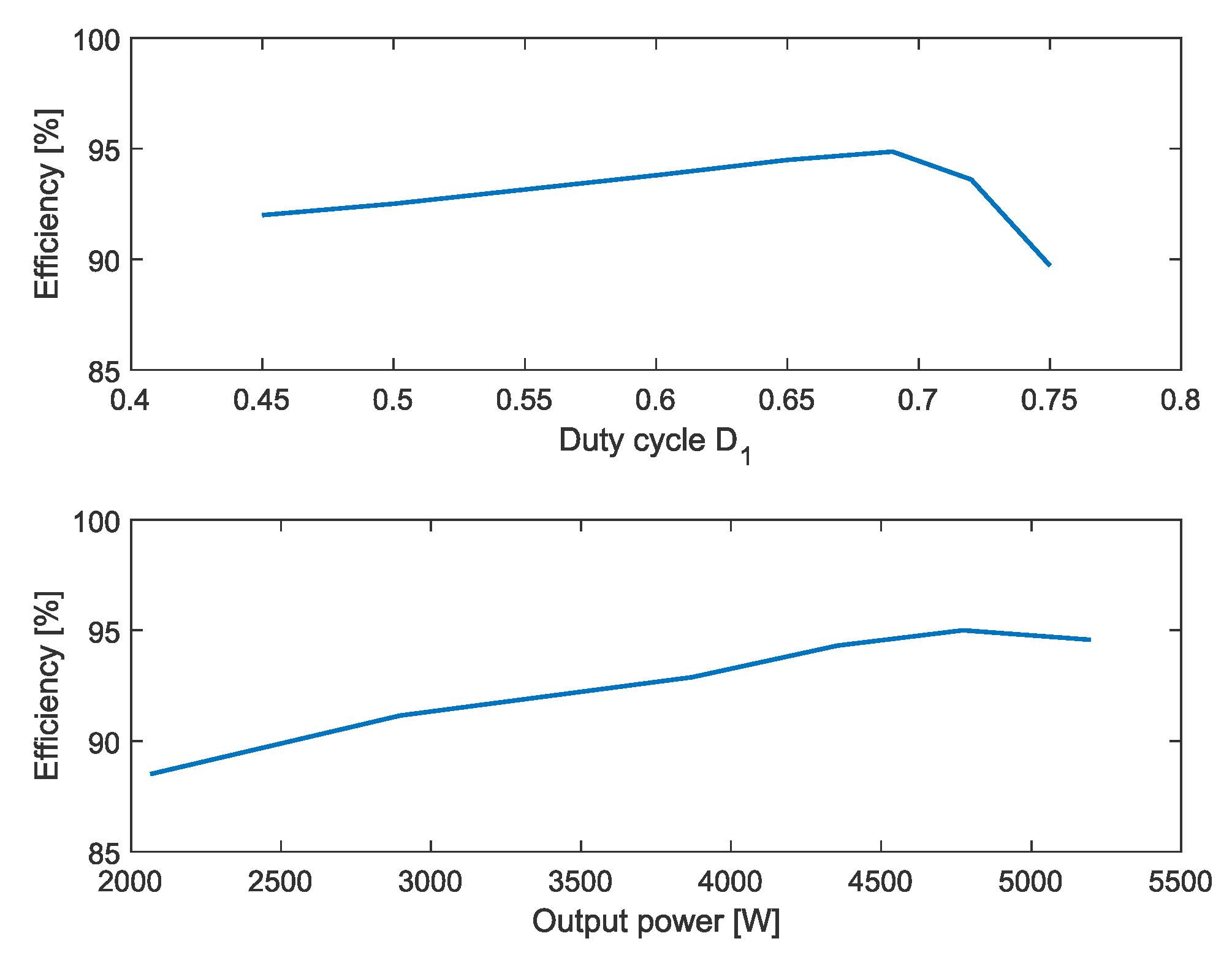

6. Efficiency Analysis

7. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Singh, S.; Singh, B. Improved power quality flyback converter fed PMBLDCM drive. In Proceedings of the 5th IEEE India International Conference on Power Electronics (IICPE), Delhi, India, 6–8 December 2012; pp. 1–5. [Google Scholar]

- Babadi, A.; Pour, A.; Amjadifard, R. Improved source-end current Power Quality performance of a BLDC motor drive using a novel DC-DC converter. In Proceedings of the Iranian Conference on Electrical Engineering (ICEE), Tehran, Iran, 2–4 May 2017; pp. 1360–1365. [Google Scholar]

- Rizzoli, G.; Zarri, L.; Wang, J.; Shen, Z.; Burgos, R.; Boroyevich, D. Design of a two-switch flyback power supply using 1.7 kV SiC devices for ultra-wide input-voltage range applications. In Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE), Milwaukee, WI, USA, 18–22 September 2016; pp. 1–5. [Google Scholar]

- Perrin, R.; Quentin, N.; Allard, B.; Martin, C.; Ali, M. High-Temperature GaN Active-Clamp Flyback Converter with Resonant Operation Mode. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 1077–1085. [Google Scholar] [CrossRef]

- Mazumdar, P.; Enjeti, P.; Balog, R. Analysis and Design of Smart PV Modules. IEEE J. Emerg. Sel. Top. Power Electron. 2014, 2, 451–459. [Google Scholar] [CrossRef]

- Lodh, T.; Pragallapati, N.; Agarwal, V. Novel Control Scheme for an Interleaved Flyback Converter Based Solar PV Microinverter to Achieve High Efficiency. IEEE Trans. Ind. Appl. 2018, 54, 3473–3482. [Google Scholar] [CrossRef]

- Kashif, M. Bidirectional flyback DC-DC converter for hybrid electric vehicle: Utility, working and PSPICE computer model. In Proceedings of the Asia Pacific Conference on Postgraduate Research in Microelectronics and Electronics, Hyderabad, India, 5–7 December 2012; pp. 61–66. [Google Scholar]

- Bhattacharya, T.; Giri, V.; Mathew, K.; Umanand, L. Multiphase Bidirectional Flyback Converter Topology for Hybrid Electric Vehicles. IEEE Trans. Ind. Electron. 2009, 56, 78–84. [Google Scholar] [CrossRef]

- Shen, C.; Chiu, P. Buck-boost-flyback integrated converter with single switch to achieve high voltage gain for PV or fuel-cell applications. IET Power Electron. 2016, 9, 1228–1237. [Google Scholar] [CrossRef]

- Yigeng, H.; Yu, W. A robust flyback converter based on high order sliding mode control for fuel cell. In Proceedings of the 40th Annual Conference of the IEEE Industrial Electronics Society (IECON), Dallas, TX, USA, 29 October–1 November 2014; pp. 3936–3940. [Google Scholar]

- Cheng, H.; Chang, Y.; Chang, C.; Hsieh, S.; Cheng, C. A Novel High-Power-Factor AC/DC LED Driver with Dual Flyback Converters. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 7, 555–564. [Google Scholar] [CrossRef]

- Tseng, S.-Y.; Huang, P.-J.; Wu, D.-H. Power Factor Corrector with Bridgeless Flyback Converter for DC Loads Applications. Energies 2018, 11, 3096. [Google Scholar] [CrossRef]

- Kazimierczuk, M. Pulse-width Modulated DC–DC Power Converters, 1st ed.; John Wiley & Sons: Hoboken, NJ, USA, 2008. [Google Scholar]

- Lin, B.; Hsieh, F. Soft-Switching Zeta–Flyback Converter with a Buck–Boost Type of Active Clamp. IEEE Trans. Ind. Electron. 2007, 54, 2813–2822. [Google Scholar]

- Pagliosa, M.; Faust, R.; Lazzarin, T.; Barbi, I. Input-series and output-series connected modular single-switch flyback converter operating in the discontinuous conduction mode. IET Power Electron. 2016, 9, 1962–1970. [Google Scholar] [CrossRef]

- Rezaei, M.; Lee, K.; Huang, A. A High-Efficiency Flyback Micro-inverter With a New Adaptive Snubber for Photovoltaic Applications. IEEE Trans. Power Electron. 2016, 31, 318–327. [Google Scholar] [CrossRef]

- Tamyurek, B.; Kirimer, B. An interleaved high-power flyback inverter for photovoltaic applications. IEEE Trans. Power Electron. 2015, 30, 3228–3241. [Google Scholar] [CrossRef]

- Zumel, P.; García, O.; Oliver, J.; Cobos, J. Differential-Mode EMI Reduction in a Multiphase DCM Flyback Converter. IEEE Trans. Power Electron. 2009, 24, 2013–2020. [Google Scholar] [CrossRef]

- Dong, M.; Tian, X.; Li, L.; Song, D.; Wang, L.; Zhao, M. Model-Based Current Sharing Approach for DCM Interleaved Flyback Micro-Inverter. Energies 2018, 11, 1685. [Google Scholar] [CrossRef]

- Pesce, C.; Blasco Gimenez, R.; Riedemann, J.; Andrade, I.; Pena, R. A DC-DC Converter Based on Modified Flyback Converter Topology. IEEE Lat. Am. Trans. 2016, 14, 3949–3956. [Google Scholar] [CrossRef]

- Alganidi, A. A Comparison between Different Snubbers for Flyback Converters. Master’s Thesis, The University of Western Ontario, London, ON, Canada, 2017. Available online: https://ir.lib.uwo.ca/etd/5153 (accessed on 22 May 2019).

- Kreyszig, E. Advanced Engineering Mathematics, 10th ed.; John Wiley & Sons: Hoboken, NJ, USA, 2010. [Google Scholar]

| Variable | Description | Value | Variable | Description | Value |

|---|---|---|---|---|---|

| Input voltage | Output capacitor | ||||

| Rated output voltage | Switching frequency | ||||

| Magnetizing inductance | Number of stages | ||||

| Transformers turns ratio | 1 | Rated power | W |

| Power Device | Experimental Results | Simulation Results | |

|---|---|---|---|

| Main Switch | |||

| - Positive peak current | : | 32 A | 31.5 A |

| - Negative peak current | : | 16 A | 15.3 A |

| - Maximum collector-emitter voltage | : | 400 V | 398.5 A |

| Snubber Switch | |||

| - Positive peak current | : | 24 A | 23.3 A |

| - Negative peak current | : | 32 A | 31.3 A |

| Main Diode | |||

| - Maximum current | : | 57 A | 56.2 A |

| 0.45 | 382 | 23.67 | 2091 | 2273 | 91.99 |

| 0.5 | 425 | 29.07 | 2581 | 2790 | 92.50 |

| 0.6 | 510 | 41.28 | 3717 | 3963 | 93.79 |

| 0.65 | 553 | 48.10 | 4362 | 4616 | 94.49 |

| 0.69 | 589 | 53.96 | 4916 | 5182 | 94.86 |

| 0.72 | 612 | 58.94 | 5353 | 5719 | 93.60 |

| 0.75 | 637 | 64.57 | 5808 | 6474 | 89.71 |

| 3.5 | 24.3 | 2065 | 2333 | 88.51 |

| 4.91 | 33.1 | 2897 | 3178 | 91.15 |

| 6.56 | 43.41 | 3870 | 4167 | 92.88 |

| 7.38 | 48.09 | 4354 | 4616 | 94.32 |

| 8.09 | 52.34 | 4773 | 5024 | 95.00 |

| 8.81 | 57.25 | 5198 | 5496 | 94.57 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Pesce, C.; Riedemann, J.; Pena, R.; Jara, W.; Maury, C.; Villalobos, R. A Modified Step-Up DC-DC Flyback Converter with Active Snubber for Improved Efficiency. Energies 2019, 12, 2066. https://doi.org/10.3390/en12112066

Pesce C, Riedemann J, Pena R, Jara W, Maury C, Villalobos R. A Modified Step-Up DC-DC Flyback Converter with Active Snubber for Improved Efficiency. Energies. 2019; 12(11):2066. https://doi.org/10.3390/en12112066

Chicago/Turabian StylePesce, Cristian, Javier Riedemann, Ruben Pena, Werner Jara, Camilo Maury, and Rodrigo Villalobos. 2019. "A Modified Step-Up DC-DC Flyback Converter with Active Snubber for Improved Efficiency" Energies 12, no. 11: 2066. https://doi.org/10.3390/en12112066

APA StylePesce, C., Riedemann, J., Pena, R., Jara, W., Maury, C., & Villalobos, R. (2019). A Modified Step-Up DC-DC Flyback Converter with Active Snubber for Improved Efficiency. Energies, 12(11), 2066. https://doi.org/10.3390/en12112066