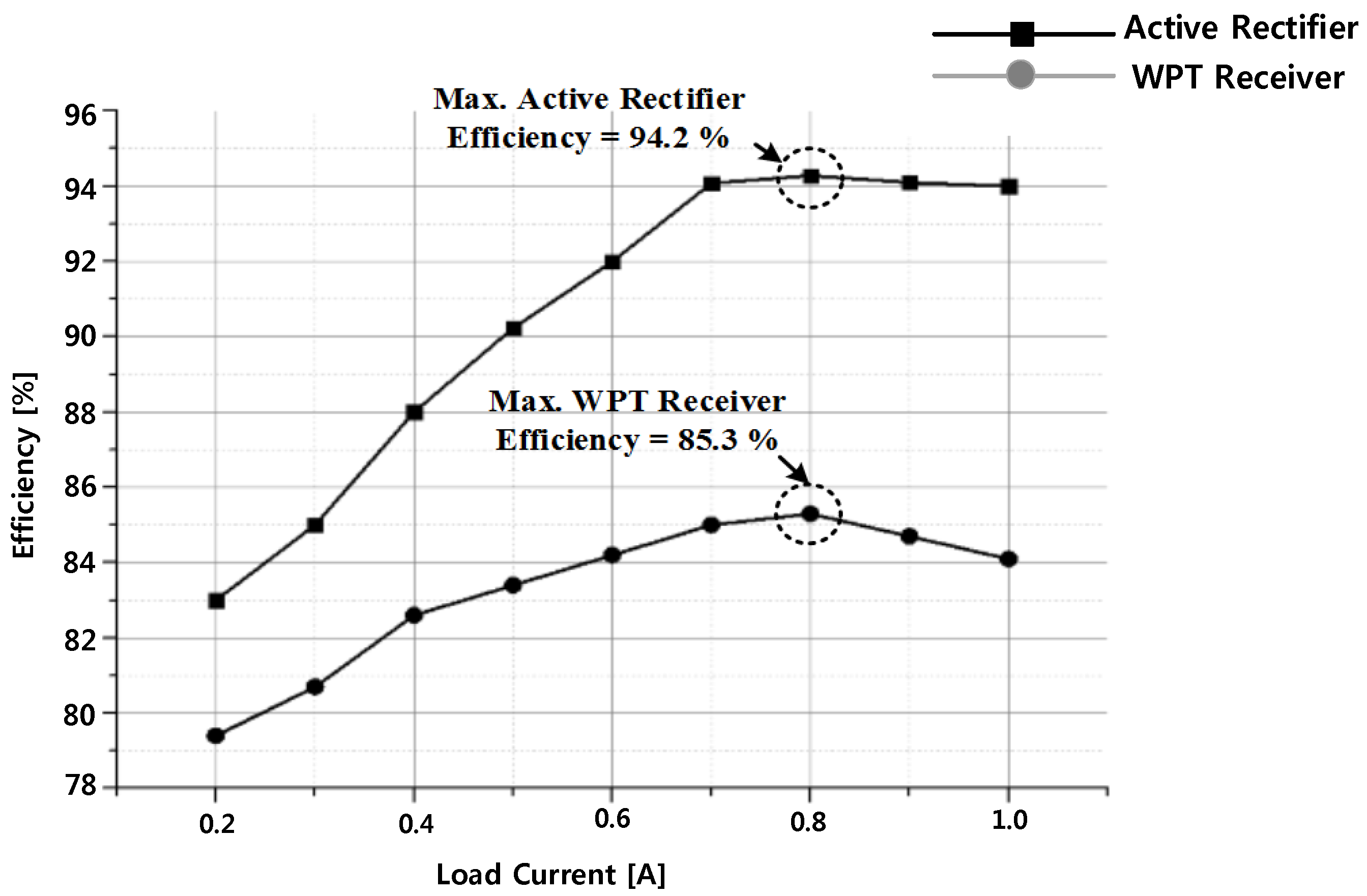

Design of Peak Efficiency of 85.3% WPC/PMA Wireless Power Receiver Using Synchronous Active Rectifier and Multi Feedback Low-Dropout Regulator

Abstract

:1. Introduction

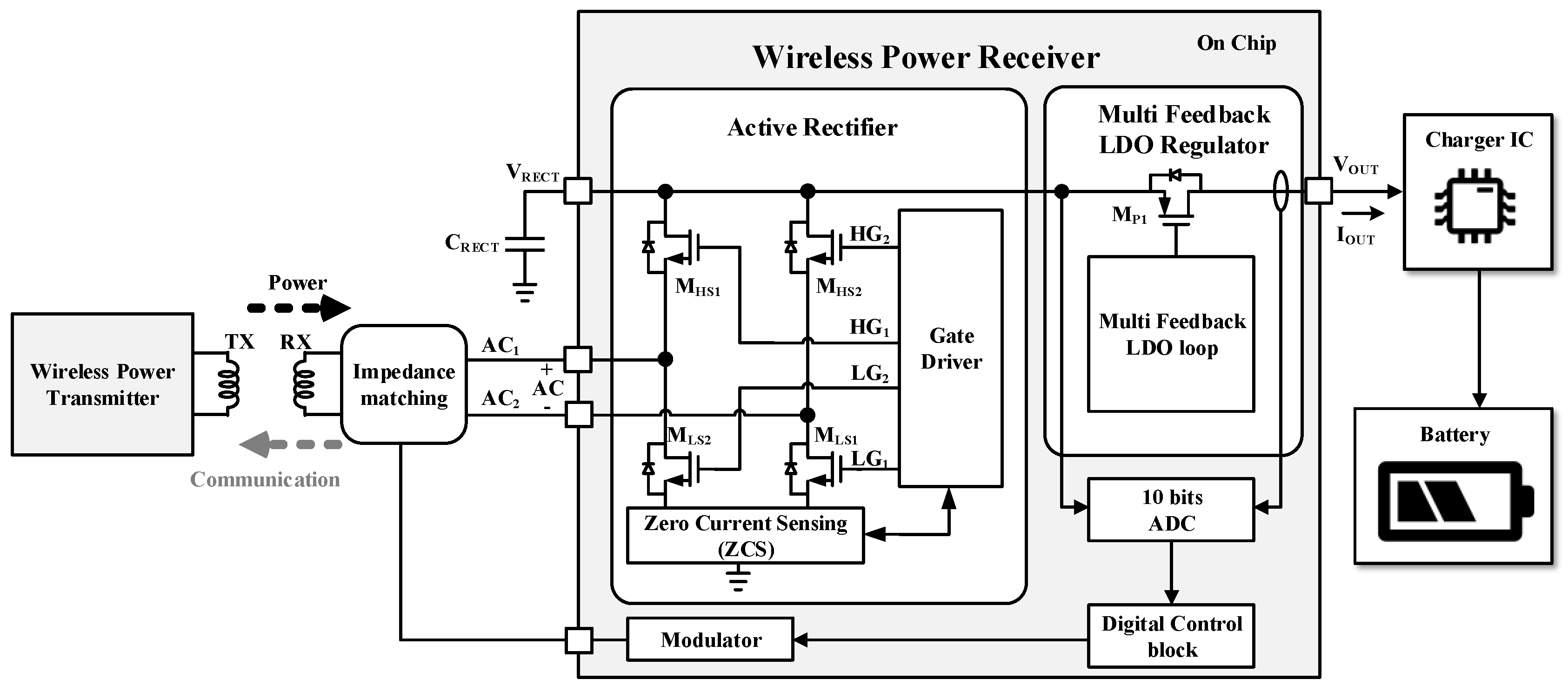

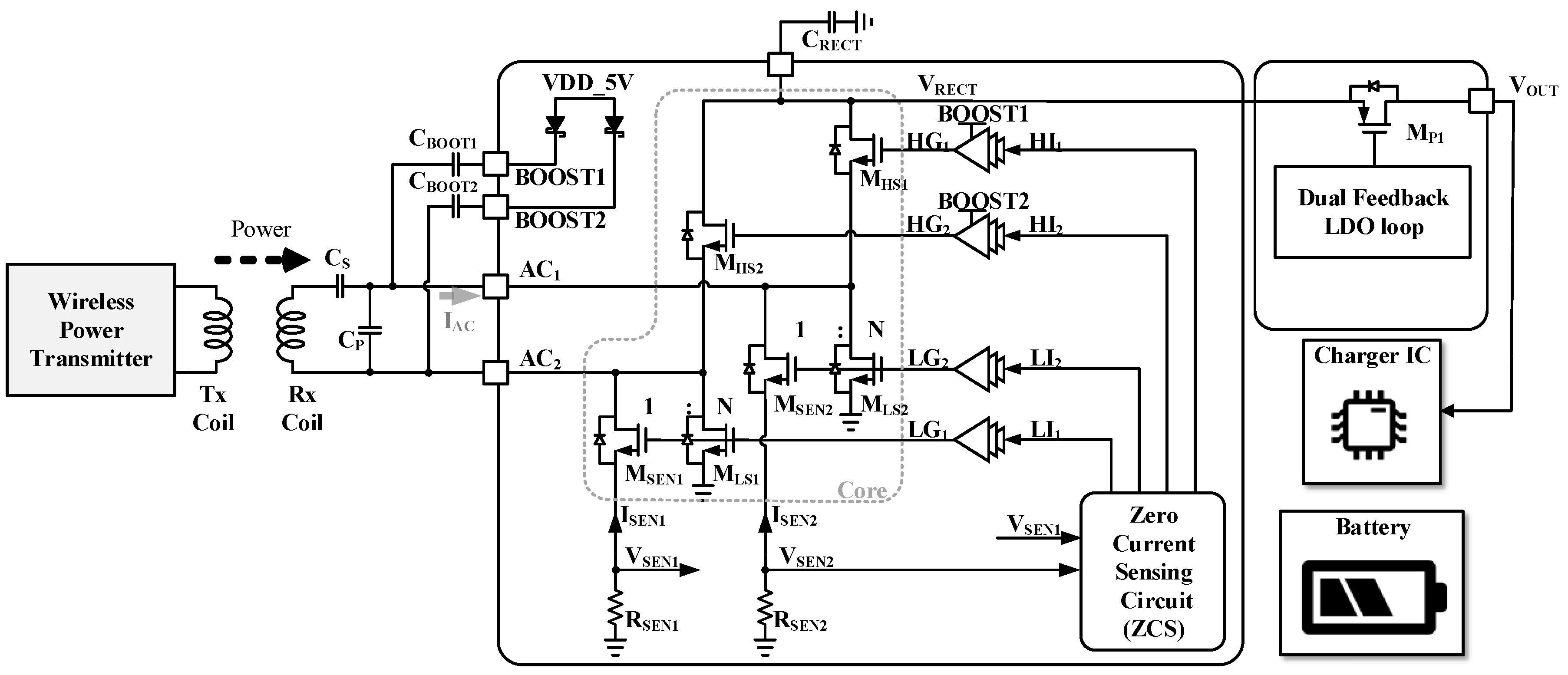

2. Proposed Wireless Power Receiver Design and Its Implementation

2.1. Architecture

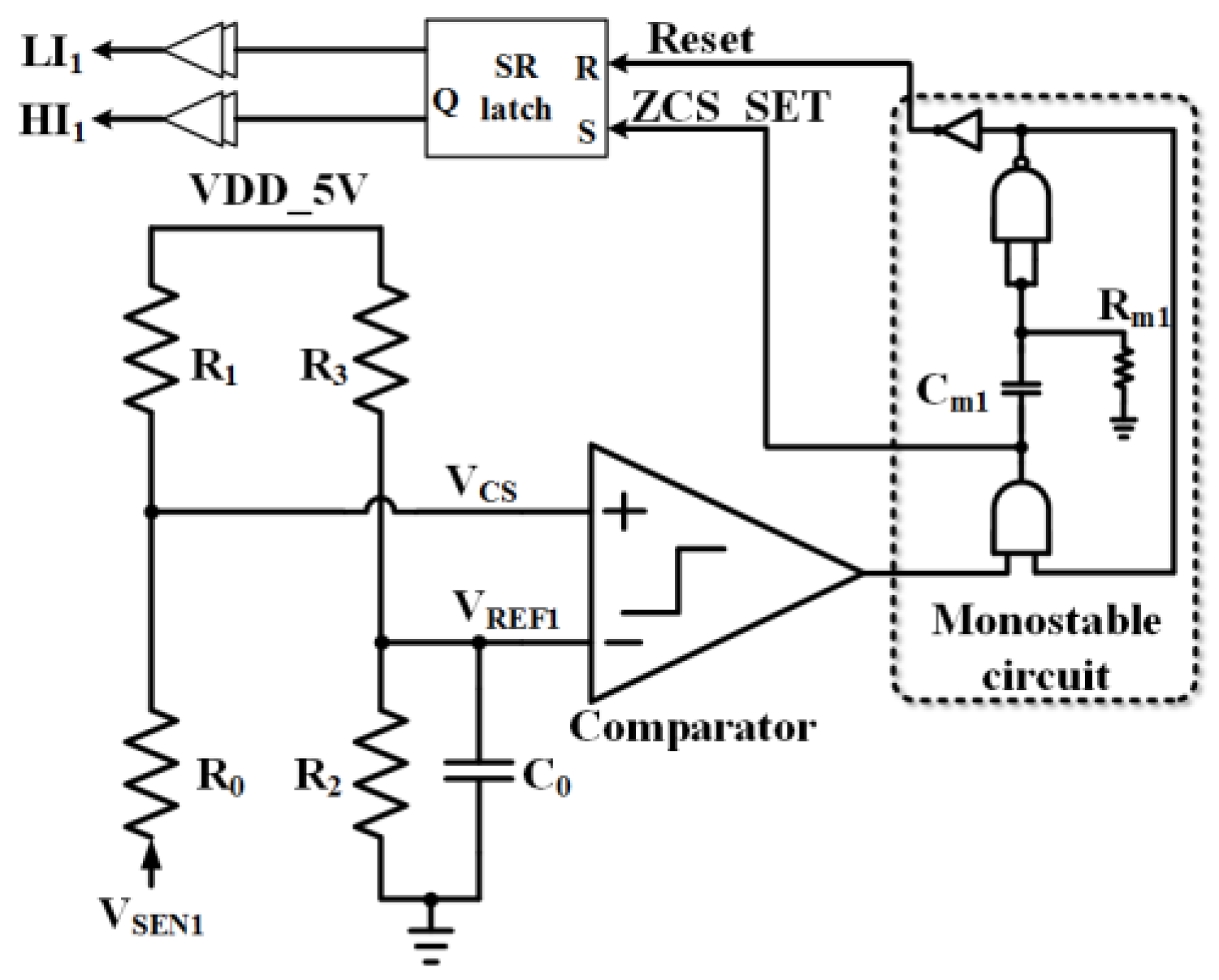

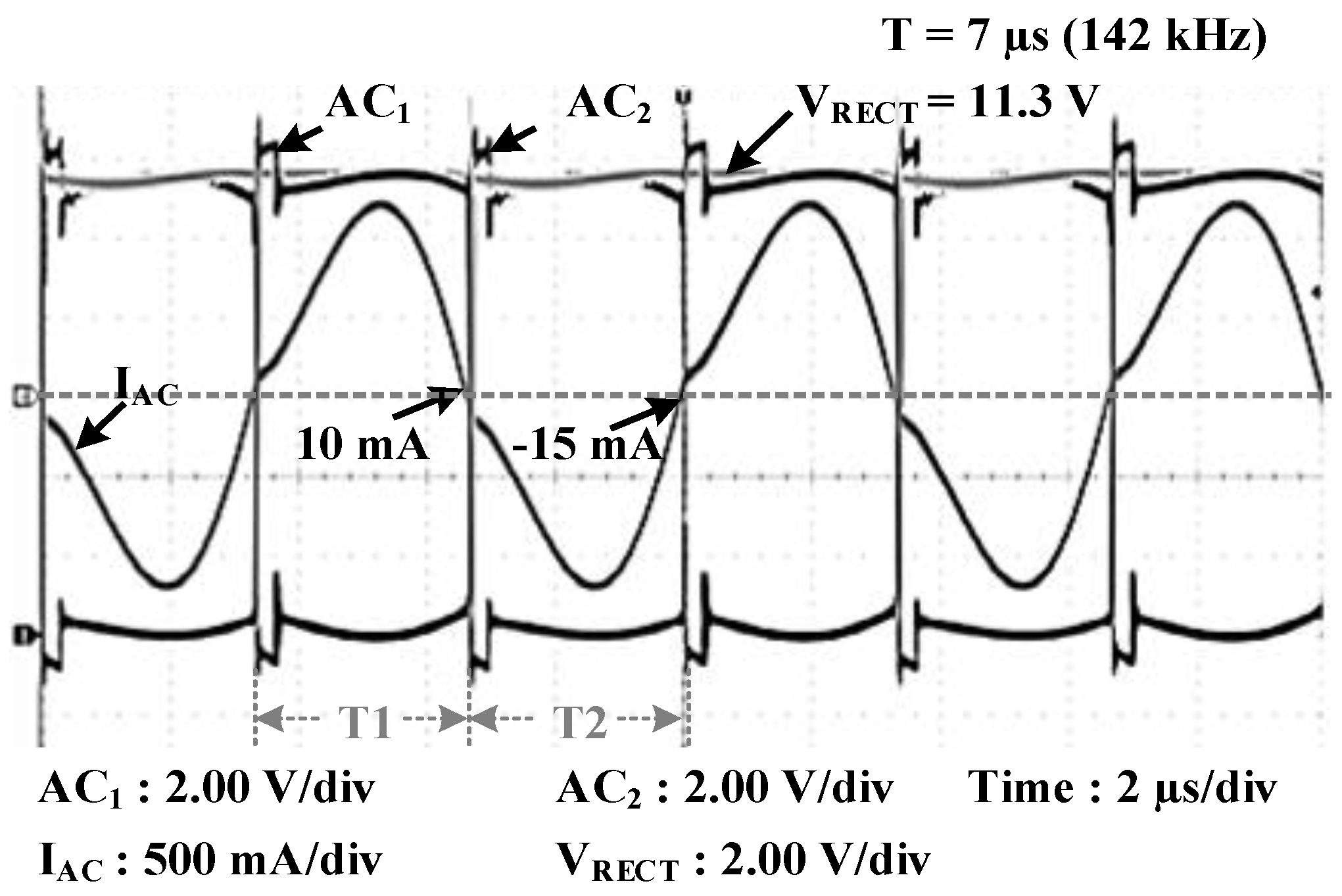

2.2. Active Rectifier

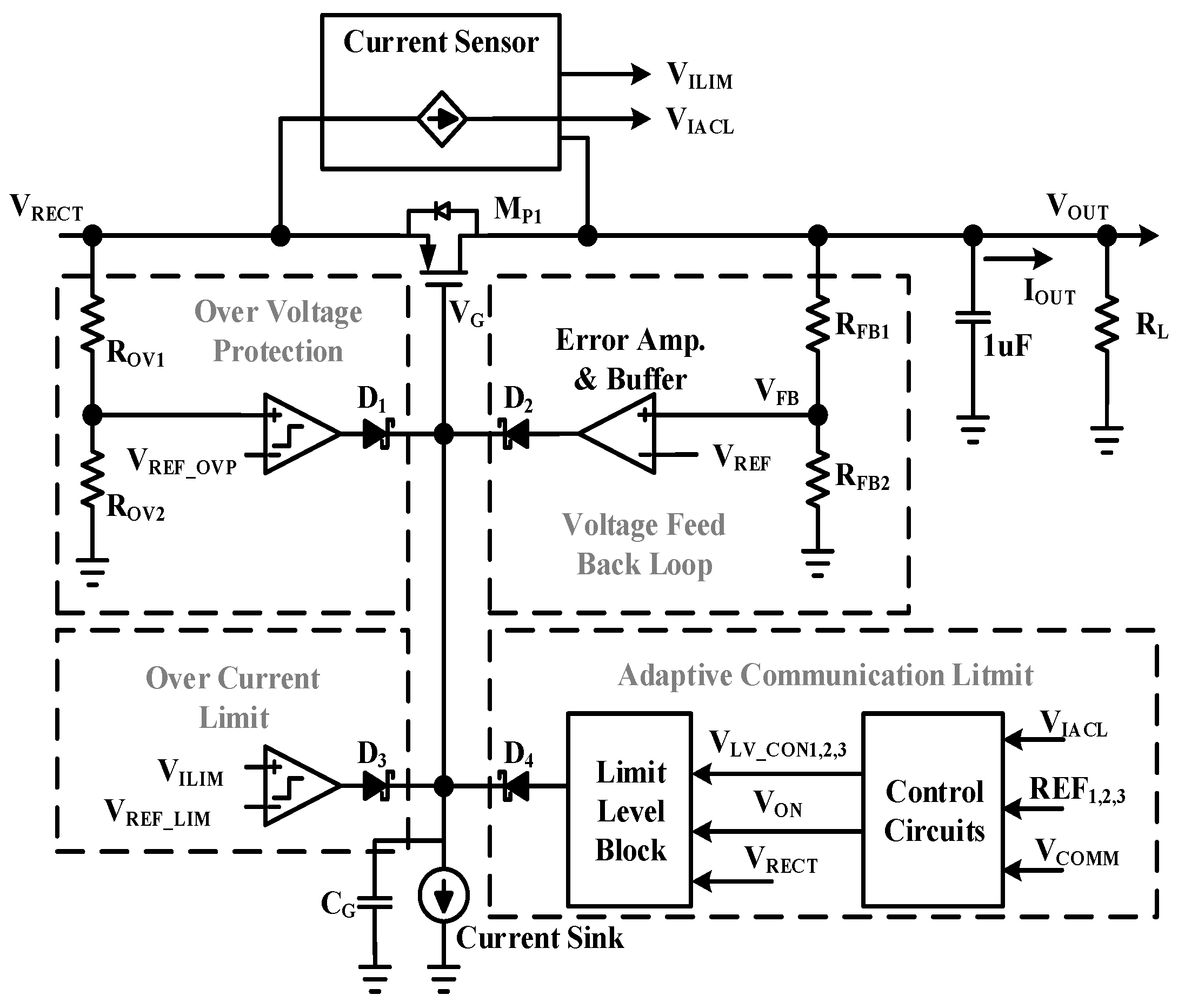

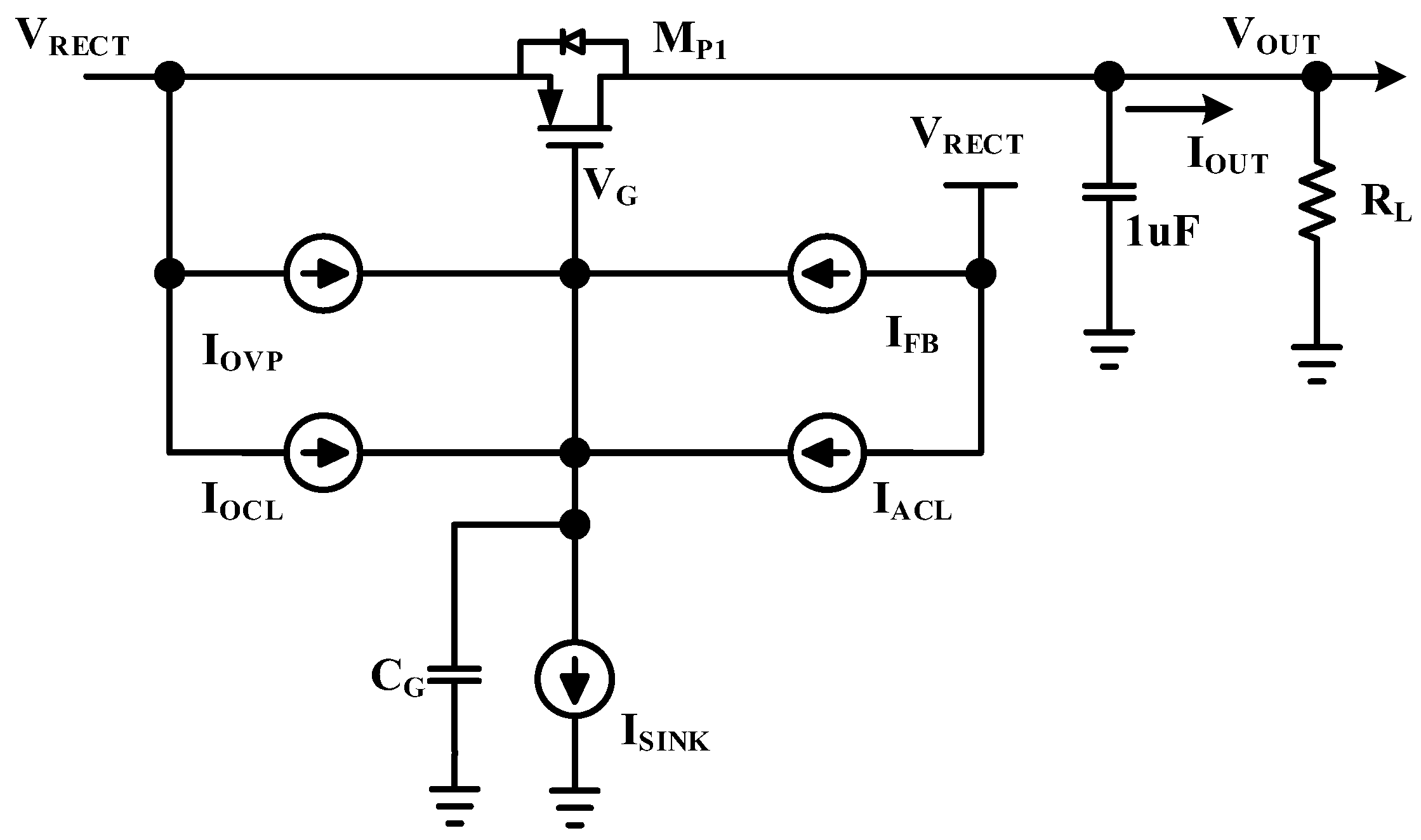

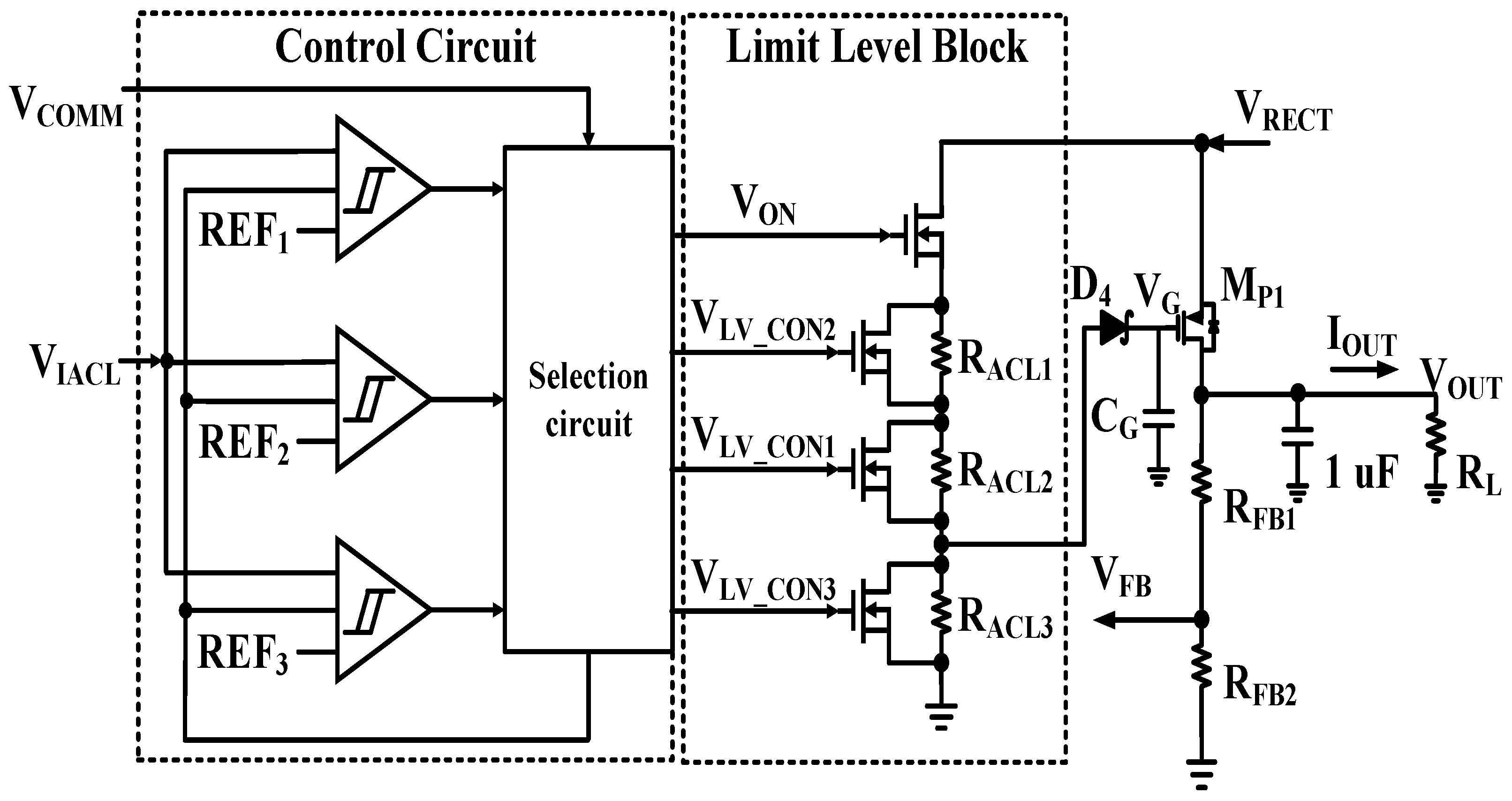

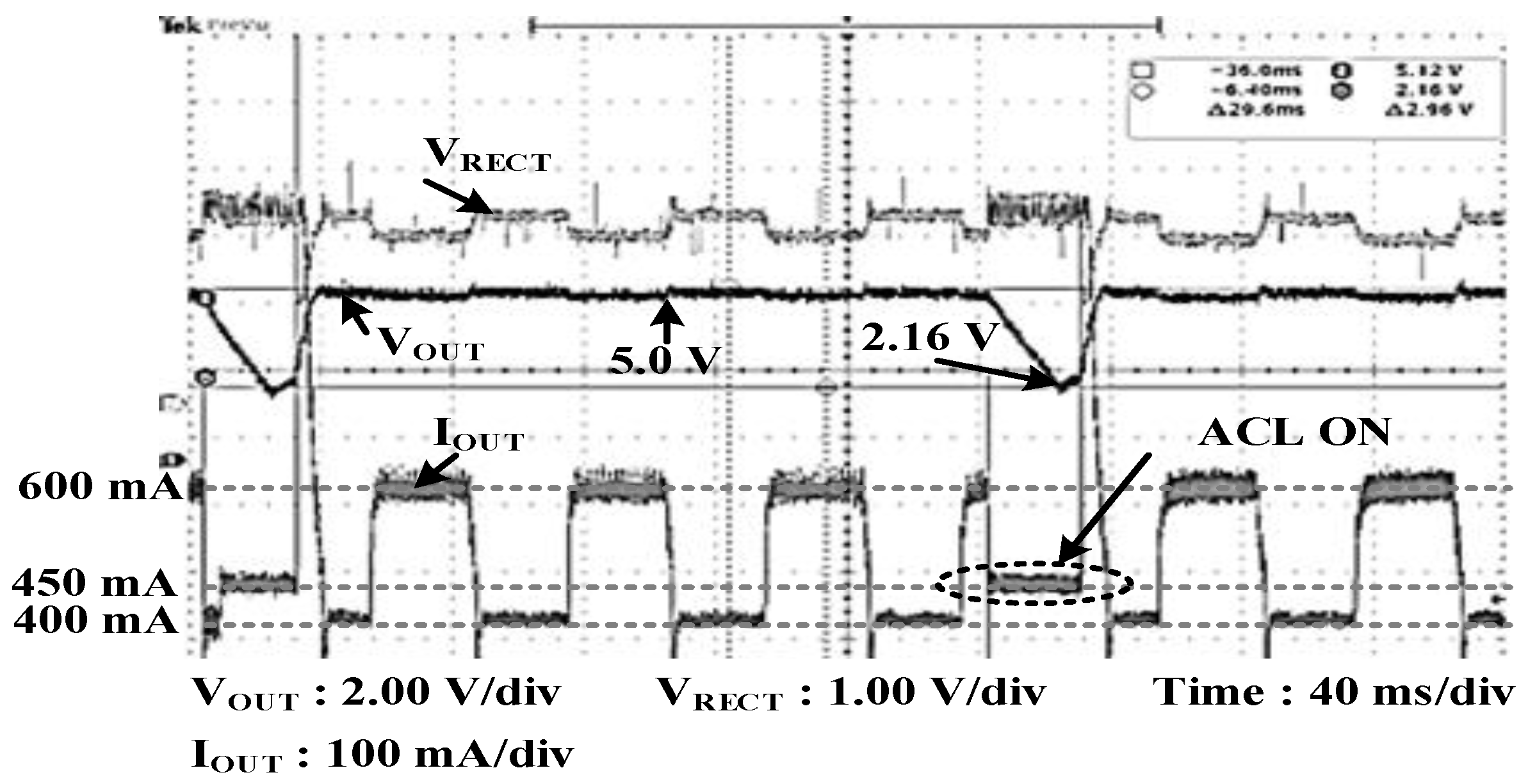

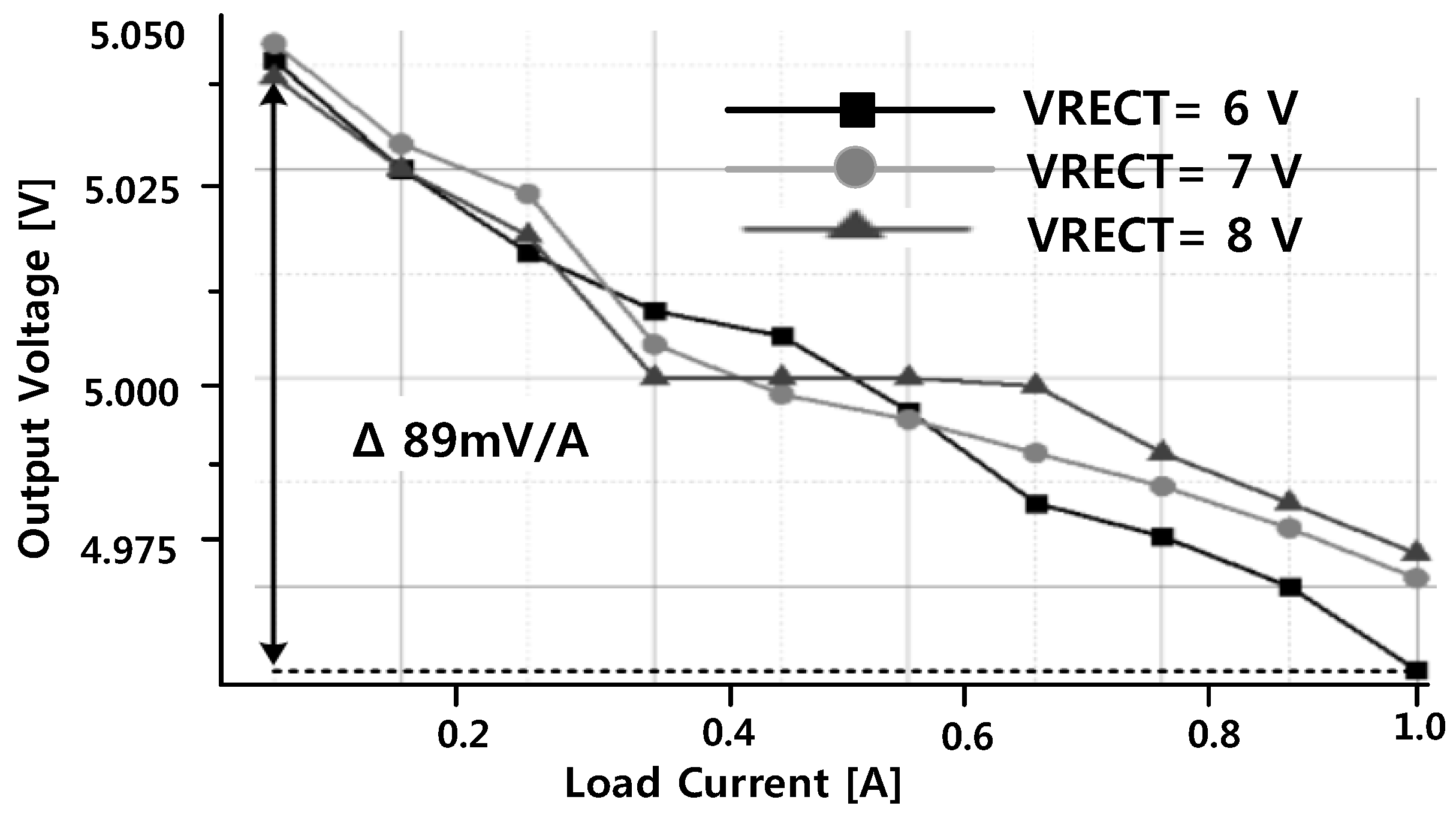

2.3. Multi Feedback LDO (MF-LDO) Regulator

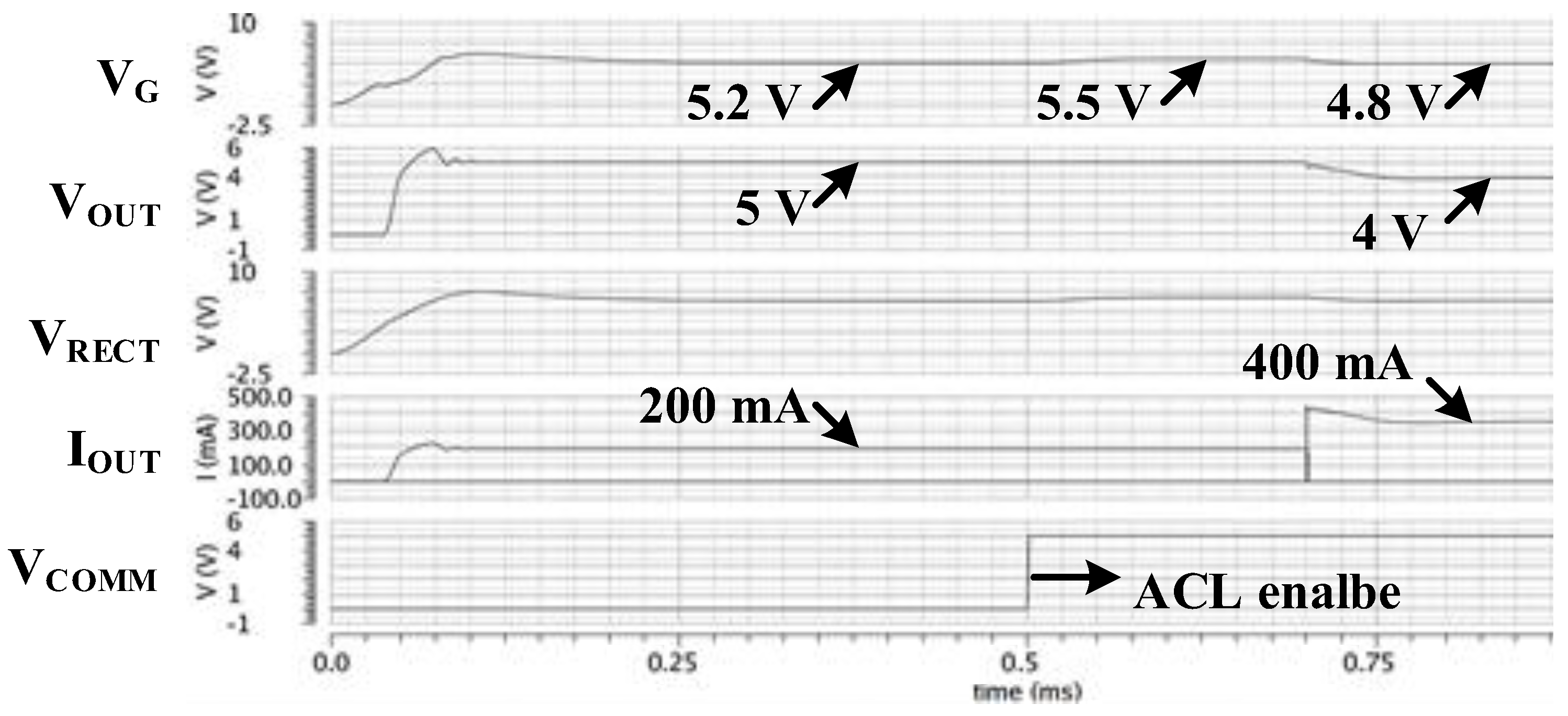

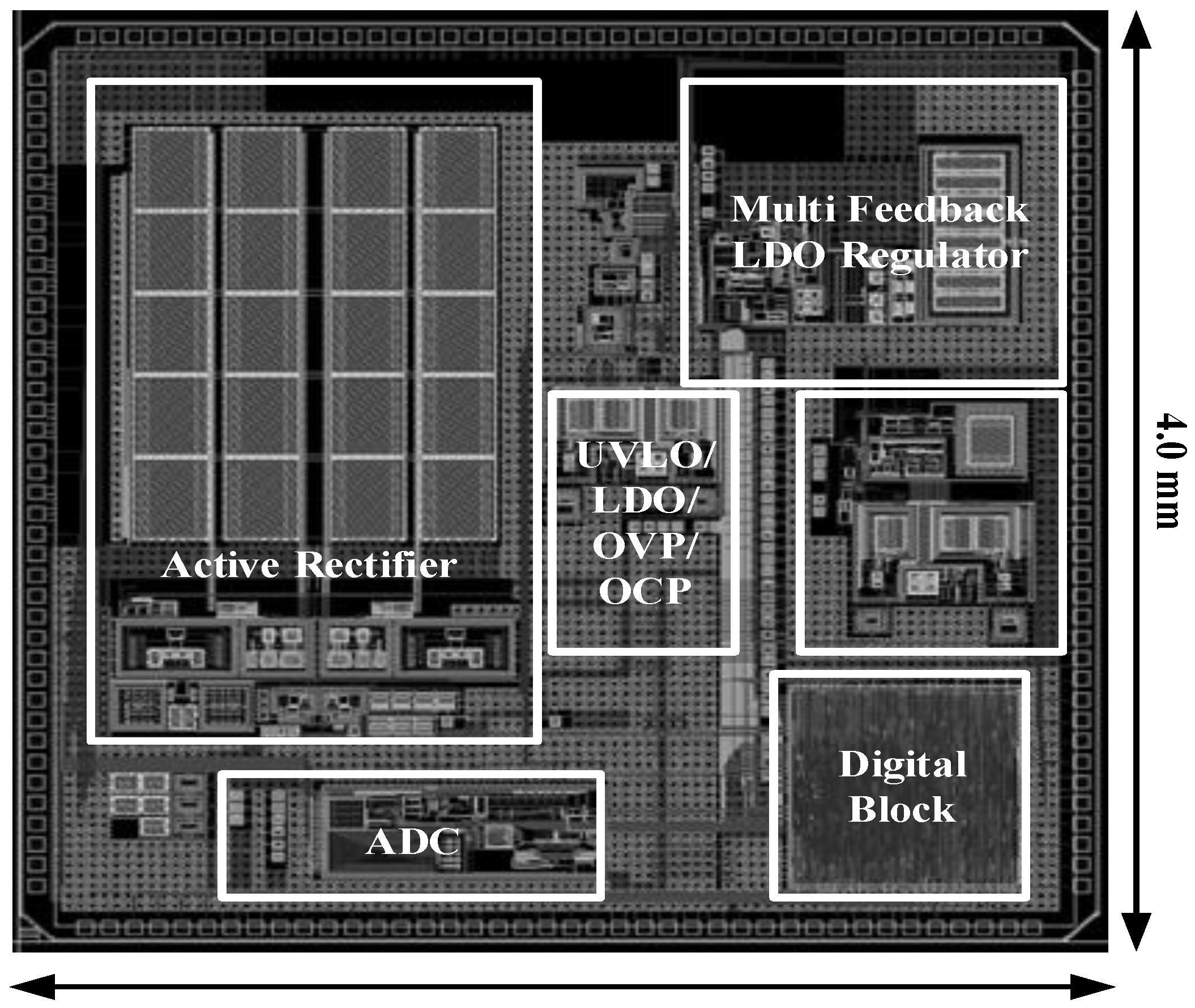

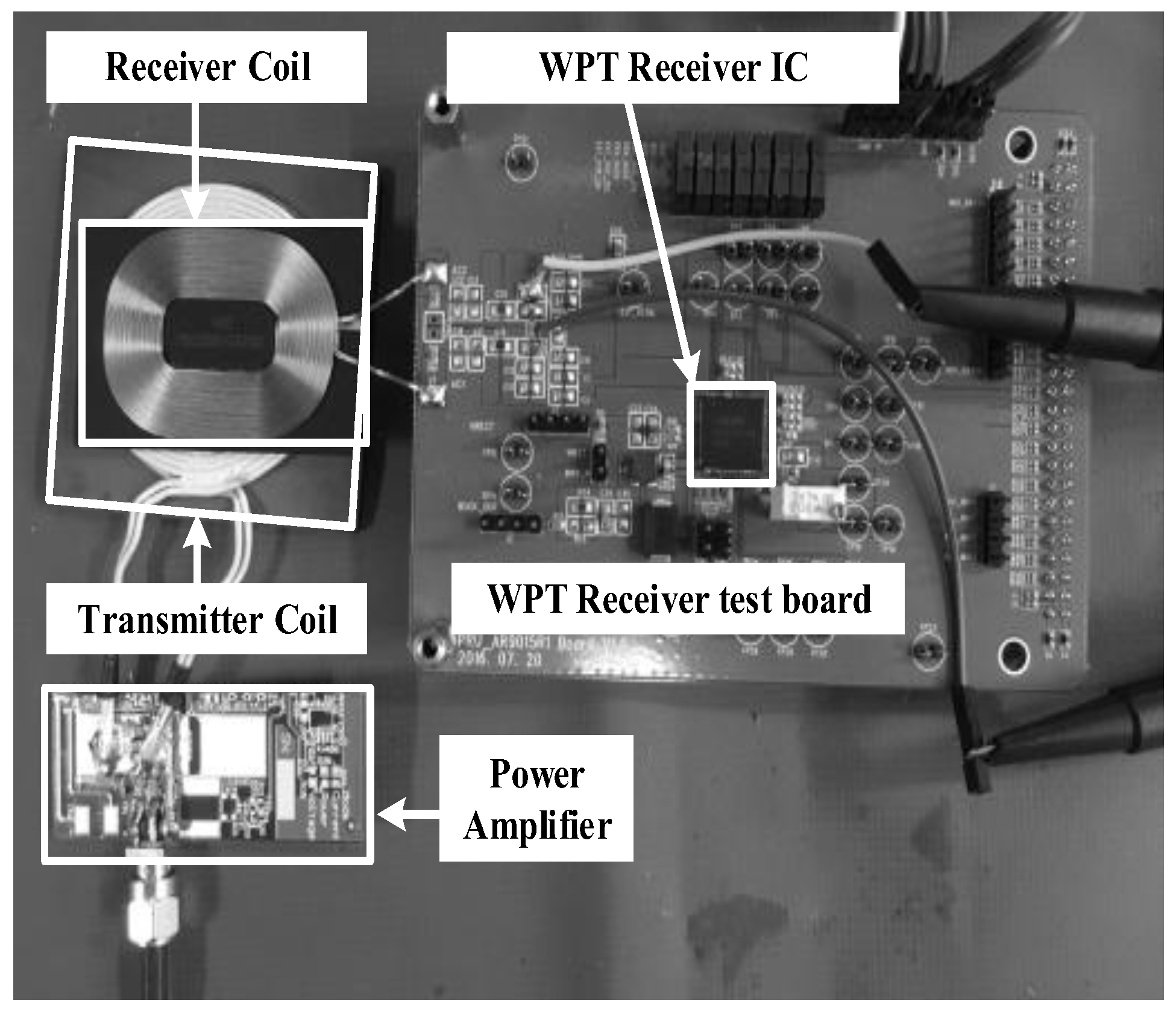

3. Experimental Results

4. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Wireless Power Consortium System. Description Wireless Power Transfer, Vol. I: Low Power, Part 1: Interface Definition Version 1.0. July 2010. Available online: https://www.wirelesspowerconsortium.com (accessed on 23 February 2018).

- Kiani, M.; Lee, B.; Yeon, P.; Ghovanloo, M. A Q-modulation technique for efficient inductive power transmission. IEEE J. Solid-State Circuits 2015, 50, 2839–2848. [Google Scholar] [CrossRef] [PubMed]

- Choi, J.-H.; Yeo, S.-K.; Park, S.; Lee, J.-S.; Cho, G.-H. Resonant regulating rectifiers (3R) operating for 6.78 MHz resonant wireless power transfer (RWPT). IEEE J. Solid-State Circuits 2013, 48, 2989–3001. [Google Scholar] [CrossRef]

- Moh, K.-G.; Neri, F.; Moon, S.; Yeon, P.; Yu, J.; Cheon, Y.; Roh, Y.; Ko, M.; Park, B.-H. A fully integrated 6W wireless power receiver operating at 6.78MHz with magnetic resonance coupling. In Proceedings of the 2015 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 22–26 February 2015; IEEE: Piscataway, NJ, USA, 2015; pp. 230–231. [Google Scholar]

- Cheng, L.; Ki, W.H.; Tsui, C.Y. A 6.78-MHz single-stage wireless power receiver with a 3-mode reconfigurable resonant regulating rectifier. IEEE J. Solid-State Circuits 2017, 52, 1412–1423. [Google Scholar] [CrossRef]

- Koh, K.; Beh, T.; Imura, T.; Hori, Y. Impedance Matching and Power Division Using Impedance Inverter for Wireless Power Transfer via Magnetic Resonant Coupling. IEEE Trans. Ind. Appl. 2013, 50, 2061–2070. [Google Scholar] [CrossRef]

- Hashemi, S.; Sawan, M.; Savania, Y. A Novel Fully-Integrated Drop Less Voltage CMOS Rectifier for Wireless Powered Devices. In Proceedings of the 2007 Internatonal Conference on Microelectronics, Cairo, Egypt, 29–31 December 2007; pp. 333–336. [Google Scholar]

- Park, H.-G.; Jang, J.-H.; Kim, H.-J.; Park, Y.-J.; Oh, S.J.; Pu, Y.G.; Hwang, K.C.; Yang, Y.; Lee, K.-Y. A Design of a Wireless Power Receiving Unit With a High-Efficiency 6.78-MHz Active Rectifier Using Shared DLLs for Magnetic-Resonant A4 WP Applications. IEEE Trans. Power Electron. 2016, 31, 4484–4498. [Google Scholar] [CrossRef]

- Guo, S.; Lee, H. An Efficiency-Enhanced CMOS Rectifier With Unbalanced-Biased Comparators for Transcutaneous-Powered High-Current Implants. IEEE J. Solid-State Circuits 2009, 44, 1796–7804. [Google Scholar] [CrossRef]

- Lee, H.-M.; Ghovanloo, M. An Adaptive Reconfigurable Active Voltage Doubler/Rectifier for Extended-Range Inductive Power Transmission. IEEE Trans. Circuits Syst. II Express Briefs 2012, 59, 481–485. [Google Scholar] [CrossRef]

- Lu, Y.; Ki, W.-H. A 13.56 MHz CMOS Active Rectifier with Switched-Offset and Compensated Biasing for Biomedical Wireless Power Transfer Systems. IEEE Trans. Biomed. Circuits Syst. 2013, 8, 334–344. [Google Scholar]

- Cheng, L.; Ki, W.H.; Lu, Y.; Yim, T.S. Adaptive on/off delay-compensated active rectifiers for wireless power transfer systems. IEEE J. Solid-State Circuits 2016, 51, 712–723. [Google Scholar]

- Lam, Y.-H.; Ki, W.-H.; Tsui, C.-Y. Integrated Low-Loss CMOS Active Rectifier for Wirelessly Powered Devices. IEEE Trans. Circuits Syst. II: Express Briefs 2006, 53, 1378–1382. [Google Scholar] [CrossRef]

- Tseng, R.; Novak, B.; Shevde, S.; Grajski, K.A. Introduction to the alliance for wireless power loosely-coupled wireless power transfer system specification version 1.0. In Proceedings of the 2013 IEEE Wireless Power Transfer (WPT), Perugia, Italy, 15–16 May 2013; pp. 79–83. [Google Scholar]

- Park, Y.-J.; Oh, S.J.; Kim, S.Y.; Cho, S.; Kim, M.C.; Park, J.-H.; Lee, D.S.; Kim, H.J.; Lee, K.-Y. A Design of Inductive Coupling Wireless Power Receiver with High-Efficiency Active Rectifier and Multi Feedback LDO Regulator. In Proceedings of the 2016 IEEE Wireless Power Transfer Conference (WPTC), Aveiro, Portugal, 5–6 May 2016. [Google Scholar]

- Shinohara, H.; Miyaji, K. A ZVS CMOS active diode rectifier with voltage-time-conversion delay-locked loop for wireless power transmission. In Proceedings of the 2015 IEEE Asian Solid-State Circuits Conference (A-SSCC), Xiamen, China, 9–11 November 2015; pp. 3–15. [Google Scholar]

- Park, Y.-J.; Park, H.-G.; Lee, J.; Oh, S.J.; Jang, J.H.; Kim, S.Y.; Pu, Y.G.; Hwang, K.C.; Yang, Y.; Seo, M.; et al. A design of wide input range triple-mode active rectifier with peak efficiency of 94.2% and maximum output power of 8 W for wireless power receiver in 0.18 μM BCD. Analog Integr. Circuits Signal Process. 2016, 86, 255–265. [Google Scholar] [CrossRef]

- Park, Y.-J.; Jang, B.G.; Park, S.-M.; Ryu, H.-C.; Oh, S.J.; Kim, S.-Y.; Pu, Y.G.; Yoo, S.-S.; Hwang, K.C.; Yang, Y.; et al. A Triple-Mode Wireless Power Receiving Unit with 85.5% System Efficiency for A4WP, WPC and PMA Applications. IEEE Trans. Power Electron. 2018, 33, 3141–3156. [Google Scholar] [CrossRef]

| Parameters | [8] | [17] | [18] | This Work |

|---|---|---|---|---|

| Technology | 0.18 μm BCD | 0.18 μm CMOS | 0.18 μm BCD | 0.18 μm BCD |

| Supported standards | A4WP | A4WP | WPC and PMA A4WP | WPC and PMA |

| Input frequency | 6.78 MHz | 6.78 MHz | 85 kHz~500 kHz 6.78 MHz | 87 kHz~375 kHz |

| Input Voltage Range (V) | 7–20 | 7–20 | 3–20 | 3–20 |

| Efficiency of rectifier (%) | 91.5 | 94.2 (rectifier only) | 91.7 @ 6.78 MHz 92.7 @ 150 kHz | 94.2 @ 150 kHz |

| Post-regulator | DC–DC converter | N/A | DC–DC converter | Low-dropout regulator |

| System efficiency (%) | 80.86 | N/A | 84.5 @ 6.78 MHz 85.5 @ 150 kHz | 85.3 |

| Max. output power (W) | 6 | 8 | 9 | 5 |

| Die area (mm2) | 12.25 | 3.45 | 17.5 | 16.0 |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Khan, Z.H.N.; Park, Y.-J.; Oh, S.J.; Jang, B.G.; Park, S.-M.; Abbasizadeh, H.; Pu, Y.G.; Hwang, K.C.; Yang, Y.; Lee, M.; et al. Design of Peak Efficiency of 85.3% WPC/PMA Wireless Power Receiver Using Synchronous Active Rectifier and Multi Feedback Low-Dropout Regulator. Energies 2018, 11, 479. https://doi.org/10.3390/en11030479

Khan ZHN, Park Y-J, Oh SJ, Jang BG, Park S-M, Abbasizadeh H, Pu YG, Hwang KC, Yang Y, Lee M, et al. Design of Peak Efficiency of 85.3% WPC/PMA Wireless Power Receiver Using Synchronous Active Rectifier and Multi Feedback Low-Dropout Regulator. Energies. 2018; 11(3):479. https://doi.org/10.3390/en11030479

Chicago/Turabian StyleKhan, Zaffar Hayat Nawaz, Young-Jun Park, Seong Jin Oh, Byeong Gi Jang, Seong-Mun Park, Hamed Abbasizadeh, Young Gun Pu, Keum Cheol Hwang, Youngoo Yang, Minjae Lee, and et al. 2018. "Design of Peak Efficiency of 85.3% WPC/PMA Wireless Power Receiver Using Synchronous Active Rectifier and Multi Feedback Low-Dropout Regulator" Energies 11, no. 3: 479. https://doi.org/10.3390/en11030479

APA StyleKhan, Z. H. N., Park, Y.-J., Oh, S. J., Jang, B. G., Park, S.-M., Abbasizadeh, H., Pu, Y. G., Hwang, K. C., Yang, Y., Lee, M., & Lee, K.-Y. (2018). Design of Peak Efficiency of 85.3% WPC/PMA Wireless Power Receiver Using Synchronous Active Rectifier and Multi Feedback Low-Dropout Regulator. Energies, 11(3), 479. https://doi.org/10.3390/en11030479