Control of the Bidirectional Buck-Boost Converter Operating in Boundary Conduction Mode to Provide Hold-Up Time Extension

Abstract

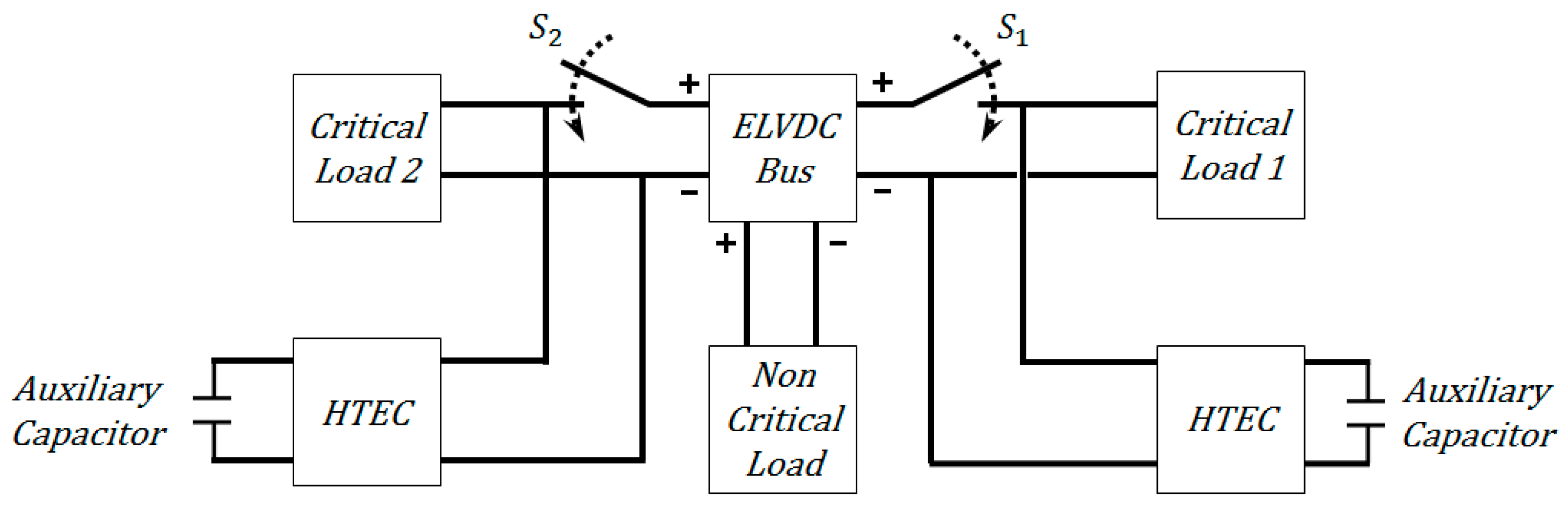

:1. Introduction

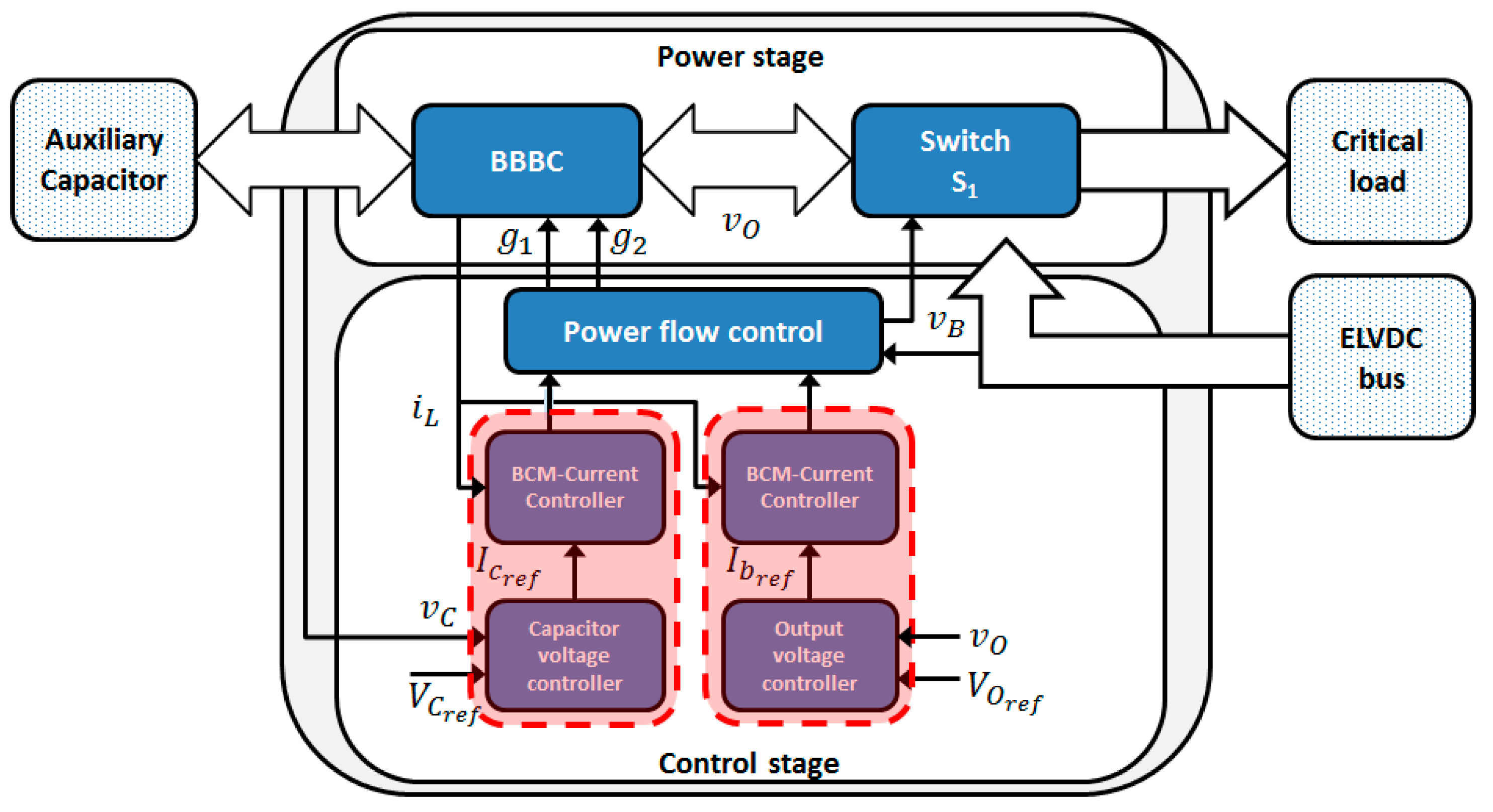

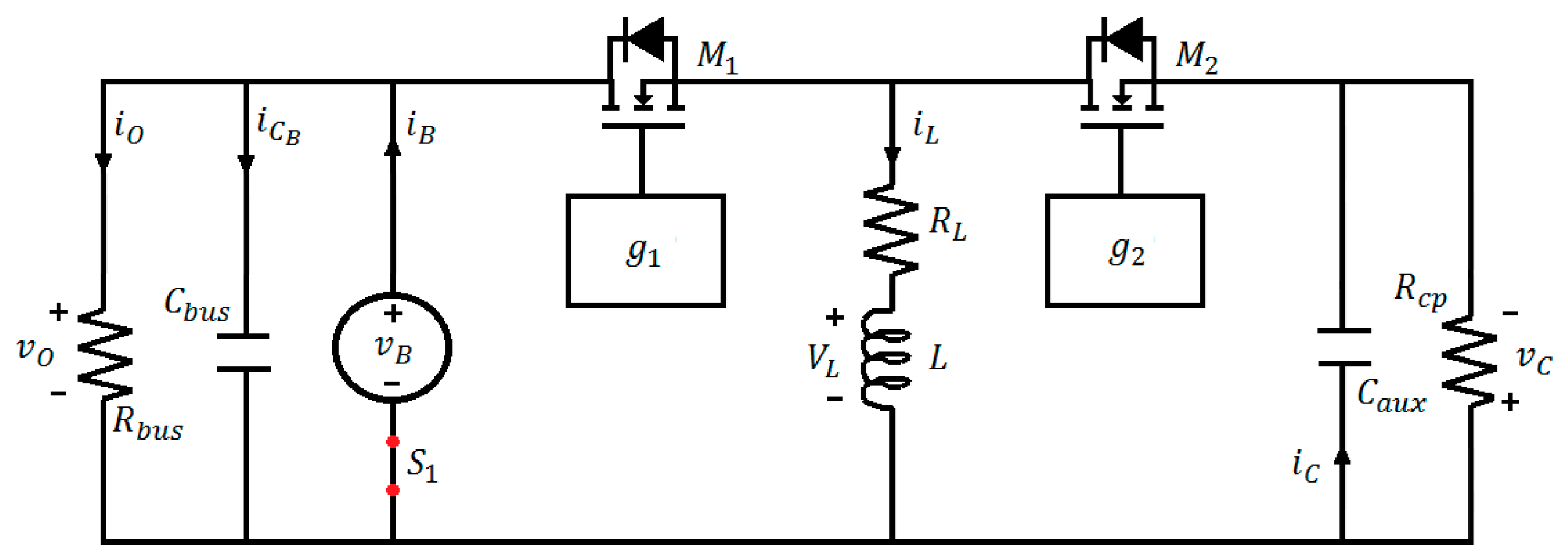

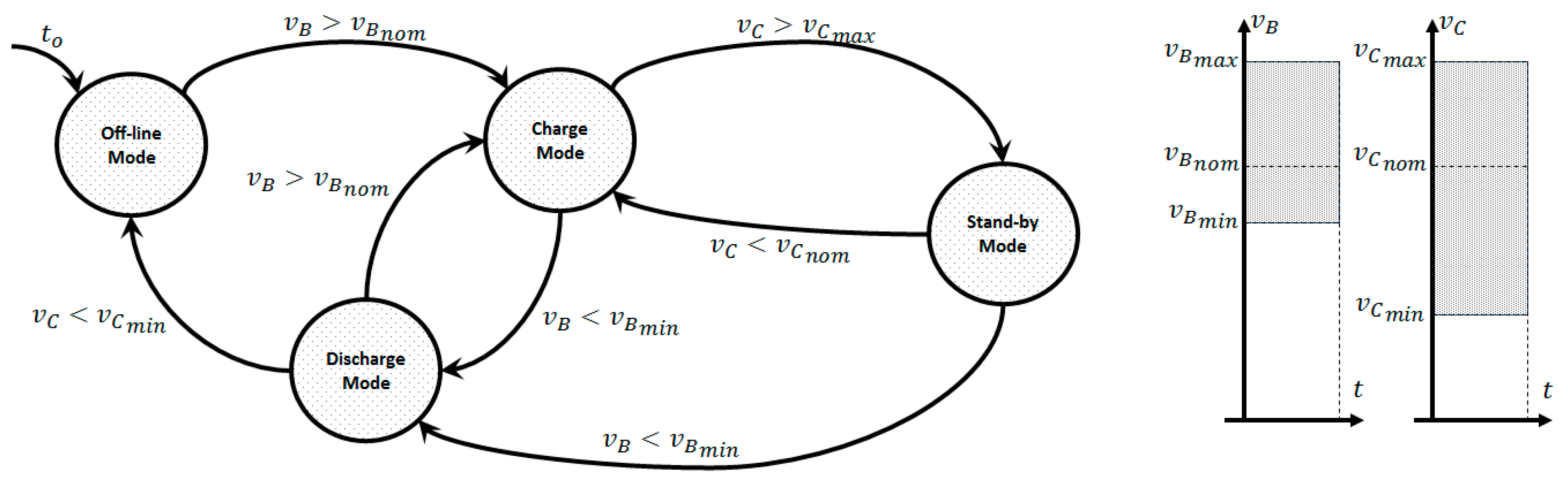

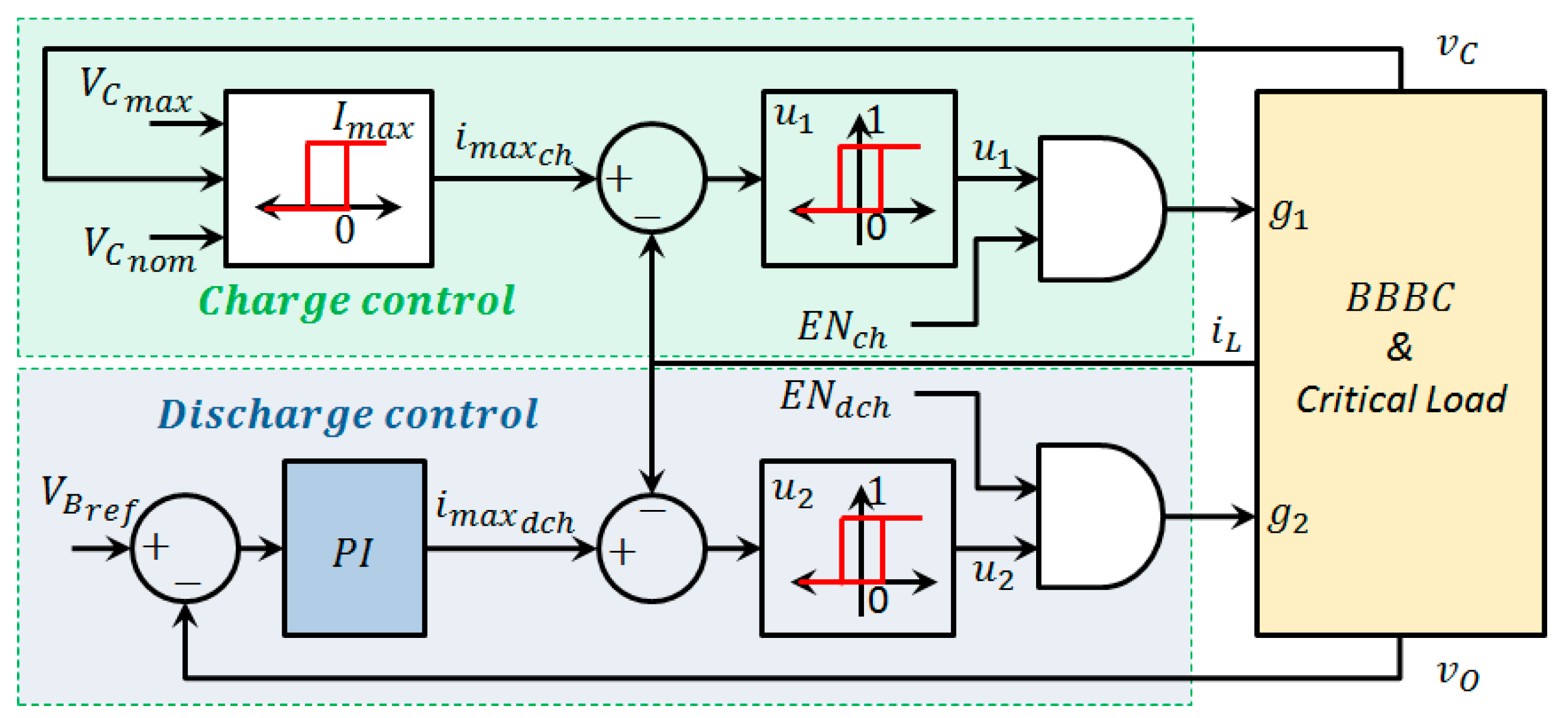

2. General Description of the Control System

3. Modeling and Control of the BBBC Converter

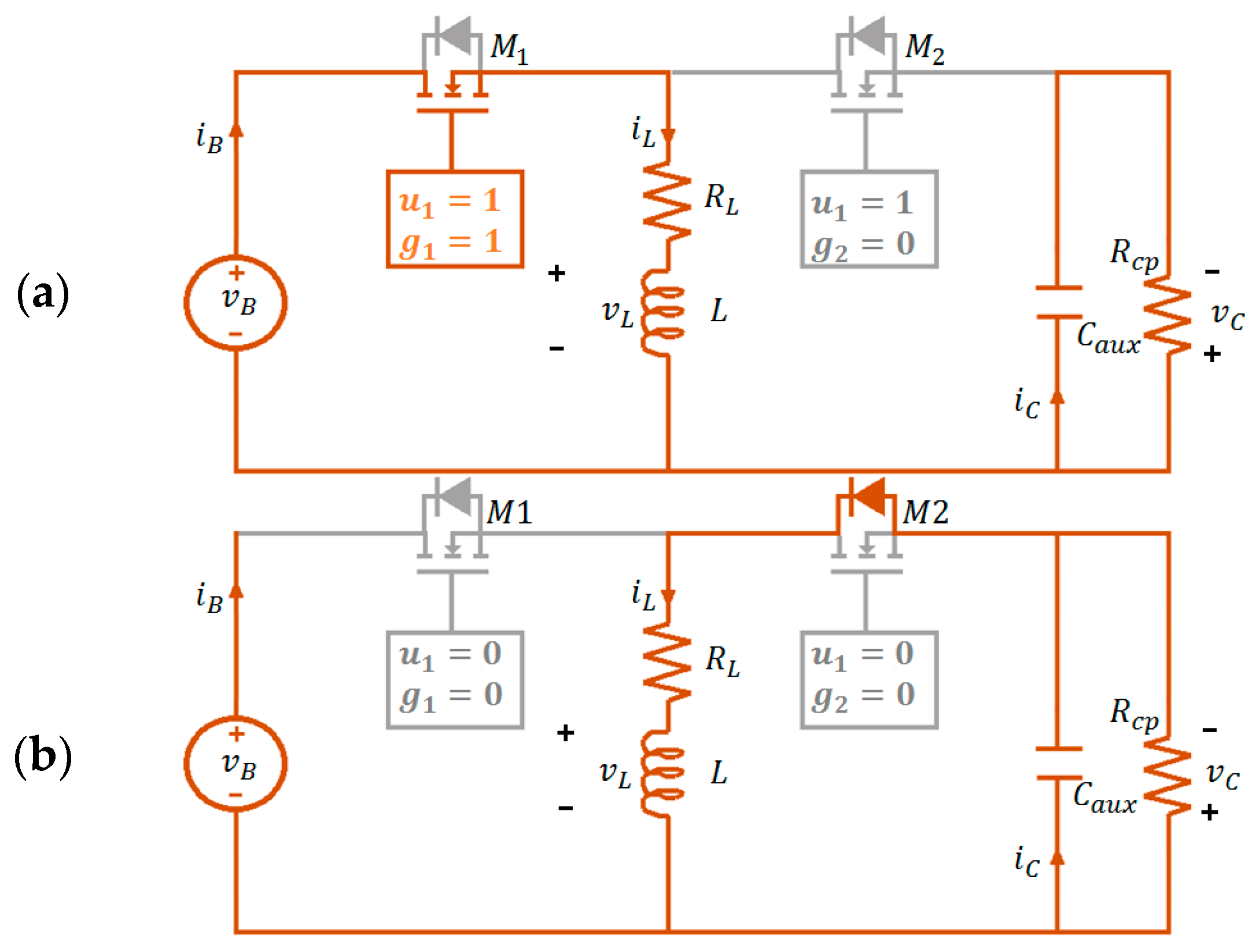

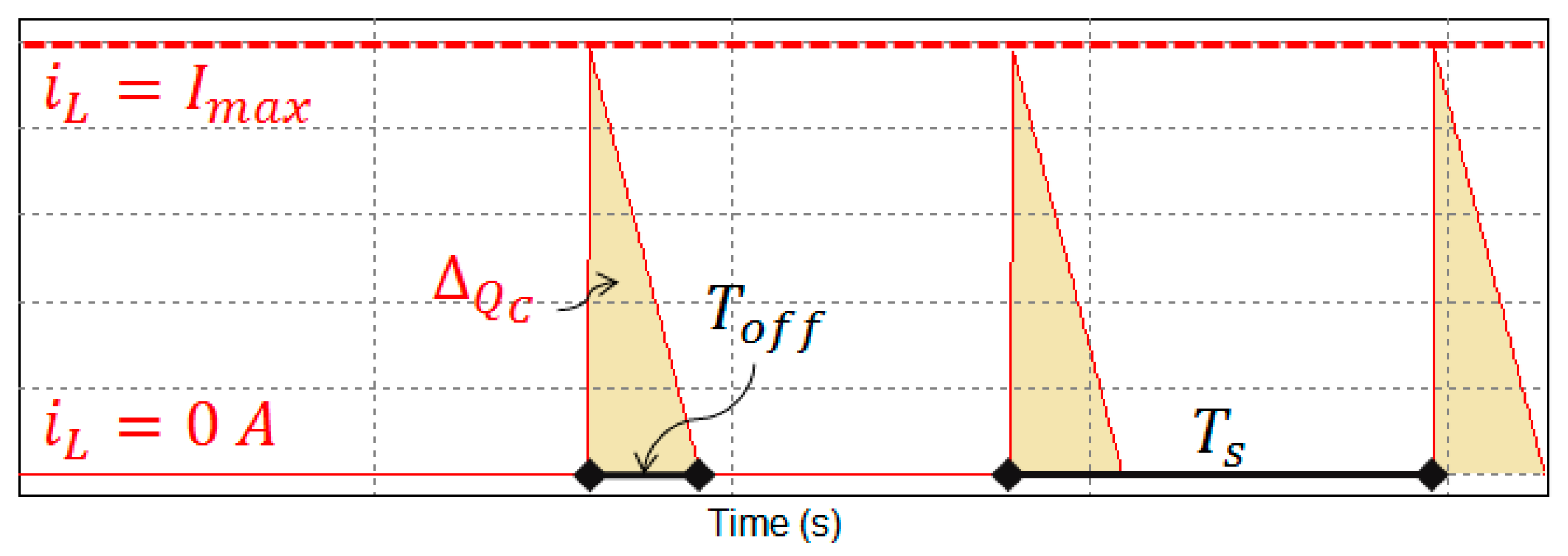

3.1. Capacitor Charging Mode

3.2. Stand-By Mode

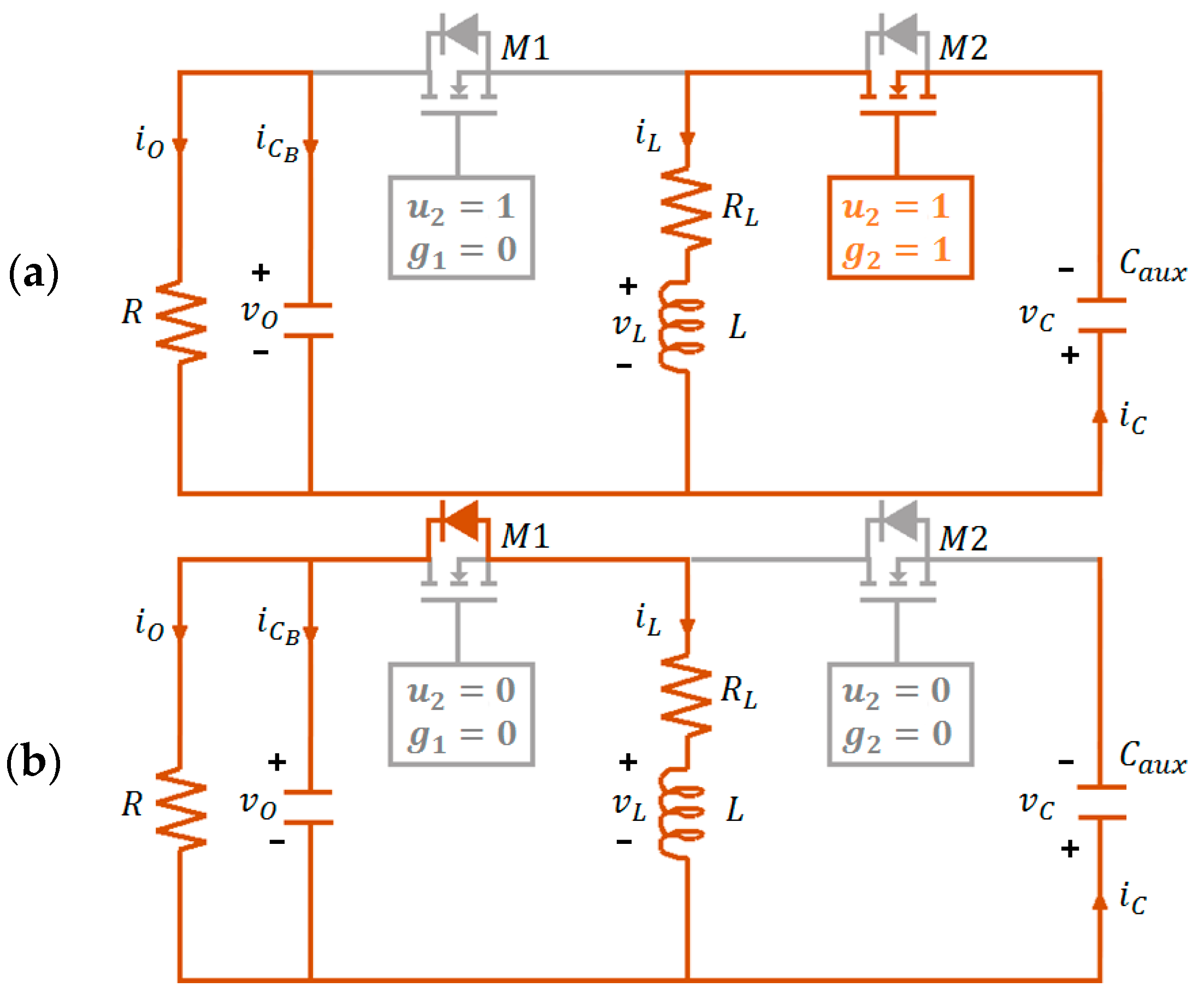

3.3. Recharging Mode of the Capacitor

3.4. Discharging Mode of the Capacitor

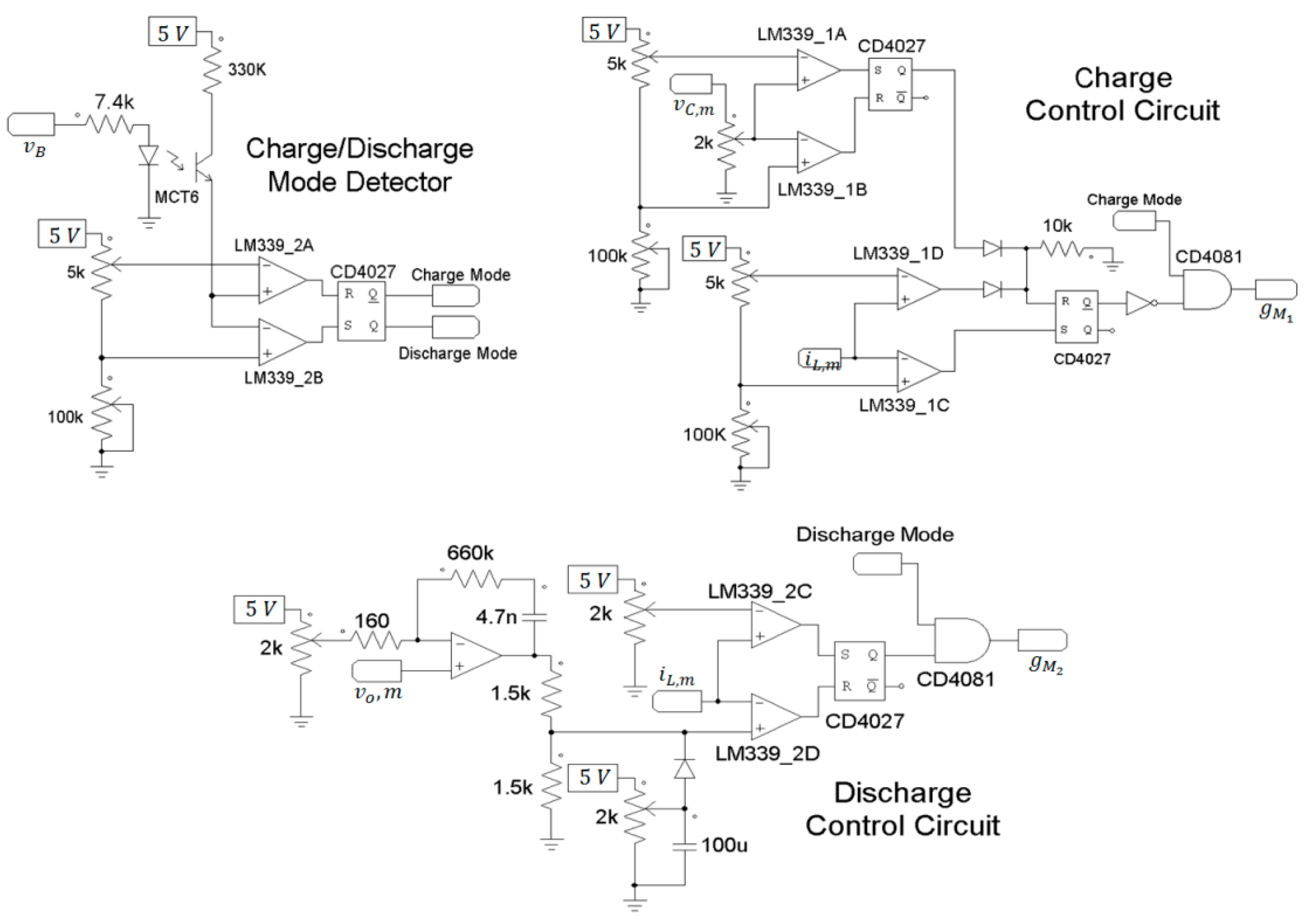

3.5. Complete Control Diagram

3.6. Converter Design Parameters

4. Simulation and Experimental Results

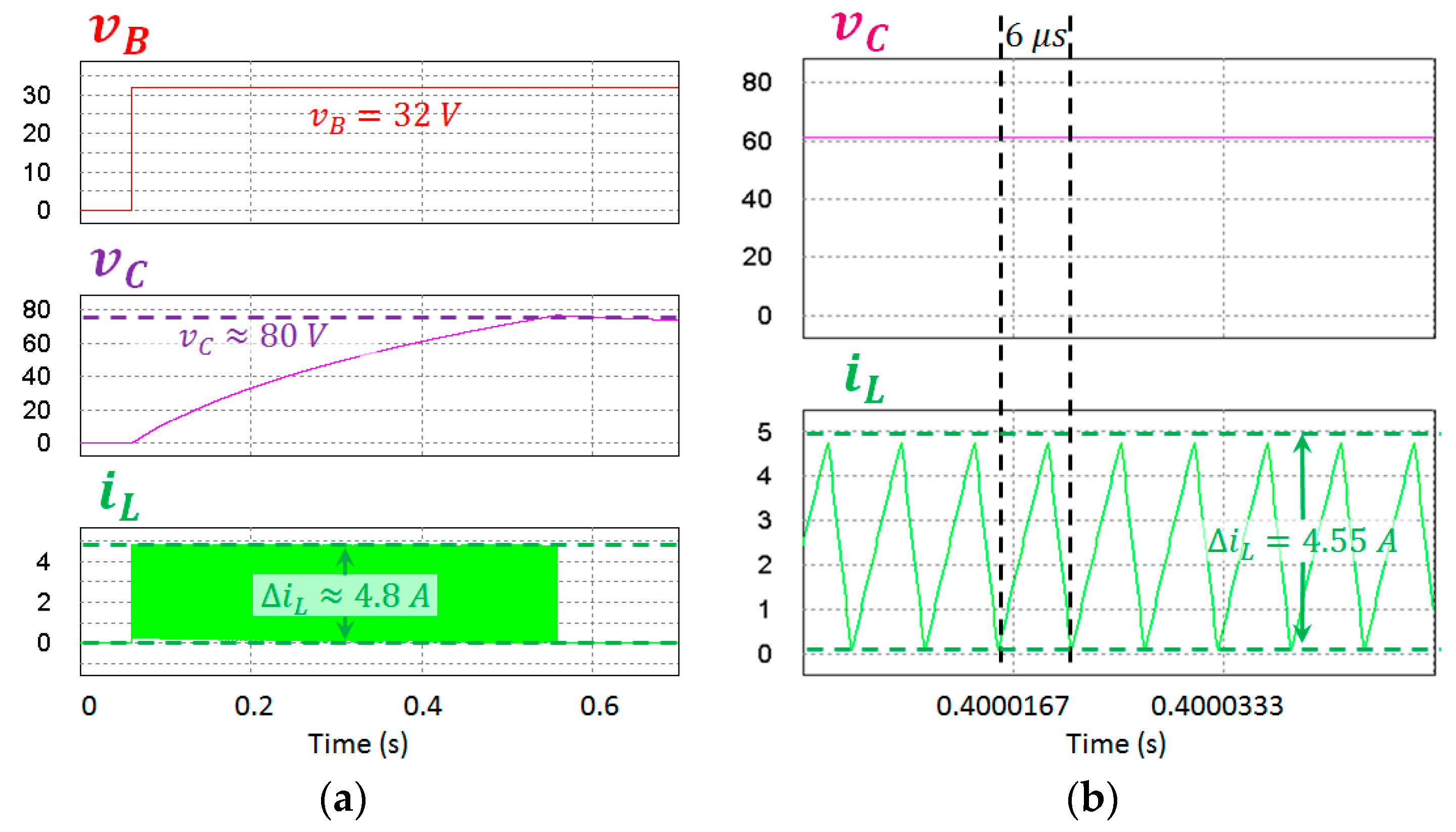

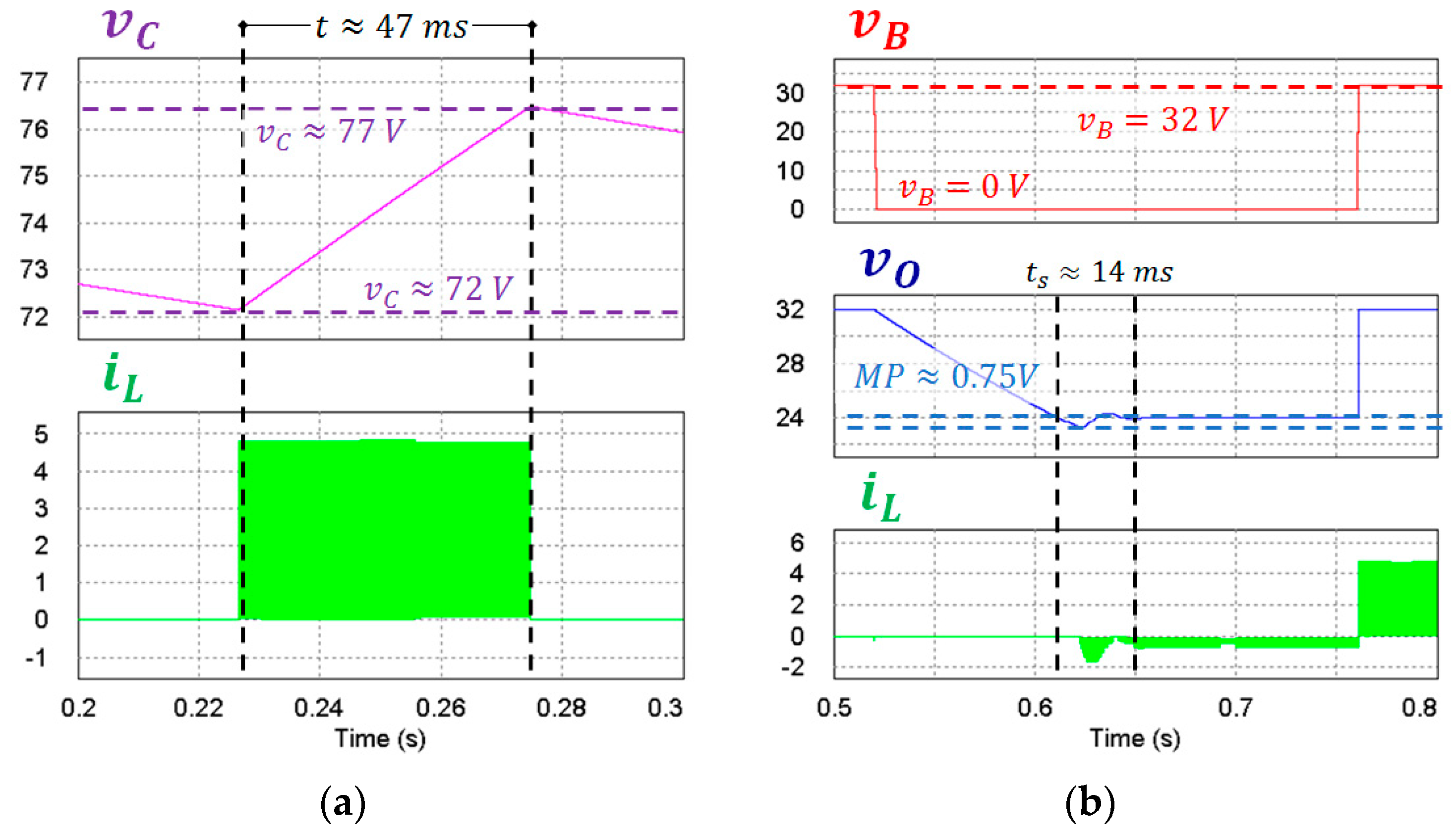

4.1. Simulation Results

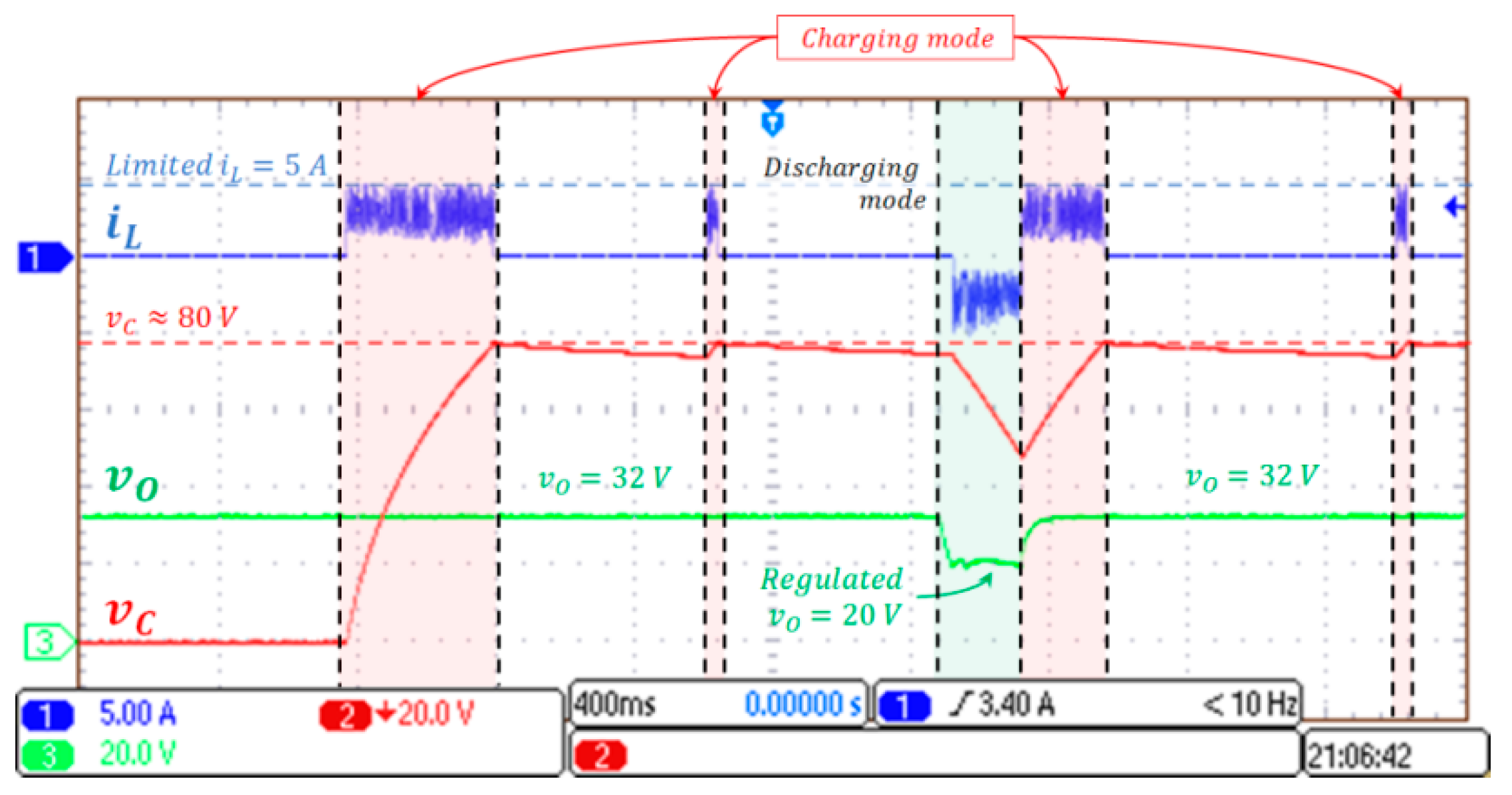

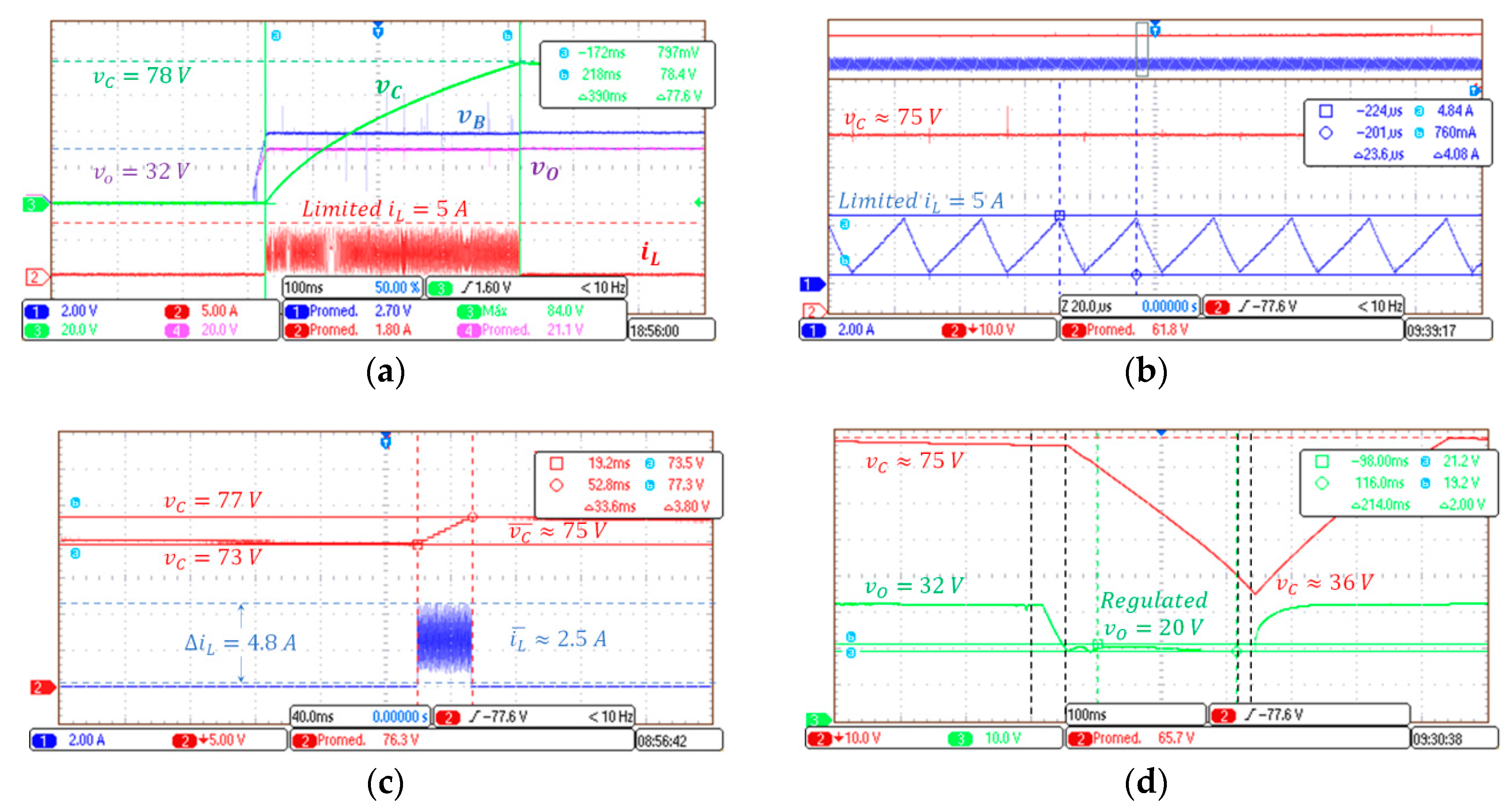

4.2. Experimental Results

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Guidance for Test Procedures for Demonstration of Utilization Equipment Compliance to Aircraft Electrical Power Characteristics 28VDC, Department of Defense Handbook, 2004. Available online: http://everyspec.com/MIL-HDBK/MIL-HDBK-0700-0799/MIL-HDBK-704-8_14620/ (accessed on 8 February 2018).

- Radio-Technical Commission for Aeronautics (RTCA). DO-160, Environmental Conditions and Test Procedures for Airborne Equipment; Section 16, Power Input ED-14G; RTCA: Washington, DC, USA, 2011. [Google Scholar]

- IEEE 946-2004. Recommended Practice for the Design of DC Auxiliary Power Systems for Generating Systems; IEEE Std 946-2004: New York, NY, USA, 2004. [Google Scholar]

- IET Standards. Code of Practice for Low and Extra Low Voltage Direct Current Power Distribution in Buildings; IET Standards: Stevenage, UK, 2015; pp. 1–60. [Google Scholar]

- ST Microelectronics. Power Supply Hold-up Time; TN0024 Technical Note; ST Microelectronics: Santa Clara, CA, USA, 2007; pp. 1–11. [Google Scholar]

- Jin, X.; Lin, H.; Yao, W.; Deng, Y.; Lyu, Z.; Qian, B. Hold-up time extension method for forward converter. In Proceedings of the IEEE 2nd Annual Southern Power Electronics Conference (SPEC), Auckland, New Zealand, 5–8 December 2016; pp. 1–4. [Google Scholar]

- Jang, Y.; Jovanovic, M.; Dillman, D.L. Hold-up time extension circuit with integrated magnetics. IEEE Trans. Power Electron. 2006, 21, 394–400. [Google Scholar] [CrossRef]

- Jang, Y.; Jovanovic, M. Hold-up-Time Extension Circuits. U.S. Patent No. US20020071300A1, 13 June 2002. [Google Scholar]

- Liu, G.; He, L. Hold-up Time Extension Circuit for a Power Converter. U.S. Patent No US20130027981A1, 31 January 2013. [Google Scholar]

- Wang, H.; Liu, W.; Chung, H. Hold-up time analysis of a dc-link module with a series voltage compensator. In Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE), Raleigh, NC, USA, 15–20 September 2012; pp. 1095–1100. [Google Scholar]

- Picard, J. High-Voltage Energy Storage: The Key to Efficient Holdup; Texas Instruments: Dallas, TX, USA, 2008. [Google Scholar]

- Interpoint. HUM-40, HUM-70, Interpoint’s Hummer Hold-Up Module Series. 2009, pp. 1–13. Available online: http://www.interpoint.com/product_documents/HUM70_Hold_Up_Module_DC_DC.pdf (accessed on 8 February 2018).

- Gaïa Converter. Hi-Rel Hold-up module HUGD-50: 50 Power. 2014, pp. 1–13. Available online: http://gaia-converter.com/50-watt-hugd-50 (accessed on 8 February 2018).

- Lai, C.-M.; Li, Y.-H.; Cheng, Y.-H.; Teh, J. A High-Gain Reflex-Based Bidirectional DC Charger with Efficient Energy Recycling for Low-Voltage Battery Charging-Discharging Power Control. Energies 2018, 11, 623. [Google Scholar] [CrossRef]

- Shiau, J.-K.; Ma, C.-W. Li-Ion Battery Charging with a Buck-Boost Power Converter for a Solar Powered Battery Management System. Energies 2013, 6, 1669–1699. [Google Scholar] [CrossRef] [Green Version]

- Serna-Garcés, S.I.; Gonzalez Montoya, D.; Ramos-Paja, C.A. Sliding-Mode Control of a Charger/Discharger DC/DC Converter for DC-Bus Regulation in Renewable Power Systems. Energies 2016, 9, 245. [Google Scholar] [CrossRef]

- Ramos-Paja, C.A.; Bastidas-Rodríguez, J.D.; González, D.; Acevedo, S.; Peláez-Restrepo, J. Design and Control of a Buck–Boost Charger-Discharger for DC-Bus Regulation in Microgrids. Energies 2017, 10, 1847. [Google Scholar] [CrossRef]

- Lopez-Santos, O.; Urrego-Aponte, J.O.; Almansa-López, J.D. Modeling and control of a new circuit to obtain hold-up time extension for electronic equipment in aircraft applications. In Proceedings of the 2016 International Conference on Electrical Systems for Aircraft, Railway, Ship Propulsion and Road Vehicles & International Transportation Electrification Conference (ESARS-ITEC), Toulouse, France, 2–4 November 2016; pp. 1–7. [Google Scholar]

- Flores-Bahamonde, F.; Valderrama-Blavi, H.; Bosque-Moncusi, J.M.; García, G.; Martínez-Salamero, L. Using the sliding-mode control approach for analysis and design of the boost inverter. IET Power Electron. 2016, 9, 1625–1634. [Google Scholar] [CrossRef]

- Chen, J.; Erickson, R.; Maksimovic, D. Averaged switch modeling of boundary conduction mode DC-to-DC converters. In Proceedings of the 27th Annual Conference of the IEEE Industrial Electronics Society (IECON), Denver, CO, USA, 29 November–2 December 2001; Volume 2, pp. 844–849. [Google Scholar]

- Lopez-Santos, O.; Zambrano-Prada, D.A.; Aldana-Rodriguez, Y.A.; Esquivel-Cabeza, H.A.; Garcia, G.; Martinez-Salamero, L. Control of a Bidirectional Cûk Converter Providing Charge/Discharge of a Battery Array Integrated in DC Buses of Microgrids. Commun. Comput. Inf. Sci. 2017, 742, 495–507. [Google Scholar]

- Lopez-Santos, O.; Martinez-Salamero, L.; Garcia, G.; Valderrama-Blavi, H.; Sierra-Polanco, T. Robust Sliding-Mode Control Design for a Voltage Regulated Quadratic Boost Converter. IEEE Trans. Power Electron. 2015, 30, 2313–2327. [Google Scholar] [CrossRef]

| General Operation Specifications | Converter Parameters | ||||||

| Parameter | Symbol | Value | Units | Parameter | Symbol | Value | Units |

| Nominal bus voltage | 28 | V | Bus capacitor | 1.880 | µF | ||

| Maximum bus voltage | 36 | V | Auxiliary capacitor | 600 | µF | ||

| Minimum bus voltage | 22 | V | Self-discharge capacitor resistance | 1 | kΩ | ||

| Regulated bus voltage | 20 | V | Inductor | 25 | µH | ||

| Auxiliary capacitor max. voltage | 78 | V | Bus load resistance | 12 | Ω | ||

| Auxiliary capacitor nom. voltage | 73 | V | Discharge PI Regulator Parameters | ||||

| Parameter | Symbol | Value | |||||

| Auxiliary capacitor min. voltage | 12 | V | Proportional gain (Discharge) | 15 | |||

| Maximum charge current | 10 | A | Integral gain (Discharge) | 5.000 | |||

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lopez-Santos, O.; Urrego-Aponte, J.O.; Tilaguy-Lezama, S.; Almansa-López, J.D. Control of the Bidirectional Buck-Boost Converter Operating in Boundary Conduction Mode to Provide Hold-Up Time Extension. Energies 2018, 11, 2560. https://doi.org/10.3390/en11102560

Lopez-Santos O, Urrego-Aponte JO, Tilaguy-Lezama S, Almansa-López JD. Control of the Bidirectional Buck-Boost Converter Operating in Boundary Conduction Mode to Provide Hold-Up Time Extension. Energies. 2018; 11(10):2560. https://doi.org/10.3390/en11102560

Chicago/Turabian StyleLopez-Santos, Oswaldo, José Omar Urrego-Aponte, Sebastián Tilaguy-Lezama, and José David Almansa-López. 2018. "Control of the Bidirectional Buck-Boost Converter Operating in Boundary Conduction Mode to Provide Hold-Up Time Extension" Energies 11, no. 10: 2560. https://doi.org/10.3390/en11102560