Design and Control of a 13.2 kV/10 kVA Single-Phase Solid-State-Transformer with 1.7 kV SiC Devices

Abstract

:1. Introduction

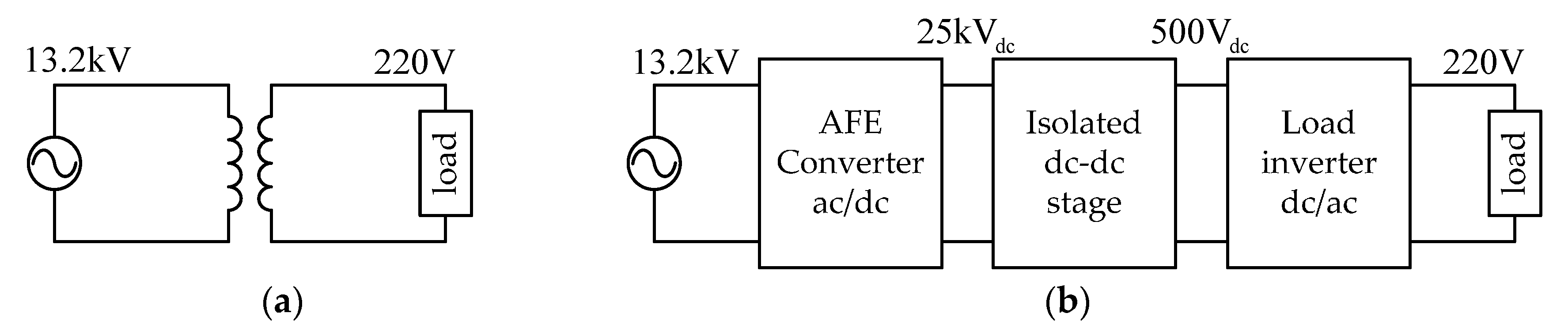

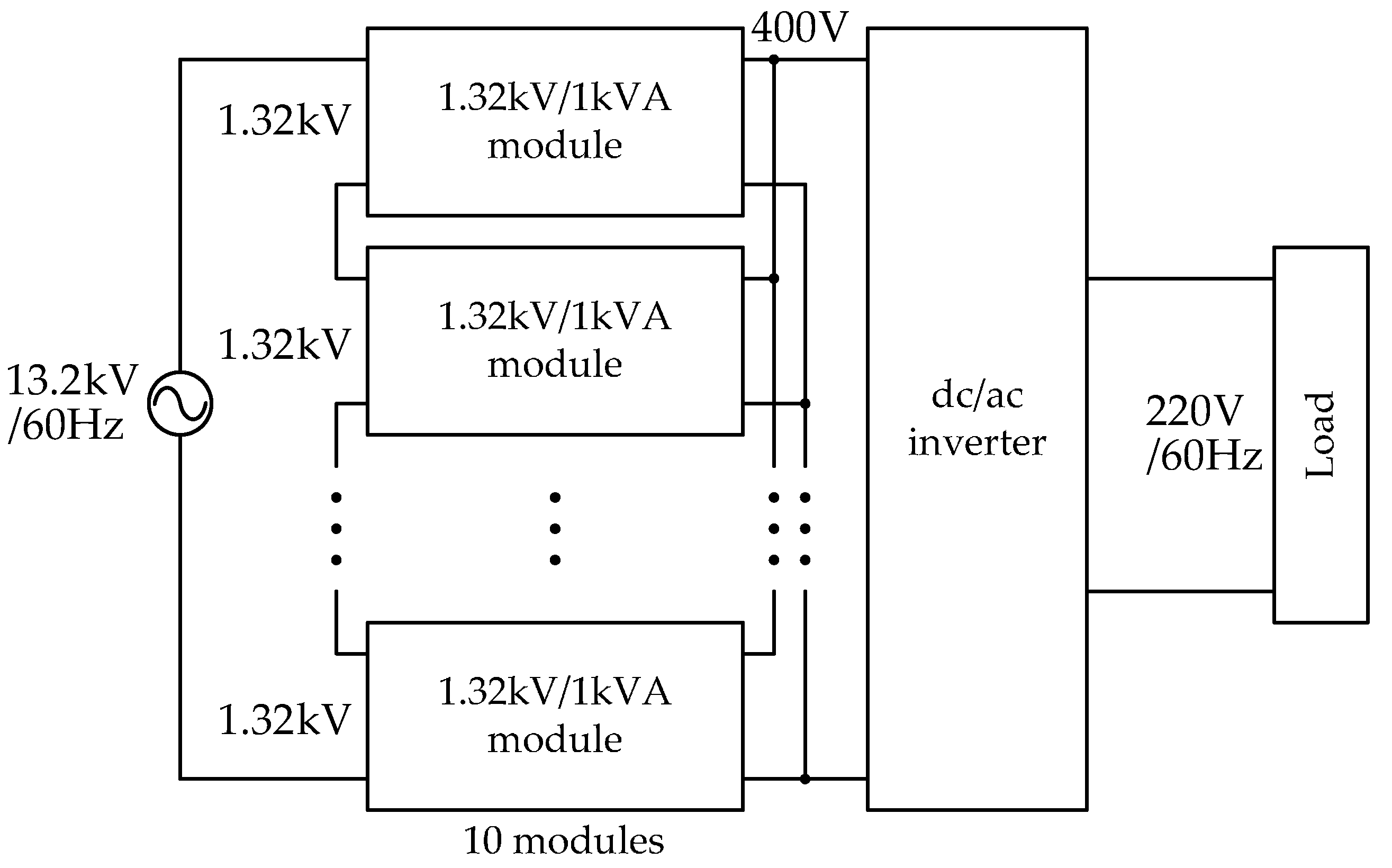

2. Solid-State-Transformer for Electric Power Distribution System

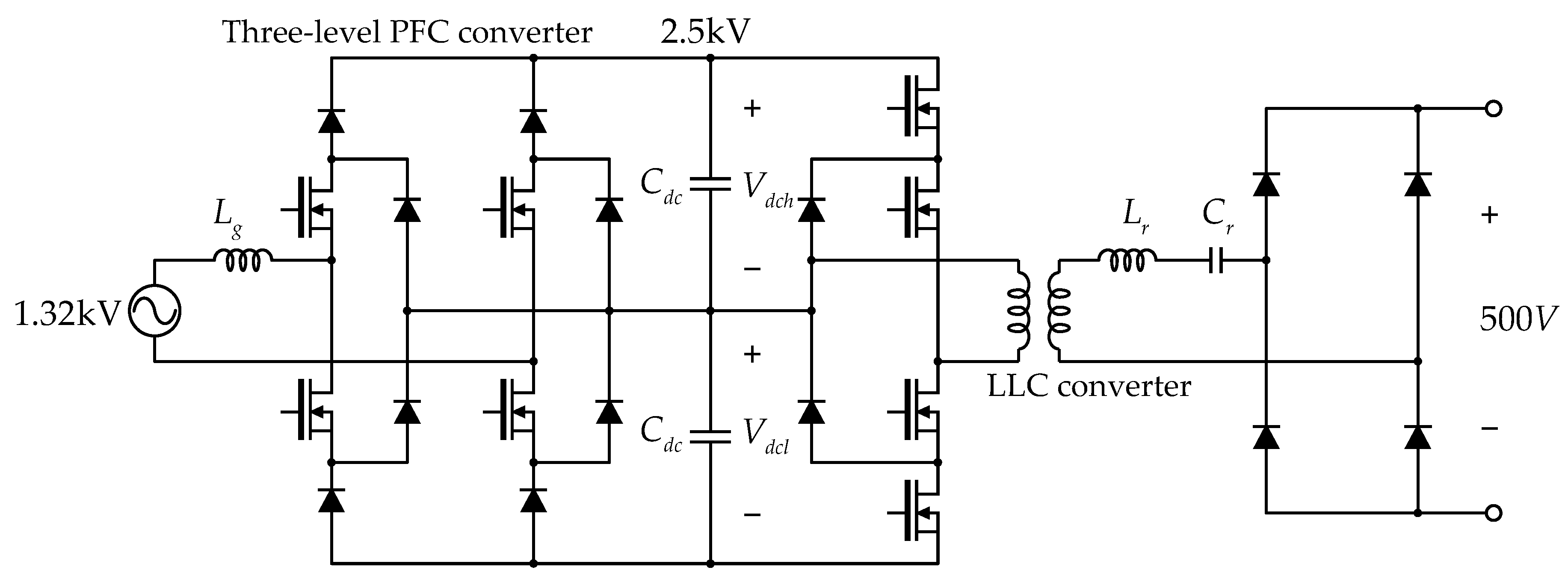

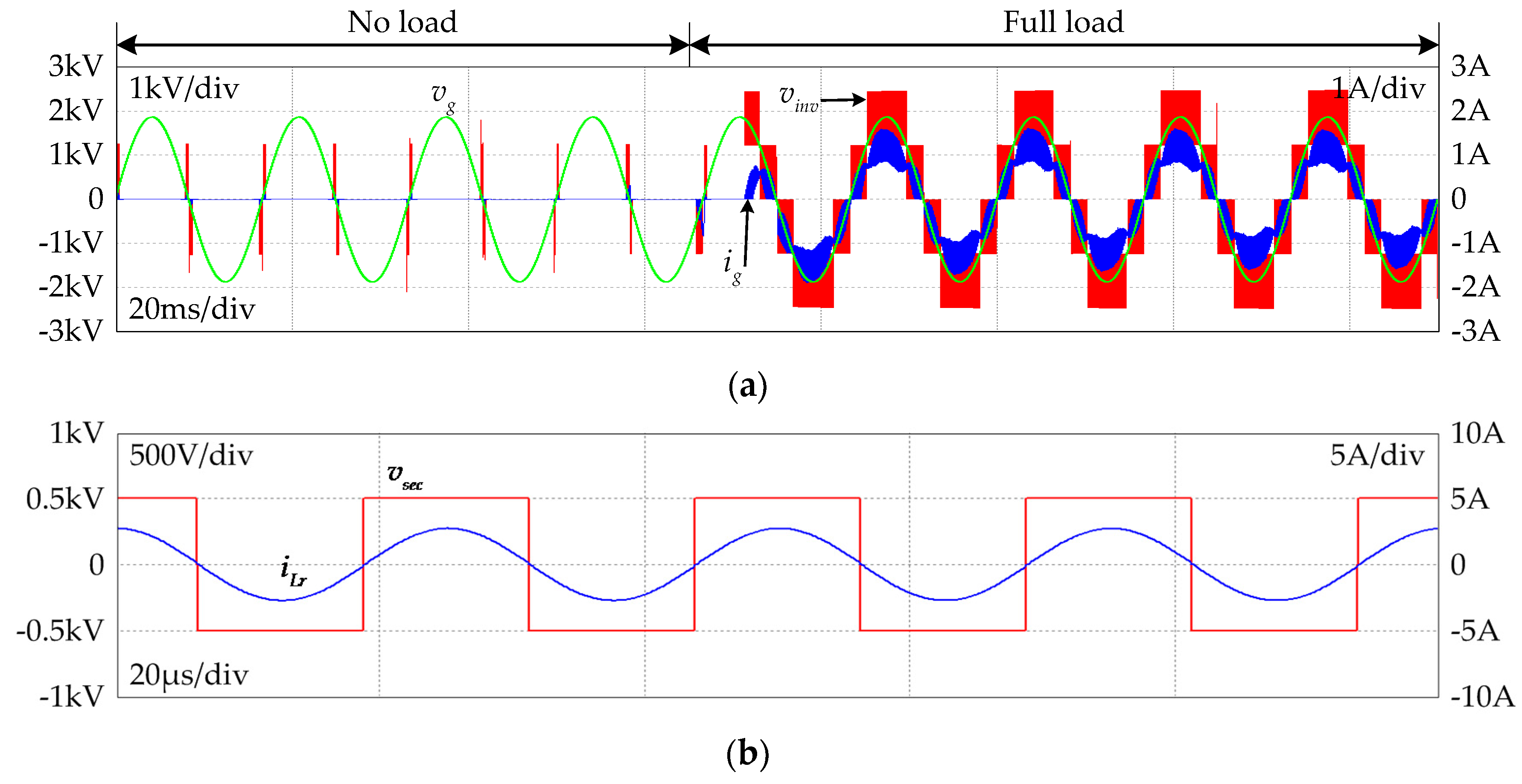

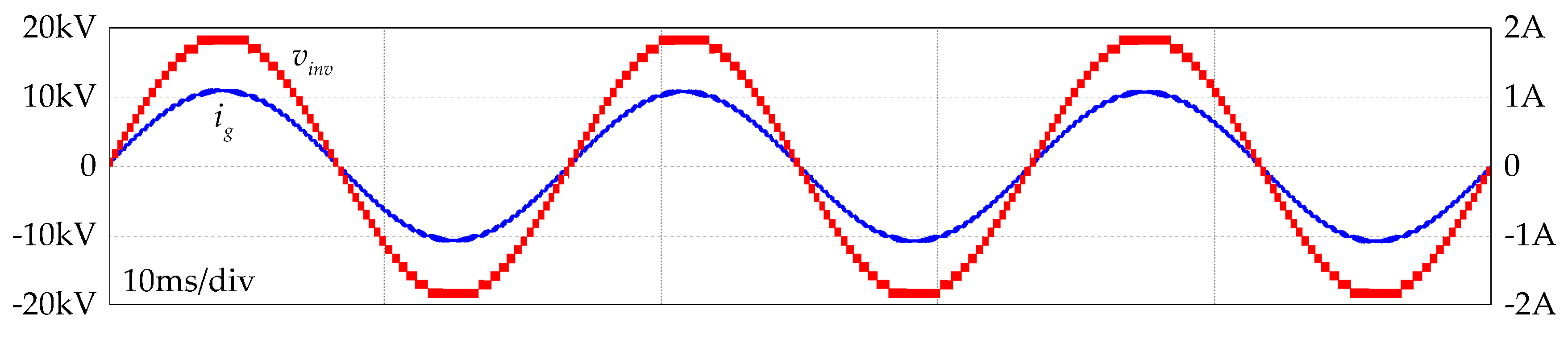

2.1. Power Stage Configuration

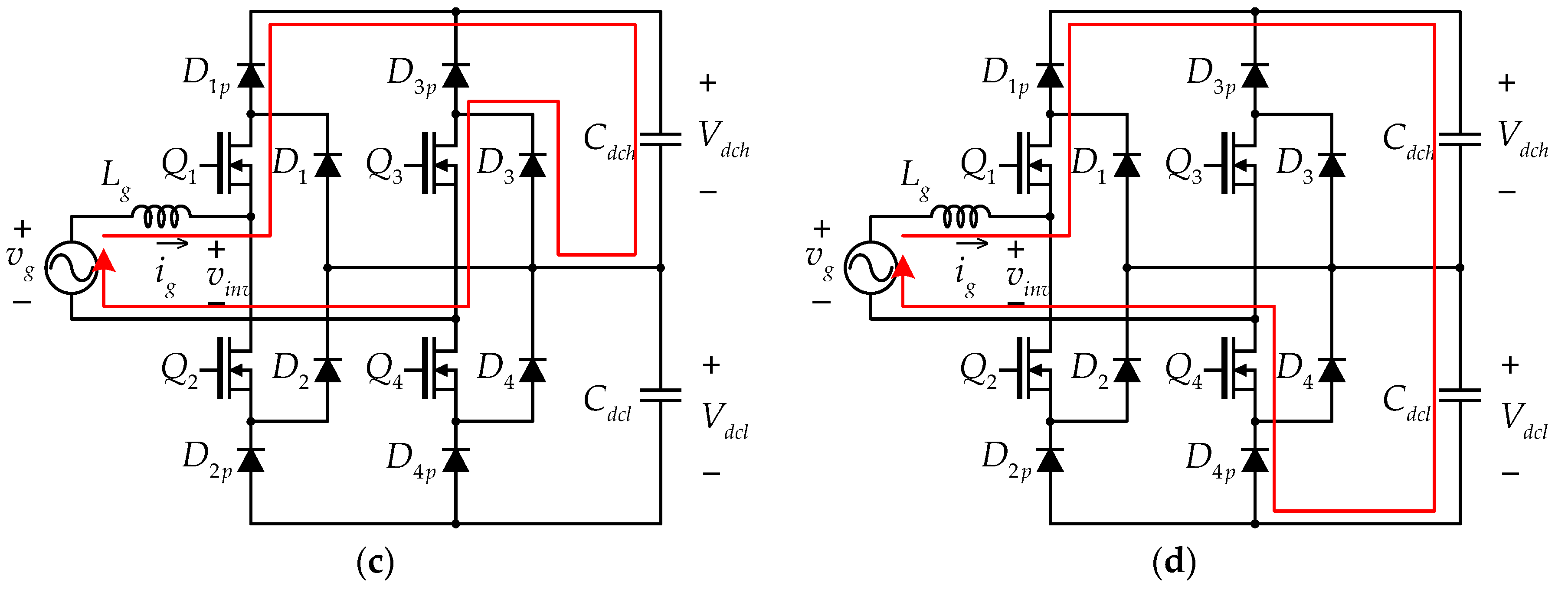

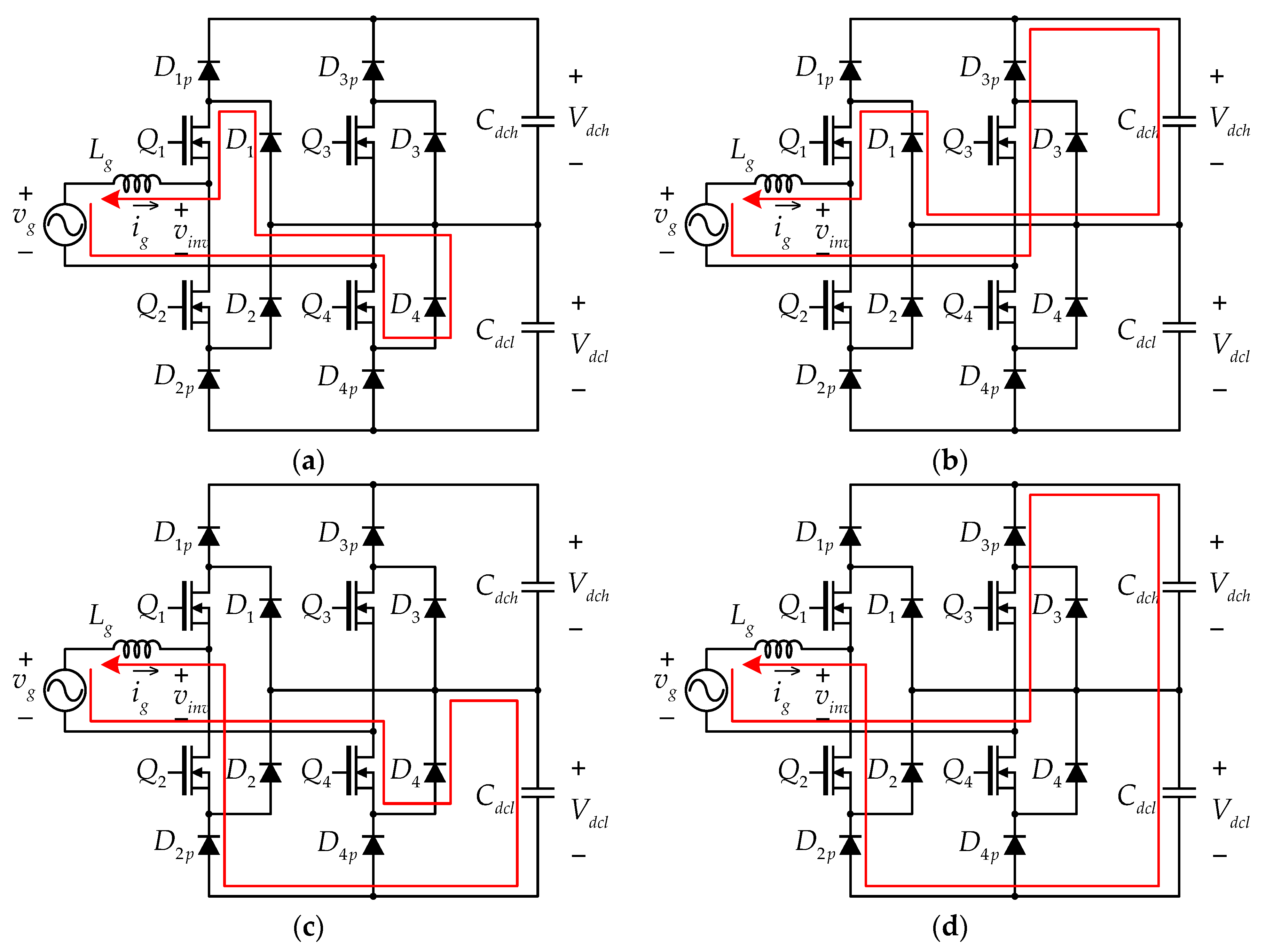

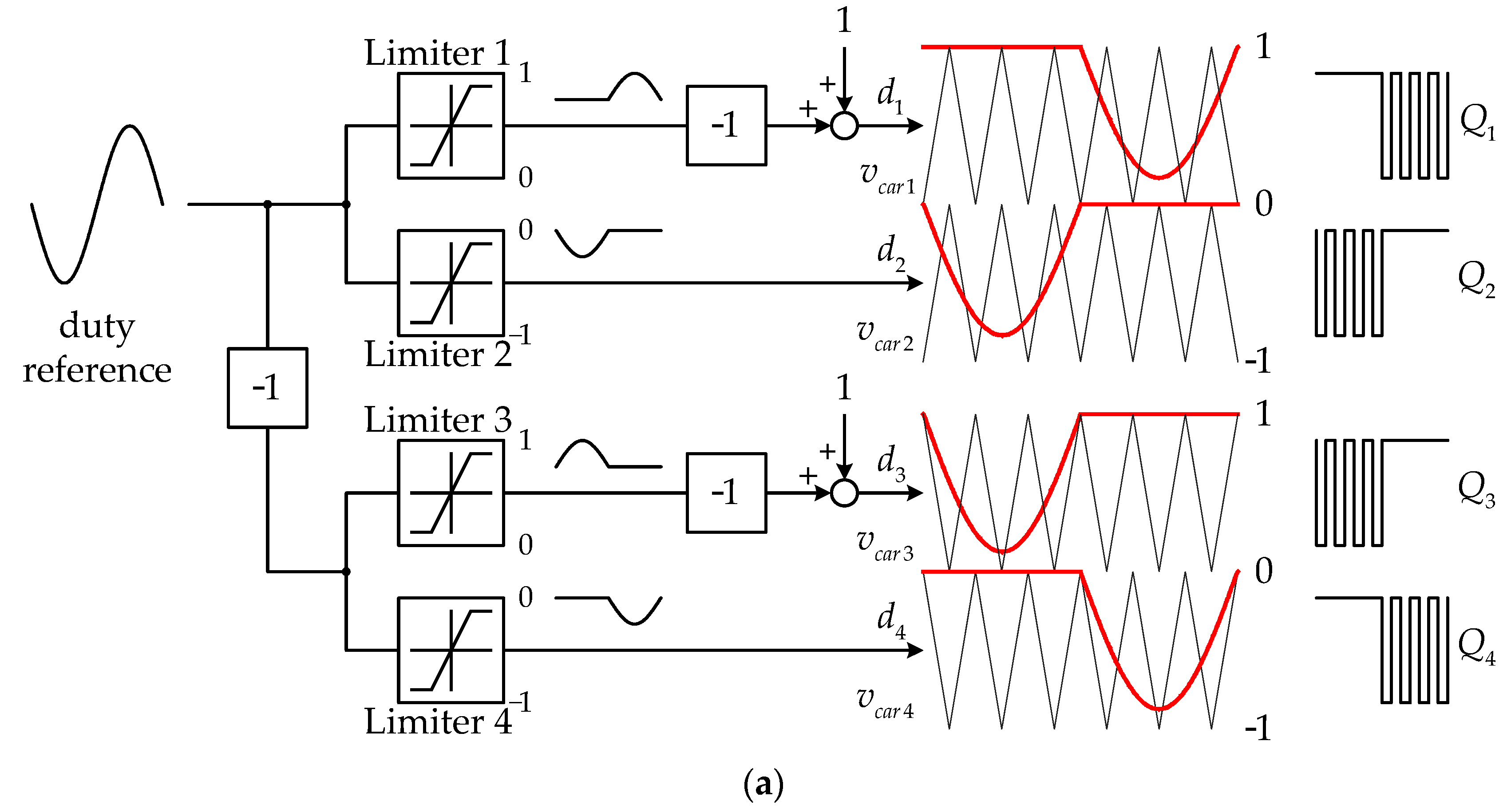

2.2. Three-Level PFC Converter Operation

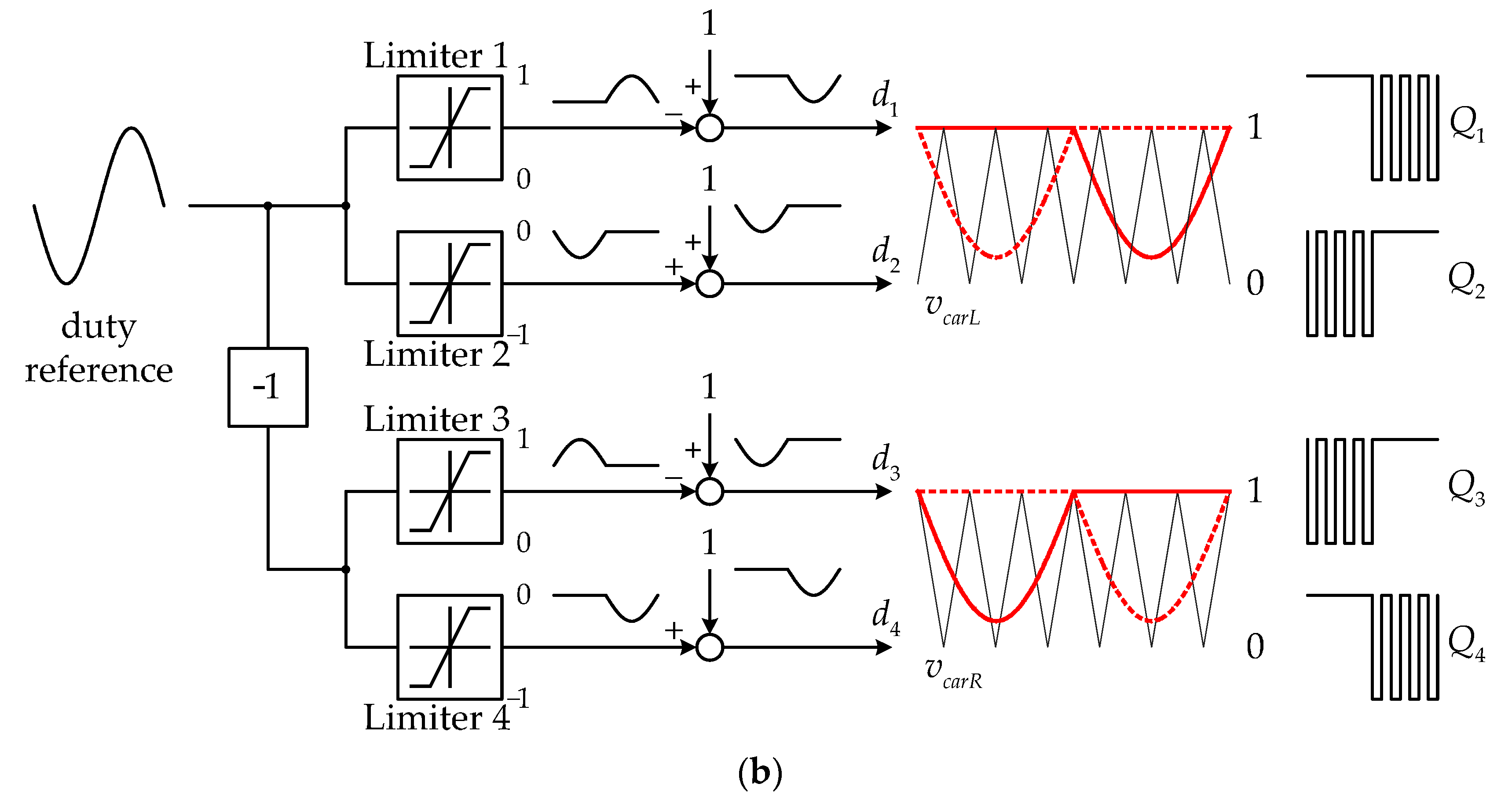

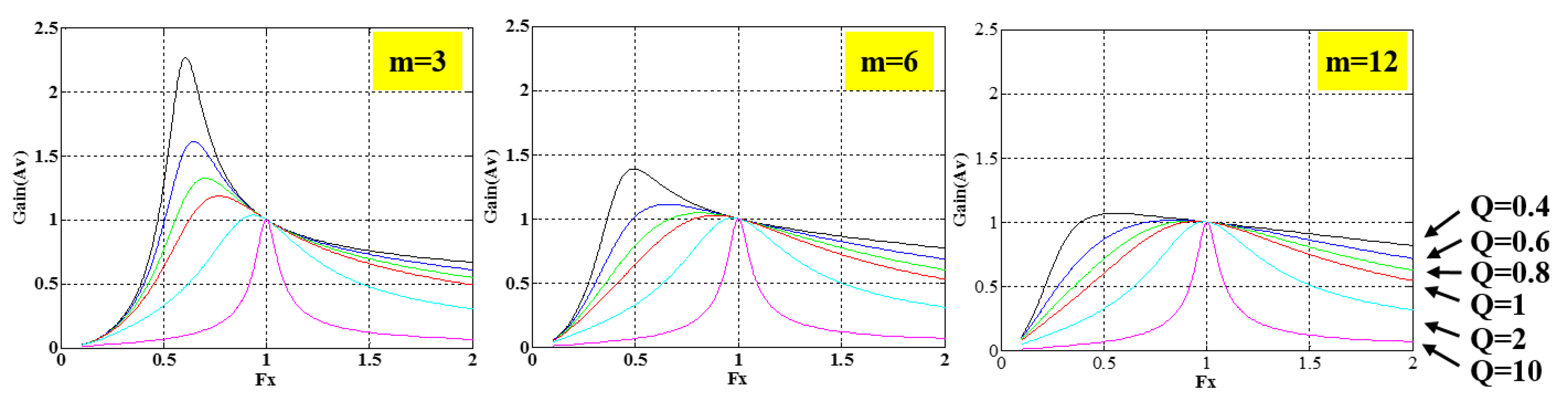

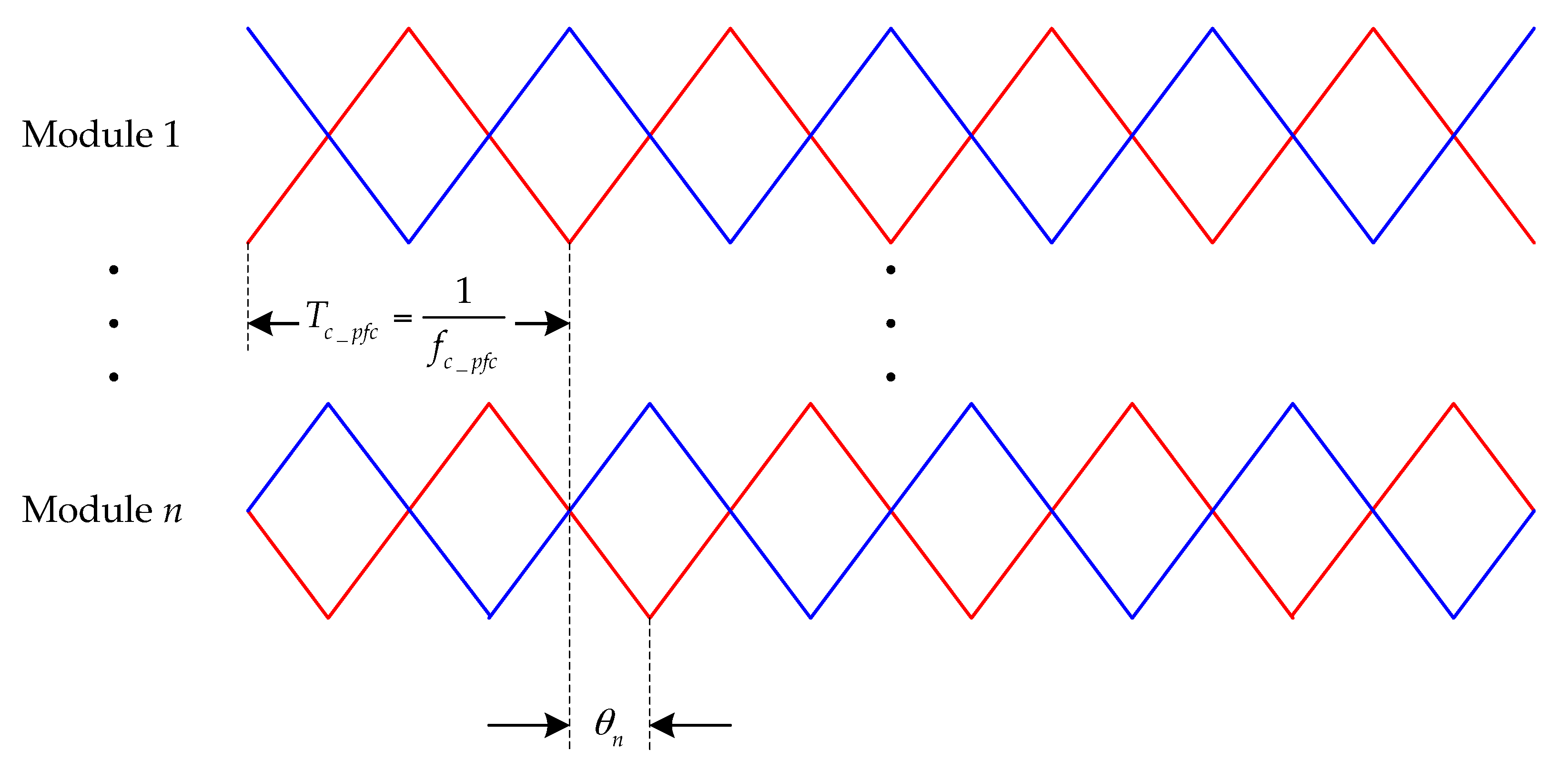

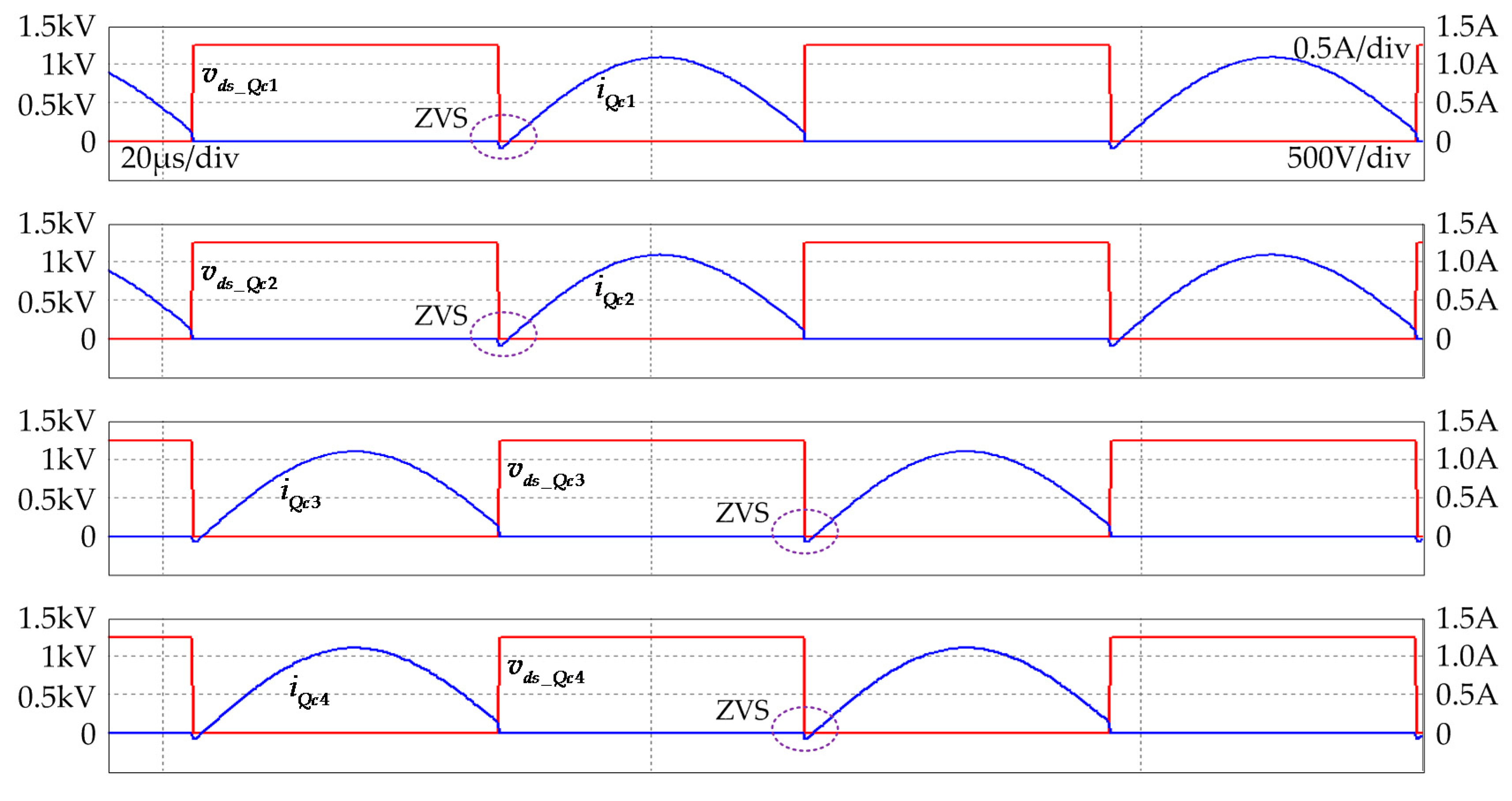

2.3. LLC Converter Operation

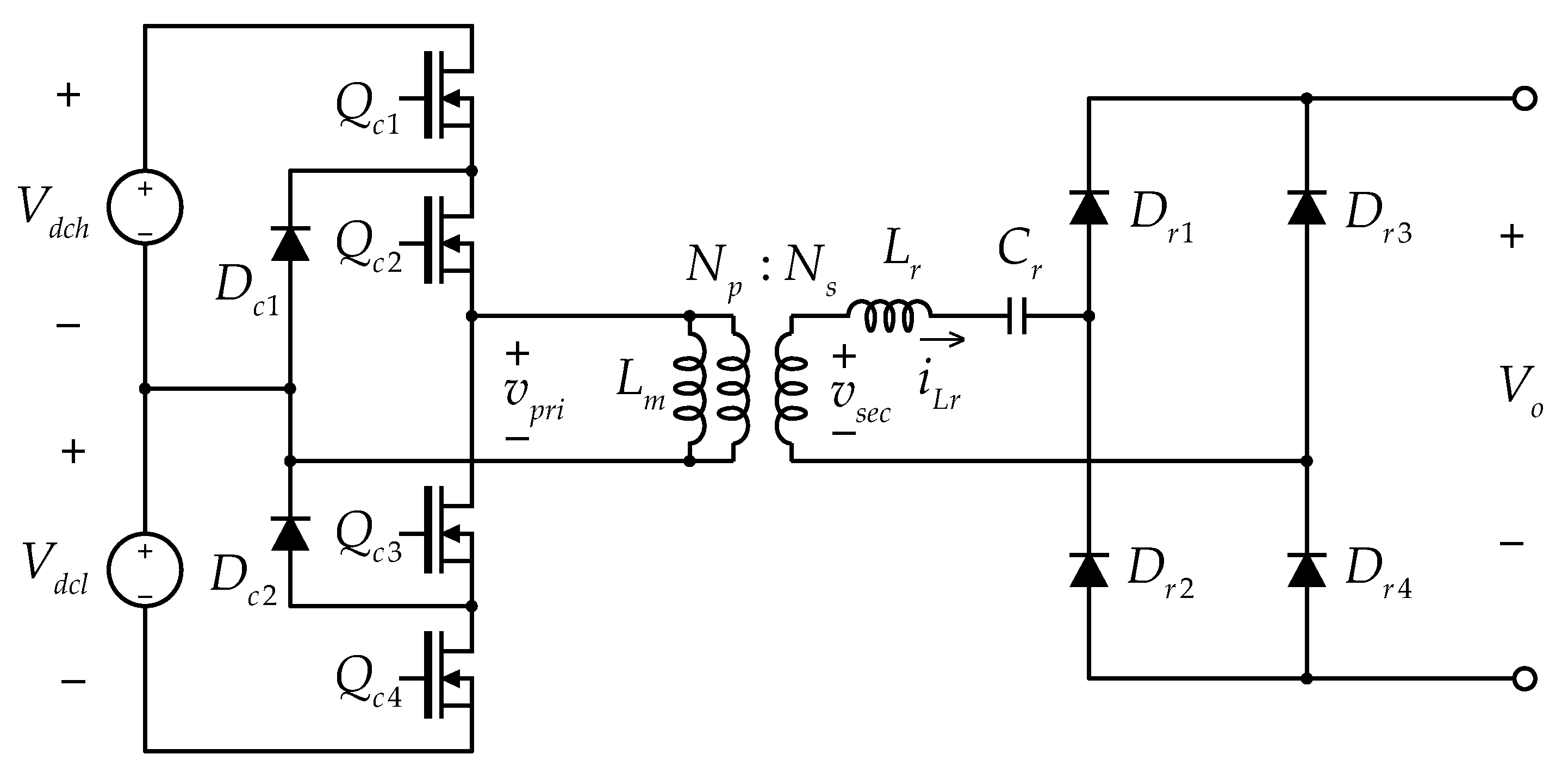

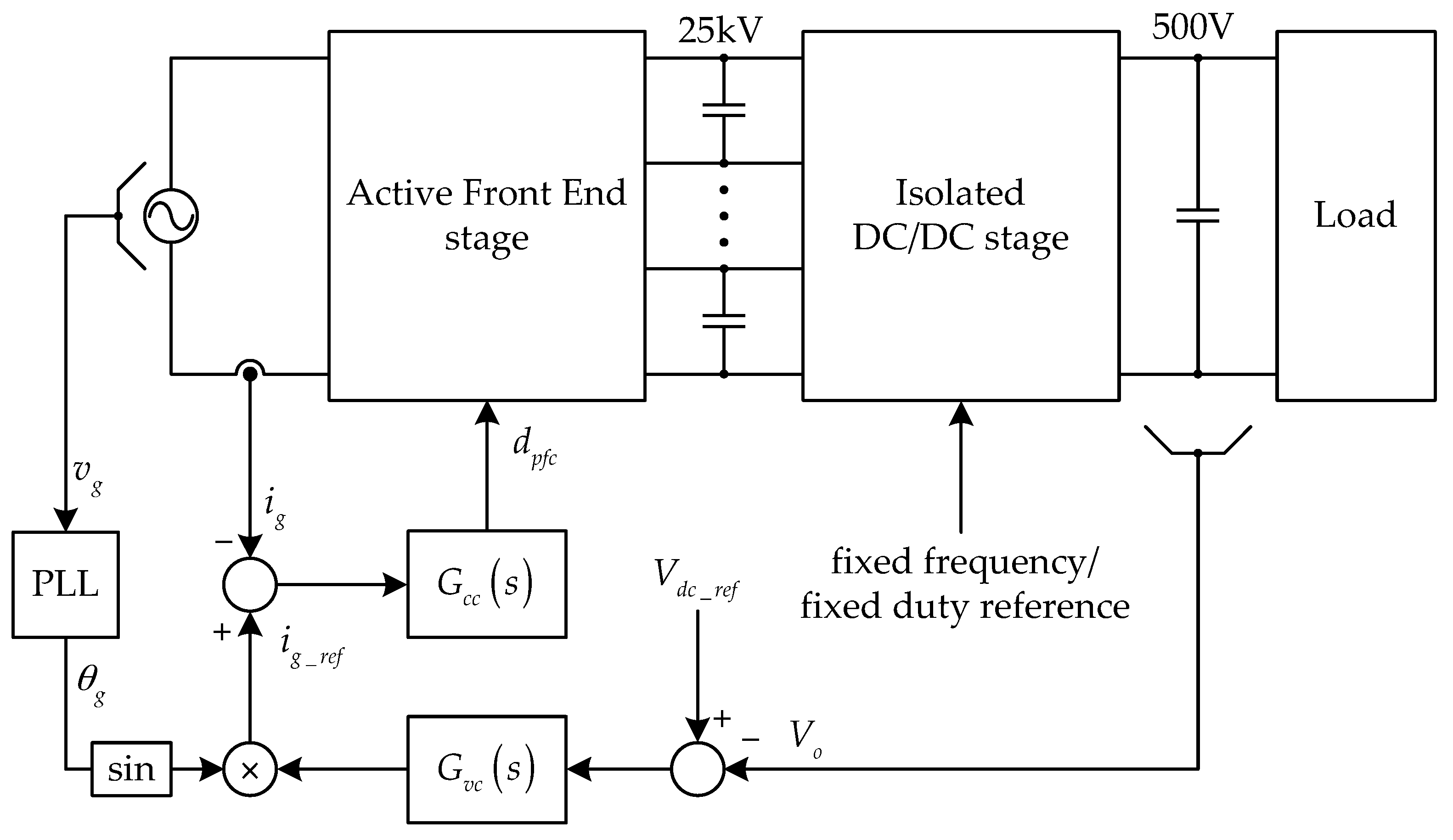

2.4. Control Strategy of the Power Stages

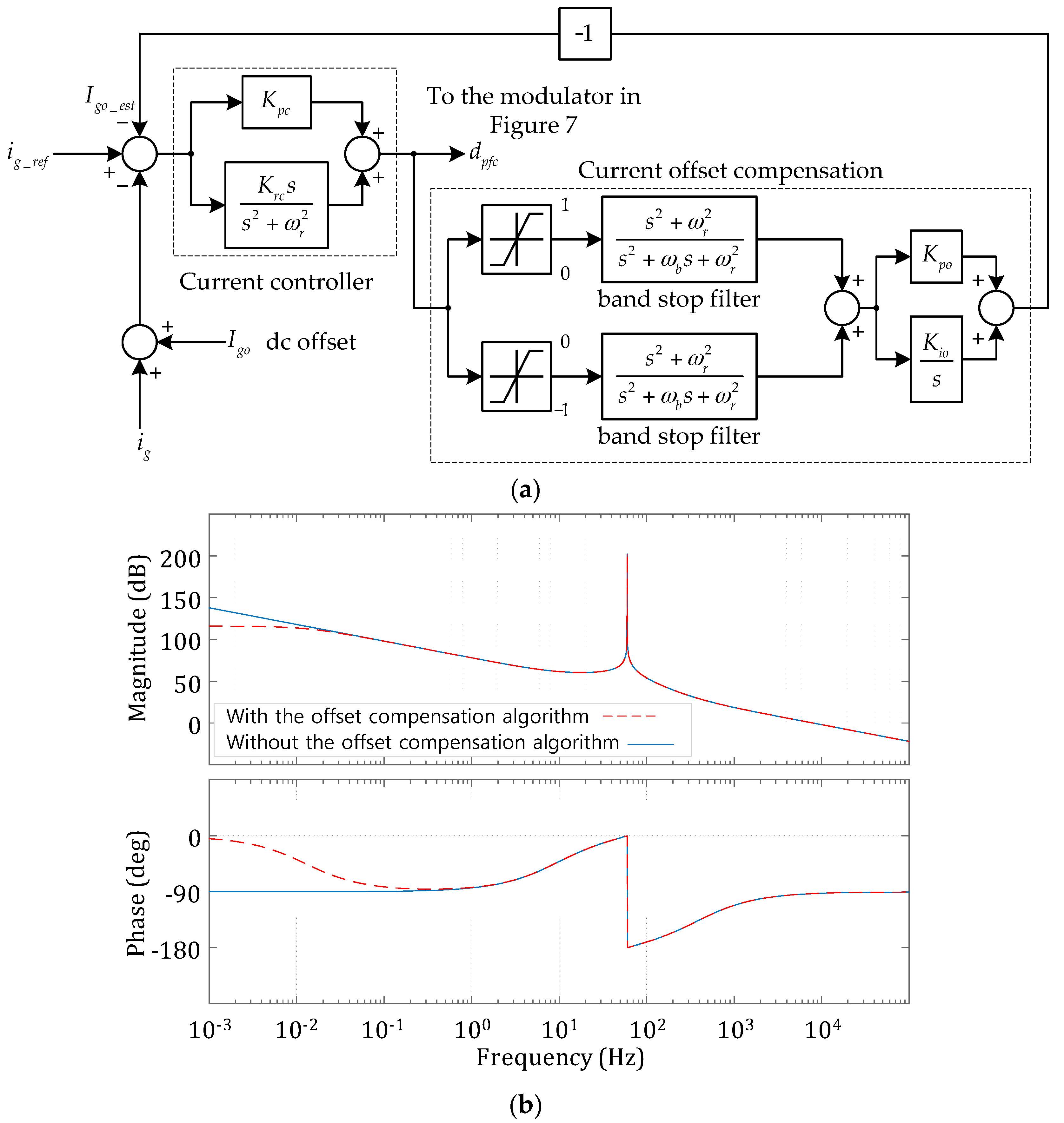

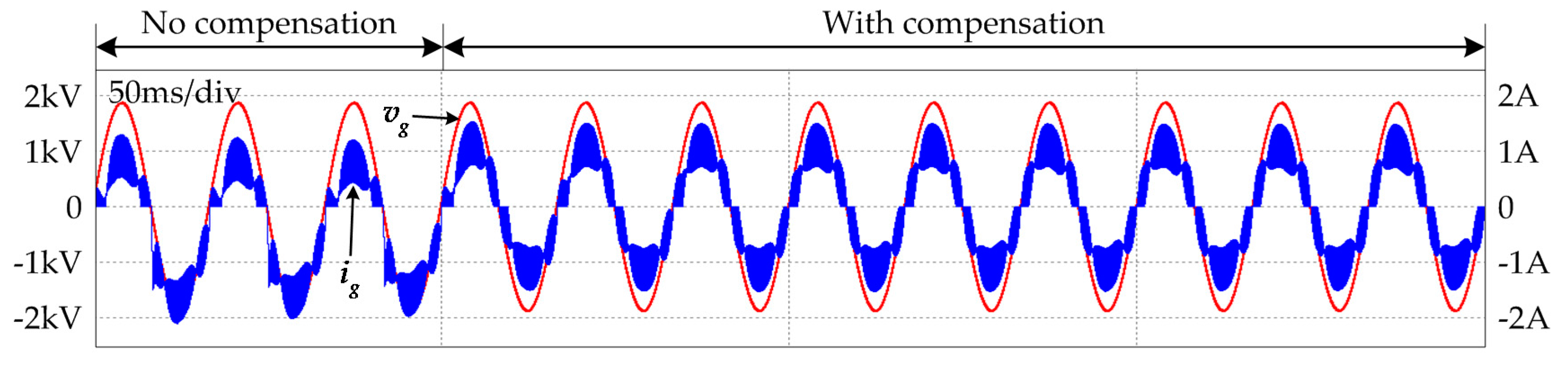

3. Proposed Input Current Offset Compensation Method

4. Simulation Results

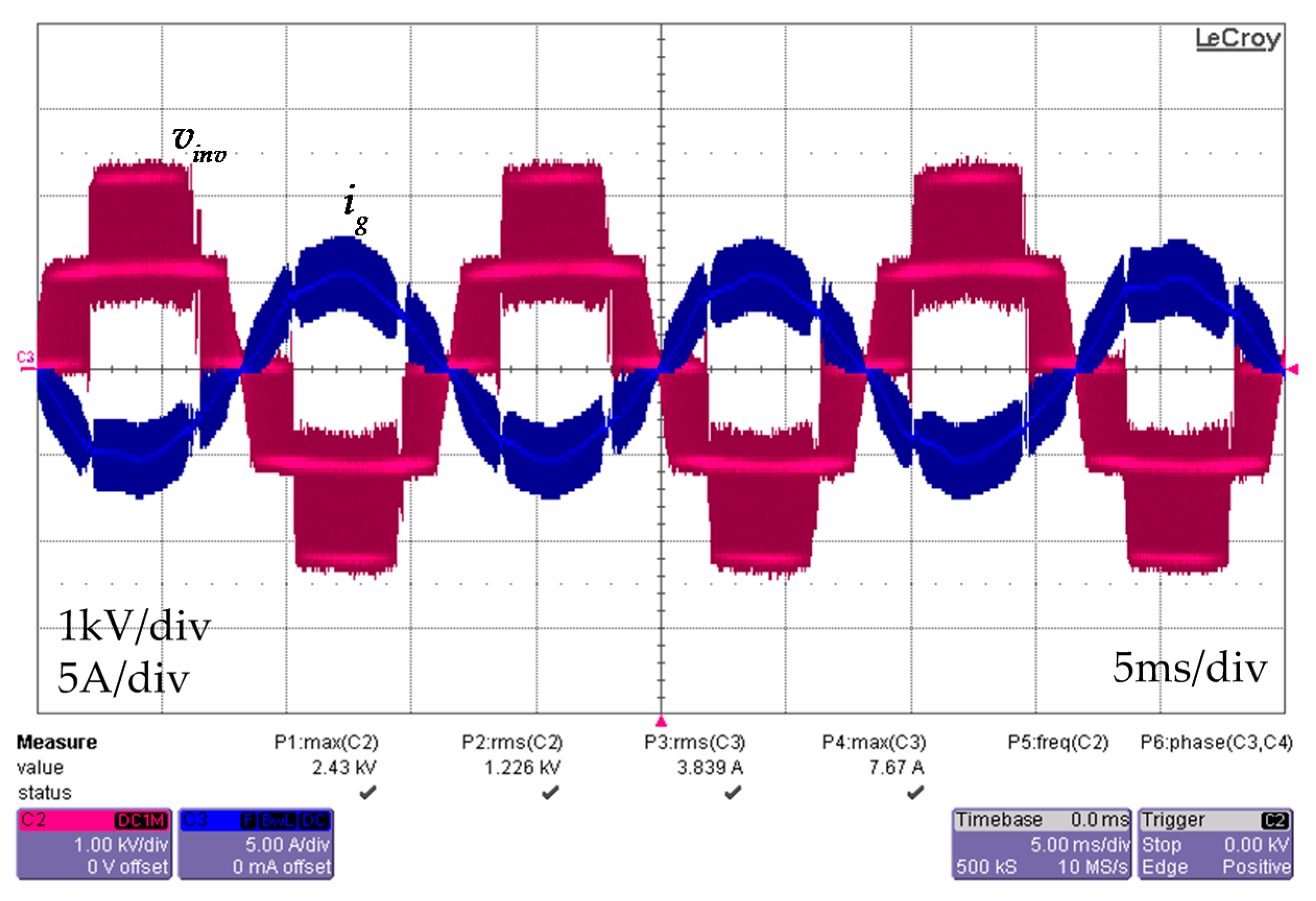

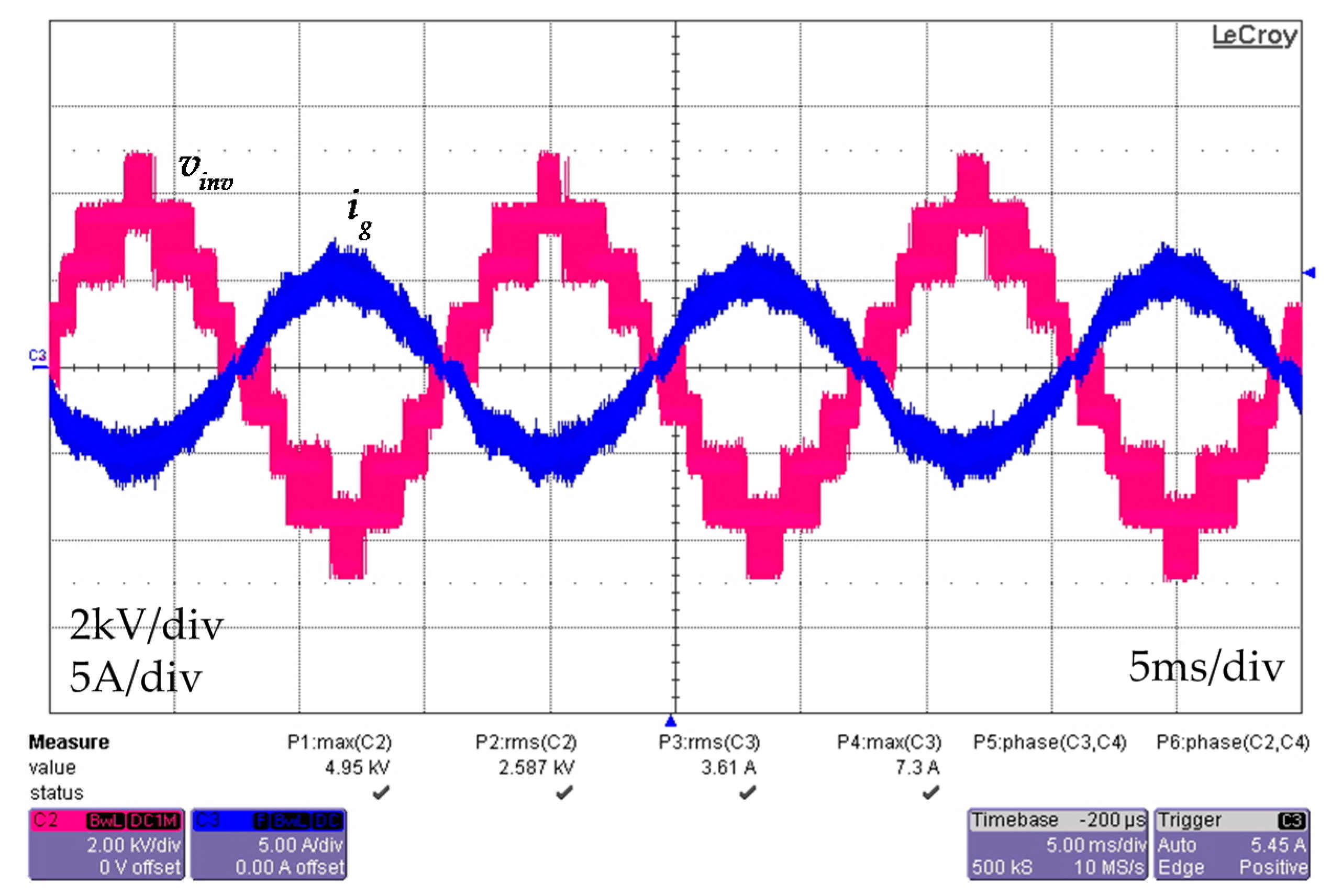

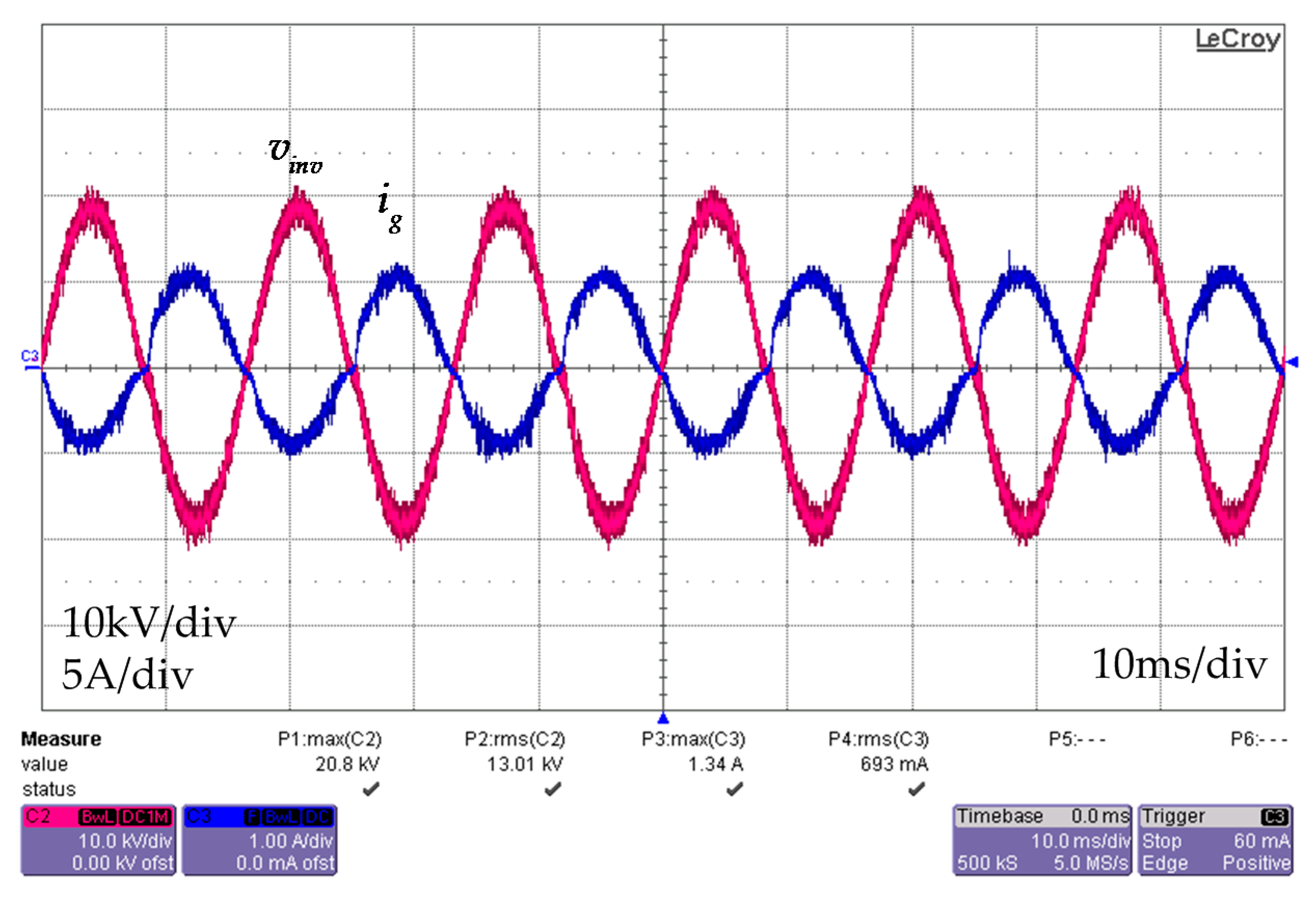

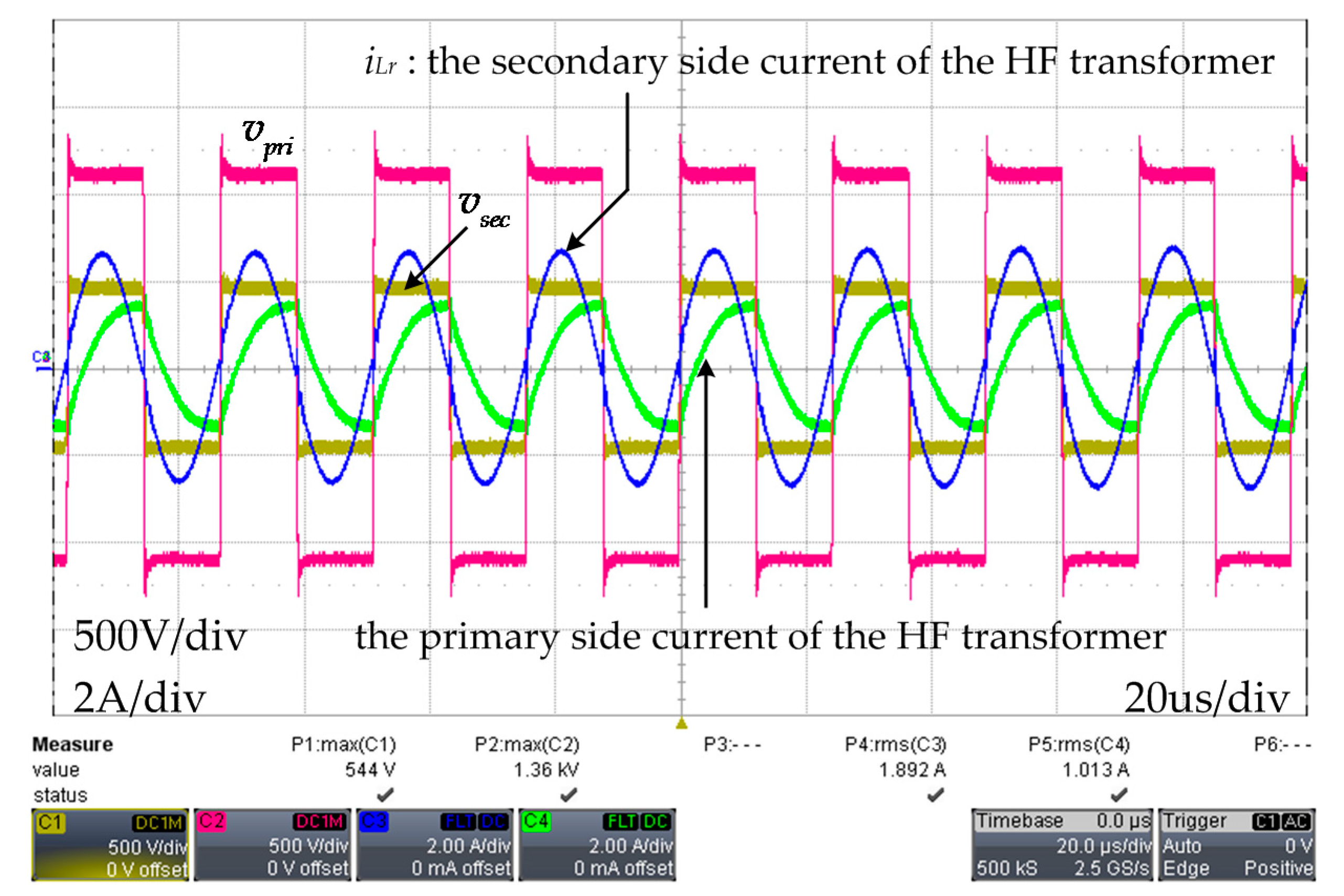

5. Experimental Results

6. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- She, X.; Huang, A.Q.; Burgos, R. Review of solid-state transformer technologies and their application in power distribution systems. IEEE J. Emerg. Sel. Top. Power Electron. 2013, 1, 186–198. [Google Scholar] [CrossRef]

- She, X.; Huang, A.Q.; Wang, G. 3-D space modulation with voltage balancing capability for a cascaded seven-level converter in a solid-state transformer. IEEE Trans. Power Electron. 2011, 26, 3778–3789. [Google Scholar] [CrossRef]

- She, X.; Yu, X.; Wang, F.; Huang, A.Q. Design and demonstration of a 3.6-kV–120-V/10-kVA solid-state transformer for smart grid application. IEEE Trans. Power Electron. 2014, 29, 3982–3996. [Google Scholar] [CrossRef]

- Yu, X.; She, X.; Zhou, X.; Huang, A.Q. Power management for dc microgrid enabled by solid-state transformer. IEEE Trans. Smart Grid 2014, 5, 954–965. [Google Scholar] [CrossRef]

- Huang, A.Q. Medium-voltage solid-state transformer: Technology for a smarter and resilient grid. IEEE Ind. Electron. Mag. 2016, 10, 29–42. [Google Scholar] [CrossRef]

- Yu, X.; She, X.; Ni, X.; Huang, A.Q. System integration and hierarchical power management strategy for a solid-state transformer interfaced microgrid system. IEEE Trans. Power Electron. 2014, 29, 4414–4425. [Google Scholar] [CrossRef]

- Jih-Sheng, L.; Maitra, A.; Mansoor, A.; Goodman, F. Multilevel intelligent universal transformer for medium voltage applications. In Proceedings of the Fourtieth IAS Annual Meeting. Conference Record of the 2005 Industry Applications Conference, Hong Kong, China, 2–6 October 2005; Volume 1893, pp. 1893–1899. [Google Scholar]

- Lai, J.S.; Maitra, A.; Goodman, F. Performance of a distribution intelligent universal transformer under source and load disturbances. In Proceedings of the Conference Record of the 2006 IEEE Industry Applications Conference Forty-First IAS Annual Meeting, Tampa, FL, USA, 8–12 October 2006; pp. 719–725. [Google Scholar]

- Zou, Z.; Carne, G.D.; Buticchi, G.; Liserre, M. Smart transforemr-fed variable frequency distributino grid. IEEE Trans. Ind. Electron. 2018, 65, 749–759. [Google Scholar] [CrossRef]

- Zou, Z.; Buticchi, G.; Liserre, M. Analysis and stabilization of a smart transformer-fed grid. IEEE Trans. Ind. Electron. 2018, 65, 1325–1335. [Google Scholar] [CrossRef]

- Andresen, M.; Raveendran, V.; Buticchi, G.; Liserre, M. Lifetime-based power routing in parallel converters for smart transformer application. IEEE Trans. Ind. Electron. 2018, 65, 1675–1684. [Google Scholar] [CrossRef]

- Zjang, J.; Wang, Z.; Shao, S. A three-phase modular multilevel DC-DC converter for power electronic transformer applications. IEEE J. Emerg. Sel. Top. Power Electron. 2017, 5, 140–150. [Google Scholar]

- Shi, J.; Gou, W.; Yuan, H.; Zhao, T.; Huang, A.Q. Research on voltage and power balance control for cascaded modular solid-state transformer. IEEE Trans. Power Electron. 2011, 26, 1154–1166. [Google Scholar] [CrossRef]

- Liu, J.; Yang, J.; Zhang, J.; Nan, Z.; Zheng, Q. Voltage balance control based on dual active bridge DC/DC converters in a power electronic traction transformer. IEEE Trans. Power Electron. 2018, 33, 1696–1714. [Google Scholar] [CrossRef]

- Wang, X.; Liu, J.; Ouyang, S.; Xu, T.; Meng, F.; Song, S. Control and experiment of an h-bridge-based three-phase three-stage modular power electronic transformer. IEEE Trans. Power Electron. 2016, 31, 2002–2011. [Google Scholar] [CrossRef]

- Costa, L.F.; Buticchi, G.; Liserre, M. Highly efficient and reliable SiC-based DC-DC converter for smart transformer. IEEE Trans. Ind. Electron. 2017, 64, 8383–8391. [Google Scholar] [CrossRef]

- Feng, J.; Chu, W.Q.; Zhang, Z.; Zhu, Z.Q. Power electronic transformer-based railway traction systems: Challenges and opportunities. IEEE J. Emerg. Sel. Top. Power Electron. 2017, 5, 1237–1253. [Google Scholar] [CrossRef]

- Gu, C.; Zheng, Z.; Xu, L.; Wang, K.; Li, Y. Modeling and control of a multiport power electronic transformer (pet) for electric traction applications. IEEE Trans. Power Electron. 2016, 31, 915–927. [Google Scholar] [CrossRef]

- She, X.; Huang, A.Q.; Lukic, S.; Baran, M.E. On integration of solid-state transformer with zonal DC microgrid. IEEE Trans. Smart Grid 2012, 3, 975–985. [Google Scholar] [CrossRef]

- Lai, J.S.; Lai, W.H.; Moon, S.R.; Zhang, L.; Maitra, A. A 15-kV class intelligent universal transformer for utility applications. In Proceedings of the 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 20–24 March 2016; pp. 1974–1981. [Google Scholar]

- Wang, J.; Wang, G.; Bhattacharya, S.; Huang, A.Q. Comparison of 10-kV SiC power devices in solid-state transformer. In Proceedings of the 2010 IEEE Energy Conversion Congress and Exposition, Atlanta, GA, USA, 12–16 September 2010; pp. 3284–3289. [Google Scholar]

- Zhao, T.; Yang, L.; Wang, J.; Huang, A.Q. 270 kVA solid state transformer based on 10 kV SiC power devices. In Proceedings of the 2007 IEEE Electric Ship Technologies Symposium, Arlington, VA, USA, 21–23 May 2007; pp. 145–149. [Google Scholar]

- Yang, L.; Zhao, T.; Wang, J.; Huang, A.Q. Design and analysis of a 270 kW five-level DC/DC converter for solid state transformer using 10 kV SiC power devices. In Proceedings of the 2007 IEEE Power Electronics Specialists Conference, Orlando, FL, USA, 17–21 June 2007; pp. 245–251. [Google Scholar]

- Wang, F.; Wang, G.; Huang, A.; Yu, W.; Ni, X. Design and operation of a 3.6 kV high performance solid state transformer based on 13 kV SiC MOSFET and JBS diode. In Proceedings of the 2014 IEEE Energy Conversion Congress and Exposition (ECCE), Pittsburgh, PA, USA, 14–18 September 2014; pp. 4553–4560. [Google Scholar]

- Wang, G.; Huang, X.; Wang, J.; Zhao, T.; Bhattacharya, S.; Huang, A.Q. Comparisons of 6.5 kV 25A Si IGBT and 10-kV SiC MOSFET in solid-state transformer application. In Proceedings of the 2010 IEEE Energy Conversion Congress and Exposition, Atlanta, GA, USA, 12–16 September 2010; pp. 100–104. [Google Scholar]

- Kim, J.-H. Generalized PWM Strategy for a Multi-Leg Multi-Level Voltage Source Inverter; Seoul National University: Seoul, Korea, 2006. [Google Scholar]

- Zhang, Y.; Gao, Y.; Li, J.; Summer, M.; Wang, P.; Zhou, L. High ratio bidirectional dc-dc converter with a synchronous rectification h-bridge for hybrid energy sources electric vehicles. J. Power Electron. 2016, 16, 2035–2044. [Google Scholar] [CrossRef]

- Kim, H.-W.; Park, J.-H.; Jeon, H.-J. Bidirectional power conversion of isolated switched-capacitor topology for photovoltaic differential power processors. J. Power Electron. 2016, 16, 1629–1638. [Google Scholar] [CrossRef]

- Yin, S.; Liu, Y.; Tseng, K.J.; Pou, J.; Simanjorang, R. Comparison of SiC voltage source inverters using synchronous rectification and freewheeling diode. IEEE Trans. Ind. Electron. 2018, 65, 1051–1061. [Google Scholar] [CrossRef]

- Heldwein, M.L.; Mussa, S.A.; Barbi, I. Three-phase multilevel pwm rectifiers based on conventional bidirectional converters. IEEE Trans. Power Electron. 2010, 25, 545–549. [Google Scholar] [CrossRef]

- Kolar, J.W.; Friedli, T. The essense of three-phase pfc rectifier systems-part I. IEEE Trans. Power Electron. 2013, 28, 176–198. [Google Scholar] [CrossRef]

- Zhao, Y.; Li, Y.; Lipo, T.A. Force commutaed three level boost type rectifier. In Proceedings of the Conference Record of the 1993 IEEE Industry Applications Society Annual Meeting, Toronto, ON, Canada, 2–8 October 1993; Volume 2, pp. 771–777. [Google Scholar]

- Wang, Z.; Cui, F.; Zhang, G.; Shi, T.; Xia, C. Novel carrier-based pwm strategy with zero-sequence voltage injected for three-level npc inverter. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 1442–1451. [Google Scholar] [CrossRef]

- Choudhury, A.; Pillay, P.; Williamson, S.S. A performance comparison study of space-vector and carrier-based pwm techniques for a 3-level neutral point clamped (NPC) traction inverter drive. In Proceedings of the 2014 IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES), Mumbai, India, 16–19 December 2014. [Google Scholar]

- Ojha, A.; Chaturvedi, P.; Littal, A.; Jain, S. Carrier based common mode voltage reduction techniques in neutral point clamped inverter based ac-dc-ac drive system. J. Power Electron. 2016, 16, 142–152. [Google Scholar] [CrossRef]

- Rahman, S. Resonant LLC Converter: Operation and Design; Infineon Technologies North America (IFNA) Corp.: Durham, NC, USA, 2012. [Google Scholar]

- Hu, Z.; Wang, L.; Qiu, Y.; Liu, Y.-F.; Sen, P.C. An accurate design algorithm for llc resonant converters-part II. IEEE Trans. Power Electron. 2016, 31, 5448–5460. [Google Scholar] [CrossRef]

- Zahid, Z.U.; Dalala, Z.M.; Chen, R.; Chen, B.; Lai, J.-S. Design of bidirectional dc-dc resonant converter for vehicle-to-grid (v2g) applications. IEEE Trans. Transp. Electr. 2015, 1, 232–244. [Google Scholar] [CrossRef]

- Jeong, M.-G.; Shin, H.; Baek, J.-W.; Lee, K.-B. An interleaving scheme for dc-link current ripple reduction in parallel-connected generator systems. J. Power Electron. 2017, 17, 1004–1013. [Google Scholar]

- Nouri, T.; Vosoughi, N.; Hosseini, S.H.; Sabahi, M. A novel interleaved nonisolated ultrahigh-step-up dc-dc converter with zvs performance. IEEE Trans. Ind. Electron. 2017, 64, 3650–3661. [Google Scholar] [CrossRef]

- Gohil, G.; Bede, L.; Teodorescu, R.; Kerekes, T.; Blaabjerg, F. Flux-balancing scheme for pd-modulated parallel-interleaved inverters. IEEE Trans. Power Electron. 2017, 32, 3442–3457. [Google Scholar] [CrossRef]

| Traditional Transformers | Solid-State-Transformers |

|---|---|

| AC distribution only | either DC or AC distribution |

| Limited steps of voltage conversion ratio | Wide voltage conversion ratio |

| No power quality compensation | Power quality compensation available |

| Heavy | Relatively light |

| Without DC-link | With DC-link (easily interfaced with other power conversion systems) |

| Mature technology | New technology |

| Polarity of ig | Switching Function Q | Pole Voltage vinv |

|---|---|---|

| ig > 0 | (1,1,1,1) | 0 V |

| (1,1,0,1) | Vdcl | |

| (1,0,1,1) | Vdch | |

| (1,0,0,1) | Vdch + Vdcl | |

| ig < 0 | (1,1,1,1) | 0 V |

| (1,1,1,0) | −Vdch | |

| (0,1,1,1) | −Vdcl | |

| (0,1,1,0) | −(Vdch + Vdcl) |

| Power Stage | Parameters | Values |

|---|---|---|

| active-front-end (AFE) converter | DC-link capacitance Cdc | 250 μF |

| Filter inductance Lg | 10 mH | |

| Switching frequency fs_AFE | 20 kHz | |

| LLC converter | Resonant inductance Lr | 16 μH |

| Resonant capacitance Cr | 1 μF | |

| HF transformer turn ratio (Np:Ns) | 120:48 | |

| Magnetizing inductance Lm | 100 mH | |

| Switching frequency fs_LLC | 40 kHz | |

| DC-link capacitance Co | 470 μF |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lim, J.-W.; Cho, Y.; Lee, H.-S.; Cho, K.-Y. Design and Control of a 13.2 kV/10 kVA Single-Phase Solid-State-Transformer with 1.7 kV SiC Devices. Energies 2018, 11, 201. https://doi.org/10.3390/en11010201

Lim J-W, Cho Y, Lee H-S, Cho K-Y. Design and Control of a 13.2 kV/10 kVA Single-Phase Solid-State-Transformer with 1.7 kV SiC Devices. Energies. 2018; 11(1):201. https://doi.org/10.3390/en11010201

Chicago/Turabian StyleLim, Jeong-Woo, Younghoon Cho, Han-Sol Lee, and Kwan-Yuhl Cho. 2018. "Design and Control of a 13.2 kV/10 kVA Single-Phase Solid-State-Transformer with 1.7 kV SiC Devices" Energies 11, no. 1: 201. https://doi.org/10.3390/en11010201

APA StyleLim, J.-W., Cho, Y., Lee, H.-S., & Cho, K.-Y. (2018). Design and Control of a 13.2 kV/10 kVA Single-Phase Solid-State-Transformer with 1.7 kV SiC Devices. Energies, 11(1), 201. https://doi.org/10.3390/en11010201