1. Introduction

Over the past few decades, the CMOS image sensor has gradually expanded its market share in the image sensor industry, becoming the mainstream image sensor technology and finding extensive applications in almost every field [

1]. The linear response of an image sensor is characterized by the output signal changing linearly with the intensity of incident light. To better display the image, many commercial photography devices have a non-linear response to light intensity [

2]. Non-linearity is intentionally implemented for purposes like high-dynamic-range image sensors [

3,

4], or to match human visual perception [

5]. But for accurate measurements, like in some medical and scientific imaging fields, optical sensors require precise light intensity and frequency responses [

6], where the linearity of the sensor becomes an important parameter. A lower level of nonlinearity can also enhance the accuracy of calculating parameters such as charge conversion gain or distance [

7,

8].

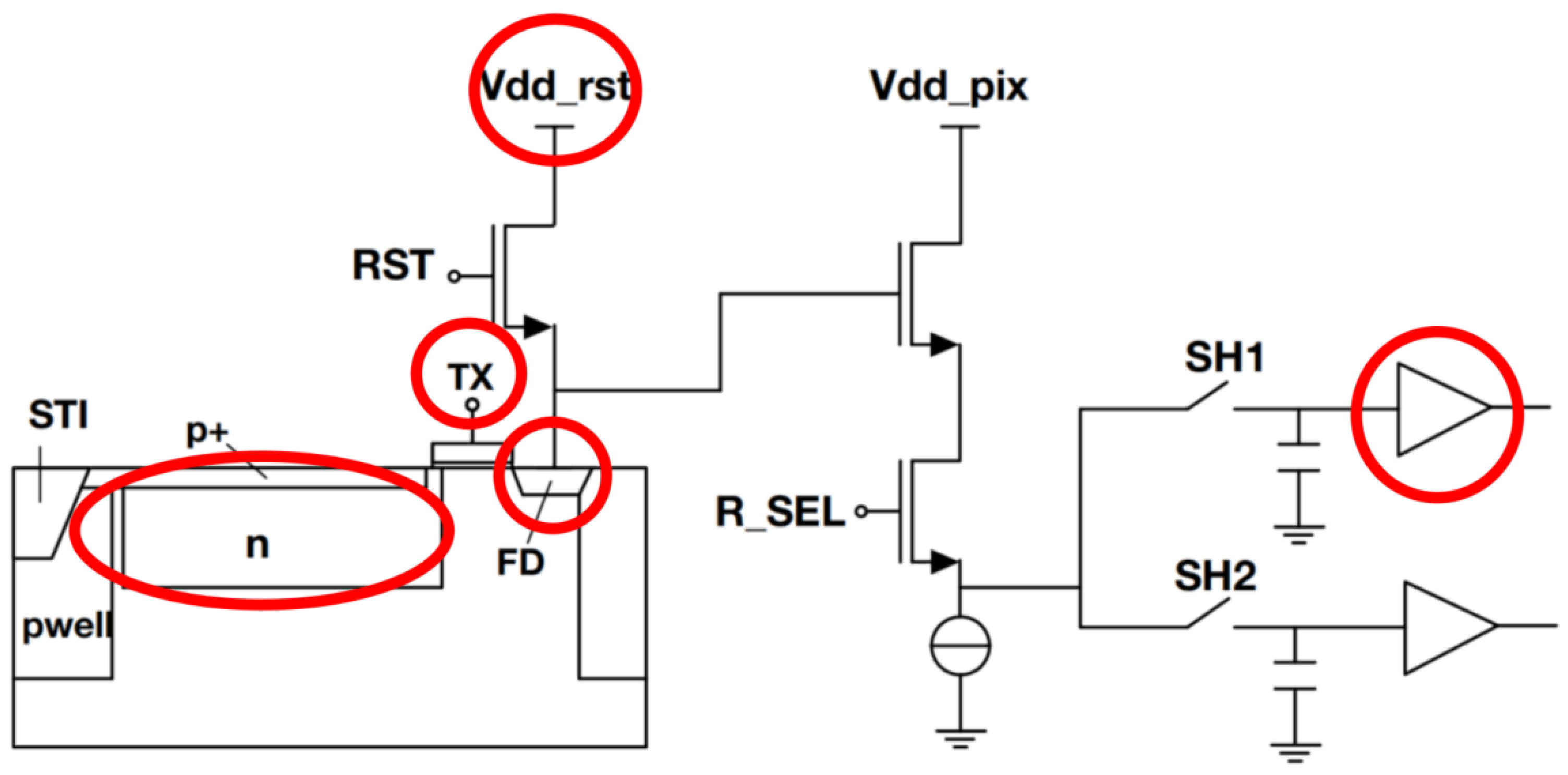

For typical 4-Transistor (4T) pixels, the PPD is the p+np structural photodiode utilized for photoelectric conversion. In this configuration, the nwell region of the PPD serves as the source of a transistor, with the Floating Diffusion (FD) acting as the drain. The FD is responsible for temporarily storing the signal electrons transferred from the PPD, as shown in

Figure 1. When increasing the light intensity or exposure time, more photoelectrons will accumulate in the PPD; the electrons are converted to a voltage change in FD and result in a larger output signal. This is a rather linear process. As the PPD gradually reaches its full well capacity at a high light level, excessive photoelectrons will not be read as an effective output signal, and the pixel’s output voltage will tend to saturate. This degrades the linearity of the pixel. Several notable studies have previously investigated the sources of nonlinearity in 4T pixels. Through improvements in circuit structure and methods such as digital calibration, these works have successfully mitigated the nonlinear response, achieving a final output linearity exceeding 99.95% [

9,

10,

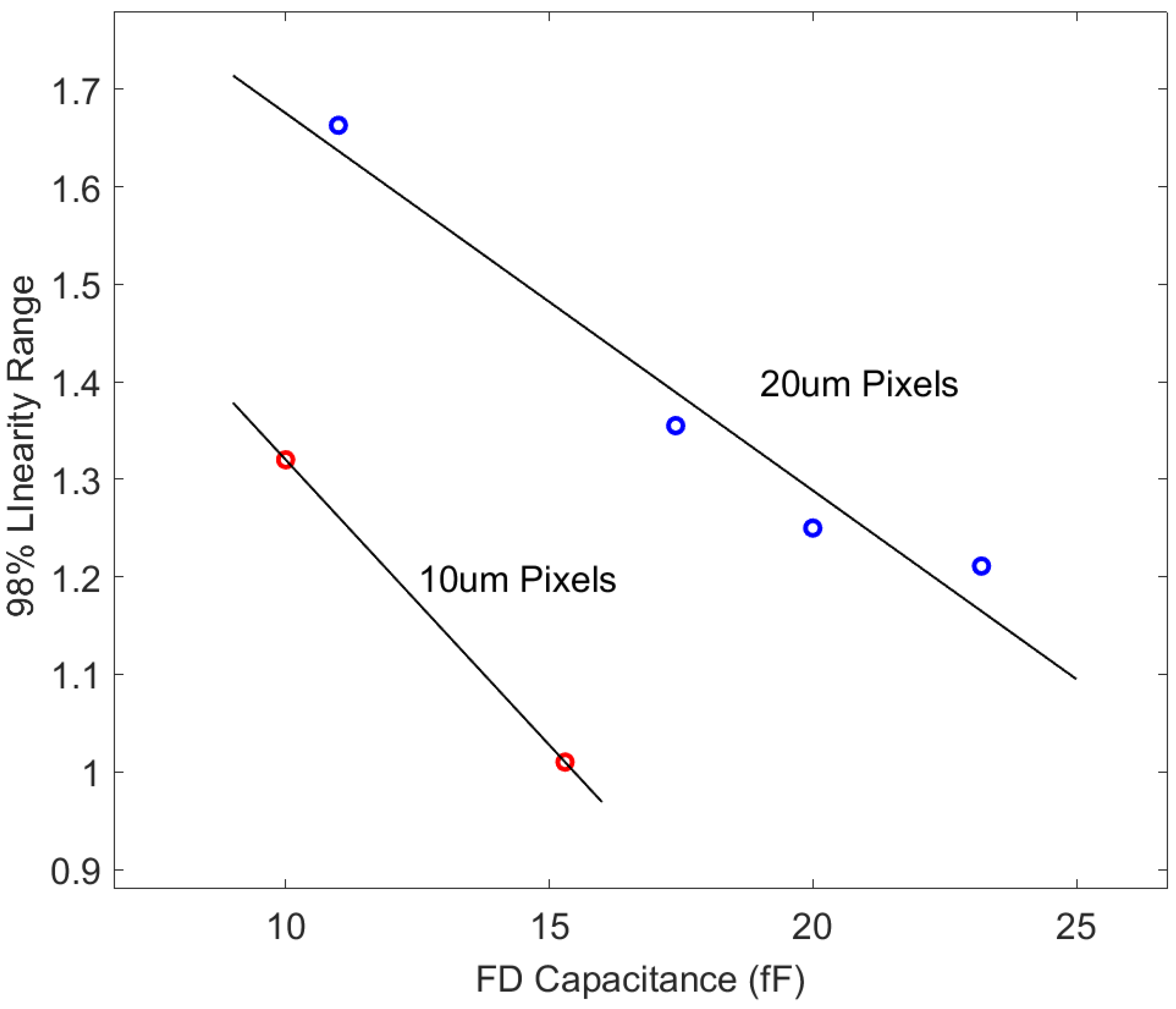

11]. Within the linear region, nonlinearity is mainly caused by the variation in electrical parameters with voltage, such as the small-signal voltage gain of the source follower (SF) and the capacitance of the FD (C

FD) node [

12]. The nonlinearity of CFD can be mitigated by reducing the capacitance value, and the linearity range of SF can be enhanced through the use of isolated p-well and deep n-well structures [

13,

14]. In terms of circuit structure, replacing the SF with p-MOS or an analog buffer, along with the addition of a capacitive trans-impedance amplifier (CTIA), has been proposed to mitigate the nonlinearity of the SF and C

FD. Replacing the SF cannot significantly reduce the nonlinearity. However, CTIA will introduce much more noise and increase the dark current [

10]. Digital calibration involves neutralizing nonlinearity in the output through a nonlinear ramp voltage generator [

5,

10]. In these studies, the optimization methods can be divided into the analog domain and digital domain. Achieving an extremely high linearity is mostly realized through digital domain; however, digital calibration is a method that consumes significant chip space and power [

9]. This underscores that the optimization at the existing hardware level is still insufficient for the design of high-linearity pixels.

In this study, our focus lies on enhancing the range of linear responses, and exploring more inherent parameters within the analog domain of 4T pixels. The essence of output nonlinearity lies in the variation in electrical parameters with output, and a higher nonlinearity inevitably leads to a reduction in the linear output range. Therefore, investigating the linear output range is a more straightforward and expedient approach.

This study centers on investigating the linear output range of 4T pixels and strategies for enhancing this range. The second section will provide a macroscopic analysis of factors influencing the linear output range. The third section will introduce the testing equipment and conditions, along with the data acquisition process. In the fourth and fifth sections, we will analyze the effects of pixel design and circuit control parameters, respectively, on the linear output range. In

Section 6, we will examine the impact of parameter adjustments on noise and offer a more detailed discussion on the influence of PPD design and TG transfer time on the linear output range. Finally,

Section 7 will summarize the results and analysis presented in this paper.

2. Influential Factors and Analysis

The structure of the 4T pixel and subsequent readout circuitry is illustrated in

Figure 1; numerous factors regarding this structure may influence the linear output range of pixels. The progression from incident light to digital signal output can be divided into four distinct stages: photo-detection, electron-to-voltage conversion, voltage amplification, and the final analog-to-digital signal conversion [

12]. Each of these stages has the potential to introduce nonlinearity. In this context, we posit that the processes of photo-detection and analog-to-digital conversion are ideal, with a specific focus on examining potential nonlinearity in the intermediate steps of electron-to-voltage conversion and voltage amplification. A portion of these influences arises from the CV characteristics of various circuit components, including the variations in C

FD and the gain in the SF with respect to output voltage, as well as the inherent linear output range of the circuit components, such as the output buffer and analog-to-digital converter. On the other hand, constraints on electron transfer efficiency, such as the design of TG sampling time and PPD doping concentration, also play a role. CV characteristics manifest in the output as nonlinearity due to variations in capacitance and gain, preventing the generation of an equivalent output voltage for the same amount of signal electrons. An insufficient charge transfer may result in the ineffective readout of signal electrons, consequently introducing nonlinearity. This phenomenon becomes more pronounced, particularly when more electrons accumulate in the PPD.

The linear output range is defined as the maximum voltage range at which the output linearity is ≥98%. This can be roughly determined using the following formula, wherein P represents the input light power, and V represents the corresponding output voltage. Four key factors contributing to nonlinearity have been identified: CG denotes the conversion gain of the FD capacitor, Q

TX is the transfer efficiency, and GSF and Gbuffer represent the small signal gain of the SF and output buffer, respectively. The denominators of each term are the values of these parameters at zero input. The numerators are the values at a certain light power. The independent variable of each parameter is labeled as P or V based on whether electron-to-voltage conversion has occurred. The overall nonlinearity effects of these factors are computed by multiplying them together to ascertain the total nonlinearity. To determine the linear output range, one must identify the corresponding P and V values where the nonlinearity calculated on the left-hand side is equal to 2%.

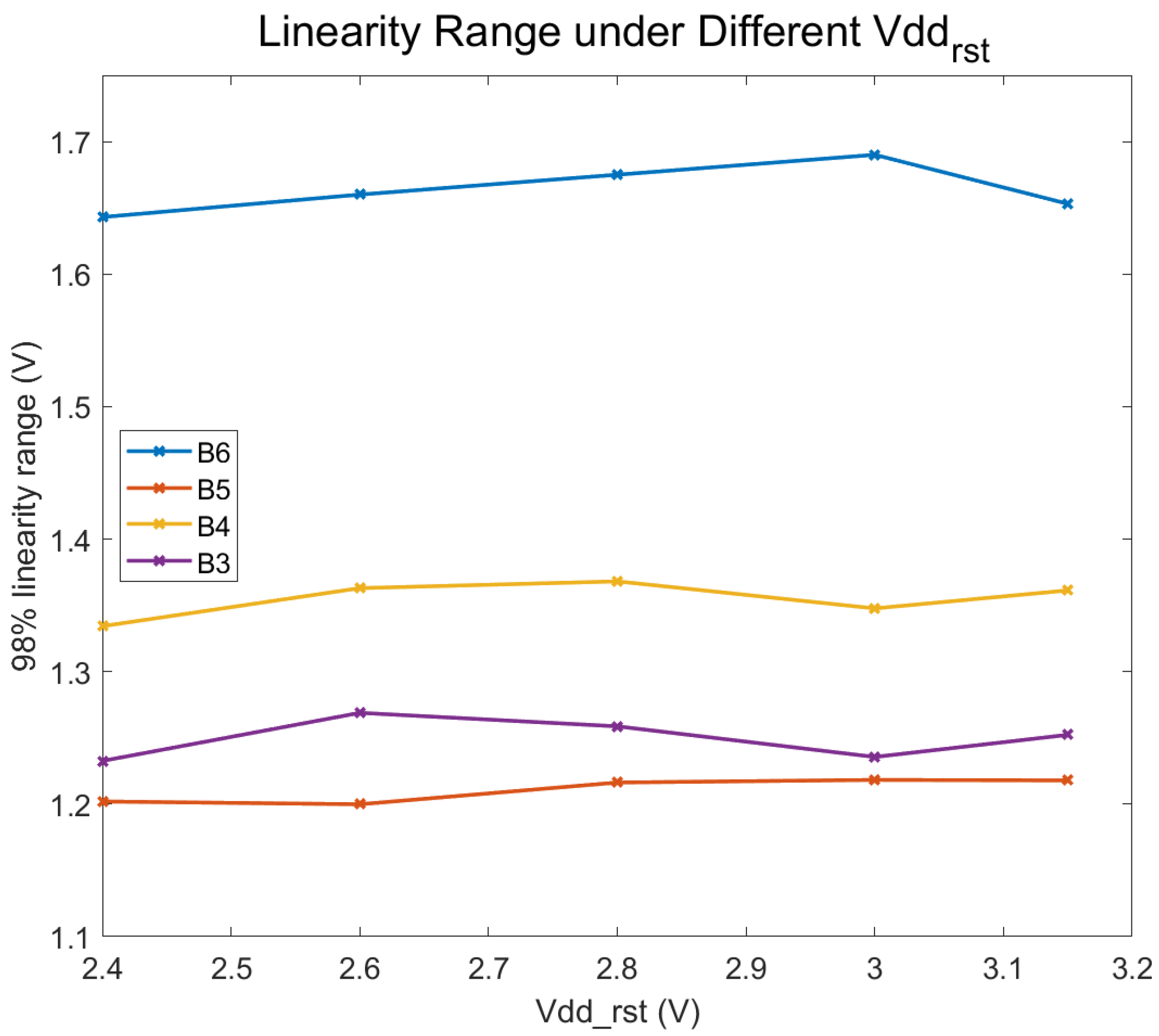

In this map, we investigate several parameters, marked in red circles, that may affect the pixel’s linear output range. These factors are categorized into two groups: pixel design and circuit control. Pixel design factors include the design of the PPD and the size of the FD capacitance. Circuit control examines the TG on-time, the reset voltage of FD, and the presence or absence of subsequent output buffers.

3. Experimental Setup and Data Process

The employed pixels are fabricated using the 0.18 μm 3.3 V CIS process. The pixel array consists of six channels, with B1 and B2 as two 10 μm pixel channels at a scale of 1 × 2560, while B3 to B6 are 20 μm channels at a scale of 1 × 1280. Each channel employs separate left and right readouts. Two different doping concentrations were employed for n-well in the PPD, namely standard doping (PPD-SD) and low-dose doping (PPD-LD). The full-well capacity of the PPD-LD is half that of PPD-SD.

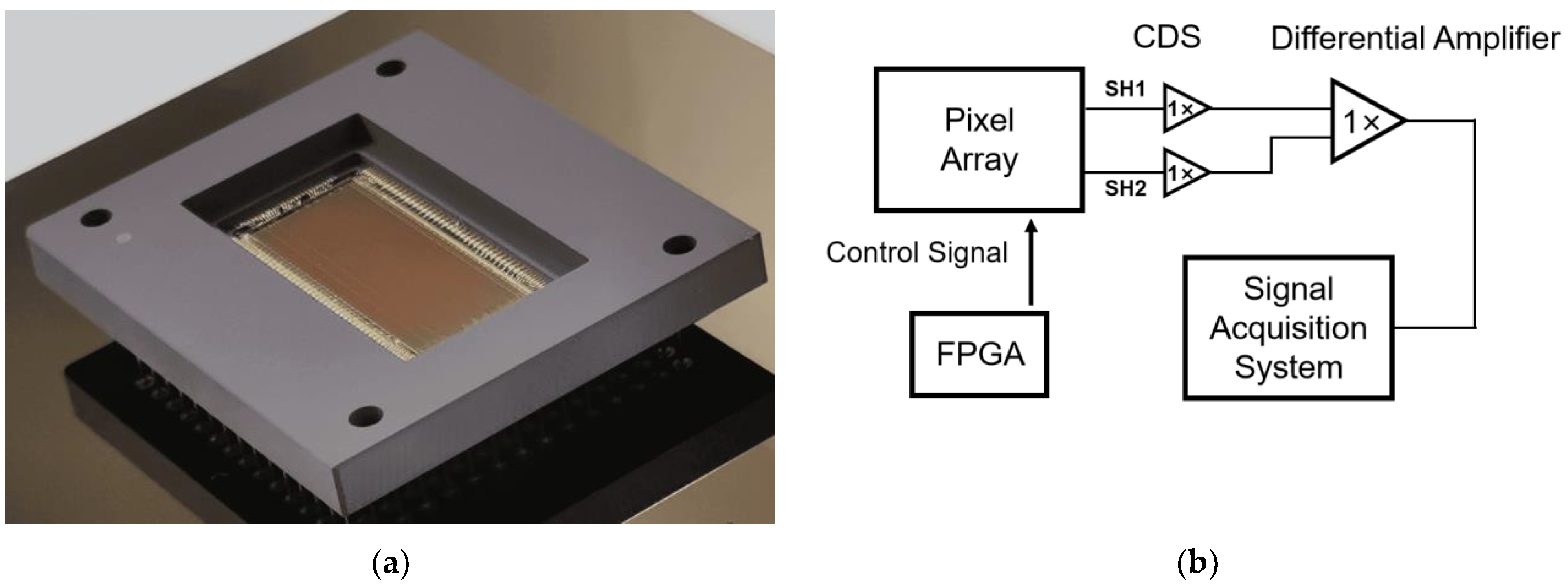

Figure 2a shows the graph of the CIS chip.

The schematic diagram of the PCB test board is presented in

Figure 2b: control signals for the CIS chip are generated by an FPGA. Utilizing a correlated double-sampling (CDS) technique, the output signals of each pixel are read, and these two signals are subsequently input into a differential amplifier to minimize readout noise. The signals are acquired using the National Instruments PXIe-6386 Multifunction I/O Module, and a pre-developed Labview program is employed to read 100 frames of data.

During testing, the output of the left half of the pixels is read, with each reading comprising 100 frames on average.

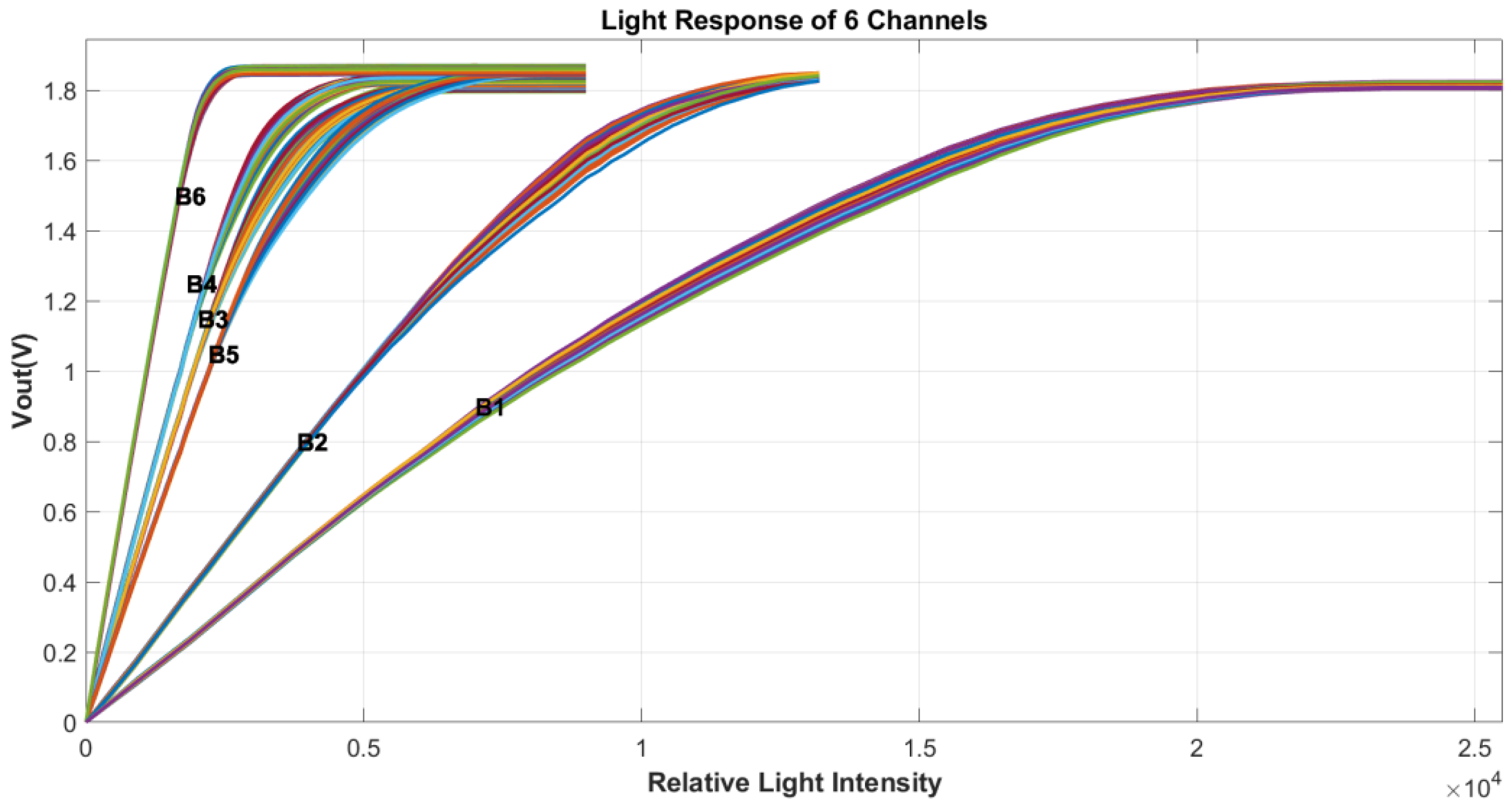

Figure 3 illustrates the output response curves of 340-pixel elements from each of the six channels, all under the same illumination intensity. Notably, the integration time for the 10 μm channels is half that of the 20 μm channels.

To better display the detail of the curves, the light power range in different figures is adjusted correspondingly using a light reduction film. The

x axes are labeled as “relative light intensity”. There are differences in the absolute light intensity corresponding to x-coordinate in each figure. For reference, the scale of 10,000 in

Figure 1 is approximately 2000 lux.

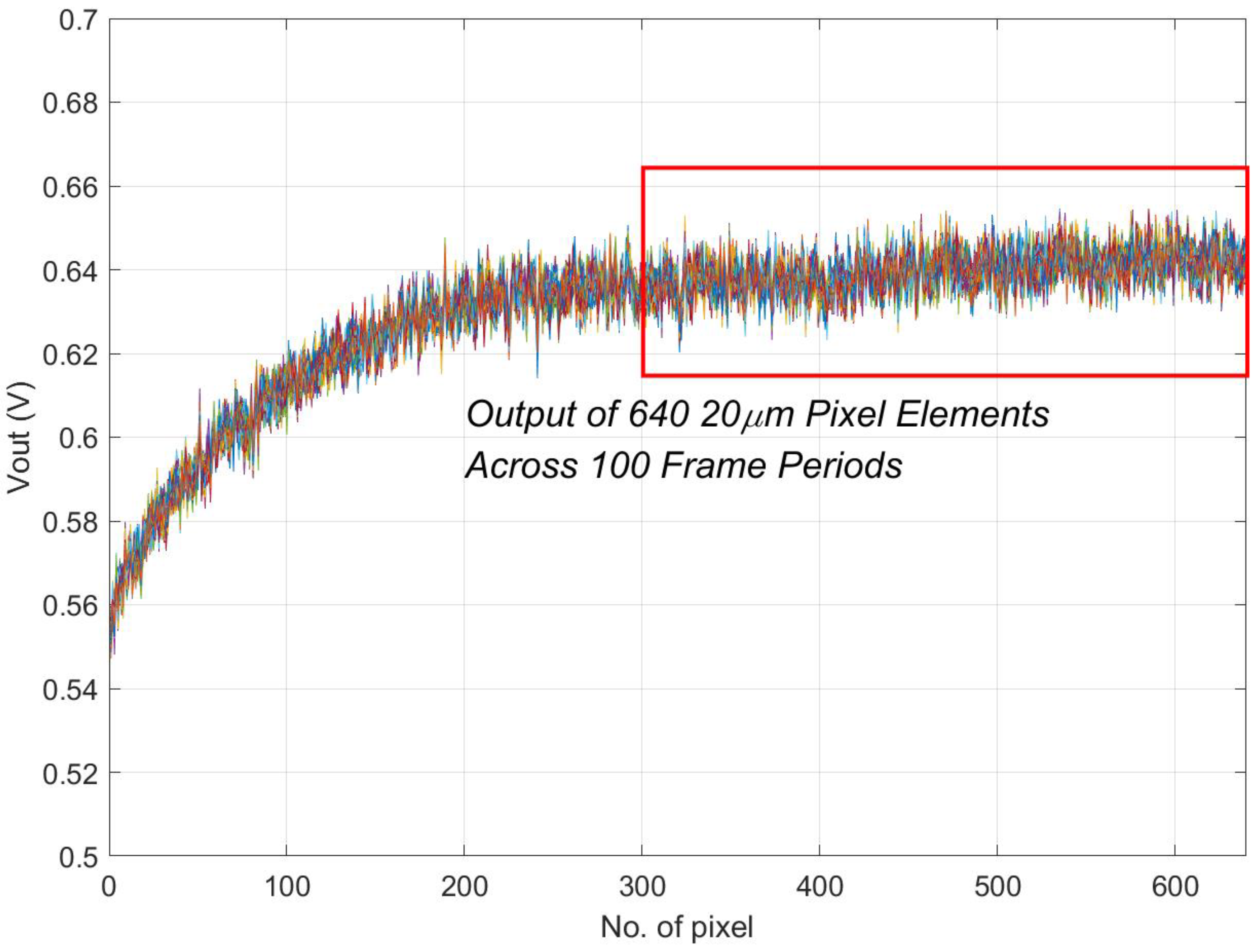

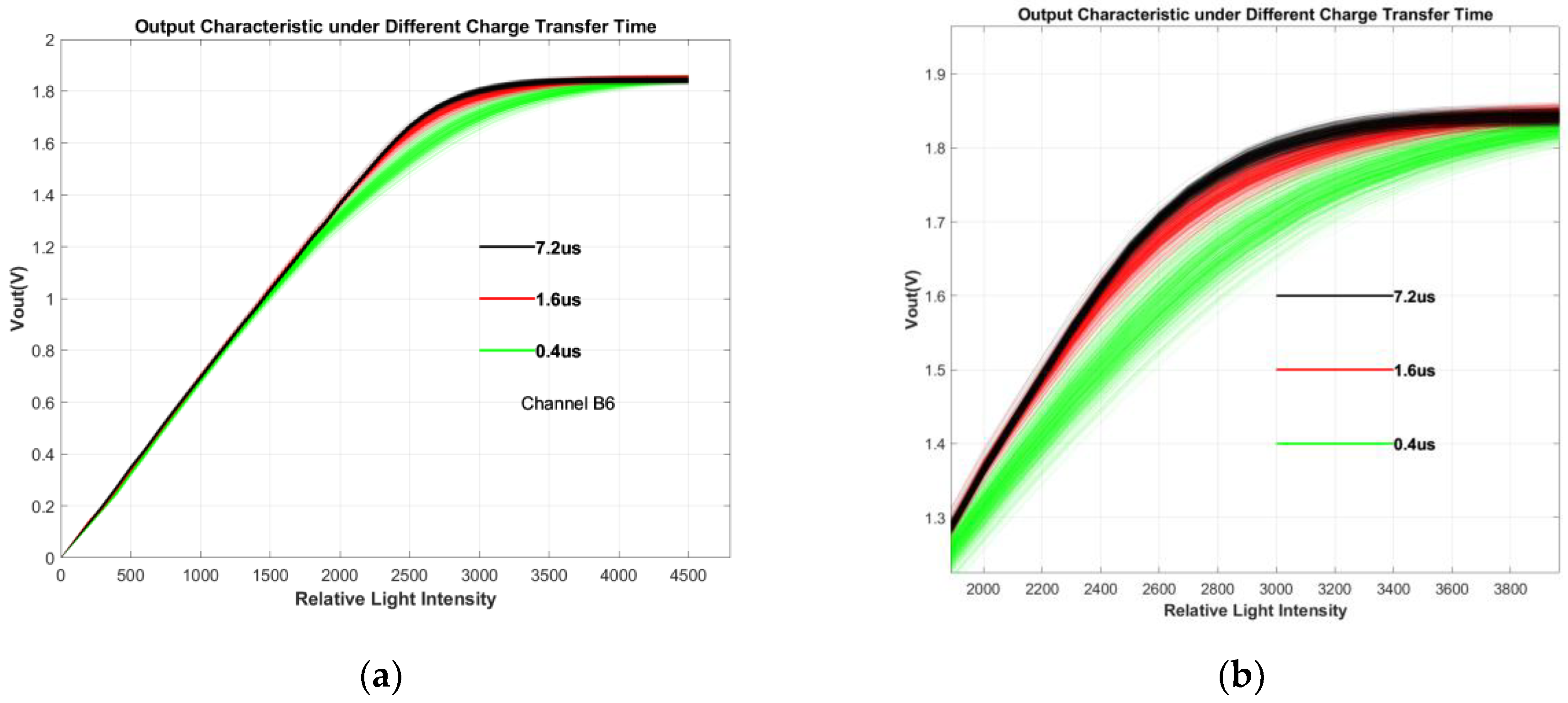

As illustrated in

Figure 4, the output of the left 640 pixels from Channel B6 is presented, comprising data from 100 frames. This representation shows the typical output of pixels under non-saturation conditions. Due to packaging constraints, the light at the edges is partially shadowed, resulting in weaker responses from these pixels. To ensure statistical accuracy, we excluded 300 pixels near the edge, as documented in

Table 1.

Each test is conducted under specific testing conditions, and if not specified, the general testing parameters are provided in

Table 1:

Table 1.

General testing conditions.

Table 1.

General testing conditions.

| Integration Time | 20 μm:280 μs; 10 μm:140 μs |

| TG Sampling Time | 3.6 μs |

| Number of Test Frames | 100 frames |

| Vdd Reset Voltage | 3.3 V |

| Output buffer | 1× output buffer |

| PPD type | PPD-SD |

| FD Capacitance | As shown in Figure 5 |

| Pixel count | 20 μm: Left No.301-640; 10 μm: Left No.941-1280 |

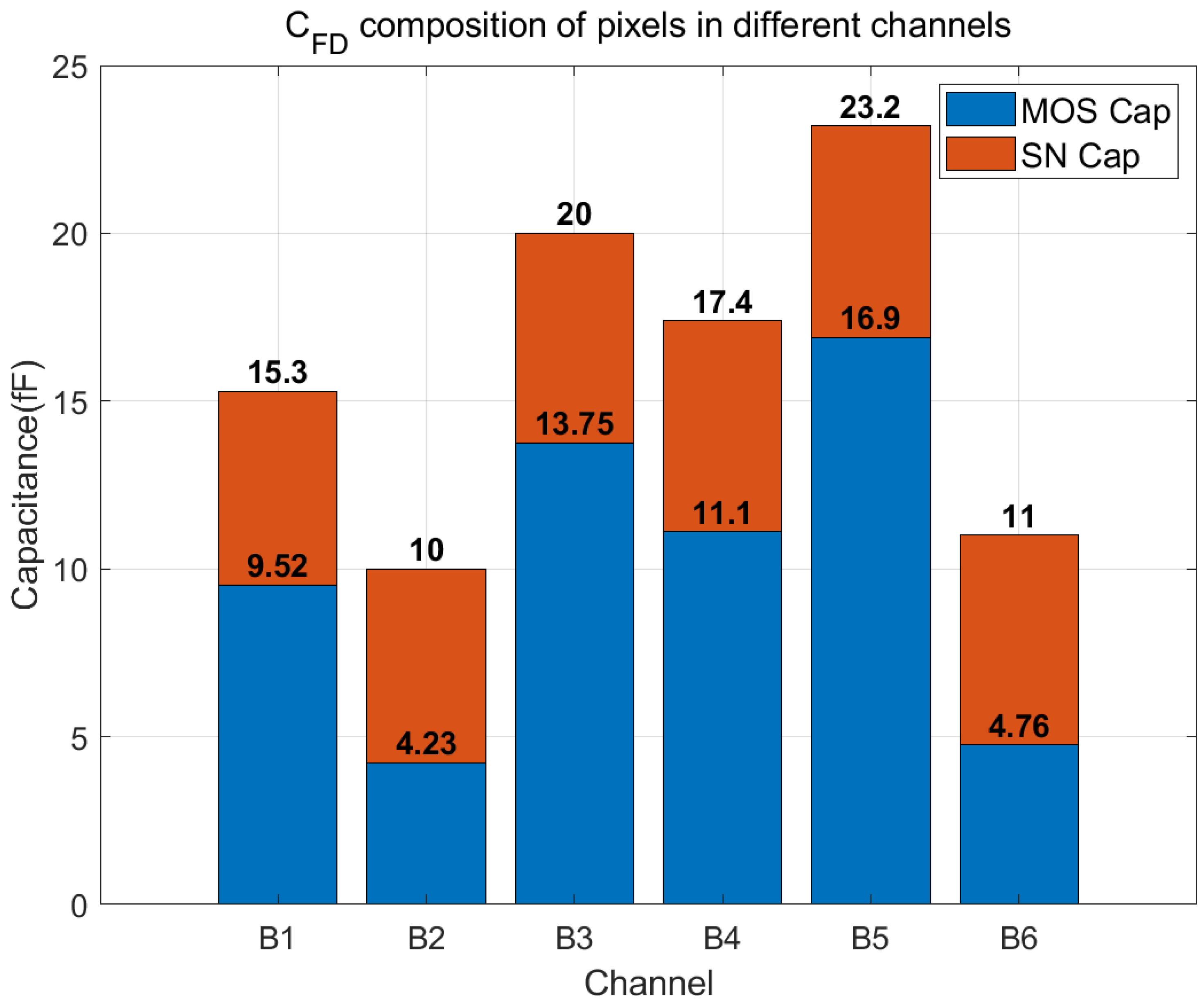

Figure 5.

The components of CFD for all six channels, with red bare representing the SN capacitance extracted from the layout and blue bar representing the additional MOS capacitance.

Figure 5.

The components of CFD for all six channels, with red bare representing the SN capacitance extracted from the layout and blue bar representing the additional MOS capacitance.

6. Discussion

Based on previous data and analysis, it is evident that methods such as reducing the PPD n-well doping concentration, adjusting the C

FD, and extending the TG time within a certain range can significantly enhance the linear output range of pixels. In this section, we will investigate whether these improvements introduce additional readout noise and delve deeper into the mechanisms behind the optimization of n-well doping and TG time. Additional noise canceling techniques can also be implemented [

15,

16].

The following figure illustrates the magnitude of noise voltage for each channel under different conditions, with Fixed Pattern Noise (FPN) contributing the most to the overall output noise. In our statistical analysis, we excluded the FPN and calculated the standard deviation of the remaining data over a 100-frame period, and then averaged the noise data for 340-pixel elements.

Figure 12a displays the noise data for several channel pixels under varying TG times, while

Figure 12b compares the noise differences between PPD-SD and PPD-LD.

For the B6 channel pixels with a smaller FD capacitance, the output noise voltage increases with longer TG times, but for channels with a larger FD capacitance, extending TG time does not result in significant changes in noise. It is noteworthy that, based on the test results in

Section 5.1, extending the TG time beyond several microseconds saturates the linear output range of pixels, and adapting a longer TG time is actually meaningless. The results in

Figure 12b demonstrate that lower-concentration n-well doping has no discernible impact on noise, and the influence of FD size on noise can be disregarded. This indicates that by optimizing factors such as the FD capacitor, PPD n-well doping, and TG time, it is possible to significantly enhance the linear output range of pixels without introducing a noticeable impact on output noise.

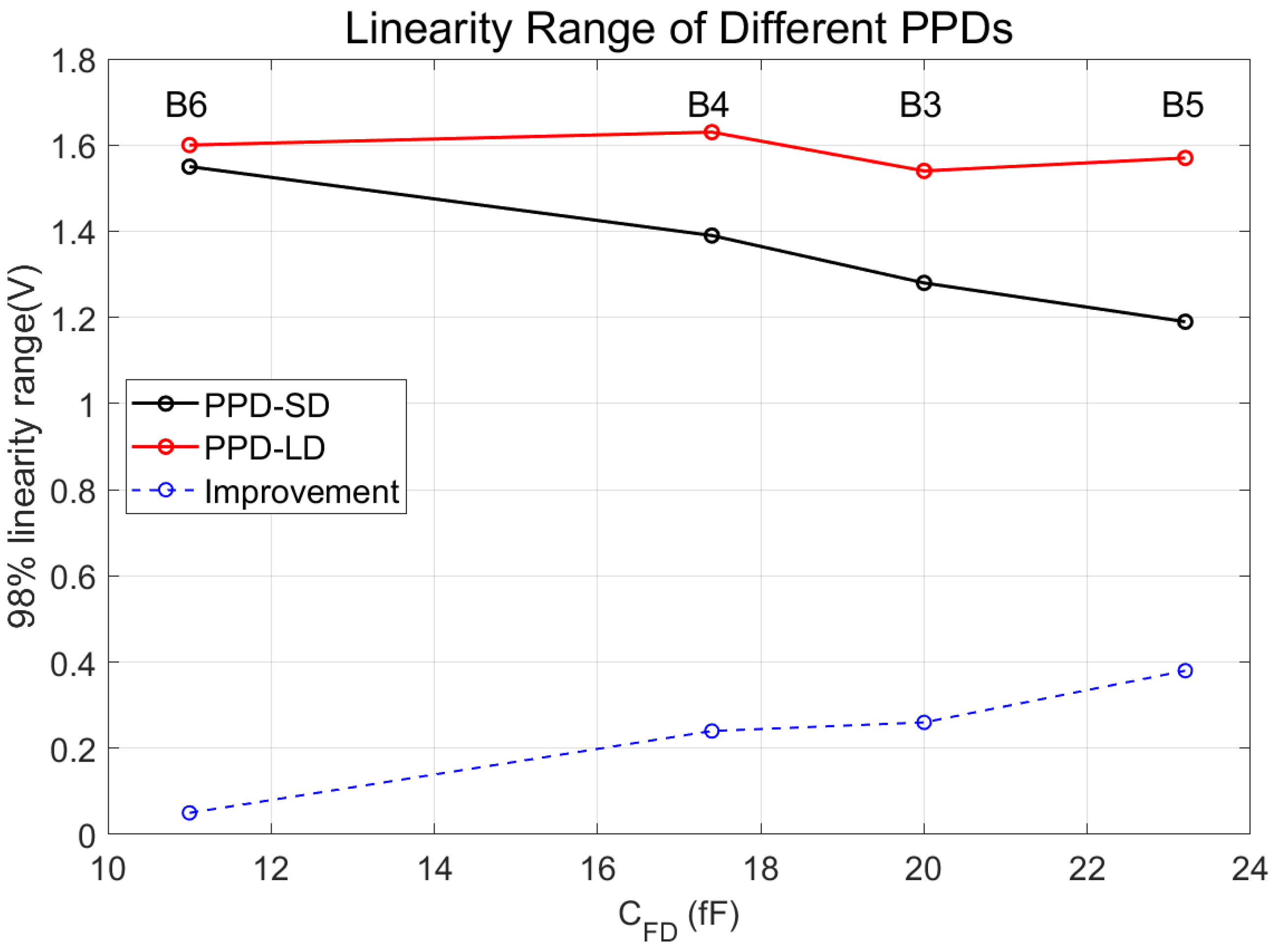

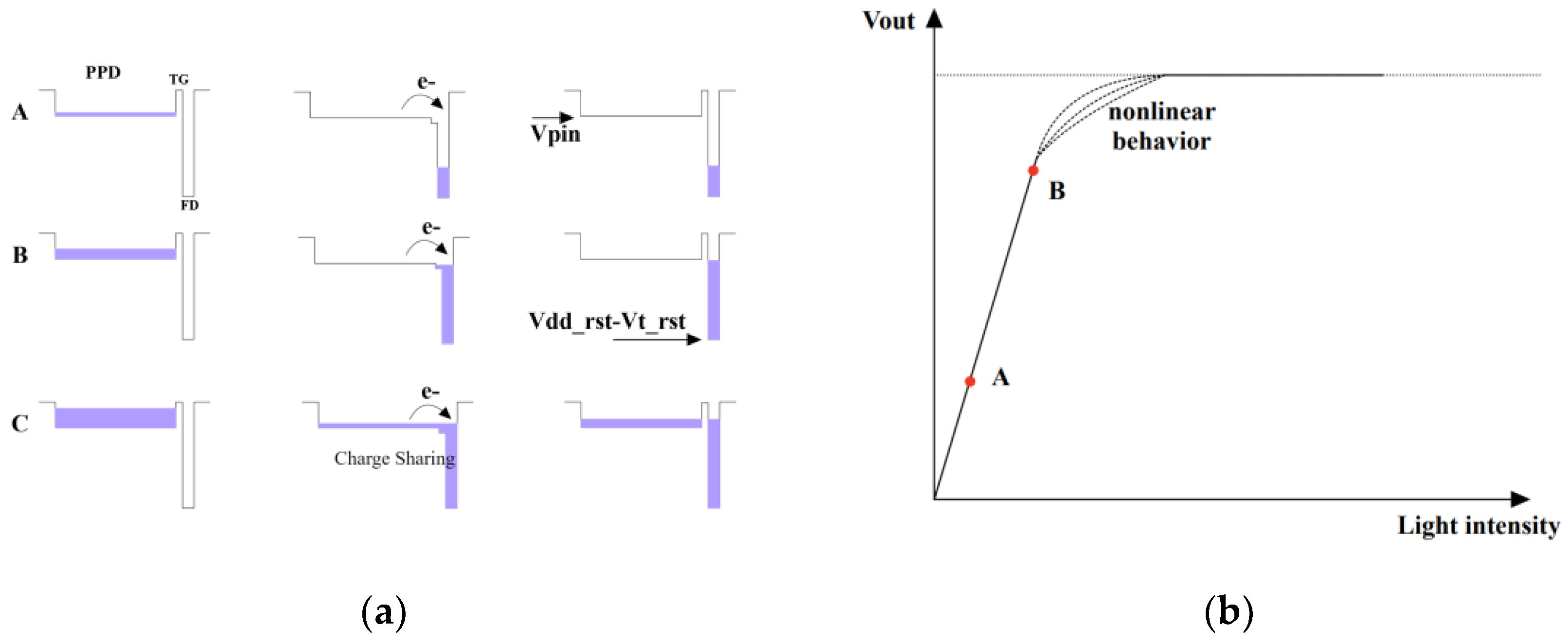

To understand the reason for the phenomenon wherein a pixel characterized by a diminished PPD capacitance exhibits an expanded linear output range, an examination of the charge transfer process is imperative.

Figure 13a presents potential diagrams illustrating the trajectory of electron transfer, starting from the edge of the PPD, passing through the channel beneath TG, and concluding at the FD node. During stage A, when the number of photoelectrons within the PPD is relatively low, the activation of TG results in the transfer of photoelectrons to the FD node, inducing a discernible drop in voltage across the FD. Progressing from stage A to B, the count of photoelectrons remains sufficiently modest, and the FD is still sufficient to accommodate all photoelectrons. Ignoring the variations in C

FD with respect to the bias voltage, as mentioned earlier, the voltage drop across the FD node steadily escalates in a linear fashion with the augmentation in the count of photoelectrons.

However, a crucial consideration arises due to the presence of a pinning potential (Vpin) within the PPD, compounded by the discrepancy in capacitance between PPD and FD. When there are excessive photoelectrons, a redistribution occurs between the two capacitors through charge-sharing, as illustrated in

Figure 13a. Hence, when the voltage on the FD node attains the critical value Vpin, an equivalent voltage drop can no longer be sustained by the same number of electrons, causing the output curve’s departure from the linear region. The process-induced deviation of Vpin also causes non-uniformity among the families of curves. Notably, the pinning voltage of PPD-LD is significantly diminished owing to the reduced n-well doping.

Furthermore, it can be observed that PPD-LD exhibits a more pronounced improvement in channels with a larger FD. This is attributed to the fact that, under the given test conditions of integration time and TG time, around 1.6 V represents the upper limit of the linear output range that is achievable using the pixels. This also explains the weaker correlation between the linear output range and CFD in the data for PPD-LD channels.

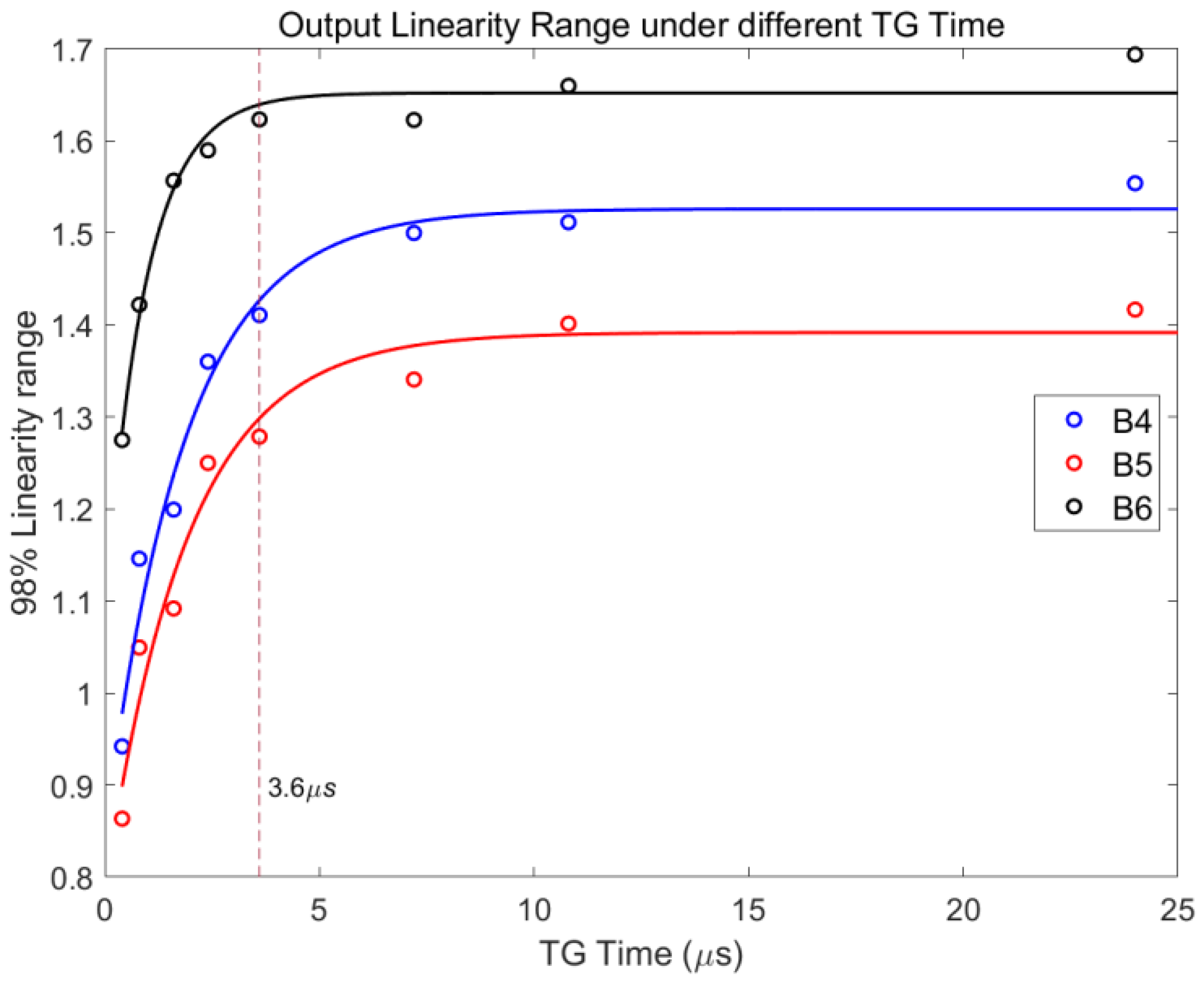

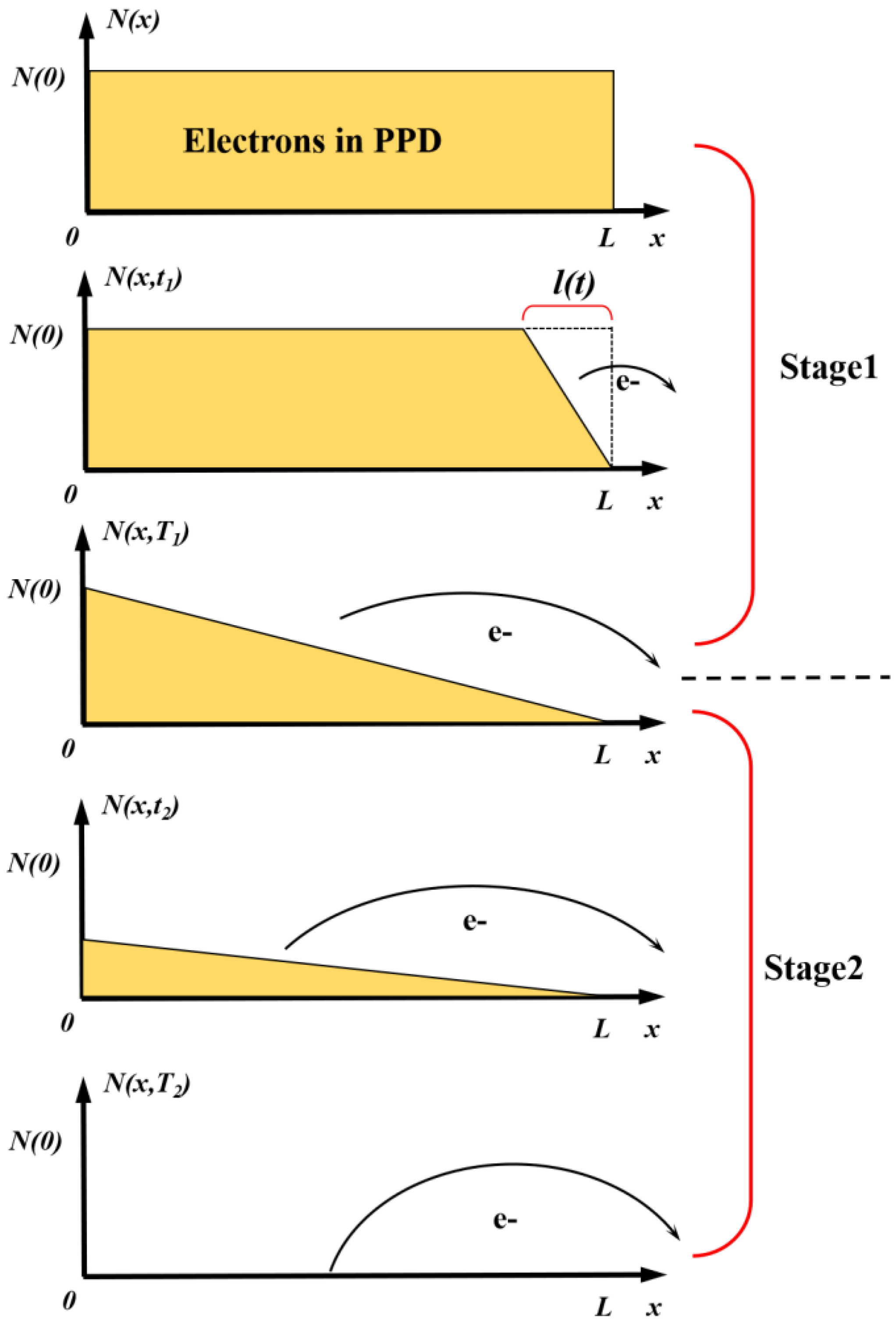

In the analysis presented in

Section 2, we posited that the linear output range is directly linked to the charge transfer efficiency, Q

TX. Consequently, it is necessary to scrutinize the charge transfer process and, based on this, develop a parameter model to fit the variation in the linear output range with respect to TG time.

Figure 14 depicts a one-dimensional PPD model with a total length L. Given the larger PPD dimensions considered in this study, the charge transfer process is predominantly governed by the diffusion mechanism [

17].

During the transfer process, electrons near the TG are rapidly swept into the FD node through the drift process. As the drift process is significantly faster than the diffusion process, the calculation of the total electron transfer time only needs to consider the diffusion process. Simultaneously, the influence range of the electric field near the TG and at the edge of the PPD is limited, so the length over which the farthest electrons need to diffuse is approximately L. Considering a PPD irradiated with a certain amount of light after a certain time, as illustrated in

Figure 15, N(t,x) represents the electron line density at a specific position in the PPD at a given moment, and N(0) represents the maximum charge line density in the PPD at the initial moment.

Initially, the electron distribution function near the TG has an infinite slope, leading to the rapid diffusion of some electrons. After the diffusion of some electrons, the slope of the N distribution (i.e., the gradient of electron density) decreases, and the diffusion process becomes progressively slower. Mathematically, as the gradient of the final charge density tends toward zero, Q

TX does not reach 100%, and it is only possible to calculate the transfer time of a specific Q

TX value. For ease of calculation, electron diffusion is divided into two processes: the first process transfers half of the charge, and the second process transfers the remaining portion of the charge, as illustrated in

Figure 15. At thermal equilibrium, the diffusion equation is expressed as follows:

where J

n represents the diffusion current density, and D is the corresponding diffusion coefficient. In the first stage, the equation can be formulated based on charge conservation as follows:

The left-hand side of the equation represents the total number of electrons diffusing during time t, which can also be calculated using the expression on the right-hand side through the distribution function N, as illustrated in

Figure 15. Accordingly, we have:

Let l = L, we can yield the transfer time of the first stage as follows:

Similarly, using charge conservation for the second stage, it can be expressed as:

If the remaining charge proportion is denoted as p, and:

The time for the second stage T

2 can be solved when the remaining charge proportion is p:

The above analysis establishes a physics-based relationship between charge transfer time and transfer efficiency. Assuming the linear output range is proportional to Q

TX with a coefficient C, we can roughly construct a mathematical relationship between TG time and the linear output range. The constant part can be set as unknown parameters. By then using the constructed parameter expression to fit the data points, we can derive a curve depicting the relationship between the linear output range and TG time:

The fitting curve in

Figure 8 is based on this expression, demonstrating that when TG time is relatively short, extending TG time leads to a rapid increase in the linear output range, and as TG time becomes longer, the linear output range tends to saturate.