Field Programmable Gate Array-Based Smart Switch to Avoid Inrush Current in PV Installations

Abstract

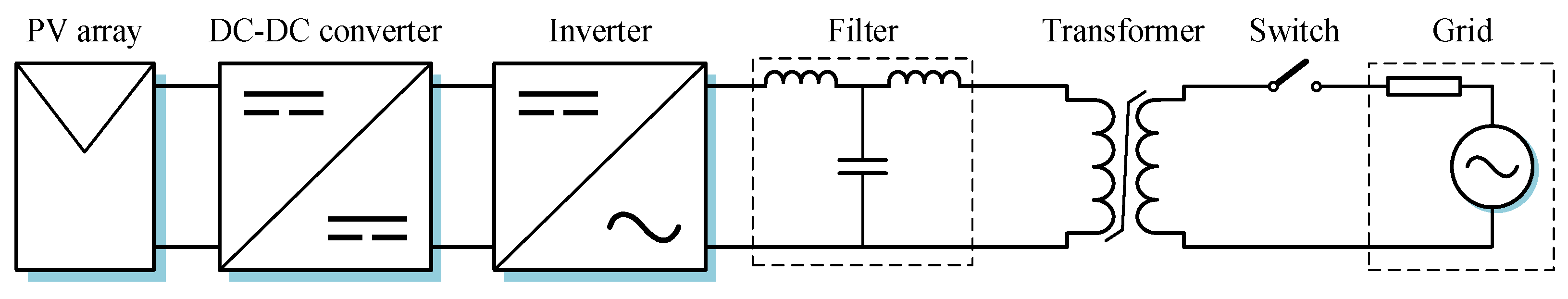

1. Introduction

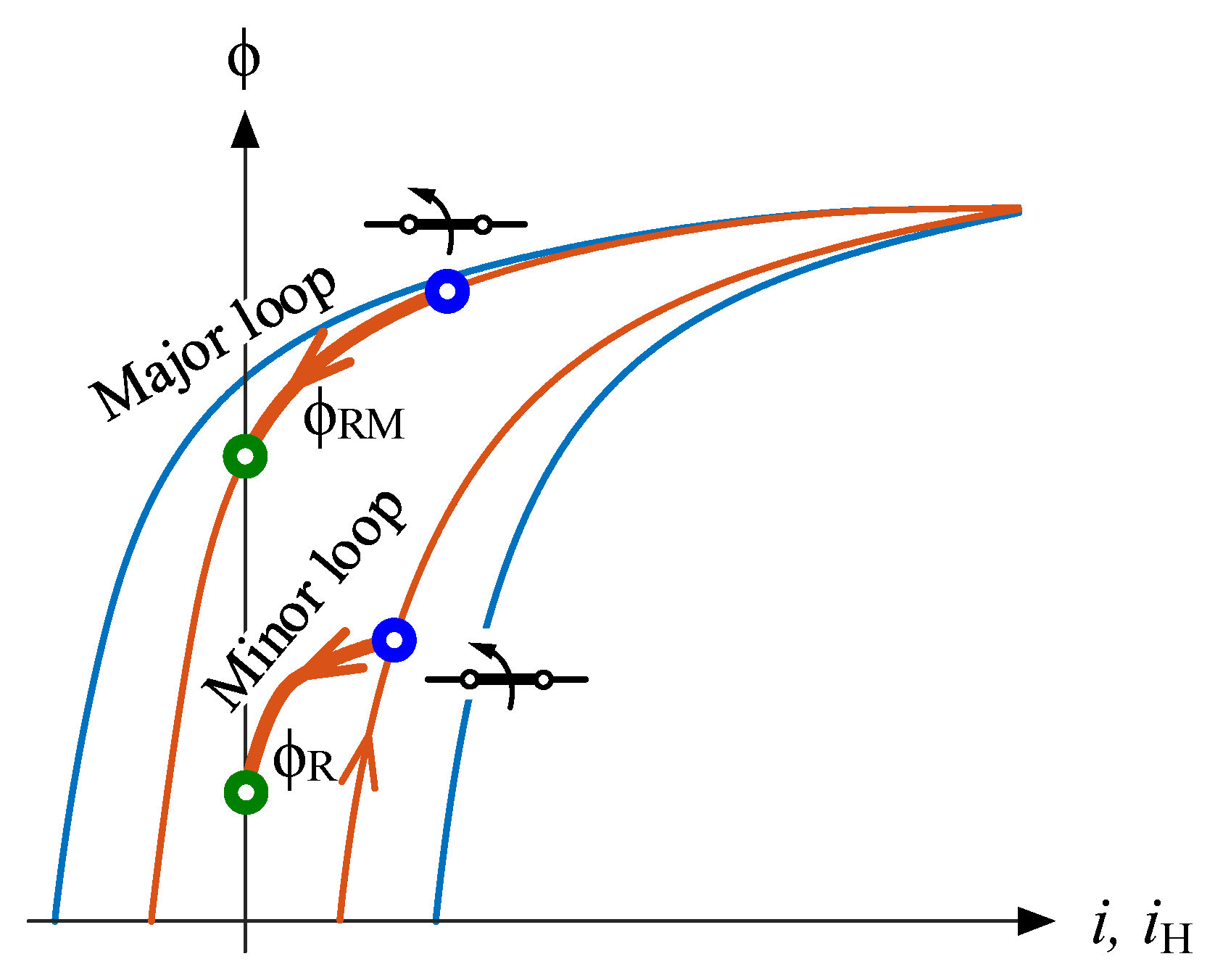

2. Theoretical Background

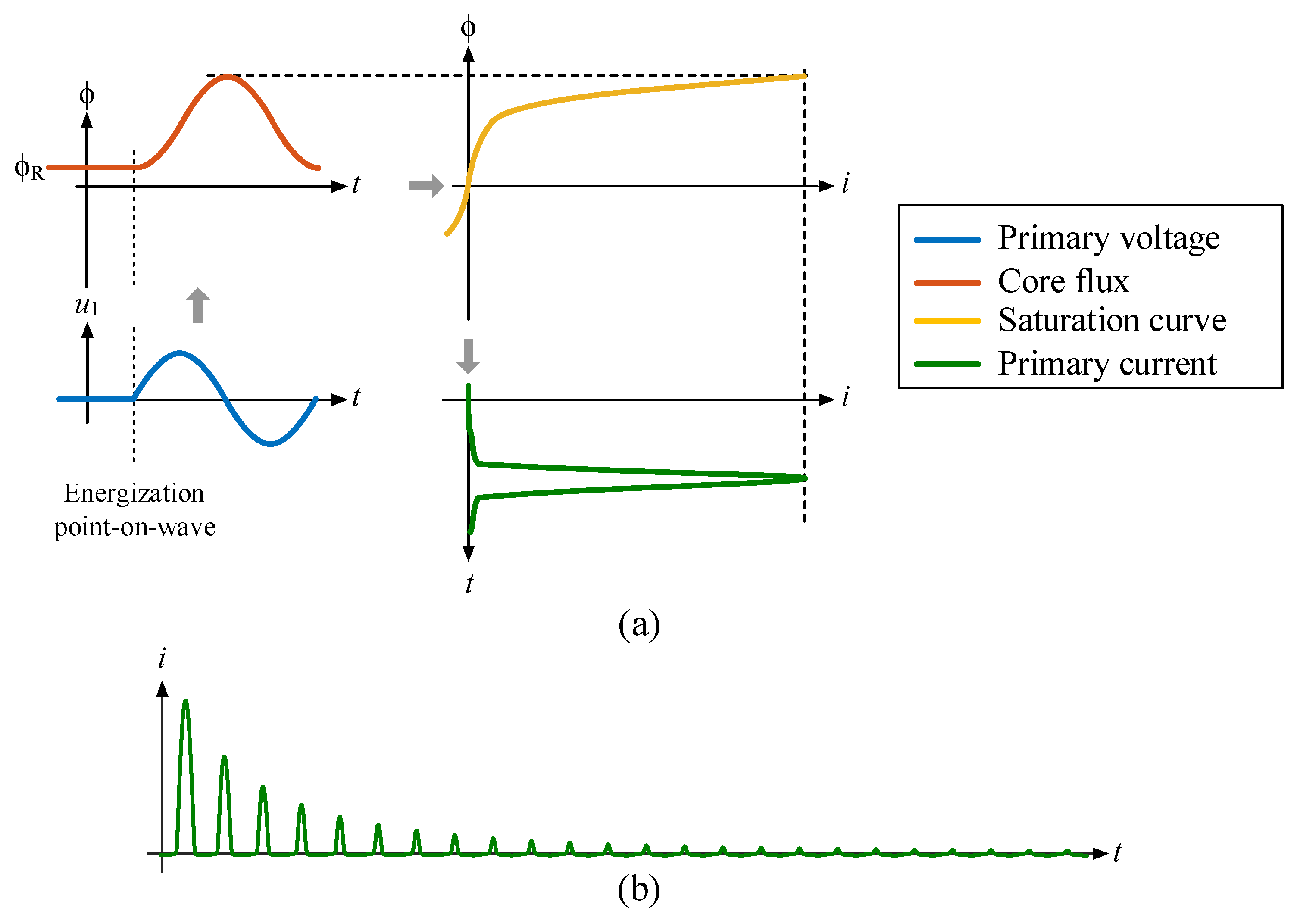

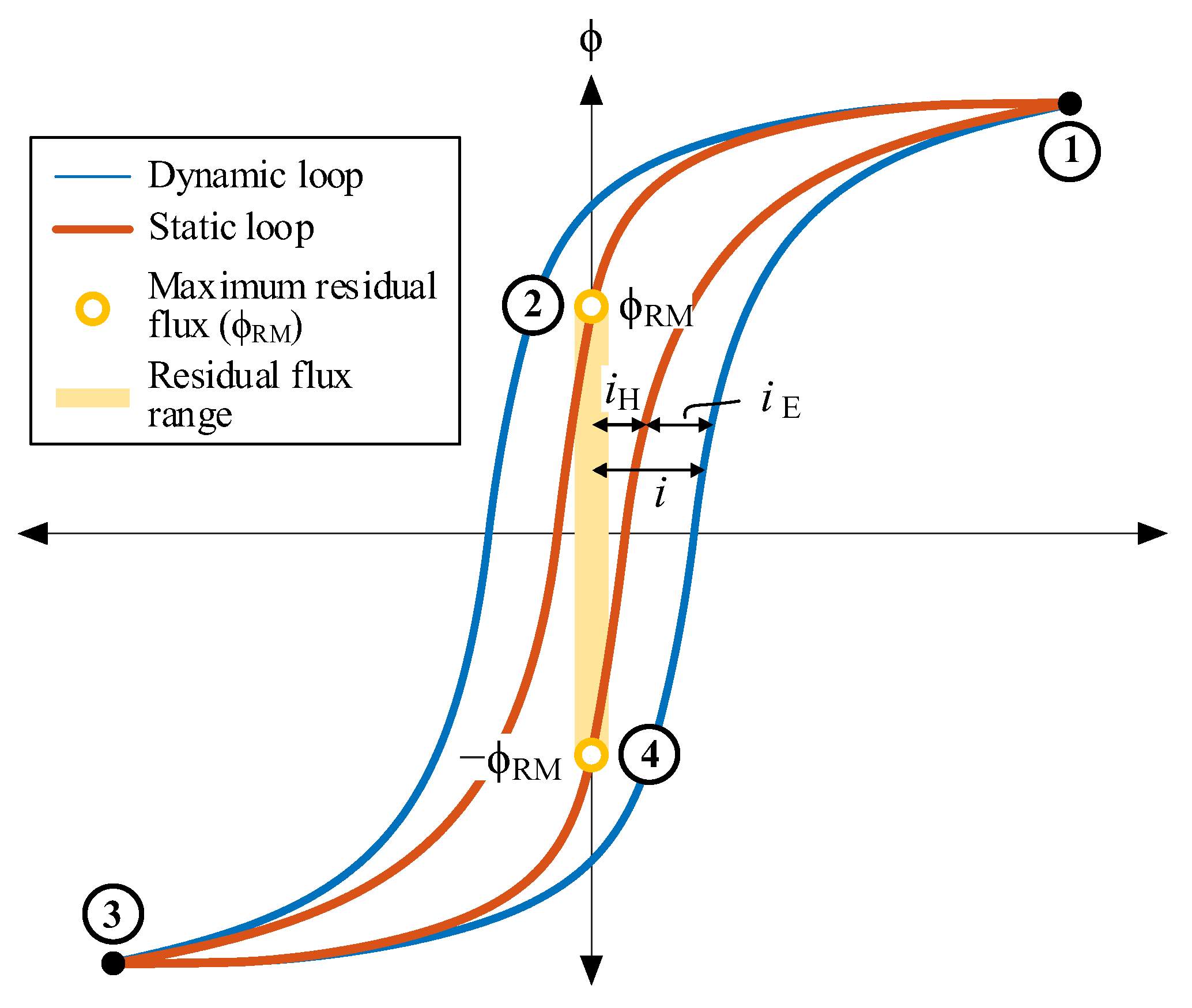

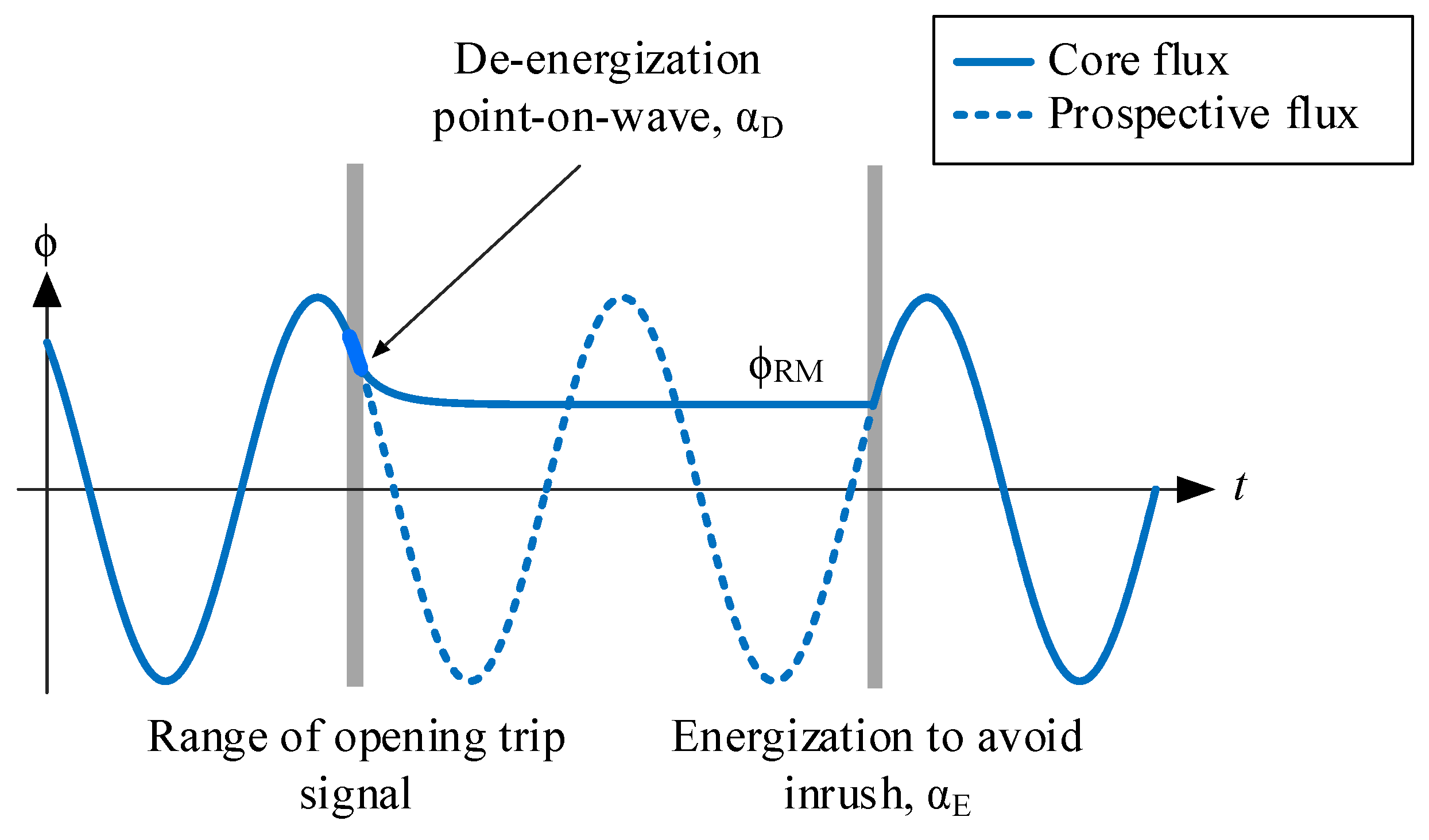

Inrush Current and Residual Flux

- -

- A static hysteresis loop (ϕ–iH, red line in Figure 3). This loop is a result of core magnetization and hysteresis losses and cannot be directly measured through the classical no-load test.

- -

- A dynamic loop (ϕ–i, blue line in Figure 3). This loop is directly measurable and comprises the static hysteresis loop plus the eddy losses.

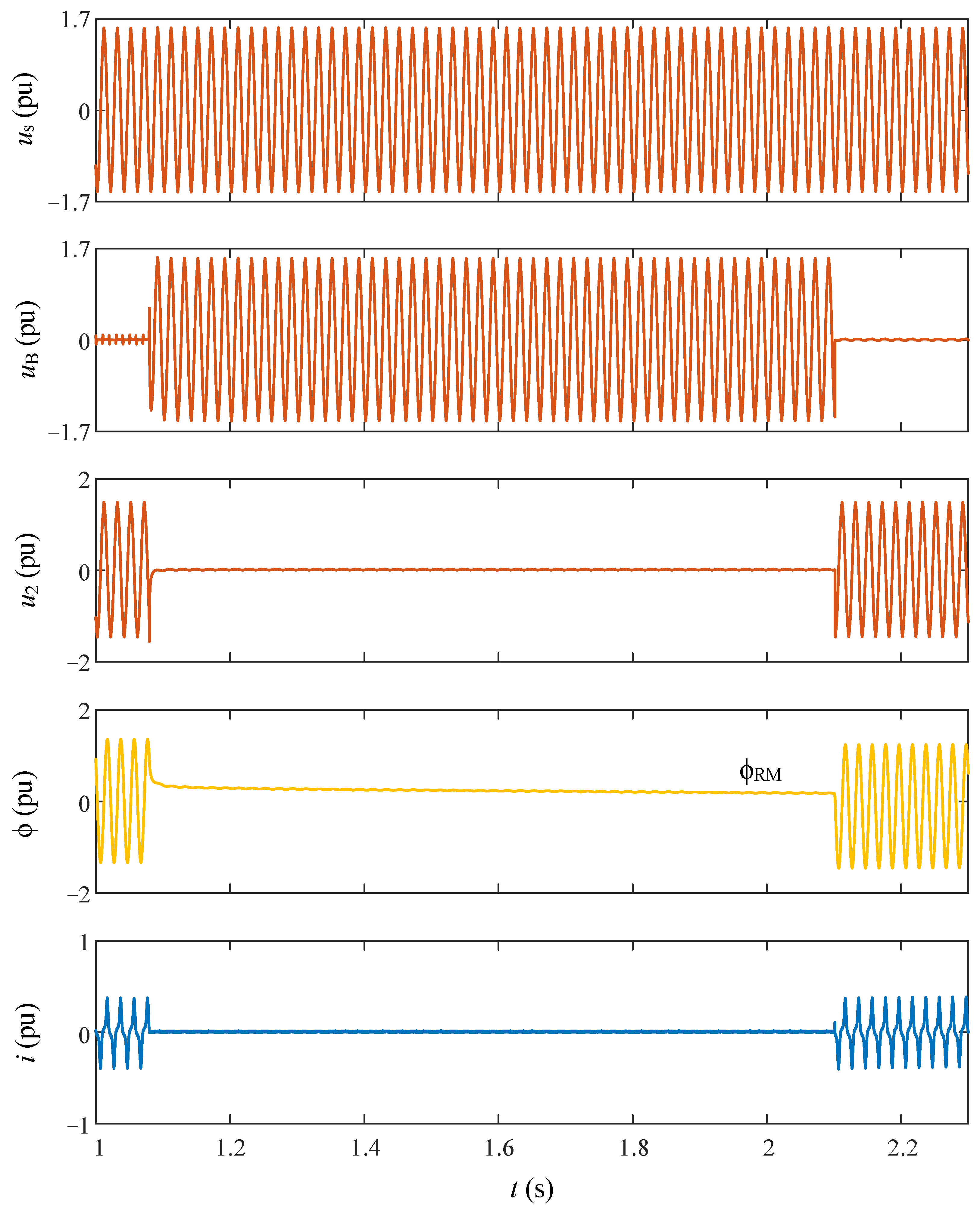

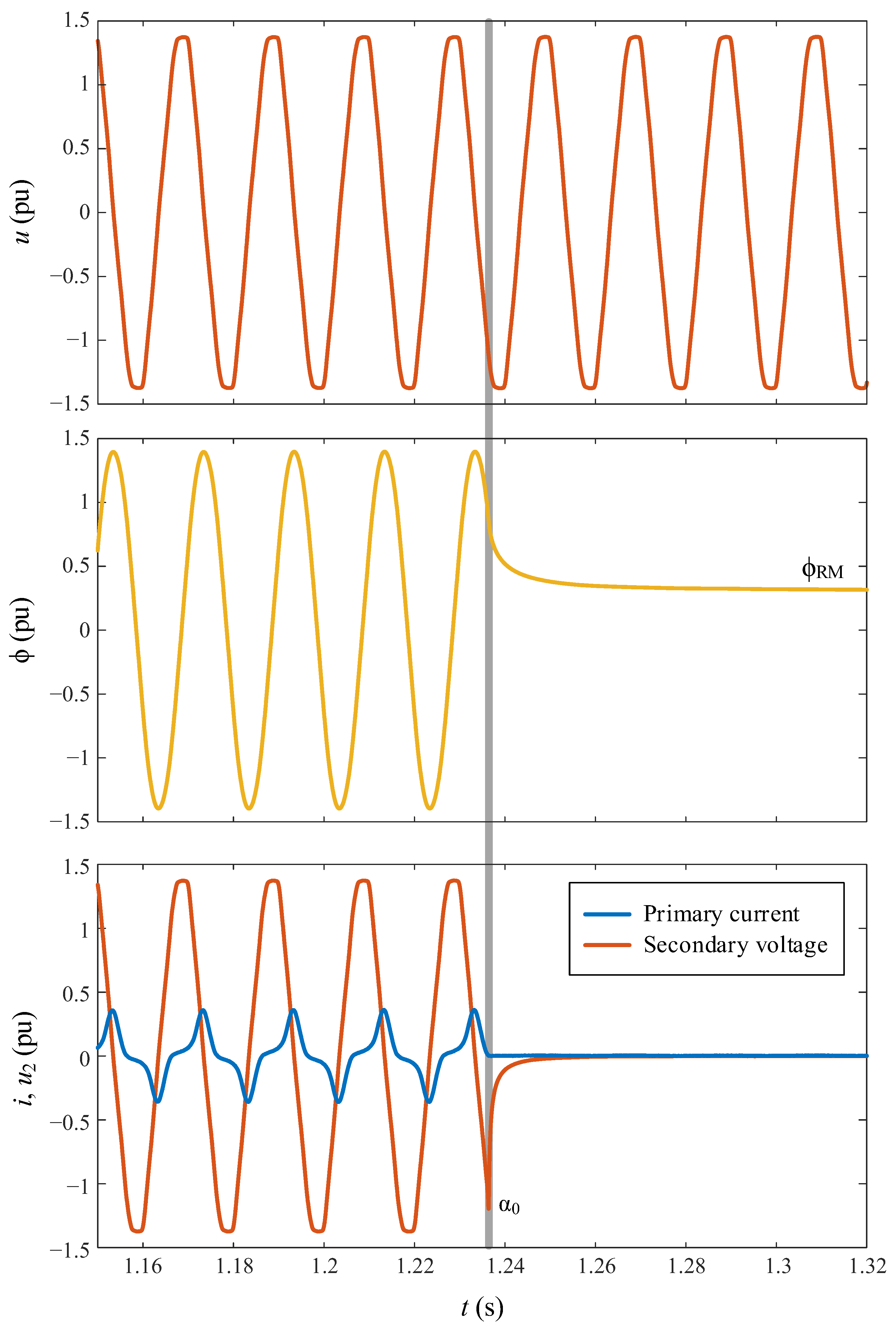

3. Optimizing Inrush Current Mitigation through Smart Switching

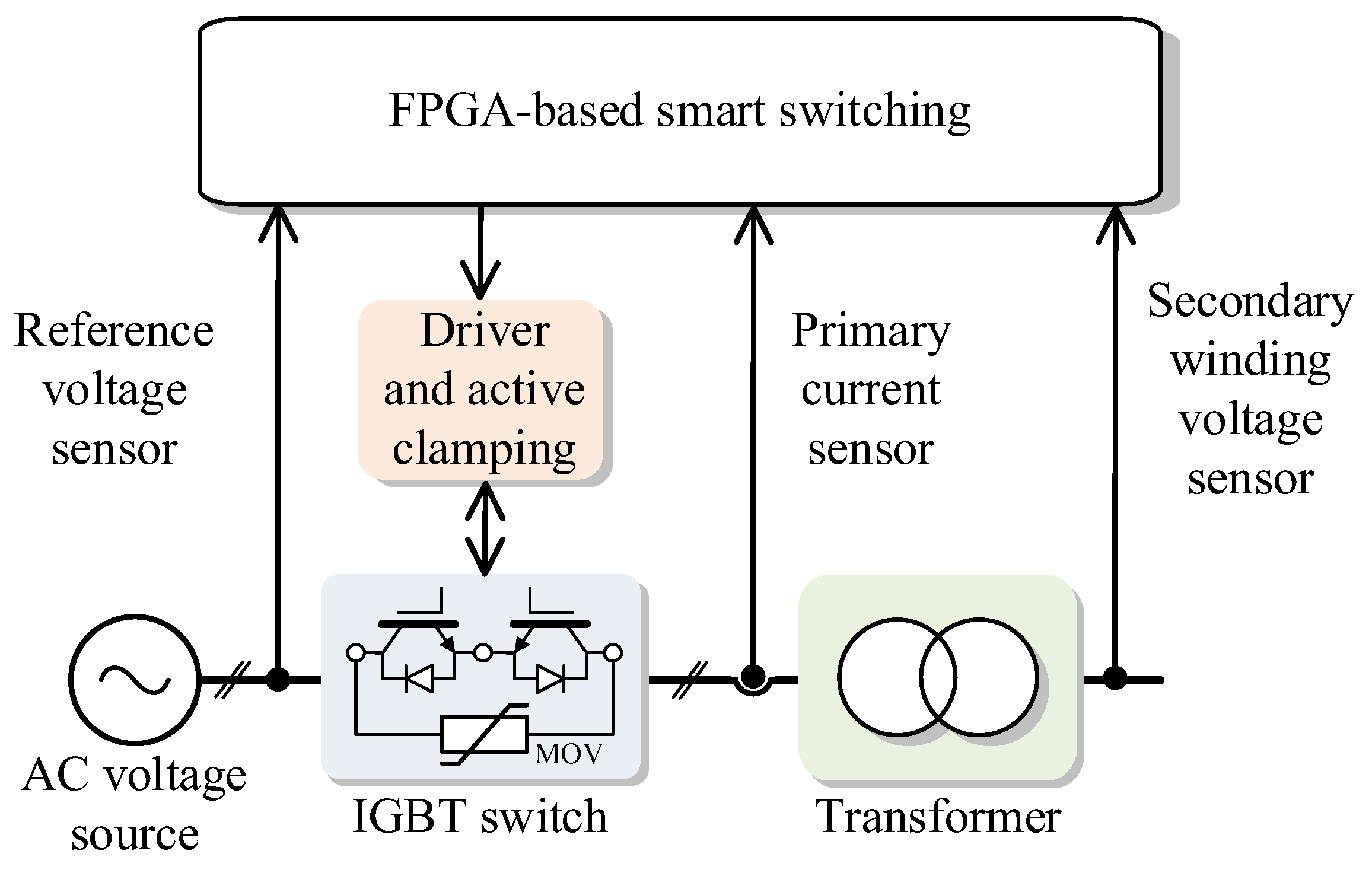

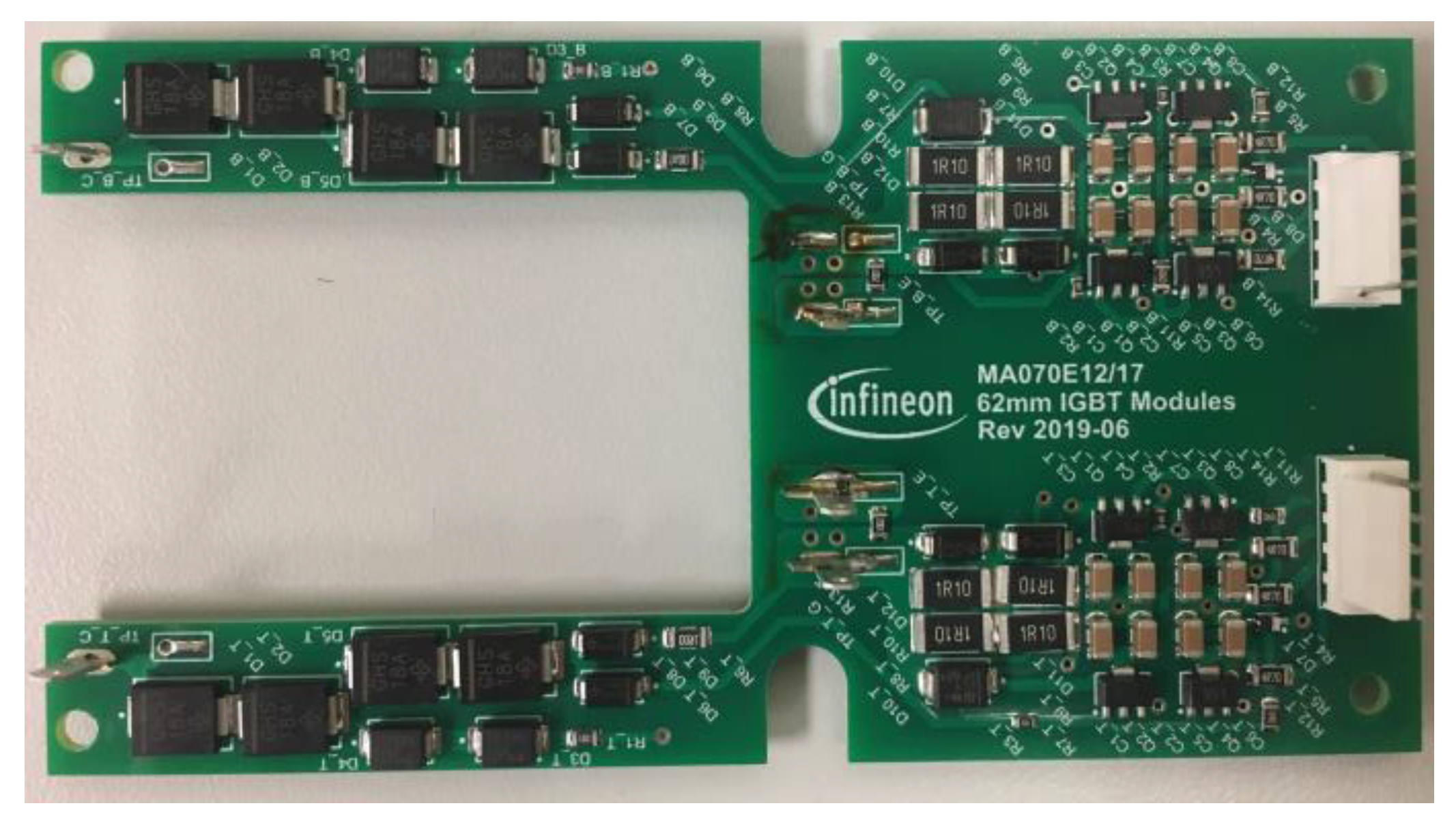

4. FPGA-Based Smart Switching Implementation

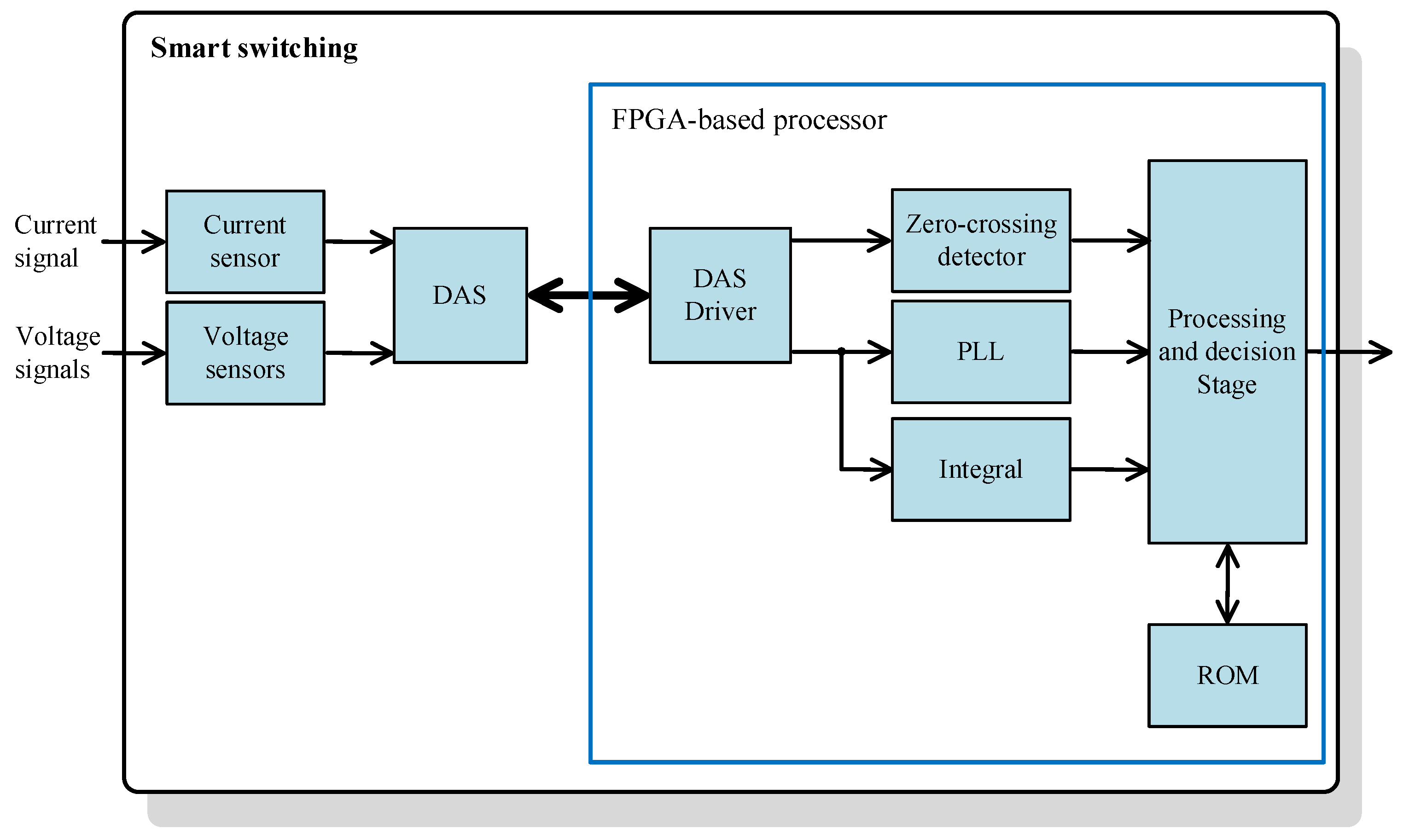

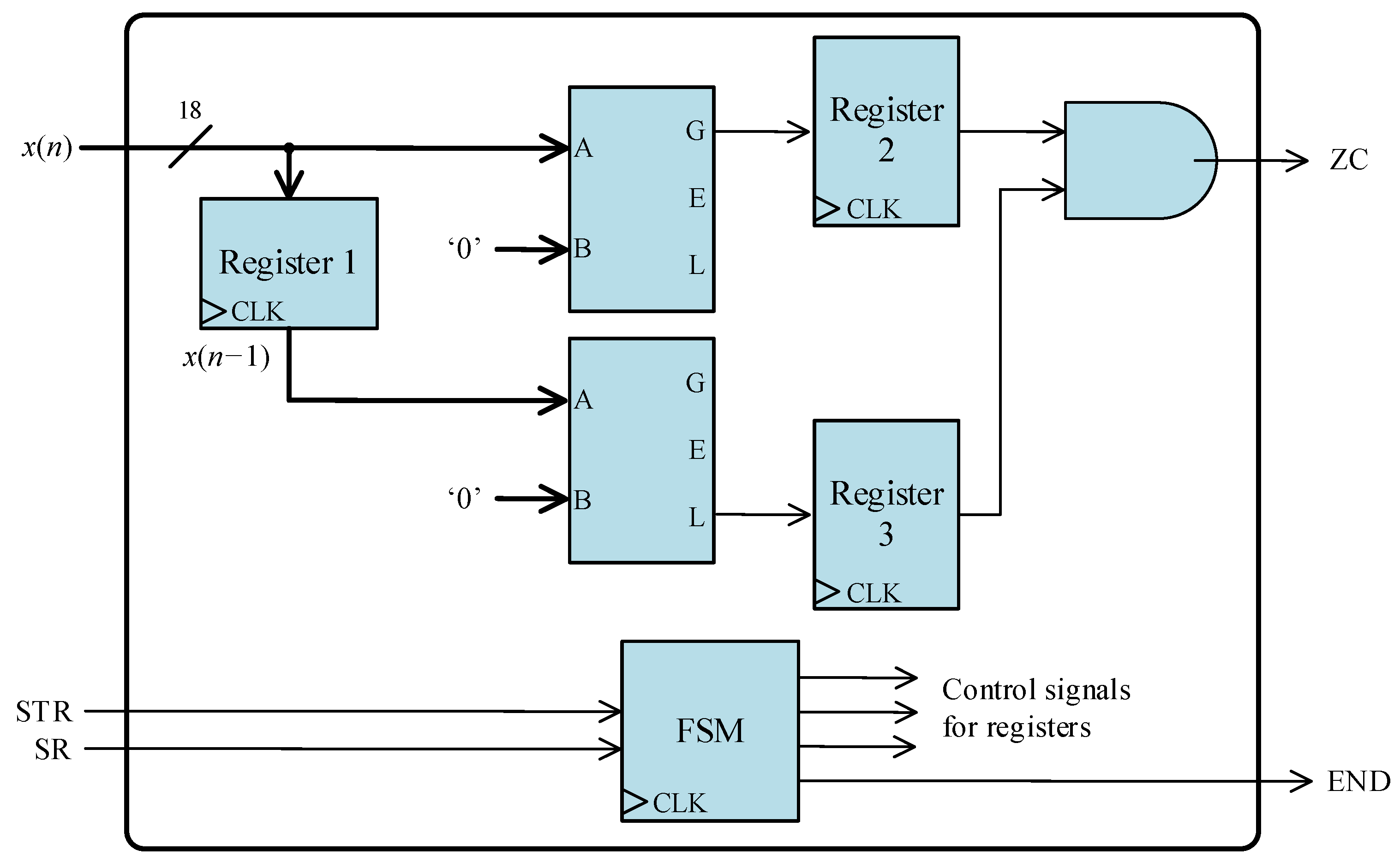

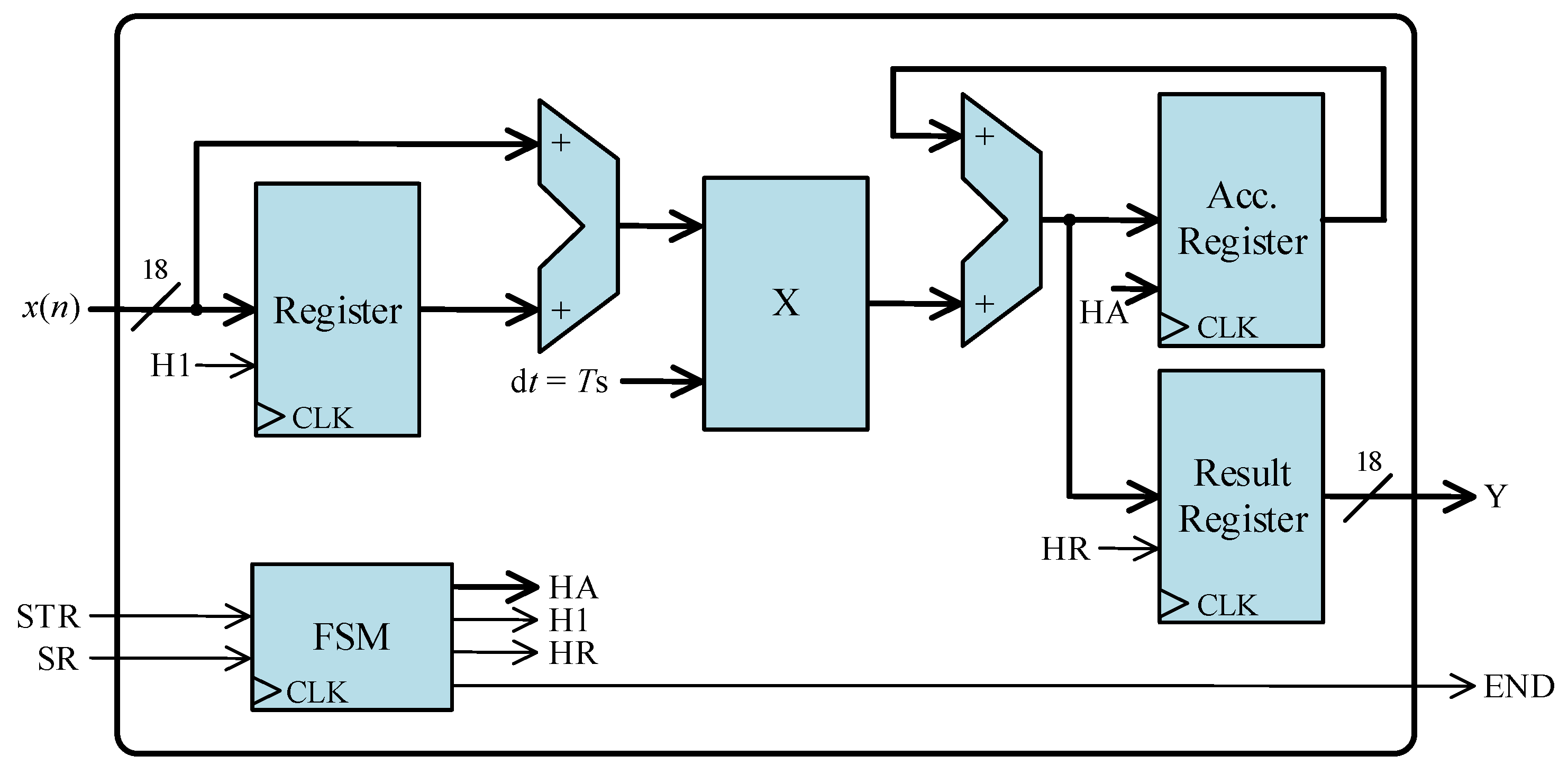

FPGA-Based Processor

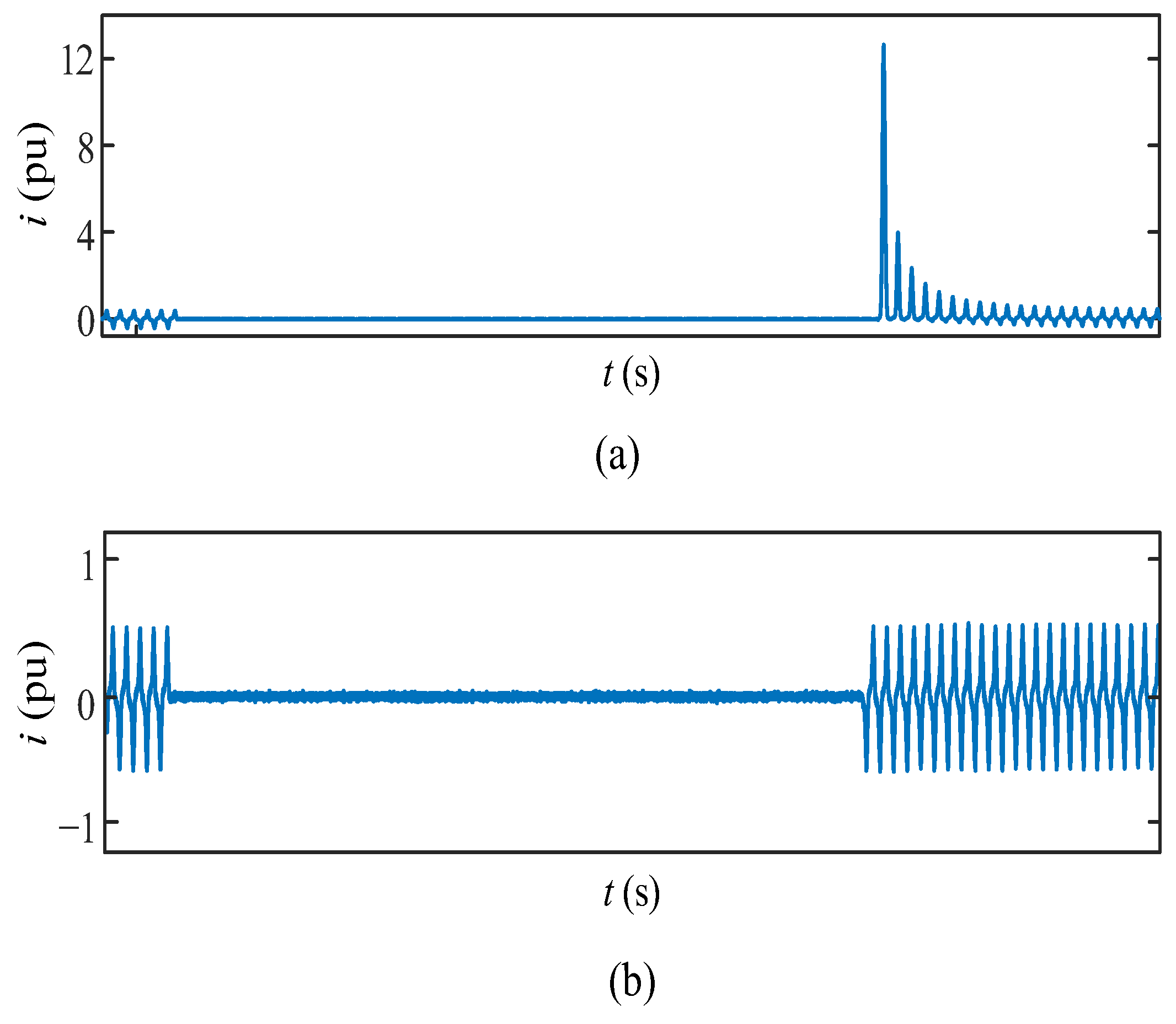

5. Experimental Results

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Trimberger, S.M.S. Three Ages of FPGAs: A Retrospective on the First Thirty Years of FPGA Technology. IEEE Solid. State Circuits Mag. 2018, 10, 16–29. [Google Scholar] [CrossRef]

- Rodríguez-Andina, J.J.; Valdés-Peña, M.D.; Moure, M.J. Advanced Features and Industrial Applications of FPGAs—A Review. IEEE Trans. Ind. Inform. 2015, 11, 853–864. [Google Scholar] [CrossRef]

- Elnawawy, M.; Farhan, A.; Al Nabulsi, A.; Al-Ali, A.; Sagahyroon, A. Role of FPGA in Internet of Things Applications. In Proceedings of the 2019 IEEE International Symposium on Signal Processing and Information Technology (ISSPIT), Ajman, United Arab Emirates, 10–12 December 2019; pp. 1–6. [Google Scholar]

- Hoozemans, J.; Peltenburg, J.; Nonnemacher, F.; Hadnagy, A.; Al-Ars, Z.; Hofstee, H.P. FPGA Acceleration for Big Data Analytics: Challenges and Opportunities. IEEE Circuits Syst. Mag. 2021, 21, 30–47. [Google Scholar] [CrossRef]

- Arenas, L.D.O.; Melo, G.D.A.E.; Canesin, C.A. A Methodology for Power Quantities Calculation Applied to an FPGA-Based Smart-Energy Meter. IEEE Trans. Instrum. Meas. 2021, 70, 9000711. [Google Scholar]

- Singh, H.R.; Mohanty, S.R.; Kishor, N.; Thakur, K.A. Real-Time Implementation of Signal Processing Techniques for Disturbances Detection. IEEE Trans. Ind. Electron. 2019, 66, 3550–3560. [Google Scholar] [CrossRef]

- Sahani, M.; Dash, P.K. FPGA-Based Online Power Quality Disturbances Monitoring Using Reduced-Sample HHT and Class-Specific Weighted RVFLN. IEEE Trans. Ind. Inform. 2019, 15, 4614–4623. [Google Scholar] [CrossRef]

- Martinez-Figueroa, G.D.J.; Morinigo-Sotelo, D.; Zorita-Lamadrid, A.L.; Morales-Velazquez, L.; Romero-Troncoso, R.D.J. FPGA-based smart sensor for detection and classification of power quality disturbances using higher order statistics. IEEE Access 2017, 5, 14259–14274. [Google Scholar] [CrossRef]

- Lopez-Ramirez, M.; Cabal-Yepez, E.; Ledesma-Carrillo, L.M.; Miranda-Vidales, H.; Rodriguez-Donate, C.; Lizarraga-Morales, R.A. FPGA-Based Online PQD Detection and Classification through DWT, Mathematical Morphology and SVD. Energies 2018, 11, 769. [Google Scholar] [CrossRef]

- Badar, J.; Ali, S.; Munir, H.M.; Bhan, V.; Bukhari, S.S.H.; Ro, J.-S. Reconfigurable Power Quality Analyzer Applied to Hardware-in-Loop Test Bench. Energies 2021, 14, 5134. [Google Scholar] [CrossRef]

- Huerta-Rosales, J.R.; Granados-Lieberman, D.; Garcia-Perez, A.; Camarena-Martinez, D.; Amezquita-Sanchez, J.P.; Valtierra-Rodriguez, M. Short-Circuited Turn Fault Diagnosis in Transformers by Using Vibration Signals, Statistical Time Features, and Support Vector Machines on FPGA. Sensors 2021, 21, 3598. [Google Scholar] [CrossRef]

- Alami, H.E.; Bossoufi, B.; Motahhir, S.; Alkhammash, E.H.; Masud, M.; Karim, M.; Taoussi, M.; Bouderbala, M.; Lamnadi, M.; El Mahfoud, M. FPGA in the Loop Implementation for Observer Sliding Mode Control of DFIG-Generators for Wind Turbines. Electronics 2022, 11, 116. [Google Scholar] [CrossRef]

- Sankar, D.; Syamala, L.; Chembathu Ayyappan, B.; Kallarackal, M. FPGA-Based Cost-Effective and Resource Optimized Solution of Predictive Direct Current Control for Power Converters. Energies 2021, 14, 7669. [Google Scholar] [CrossRef]

- Bao, Y.; Li, Y. FPGA-Based Design of Grid Friendly Appliance Controller. IEEE Trans. Smart Grid 2014, 5, 924–931. [Google Scholar] [CrossRef]

- Mirzahosseini, R.; Iravani, R. Small Time-Step FPGA-Based Real-Time Simulation of Power Systems Including Multiple Converters. IEEE Trans. Power Del. 2019, 34, 2089–2099. [Google Scholar] [CrossRef]

- Bai, H.; Luo, H.; Liu, C.; Paire, D.; Gao, F. A Device-Level Transient Modeling Approach for the FPGA-Based Real-Time Simulation of Power Converters. IEEE Trans. Power Electron. 2020, 35, 1282–1292. [Google Scholar] [CrossRef]

- Xu, J.; Wang, K.; Wu, P.; Li, G. FPGA-Based Sub-Microsecond-Level Real-Time Simulation for Microgrids with a Network-Decoupled Algorithm. IEEE Trans. Power Del. 2020, 35, 987–998. [Google Scholar] [CrossRef]

- Mitra, S.; Chattopadhyay, P. Design and implementation of flexible Numerical Overcurrent Relay on FPGA. Int. J. Electr. Power Energy Syst. 2019, 104, 797–806. [Google Scholar] [CrossRef]

- Maheshwari, V.; Das Devulapalli, B.; Saxena, A.K. FPGA-based digital overcurrent relay with concurrent sense-process-communicate cycles. Int. J. Electr. Power Energy 2014, 55, 66–73. [Google Scholar] [CrossRef]

- Wang, Y.; Dinavahi, V. Low-latency distance protective relay on FPGA. IEEE Trans. Smart Grid. 2013, 5, 896–905. [Google Scholar] [CrossRef]

- Jin, X.; Gokaraju, R.; Wierckx, R.; Nayak, O. High speed digital distance relaying scheme using FPGA and IEC 61850. IEEE Trans. Smart Grid 2018, 9, 4383–4393. [Google Scholar] [CrossRef]

- Sano, K.; Takasaki, M. A Surge less Solid-State DC Circuit Breaker for Voltage-Source-Converter Based HVDC Systems. IEEE Trans. Ind. Appl. 2014, 50, 2690–2699. [Google Scholar] [CrossRef]

- Liu, F.; Liu, W.; Zha, X. Solid-State Circuit Breaker Snubber Design for Transient Overvoltage Suppression at Bus Fault Interruption in Low-Voltage DC Microgrid. IEEE Trans. Power Electron. 2017, 32, 3007–3021. [Google Scholar] [CrossRef]

- Irfan, M.M.; Malaji, S.; Patsa, C.; Rangarajan, S.S.; Collins, R.E.; Senjyu, T. Online Learning-Based ANN Controller for a Grid-Interactive Solar PV System. Appl. Sci. 2021, 11, 8712. [Google Scholar] [CrossRef]

- Shanmugam, L.; Balasubramaniam, P.M.; Shnain, A.H.; Abdulkader, R.; Alharbi, M.; Pustokhin, D.A.; Pustokhina, I.V.; Mohammed, S.; Sengan, S. Solar-Powered LVDC Nano-Grid with Smart FPGA-based Residential Power Switching Algorithm. IEEE Access 2023. early access. [Google Scholar] [CrossRef]

- Youssef, A.; El Telbany, M.; Zekry, A. Reconfigurable generic FPGA implementation of fuzzy logic controller for MPPT of PV systems. Renew. Sustain. Energy Rev. 2018, 82, 1313–1319. [Google Scholar] [CrossRef]

- Ricco, M.; Manganiello, P.; Monmasson, E.; Petrone, G.; Spagnuolo, G. FPGA-based implementation of dual Kalman filter for PV MPPT applications. IEEE Trans. Ind. Inform. 2015, 13, 176–185. [Google Scholar] [CrossRef]

- Nagpal, M.; Martinich, T.G.; Moshref, A.; Morison, K.; Kundur, P. Assessing and limiting impact of transformer inrush current on power quality. IEEE Trans. Power Deliv. 2006, 21, 890–896. [Google Scholar] [CrossRef]

- Steurer, M.; Frohlich, K. The impact of inrush currents on the mechanical stress of high voltage power transformer coils. IEEE Trans. Power Deliv. 2002, 17, 155–160. [Google Scholar] [CrossRef]

- Mikhak-Beyranvand, M.; Rezaeealam, B.; Faiz, J.; Rezaei-Zare, A. Impacts of ferroresonance and inrush current forces on transformer windings. IET Electr. Power Appl. 2019, 13, 914–921. [Google Scholar] [CrossRef]

- Tajdinian, M.; Samet, H. Application of probabilistic distance measures for inrush and internal fault currents discrimination in power transformer differential protection. Electr. Power Syst. Res. 2021, 193, 107012. [Google Scholar] [CrossRef]

- Abbaszadeh, A.; Abedi, M.; Doustmohammadi, A.; Ebrahimi, M.R. Arrester thermal stability control: Implementing a combination of countermeasures during power system restoration: A real case study. IEEE Syst. J. 2019, 13, 3223–3232. [Google Scholar] [CrossRef]

- Lennerhag, O.; Bollen, M.H.J. Impact of uncertainties on resonant overvoltages following transformer energization. Electr. Power Syst. Res. 2020, 187, 106503. [Google Scholar] [CrossRef]

- Turner, R.A.; Smith, K.S. Resonance excited by transformer inrush current in inter-connected offshore power systems. In Proceedings of the 2008 IEEE Industry Applications Society Annual Meeting, Edmonton, AB, Canada, 5–9 October 2008. [Google Scholar]

- Mo, C.; Ji, T.Y.; Zhang, L.L.; Wu, Q.H. Equivalent statistics based inrush identification method for differential protection of power transformer. Electr. Power Syst. Res. 2022, 203, 107664. [Google Scholar] [CrossRef]

- Samet, H.; Shadaei, M.; Tajdinian, M. Statistical discrimination index founded on rate of change of phase angle for immunization of transformer differential protection against inrush current. Int. J. Electr. Power Energy Syst. 2022, 134, 107381. [Google Scholar] [CrossRef]

- Ruhan, Z.; Mansor, N.N.B.; Illias, H.A. Identification of Inrush Current Using a GSA-BP Network. Energies 2023, 16, 2340. [Google Scholar] [CrossRef]

- Ni, H.; Fang, S.; Lin, H. A simplified phase-controlled switching strategy for inrush current reduction. IEEE Trans. Power Del. 2021, 36, 215–222. [Google Scholar] [CrossRef]

- Wang, Y.; Yin, X.; Qiao, J.; Tan, L.; Xu, W. Inrush current suppression technology for floating nuclear power plants based on connecting Pre-T in series. Int. J. Electr. Power Energy Syst. 2022, 135, 107508. [Google Scholar] [CrossRef]

- Shahparasti, M.; Laaksonen, H.; Kauhaniemi, K.; Lauttamus, P.; Strandberg, S.; Strandberg, J. Inrush current management during medium voltage microgrid black start with battery energy storage system. IEEE Access. 2022, 10, 42287–42296. [Google Scholar] [CrossRef]

- Singh, G.; McGuinness, S.; Miller, C.; Stephens, M.; McGranaghan, M. Effects of PV transformer energization on power quality. In Proceedings of the 18th International Conference on Harmonics and Quality of Power (ICHQP), Ljubljana, Slovenia, 13–16 May 2018. [Google Scholar]

- Rane, M.; Wagh, S. Stability enhancement of transformered PV system using inrush mitigation techniques. In Proceedings of the 2017 North American Power Symposium (NAPS), Morgantown, WV, USA, 17–19 September 2017. [Google Scholar]

- Ahmed, A.A.; Abdelsalam, H.A. Mitigation of transformer-energizing inrush current using grid-connected photovoltaic system. Int. J. Electr. Power Energy Syst. 2016, 79, 312–321. [Google Scholar] [CrossRef]

- Balvet, V. Combining Controlled Switching and Flux Conditioning to Eliminate the Voltage Dips When Energizing the Step-Up Transformer of Renewables and Distributed Energy Resources. In Proceedings of the Cigre Canada Conference, Toronto, ON, Canada, 25–28 October 2021. [Google Scholar]

- Chen, H.C.; Wu, P.H.; Cheng, P.T. A transformer inrush reduction technique for low-voltage ride-through operation of renewable converters. IEEE Trans. Ind. Appl. 2016, 52, 2467–2474. [Google Scholar] [CrossRef]

- Bertotti, G. General properties of power losses in soft ferromagnetic materials. IEEE Trans. Magn. 1988, 24, 621–630. [Google Scholar] [CrossRef]

- Sima, W.; Peng, D.; Yang, M.; Liu, Y.; Duan, P.; Deng, J.; Qian, H. Low-frequency model for single-phase transformers based on the three-component Preisach model considering deep saturation. Int. J. Electr. Power Energy Syst. 2019, 110, 107–117. [Google Scholar] [CrossRef]

- Lotfi, A.; Høidalen, H.K.; Agheb, E.; Nysveen, A. Characterization of Magnetic Losses in the Transformer Tank Steel. IEEE Trans. Magn. 2016, 52, 1–4. [Google Scholar] [CrossRef]

- Wang, Y.; Liu, Z. Estimation Model of Core Loss Under DC Bias. IEEE Trans. Appl. Supercond. 2016, 26, 1–5. [Google Scholar] [CrossRef]

- Martínez-Figueroa, G.d.J.; Bogarra, S.; Córcoles, F. Smart Switching in Single-Phase Grid-Connected Photovoltaic Power Systems for Inrush Current Elimination. Energies 2023, 16, 7211. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Martínez-Figueroa, G.d.J.; Córcoles, F.; Bogarra, S. Field Programmable Gate Array-Based Smart Switch to Avoid Inrush Current in PV Installations. Sensors 2024, 24, 1121. https://doi.org/10.3390/s24041121

Martínez-Figueroa GdJ, Córcoles F, Bogarra S. Field Programmable Gate Array-Based Smart Switch to Avoid Inrush Current in PV Installations. Sensors. 2024; 24(4):1121. https://doi.org/10.3390/s24041121

Chicago/Turabian StyleMartínez-Figueroa, Gerardo de J., Felipe Córcoles, and Santiago Bogarra. 2024. "Field Programmable Gate Array-Based Smart Switch to Avoid Inrush Current in PV Installations" Sensors 24, no. 4: 1121. https://doi.org/10.3390/s24041121

APA StyleMartínez-Figueroa, G. d. J., Córcoles, F., & Bogarra, S. (2024). Field Programmable Gate Array-Based Smart Switch to Avoid Inrush Current in PV Installations. Sensors, 24(4), 1121. https://doi.org/10.3390/s24041121