Design of Ultra-Wideband Doherty Power Amplifier Using a Modified Combiner Integrated with Complex Combining Impedance

Abstract

1. Introduction

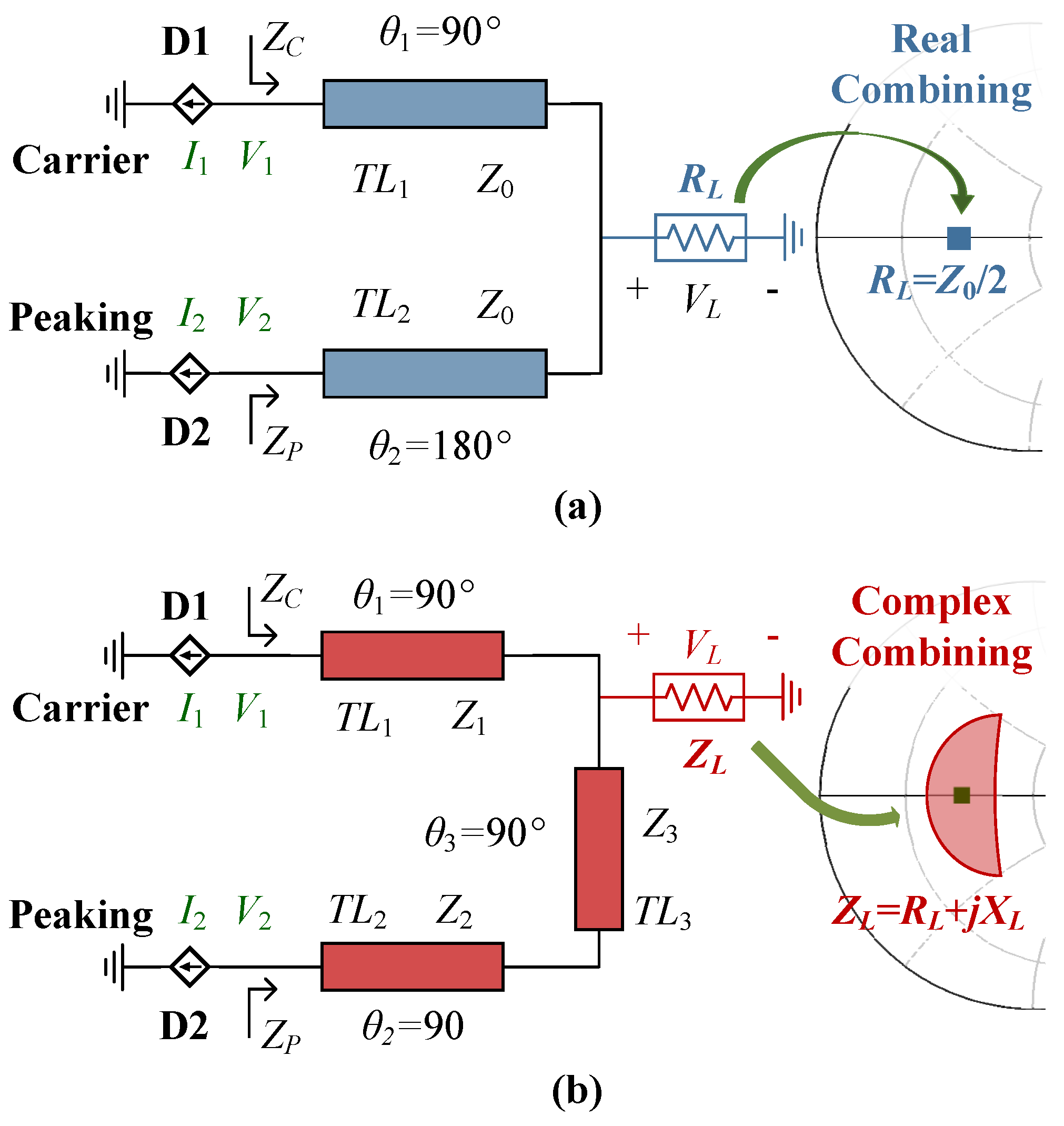

2. Modified Doherty Combiner Integrated with Complex Combining Impedance

2.1. General Equations

2.2. Analysis of the Modified Doherty Combiner

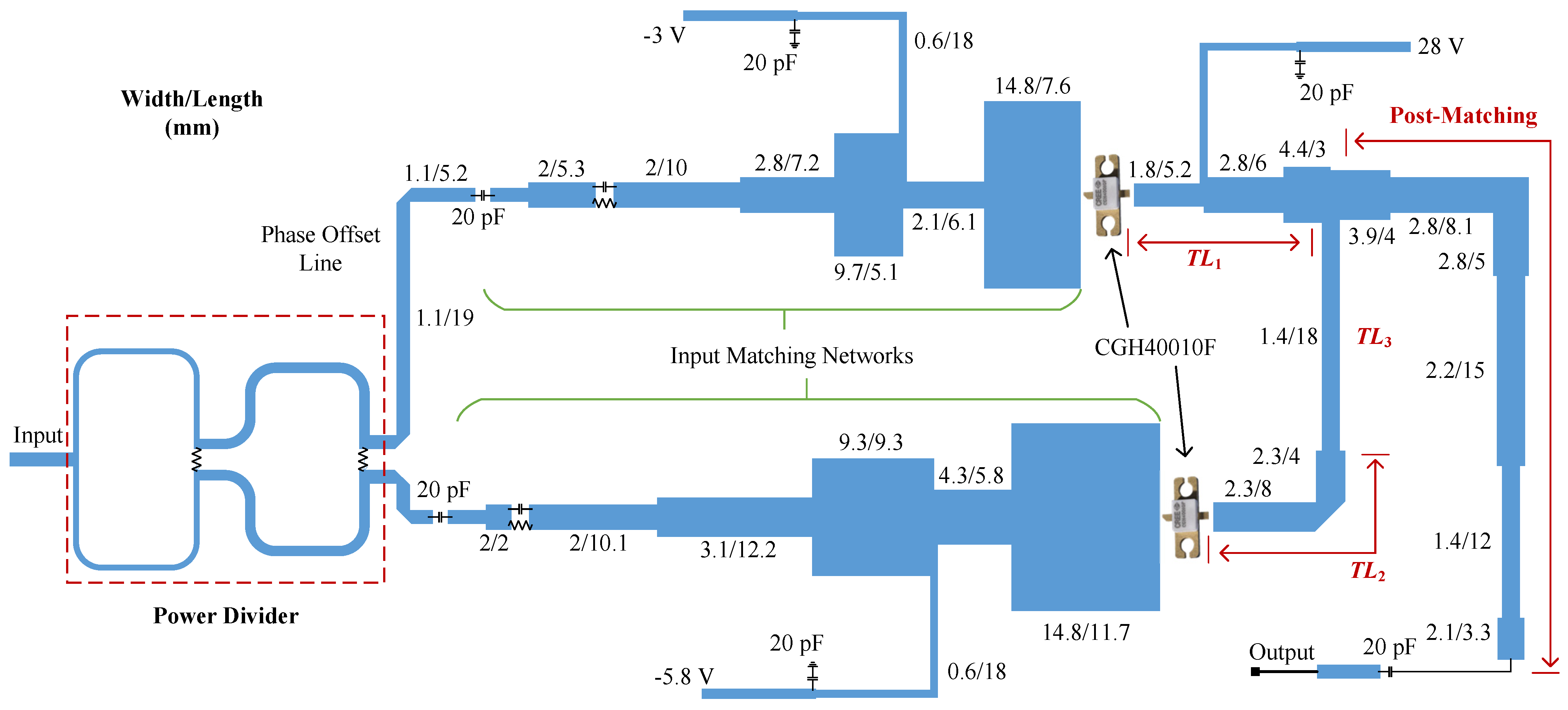

3. Design and Simulation of a Broadband DPA

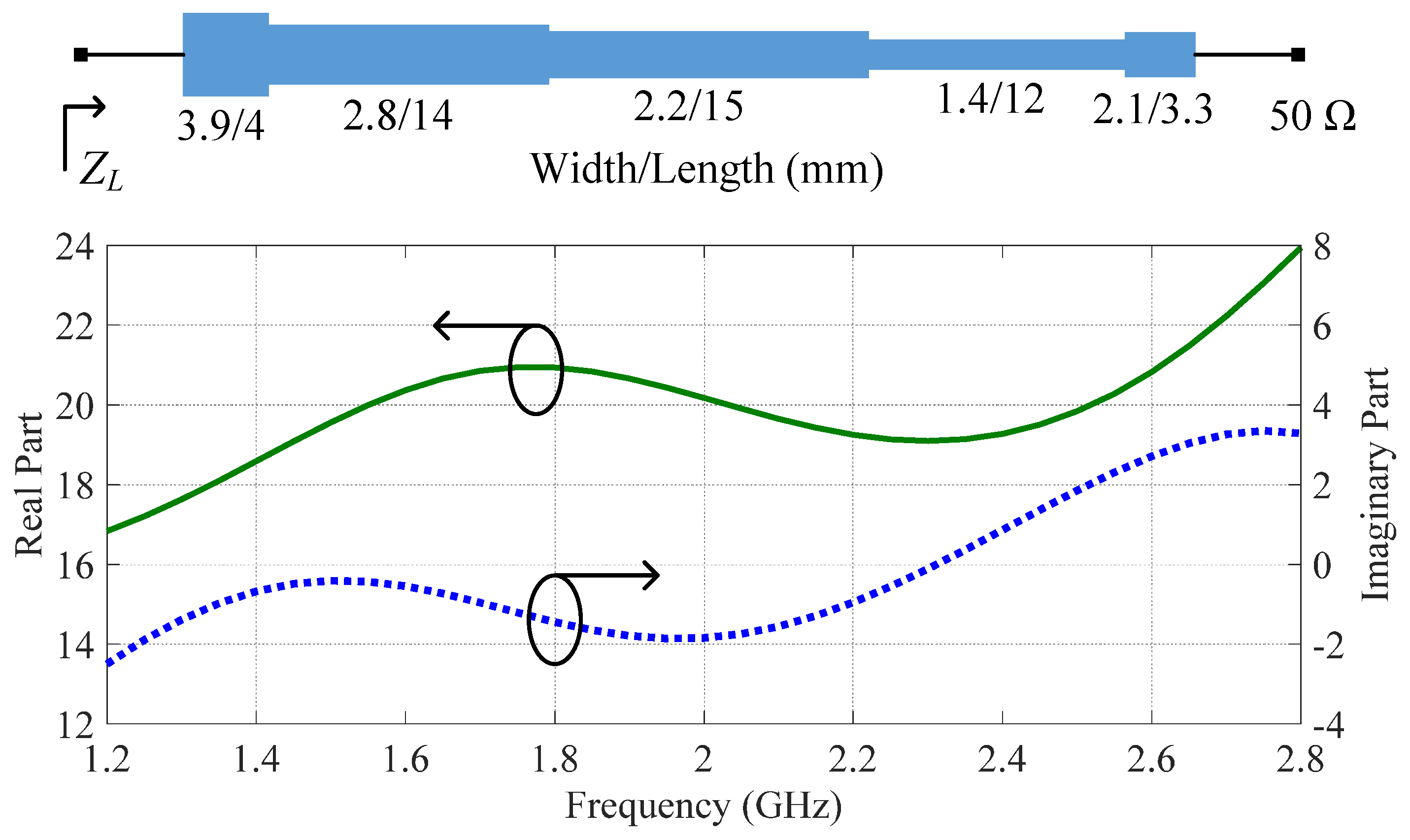

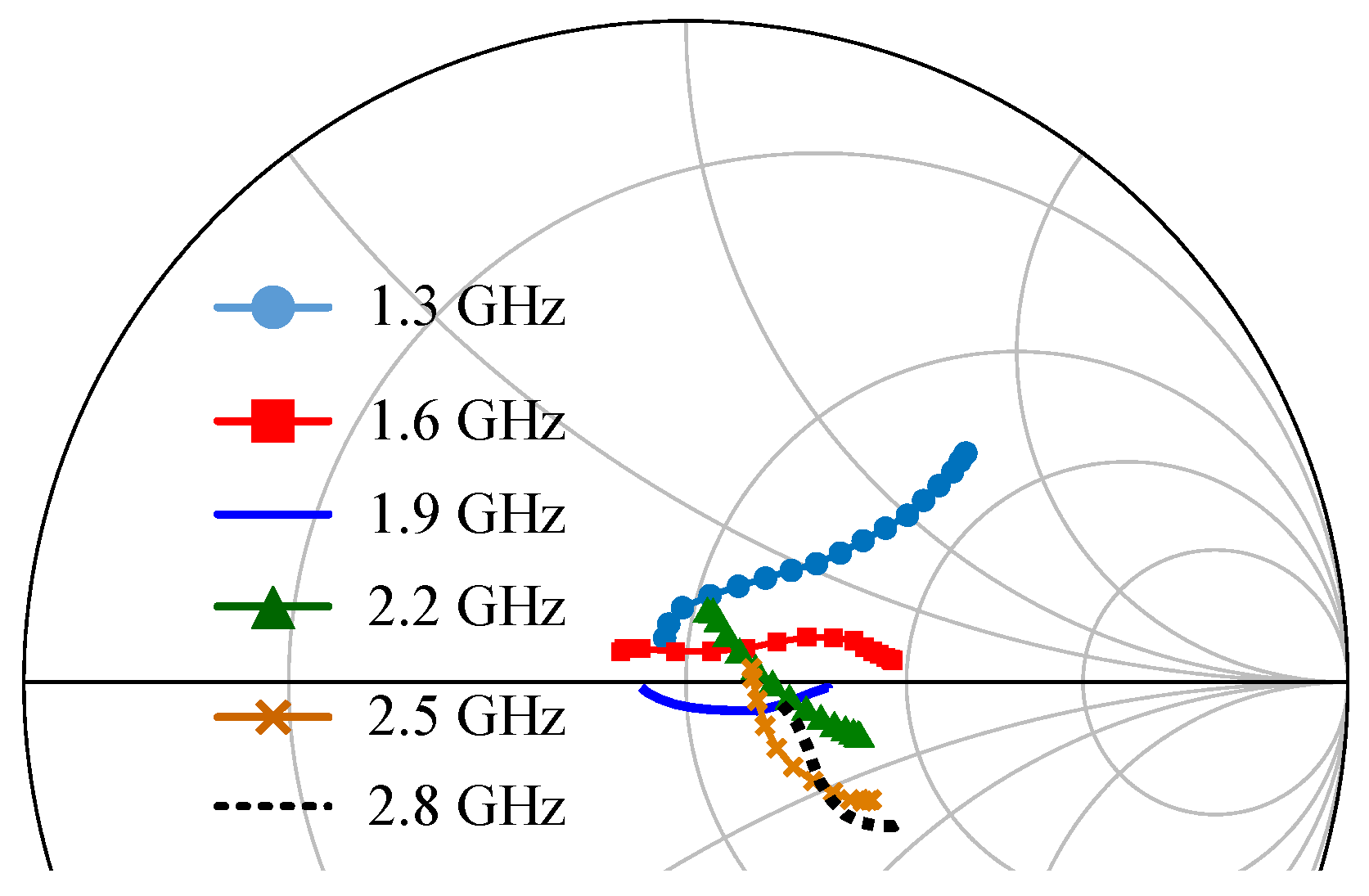

3.1. Design

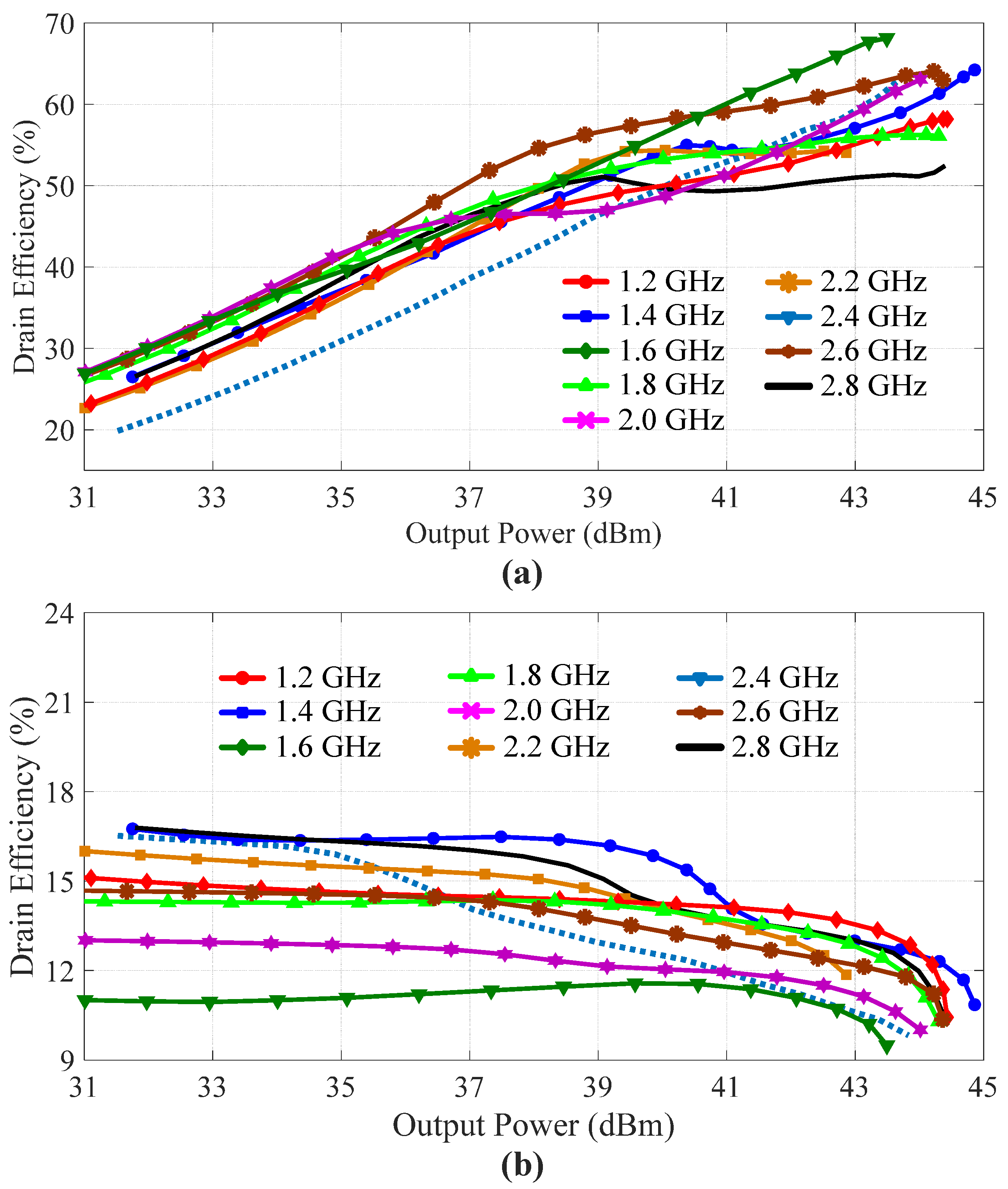

3.2. Simulation

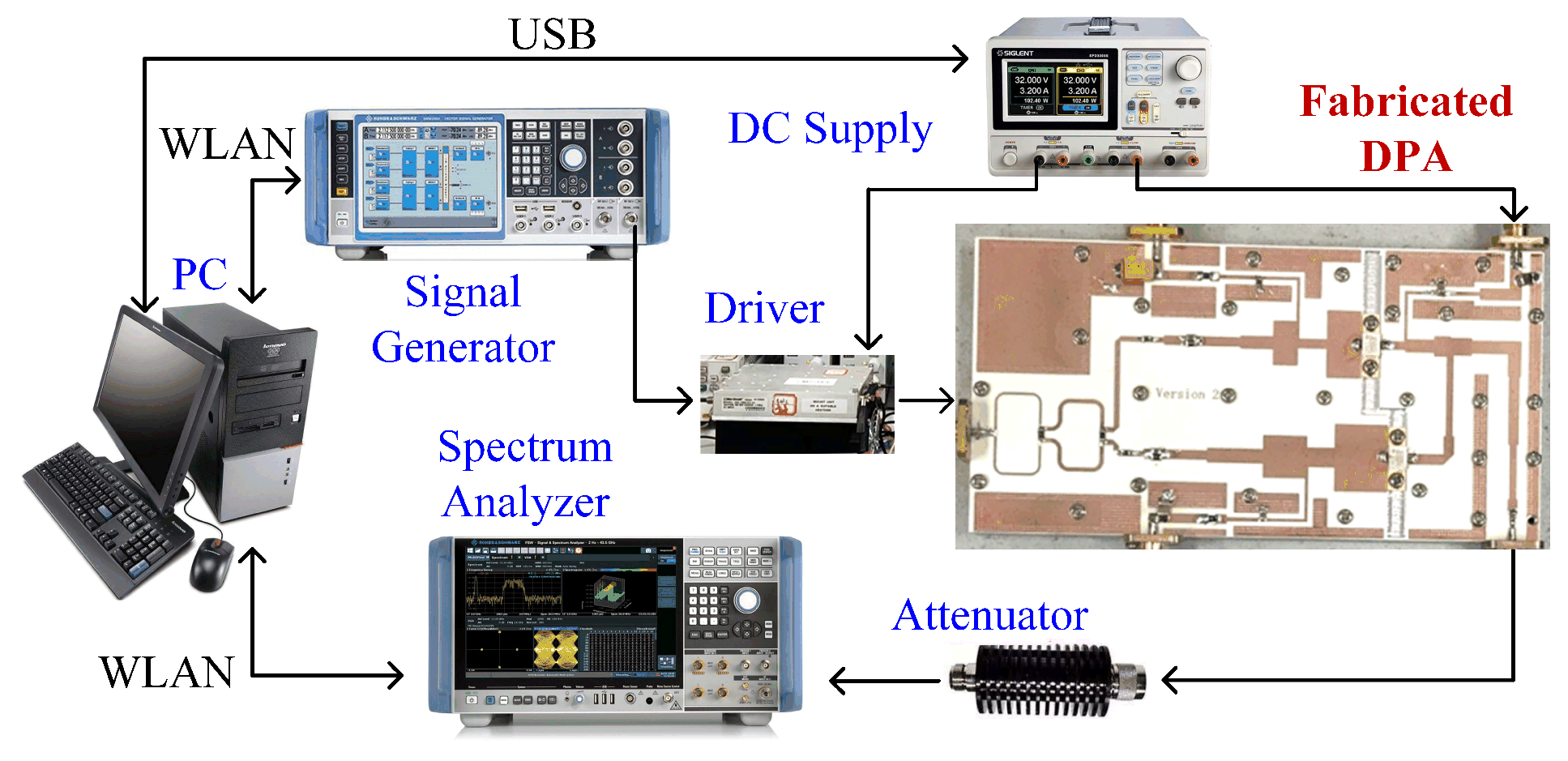

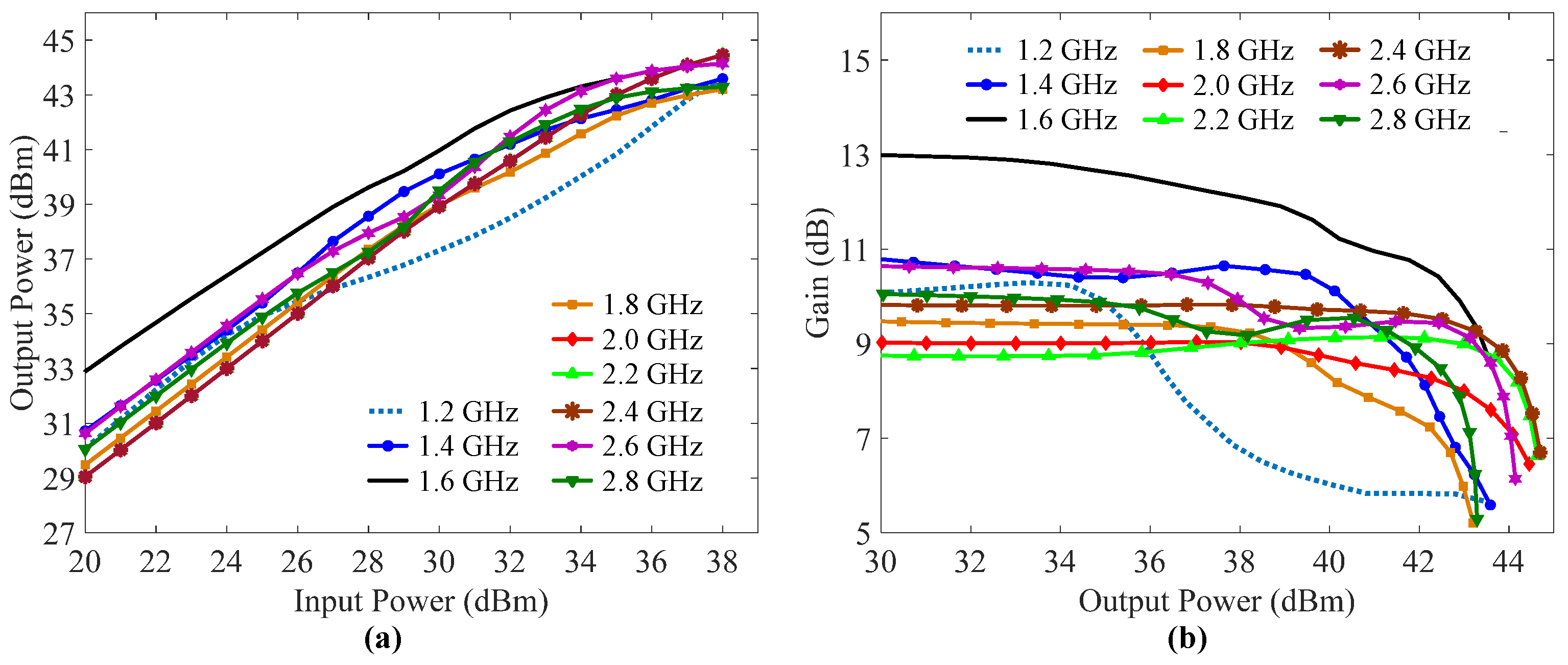

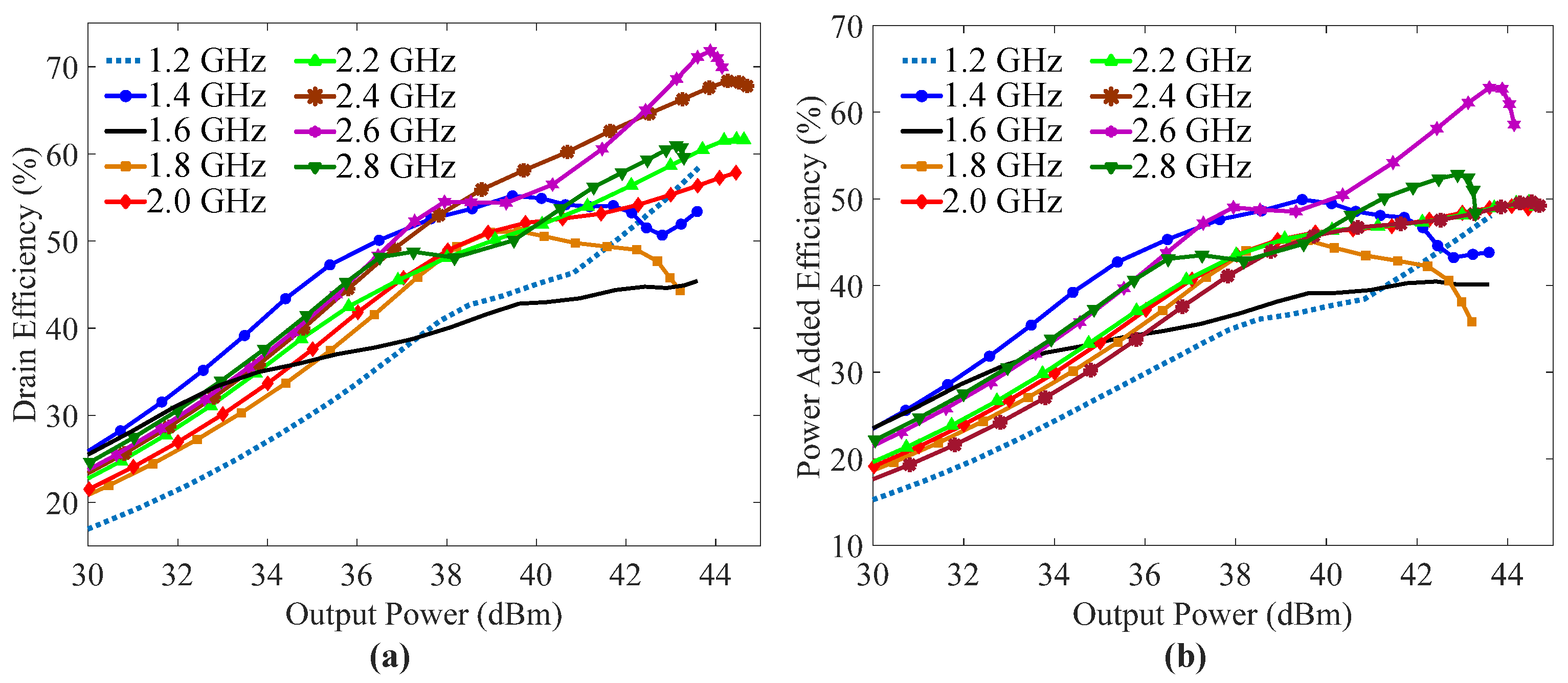

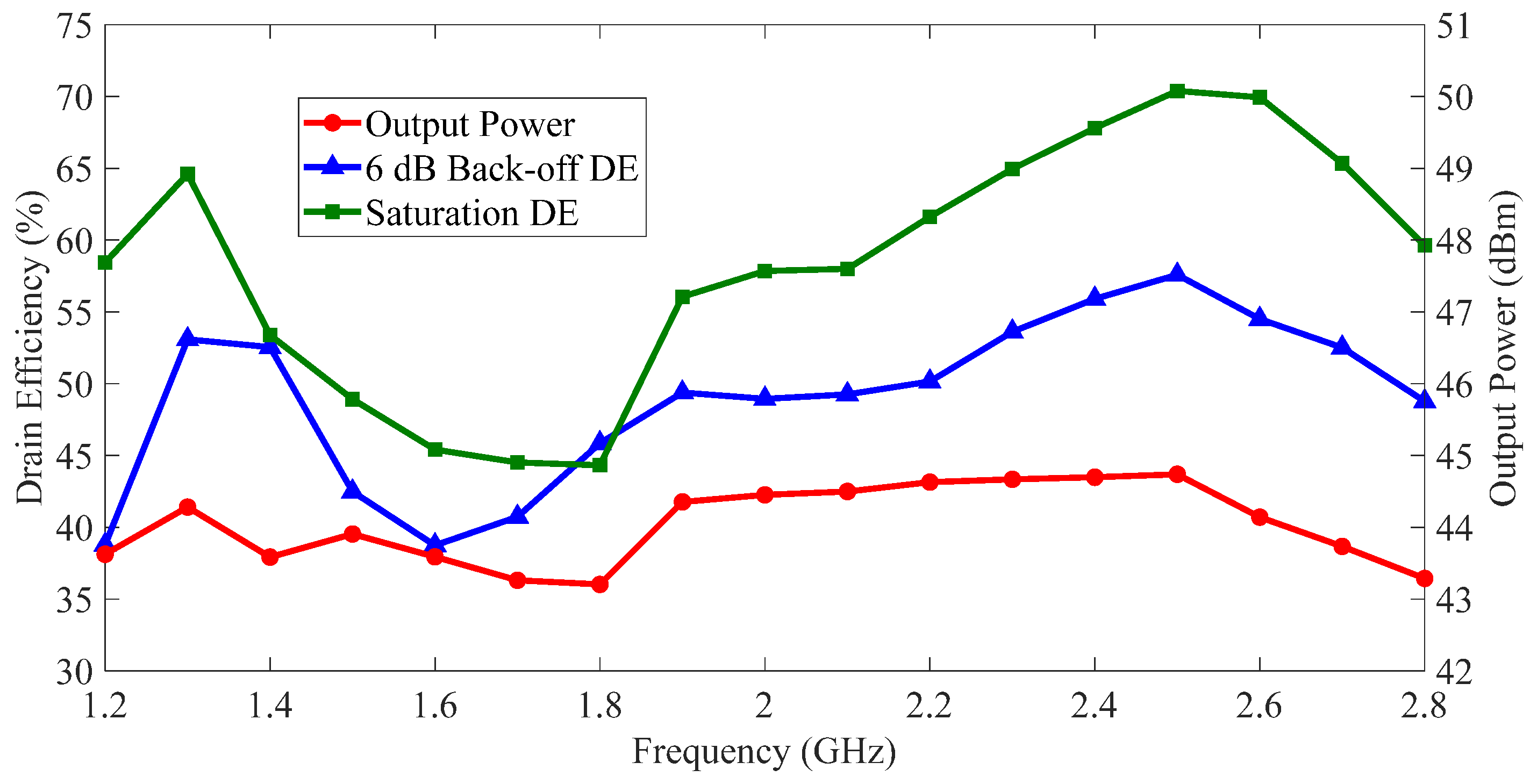

4. Experimental Results

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Mengozzi, M.; Gibiino, G.P.; Angelotti, A.M.; Santarelli, A.; Florian, C.; Colantonio, P. Automatic optimization of input split and bias voltage in digitally controlled dual-input Doherty RF PAs. Energies 2022, 15, 4892. [Google Scholar] [CrossRef]

- Ghosh, A.; Maeder, A.; Baker, M.; Chandramouli, D. 5G evolution: A view on 5G cellular technology beyond 3GPP release 15. IEEE Access 2019, 7, 127639–127651. [Google Scholar] [CrossRef]

- Qi, T.; He, S. Power up potential power amplifier technologies for 5G applications. IEEE Microw. Mag. 2019, 20, 89–101. [Google Scholar] [CrossRef]

- Popovic, Z. Amping up the PA for 5G: Efficient GaN power amplifiers with dynamic supplies. IEEE Microw. Mag. 2017, 18, 137–149. [Google Scholar] [CrossRef]

- Nasri, A.; Estebsari, M.; Toofan, S.; Piacibello, A.; Pirola, M.; Camarchia, V.; Ramella, C. Design of a wideband Doherty power amplifier with high efficiency for 5G application. Electronics 2021, 10, 873. [Google Scholar] [CrossRef]

- Ramella, C.; Piacibello, A.; Quaglia, R.; Camarchia, V.; Pirola, M. High efficiency power amplifiers for modern mobile communications: The load-modulation approach. Electronics 2017, 6, 96. [Google Scholar] [CrossRef]

- Martin, D.N.; Barton, T.W. Inphasing signal component separation for an X-Band Outphasing power amplifier. IEEE Trans. Microw. Theory Tech. 2021, 69, 1661–1674. [Google Scholar] [CrossRef]

- Choi, H. A Doherty power amplifier for ultrasound instrumentation. Sensors 2023, 23, 2406. [Google Scholar] [CrossRef]

- Lotfi, S.; Roshani, S.; Roshani, S.; Shirzadian Gilan, M. A planner Doherty power amplifier with harmonic suppression with open and short ended stubs. Frequenz 2022, 76, 121–130. [Google Scholar] [CrossRef]

- Bathich, K.; Markos, A.Z.; Boeck, G. Frequency response analysis and bandwidth extension of the Doherty amplifier. IEEE Trans. Microw. Theory Tech. 2011, 59, 934–944. [Google Scholar] [CrossRef]

- Cidronali, A.; Maddio, S.; Giovannelli, N.; Collodi, G. Frequency analysis and multiline implementation of compensated impedance inverter for wideband Doherty high-power amplifier design. IEEE Trans. Microw. Theory Tech. 2016, 64, 1359–1372. [Google Scholar] [CrossRef]

- Gustafsson, D.; Andersson, C.; Fager, C. A modified Doherty power amplifier with extended bandwidth and reconfigurable efficiency. IEEE Trans. Microw. Theory Tech. 2013, 61, 533–542. [Google Scholar] [CrossRef]

- Khan, M.S.; Zhang, H.; Wang, X.; Ullah, R.; Ahmad, I.; Shahzad, S.; Arain, Q.A.; Tunio, M.Z. A novel two-stage broadband Doherty power amplifier for wireless applications. IEEE Microw. Wirel. Compon. Lett. 2018, 28, 40–42. [Google Scholar] [CrossRef]

- Darraji, R.; Bhaskar, D.; Sharma, T.; Helaoui, M.; Mousavi, P.; Ghannouchi, F.M. Generalized theory and design methodology of wideband Doherty amplifiers applied to the realization of an octave-bandwidth prototype. IEEE Trans. Microw. Theory Tech. 2017, 65, 3014–3023. [Google Scholar] [CrossRef]

- Chen, X.; Chen, W. A novel broadband Doherty power amplifier with post-matching structure. In Proceedings of the 2012 Asia Pacific Microwave Conference (APMC), Kaohsiung, Taiwan, 4–7 December 2012; pp. 370–372. [Google Scholar] [CrossRef]

- Pang, J.; He, S.; Huang, C.; Dai, Z.; Peng, J.; You, F. A post-matching Doherty power amplifier employing low-order impedance inverters for broadband applications. IEEE Trans. Microw. Theory Tech. 2015, 63, 4061–4071. [Google Scholar] [CrossRef]

- Xia, J.; Yang, M.; Zhu, A. Improved Doherty amplifier design with minimum phase delay in output matching network for wideband application. IEEE Microw. Wirel. Compon. Lett. 2016, 26, 915–917. [Google Scholar] [CrossRef]

- Zhou, X.Y.; Zheng, S.Y.; Chan, W.S.; Chen, S.; Ho, D. Broadband efficiency-enhanced mutually coupled harmonic postmatching Doherty power amplifier. IEEE Trans. Circuits Syst. I Regul. Pap. 2017, 64, 1758–1771. [Google Scholar] [CrossRef]

- Chen, S.; Wang, G.; Cheng, Z.; Xue, Q. A bandwidth enhanced Doherty power amplifier with a compact output combiner. IEEE Microw. Wirel. Compon. Lett. 2016, 26, 434–436. [Google Scholar] [CrossRef]

- Shi, W.; He, S.; You, F.; Xie, H.; Naah, G.; Liu, Q.-A.; Li, Q. The influence of the output impedances of peaking power amplifier on broadband Doherty amplifiers. IEEE Trans. Microw. Theory Tech. 2017, 65, 3002–3013. [Google Scholar] [CrossRef]

- Xia, J.; Yang, M.; Guo, Y.; Zhu, A. A broadband high-efficiency Doherty power amplifier with integrated compensating reactance. IEEE Trans. Microw. Theory Tech. 2016, 64, 2014–2024. [Google Scholar] [CrossRef]

- Shi, W.; He, S.; Zhu, X.; Song, B.; Zhu, Z.; Naah, G.; Zhang, M. Broadband continuous-mode Doherty power amplifiers with noninfinity peaking impedance. IEEE Trans. Microw. Theory Tech. 2018, 66, 1034–1046. [Google Scholar] [CrossRef]

- Chen, X.; Chen, W.; Ghannouchi, F.M.; Feng, Z.; Liu, Y. A broadband Doherty power amplifier based on continuous-mode technology. IEEE Trans. Microw. Theory Tech. 2016, 64, 4505–4517. [Google Scholar] [CrossRef]

- Ghosh, S.; Rawat, K. Hybrid analog digital continuous class B/J mode for broadband Doherty power amplifiers. IEEE Access 2019, 7, 74986–74995. [Google Scholar] [CrossRef]

- Li, Y.; Fang, X.; Jundi, A.; Huang, H.; Boumaiza, S. Two-port network theory-based design method for broadband class J Doherty amplifiers. IEEE Access 2019, 7, 51028–51038. [Google Scholar] [CrossRef]

- Nasri, A.; Estebsari, M.; Toofan, S.; Piacibello, A.; Pirola, M.; Camarchia, V.; Ramella, C. Broadband class-J GaN Doherty power amplifier. Electronics 2022, 11, 552. [Google Scholar] [CrossRef]

- Shi, W.; Shi, W.; Peng, J.; Feng, L.; Gao, Y.; He, S.; Yue, C.P. Design and analysis of continuous-mode Doherty power amplifier with second harmonic control. IEEE Trans. Circuits Syst. II Exp. Briefs 2021, 68, 2247–2251. [Google Scholar] [CrossRef]

- Giofrè, R.; Piazzon, L.; Colantonio, P.; Giannini, F. A closed-form design technique for ultra-wideband Doherty power amplifiers. IEEE Trans. Microw. Theory Tech. 2014, 62, 3414–3424. [Google Scholar] [CrossRef]

- Barakat, A.; Thian, M.; Fusco, V.; Bulja, S.; Guan, L. Toward a more generalized Doherty power amplifier design for broadband operation. IEEE Trans. Microw. Theory Tech. 2017, 65, 846–859. [Google Scholar] [CrossRef]

- Moreno Rubio, J.J.; Camarchia, V.; Pirola, M.; Quaglia, R. Design of an 87% fractional bandwidth Doherty power amplifier supported by a simplified estimation method. IEEE Trans. Microw. Theory Tech. 2018, 66, 1319–1327. [Google Scholar] [CrossRef]

- Yang, Z.; Yao, Y.; Li, M.; Jin, Y.; Li, T.; Dai, Z.; Tang, F.; Li, Z. Bandwidth extension of Doherty power amplifier using complex combining load with noninfinity peaking impedance. IEEE Trans Microw. Theory Tech. 2019, 67, 765–777. [Google Scholar] [CrossRef]

- Rafati, S.; Nayyeri, V.; Soleimani, M. A 100-W Doherty power amplifier with super-octave bandwidth. IEEE Trans. Circuits Syst. II Exp. Briefs 2020, 67, 1009–1013. [Google Scholar] [CrossRef]

- Li, M.; Pang, J.; Li, Y.; Zhu, A. Bandwidth enhancement of Doherty power amplifier using modified load modulation network. IEEE Trans. Circuits Syst. I Reg. Pap. 2020, 67, 1824–1834. [Google Scholar] [CrossRef]

- Zhou, X.Y.; Chan, W.S.; Feng, W.; Fang, X.; Sharma, T.; Chen, S. Broadband Doherty power amplifier based on coupled phase compensation network. IEEE Trans Microw. Theory Tech. 2022, 70, 210–221. [Google Scholar] [CrossRef]

- Xu, Y.; Pang, J.; Wang, X.; Zhu, A. Enhancing bandwidth and back-off range of Doherty power amplifier with modified load modulation network. IEEE Trans Microw. Theory Tech. 2021, 69, 2291–2303. [Google Scholar] [CrossRef]

- Xu, J.X.; Chen, H.; Chen, W.; Zhang, X.Y. Broadband Doherty power amplifier using short ended λ-4 transmission lines based on the analysis of negative characteristic impedance. IEEE Trans. Circuits Syst. I Reg. Pap. 2023, 70, 545–555. [Google Scholar] [CrossRef]

| Ref. (Year) | Frequency (GHz) | RBW | Power (dBm) | Gain (dB) | DE@Sat (%) | DE@-6dB (%) |

|---|---|---|---|---|---|---|

| [14] (2017) | 0.55–1.1 | 66.7% | 42–43.5 | N/A | 56–72 | 40–52 |

| [19] (2016) | 1.5–2.5 | 50% | 42–44.5 | 8–11 | 55–75 | 42–53 |

| [21] (2016) | 1.7–2.8 | 49% | 44–44.5 | 11–12 | 57–71 | 50–55 |

| [23] (2016) | 1.65–2.75 | 50% | 44–46 | 7–8 | 60–75 | 50–60 |

| [24] (2019) | 1.25–2.3 | 59.2% | 41.4–44.6 | N/A | 56–75.4 | 45–56.5 |

| [27] (2021) | 1.5–2.55 | 51.8% | 42.6–44.4 | 7.2–11.6 | 50.7–69.7 | 43.3–57 |

| [28] (2014) | 1.05–2.55 | 83% | 40–42 | >7 | 45–83 | 35–58 |

| [30] (2018) | 1.5–3.8 | 87% | 42.3–43.4 | 10–13.8 | 42–63 | 33–55 |

| [31] (2019) | 1.1–2.4 | 74% | 43.3–45.4 | 9.5–11.1 | 55.4–68 | 43.8–54.9 |

| [33] (2020) | 2.8–3.55 | 23.6% | 43–45 | 8.3–9.1 | 66–78 | 50–60.6 |

| [36] (2023) | 0.8–2.7 | 108.6% | 41.8–44 | 7.1–11.1 | 47.6–84.4 | 39.5–52 |

| This Work | 1.2–2.8 | 80% | 43.2–44.7 | 5.2–8.6 | 44.3–70.4 | 38.7–57.6 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chen, J.; Liu, Z.; Dong, T.; Shi, W. Design of Ultra-Wideband Doherty Power Amplifier Using a Modified Combiner Integrated with Complex Combining Impedance. Sensors 2023, 23, 3882. https://doi.org/10.3390/s23083882

Chen J, Liu Z, Dong T, Shi W. Design of Ultra-Wideband Doherty Power Amplifier Using a Modified Combiner Integrated with Complex Combining Impedance. Sensors. 2023; 23(8):3882. https://doi.org/10.3390/s23083882

Chicago/Turabian StyleChen, Jian, Zhihui Liu, Tao Dong, and Weimin Shi. 2023. "Design of Ultra-Wideband Doherty Power Amplifier Using a Modified Combiner Integrated with Complex Combining Impedance" Sensors 23, no. 8: 3882. https://doi.org/10.3390/s23083882

APA StyleChen, J., Liu, Z., Dong, T., & Shi, W. (2023). Design of Ultra-Wideband Doherty Power Amplifier Using a Modified Combiner Integrated with Complex Combining Impedance. Sensors, 23(8), 3882. https://doi.org/10.3390/s23083882