Design of Low-Noise CMOS Image Sensor Using a Hybrid-Correlated Multiple Sampling Technique

Abstract

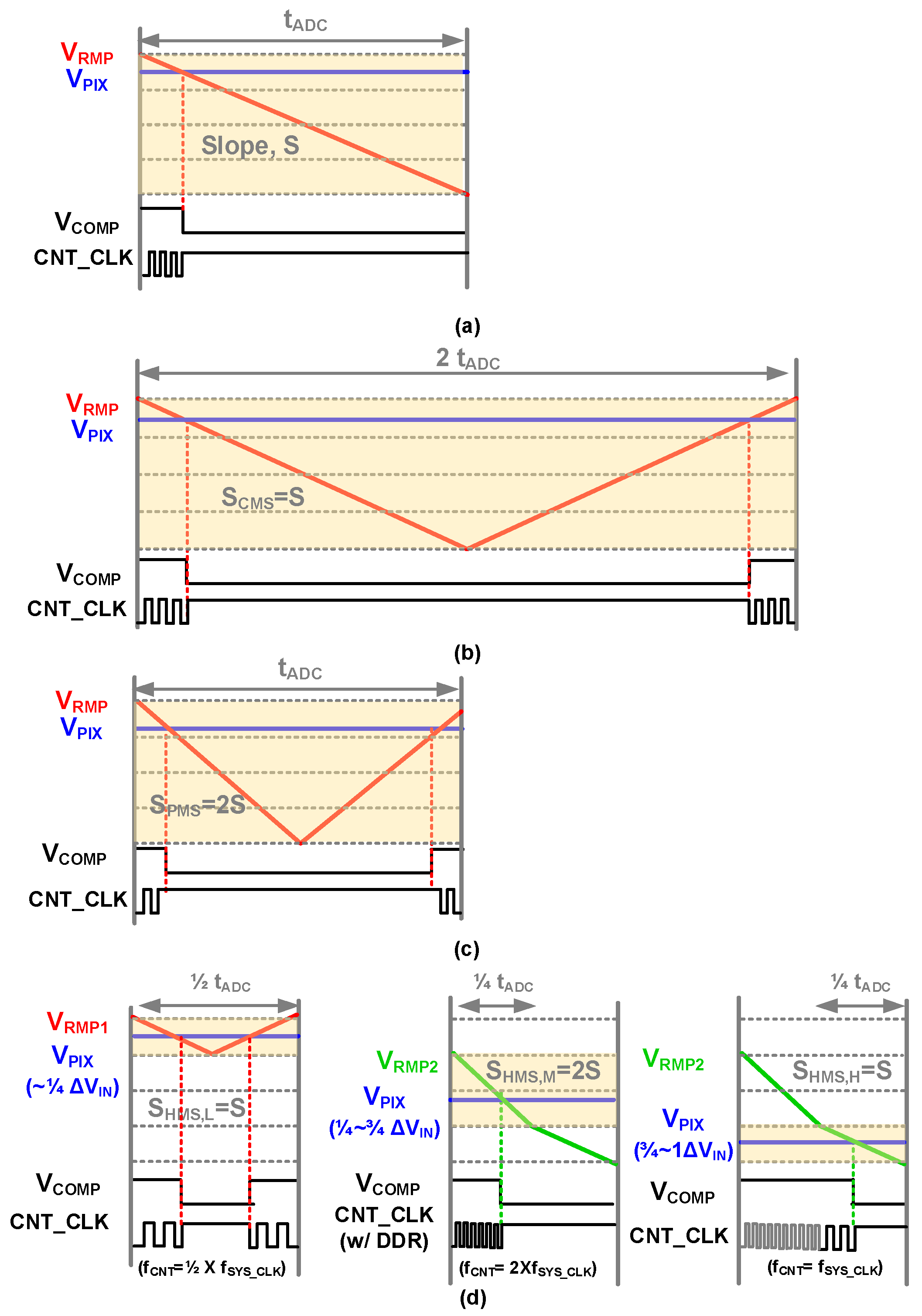

:1. Introduction

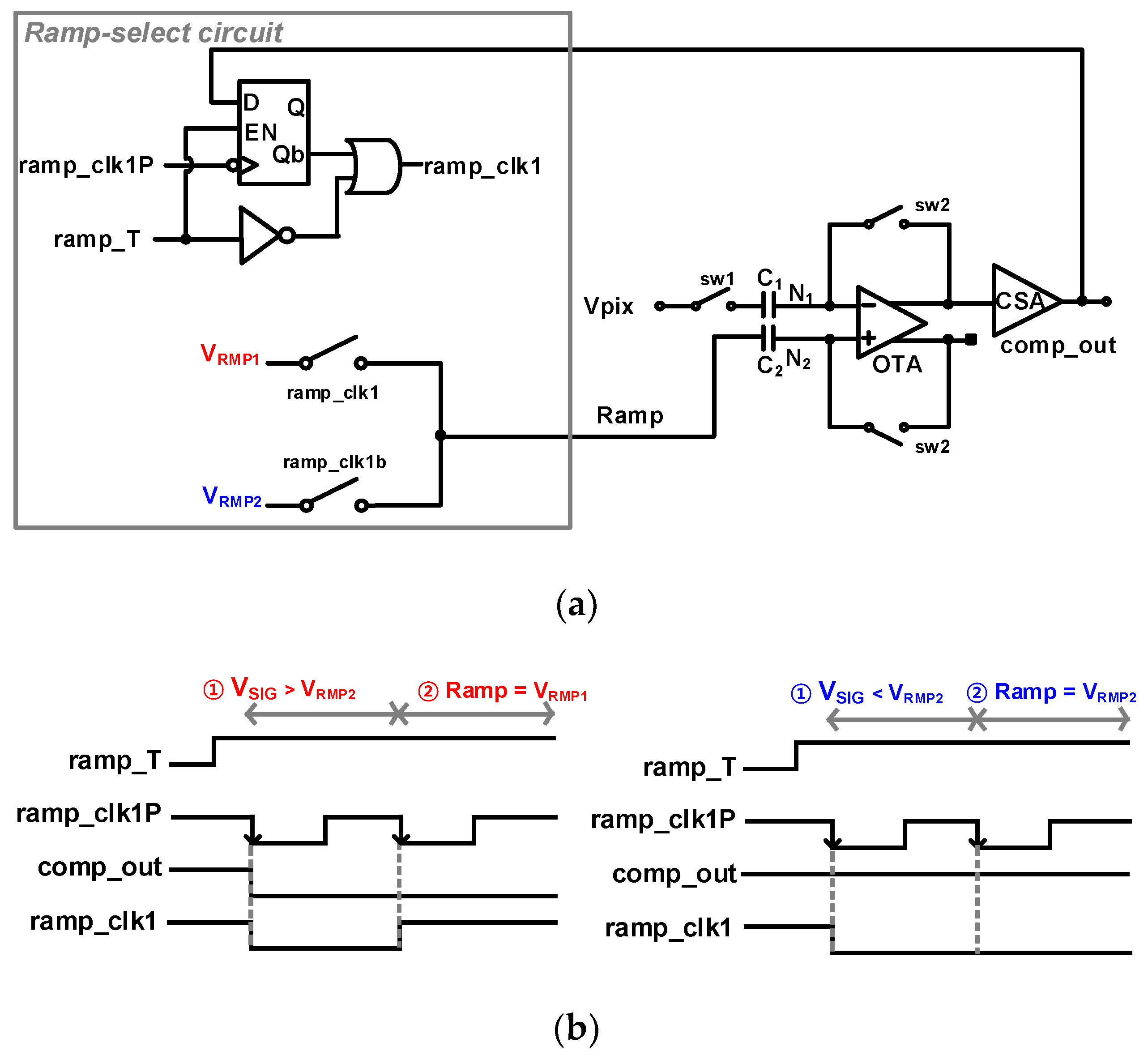

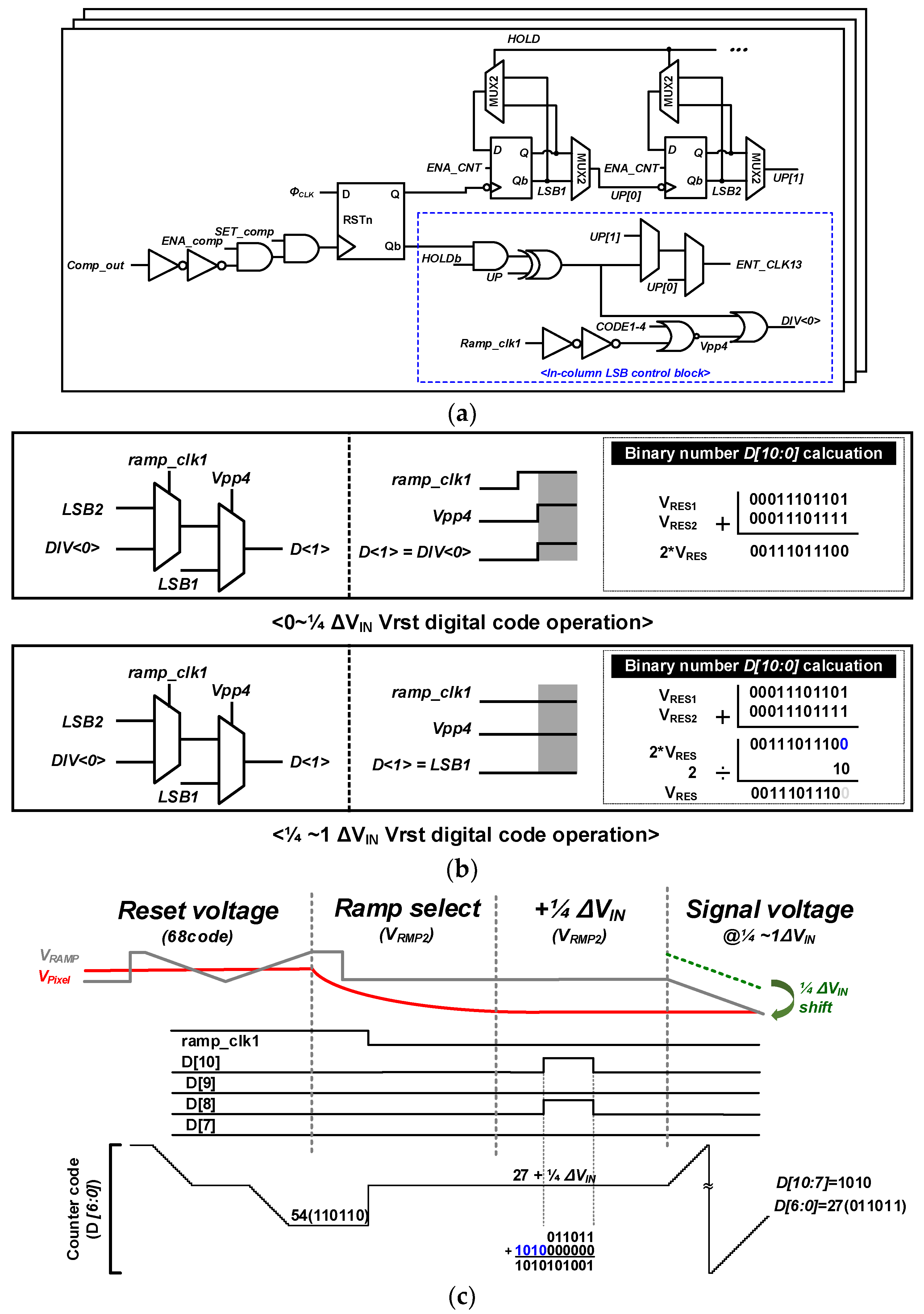

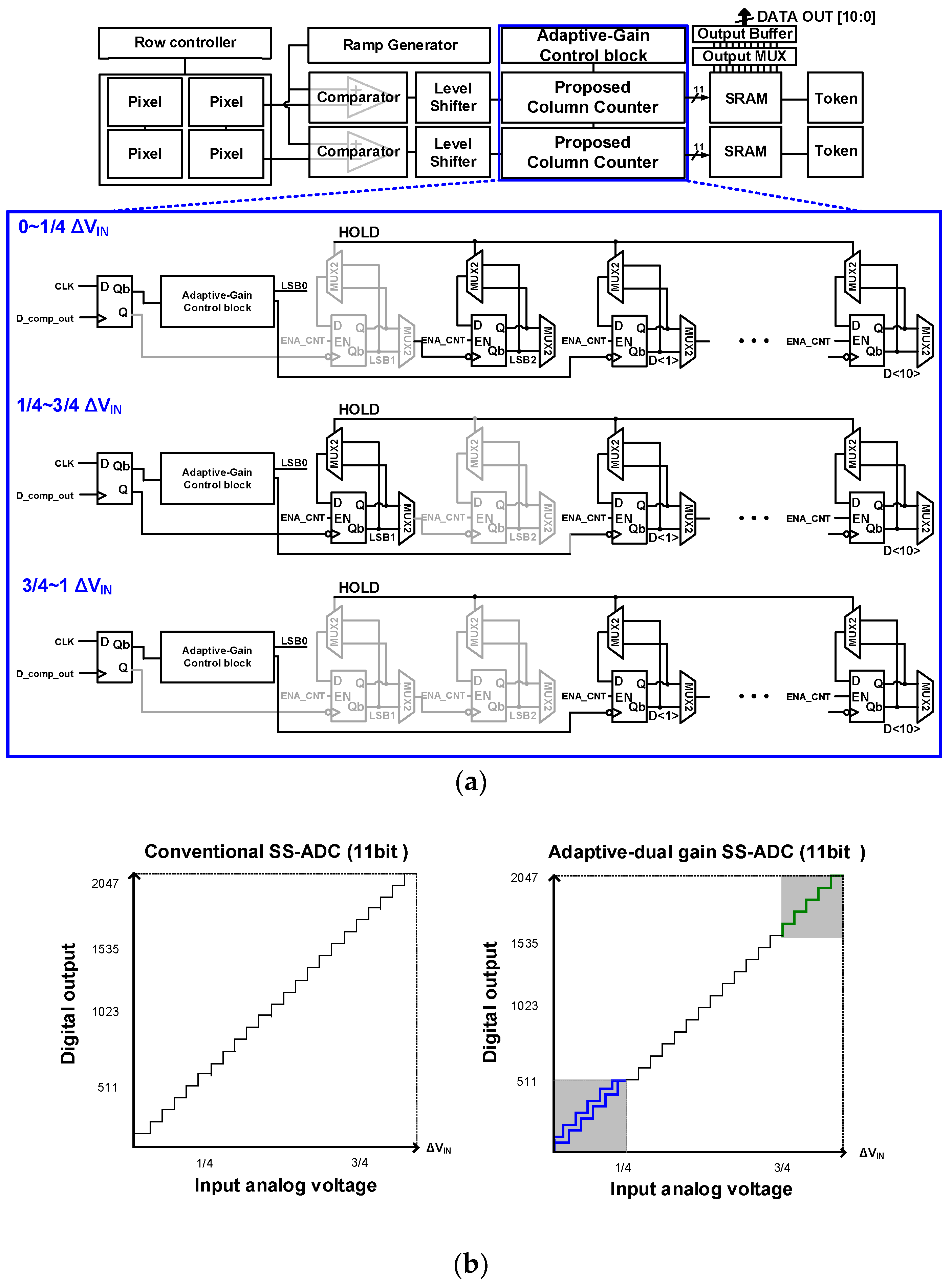

2. Proposed CIS Structure

2.1. Ramp-Select Circuit Using Feedback Scheme

2.2. Binary Calculation for HMS

2.3. LSB Control Counter

3. Experiment Results

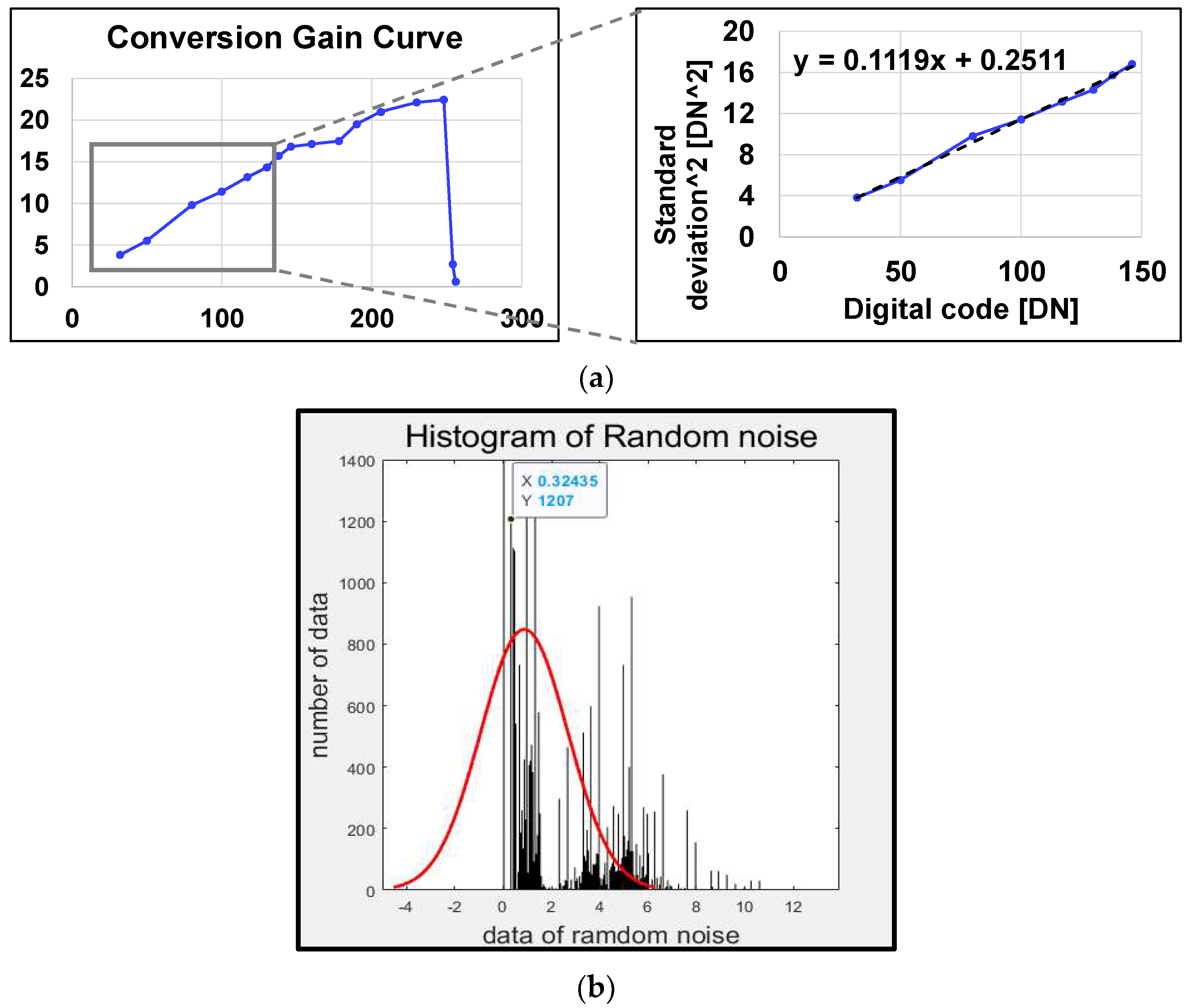

3.1. Dark Random Noise

3.2. Signal-to-Noise Ratio

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- He, Z.; Li, F.; Zuo, P.; Tian, H. Principles and Applications of Resonance Energy Transfer Involving Noble Metallic Nanoparticles. Materials 2023, 16, 3083. [Google Scholar] [CrossRef] [PubMed]

- Gao, Z.; Yao, S.; Yang, C.; Xu, J. A Dynamic Range Extension Technique for CMOS Image Sensors with In-Pixel Dual Exposure Synthesis. IEEE Sens. J. 2015, 15, 3265–3273. [Google Scholar] [CrossRef]

- Jeong, B.; Lee, J.; Choi, J.; Song, M.; Son, Y.; Kim, S. A 0.57 mW@1 FPS In-Column Analog CNN Processor Integrated Into CMOS Image Sensor. IEEE Access 2023, 11, 61082–61090. [Google Scholar] [CrossRef]

- Cho, J.; Choo, H.; Lee, S.; Yoon, S.; Kam, G.; Kim, S. Design of a CMOS Image Sensor with Bi-Directional Gamma-Corrected Digital-Correlated Double Sampling. Sensors 2023, 23, 1031. [Google Scholar] [CrossRef] [PubMed]

- Fowler, B.; Liu, C.; Mims, S.; Balicki, J.; Li, W.; Do, H.; Vu, P. Wide Dynamic Range Low Light Level CMOS Image Sensor. In Proceedings of the 2009 International Image Sensor Workshop, Bergen, Norway, 26–28 June 2009; pp. 340–343. [Google Scholar]

- Ma, C.; Liu, Y.; Li, Y.; Zhou, Q.; Wang, X.; Chang, Y. A 4-M Pixel High Dynamic Range, Low-Noise CMOS Image Sensor with Low-Power Counting ADC. IEEE Trans. Electron Devices 2017, 64, 3199–3205. [Google Scholar] [CrossRef]

- Um, B.Y.; Kim, J.R.; Kim, S.H.; Lee, J.H.; Cheon, J.; Choi, J.; Chun, J.H. Design and evaluation of a CMOS image sensor with dual-CDS and column-parallel SS-ADCs. J. Semicond. Technol. Sci. 2017, 17, 110–119. [Google Scholar] [CrossRef]

- Cho, K.; Kim, D.; Song, M. A low power dual CDS for a column-parallel CMOS image sensor. J. Semicond. Technol. Sci. 2012, 12, 388–396. [Google Scholar] [CrossRef]

- Kawai, N.; Kawahito, S. Effectiveness of a correlated multiple sampling differential average for reducing 1/f noise. IEICE Electron. Exp. 2005, 2, 379–383. [Google Scholar] [CrossRef]

- Kawahito, S.; Suh, S.; Shirei, T.; Itoh, S.; Aoyama, S. Noise reduction effects of column-parallel correlated multiple sampling and source-follower driving current switching for CMOS image sensors. In Proceedings of the 2009 International Image Sensor Workshop, Bergen, Norway, 26–28 June 2009; Volume 8. [Google Scholar]

- Lim, Y.; Koh, K.; Kim, K.; Yang, H.; Kim, J.; Jeong, Y.; Lee, S.; Lee, H.; Lim, S.H.; Han, Y.; et al. A 1.1 e-temporal noise 1/3.2-inch 8Mpixel CMOS image sensor using pseudo-multiple sampling. In Proceedings of the 2010 IEEE International Solid-State Circuits Conference-(ISSCC), San Francisco, CA, USA, 7–11 February 2010; pp. 396–397. [Google Scholar] [CrossRef]

- Xhakoni, A.; Fekri, A.; Francis, P.; Vancauwenbergh, K.; Van Esbroeck, K. A 40000fps global shutter image sensor with 26.7 ns 12-bit row readout time. In Proceedings of the 2021 International Image Sensor Workshop, Online, 20–23 September 2021. [Google Scholar]

- Park, H.; Yu, C.; Kim, H.; Roh, Y.; Burm, J. Low Power CMOS Image Sensors Using Two Step Single Slope ADC with Bandwidth-Limited Comparators & Voltage Range Extended Ramp Generator for Battery-Limited Application. IEEE Sens. J. 2020, 20, 2831–2838. [Google Scholar] [CrossRef]

| Illumination | Output | Noise | SNR | SS-ADC SNR |

|---|---|---|---|---|

| 340 | 95.40 | 2.18 | 32.80 | 21.38 |

| 900 | 275.39 | 6.11 | 33.06 | 28.68 |

| 1280 | 466.64 | 8.87 | 34.42 | 28.71 |

| [11] | [13] | This Work | |

|---|---|---|---|

| Technology (nm) | 90 | 90 | 110 |

| Image Resolution | 8 M | 960 × 720 | 320 × 240 |

| Pixel Size (μm2) | 1.4 × 1.4 | 1.4 × 1.4 | 3.25 × 3.25 |

| ADC Column Pitch (μm) | 2.8 (even/odd readout) | 2.8 (even/odd readout) | 3.25 (even readout) |

| ADC Resolution (bit) | 10 | 10 | 11 |

| System CLK (MHz) | 130 | 50 | 12.5 |

| Random Noise (VRMS) | 336 μ | 472 μ | 80.39 μ 169.69 μ |

| Total Power (mV) | 280 | 28 | 5.349 |

| FoM (VRMS·W/FPS·# of Pixels) | N/A | 542.8 μ @dark | 336 μ @dark 710.15 μ @bright |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Youn, S.J.; Yun, S.Y.; Lee, H.; Park, K.J.; Kim, J.; Kim, S.Y. Design of Low-Noise CMOS Image Sensor Using a Hybrid-Correlated Multiple Sampling Technique. Sensors 2023, 23, 9551. https://doi.org/10.3390/s23239551

Youn SJ, Yun SY, Lee H, Park KJ, Kim J, Kim SY. Design of Low-Noise CMOS Image Sensor Using a Hybrid-Correlated Multiple Sampling Technique. Sensors. 2023; 23(23):9551. https://doi.org/10.3390/s23239551

Chicago/Turabian StyleYoun, Seung Ju, Su Yeon Yun, Hoyeon Lee, Kwang Jin Park, Jiwon Kim, and Soo Youn Kim. 2023. "Design of Low-Noise CMOS Image Sensor Using a Hybrid-Correlated Multiple Sampling Technique" Sensors 23, no. 23: 9551. https://doi.org/10.3390/s23239551

APA StyleYoun, S. J., Yun, S. Y., Lee, H., Park, K. J., Kim, J., & Kim, S. Y. (2023). Design of Low-Noise CMOS Image Sensor Using a Hybrid-Correlated Multiple Sampling Technique. Sensors, 23(23), 9551. https://doi.org/10.3390/s23239551