A Comprehensive Methodology for Optimizing Read-Out Timing and Reference DAC Offset in High Frame Rate Image Sensing Systems

Abstract

1. Introduction

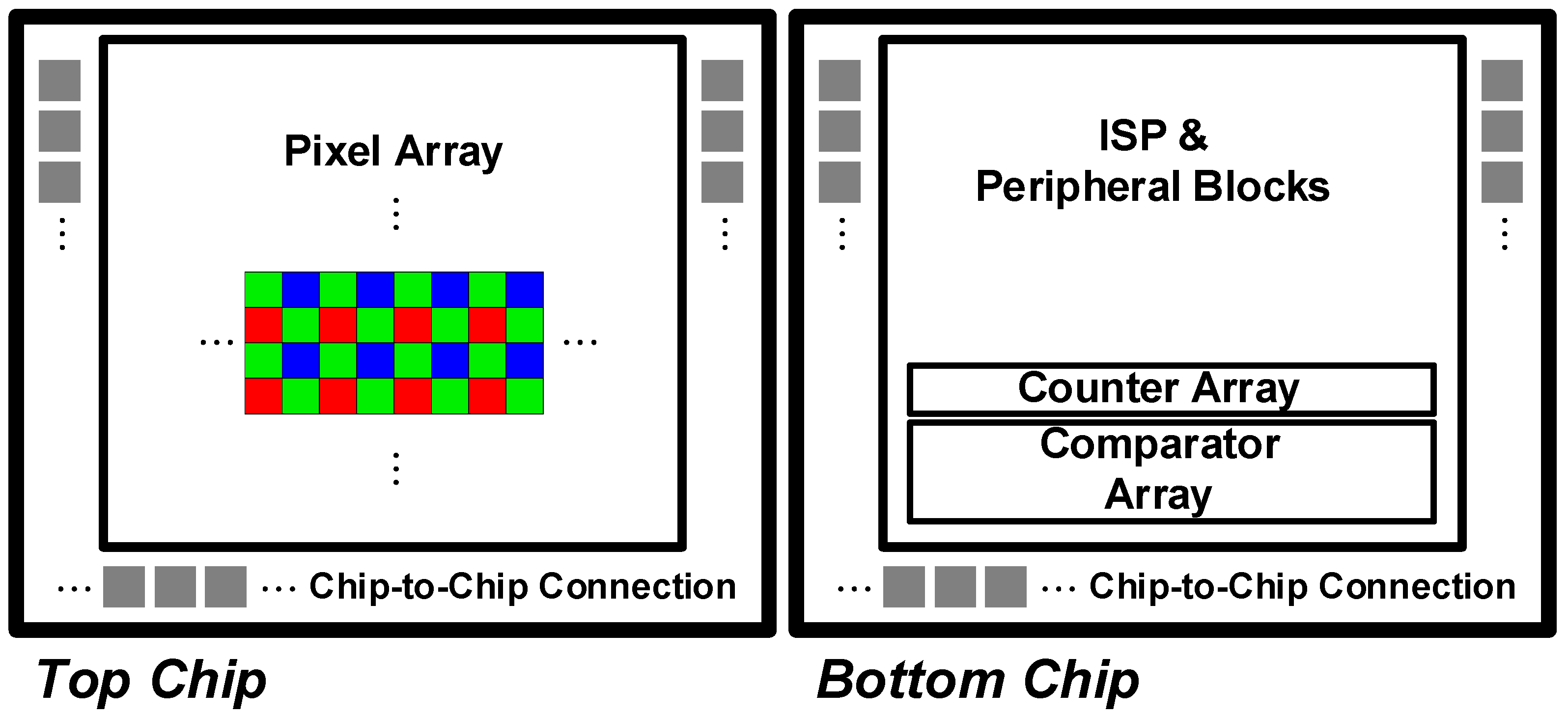

2. Image Sensor Architecture

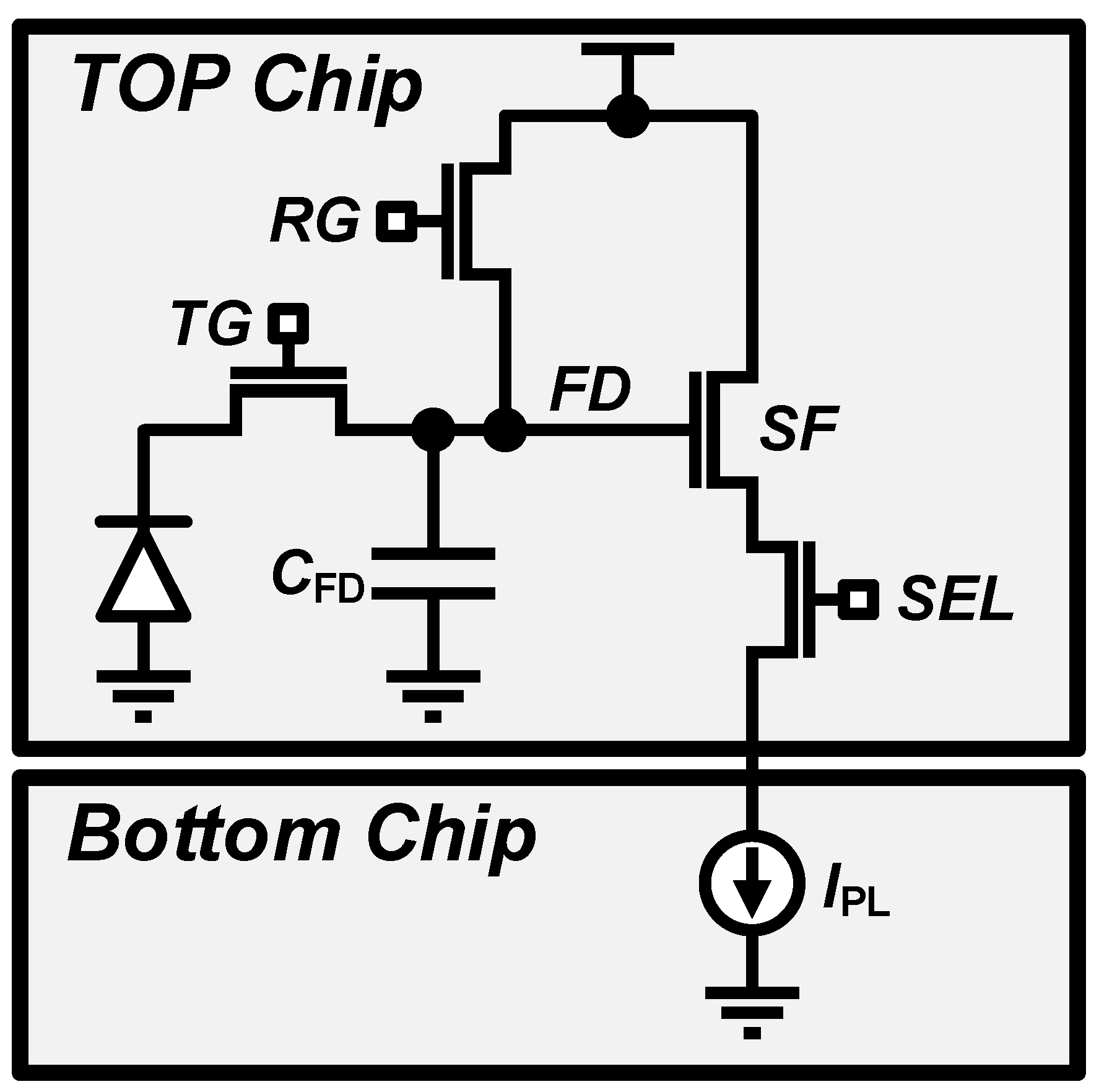

2.1. Pixel Structure

2.2. Read-Out IC Structure

3. Read-Out Timing Optimization Methodology

3.1. Period A: Reset

3.2. Periods B and C: AZ

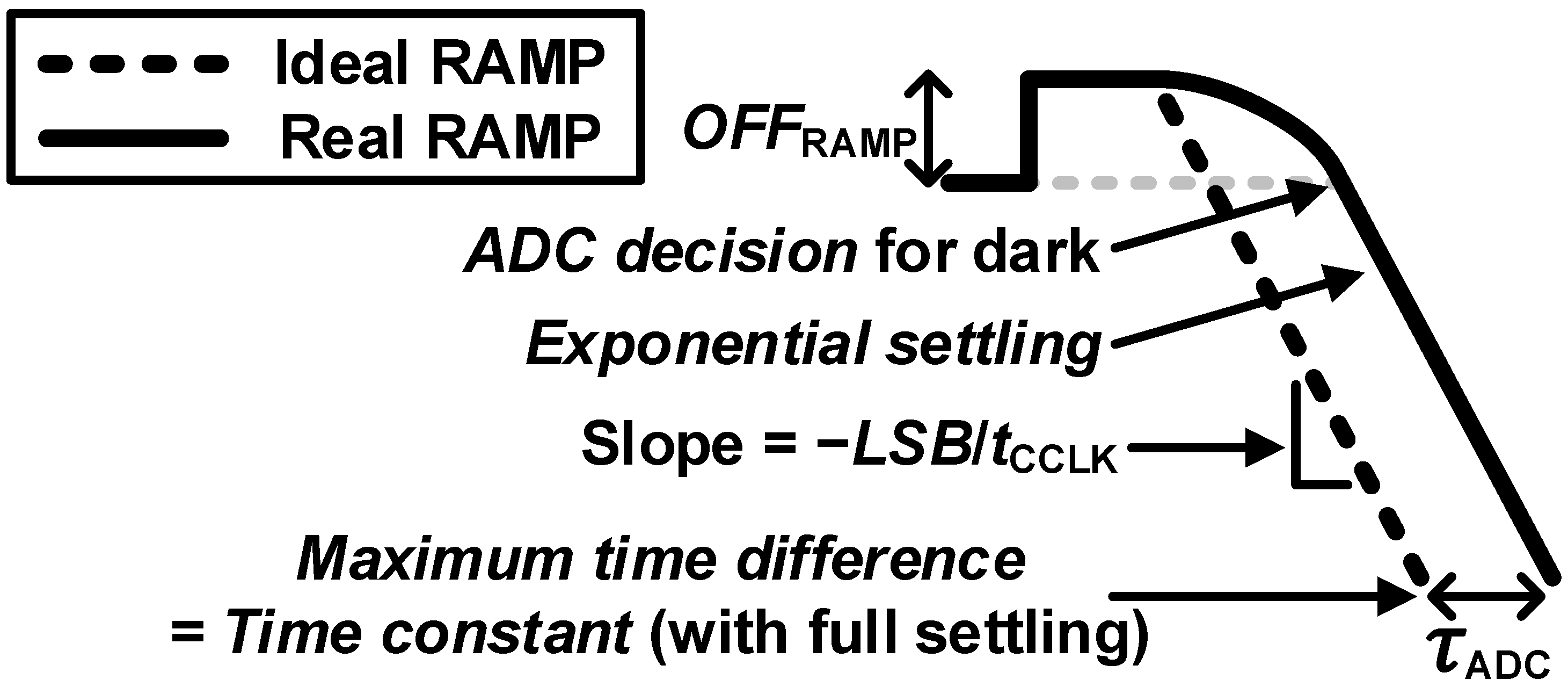

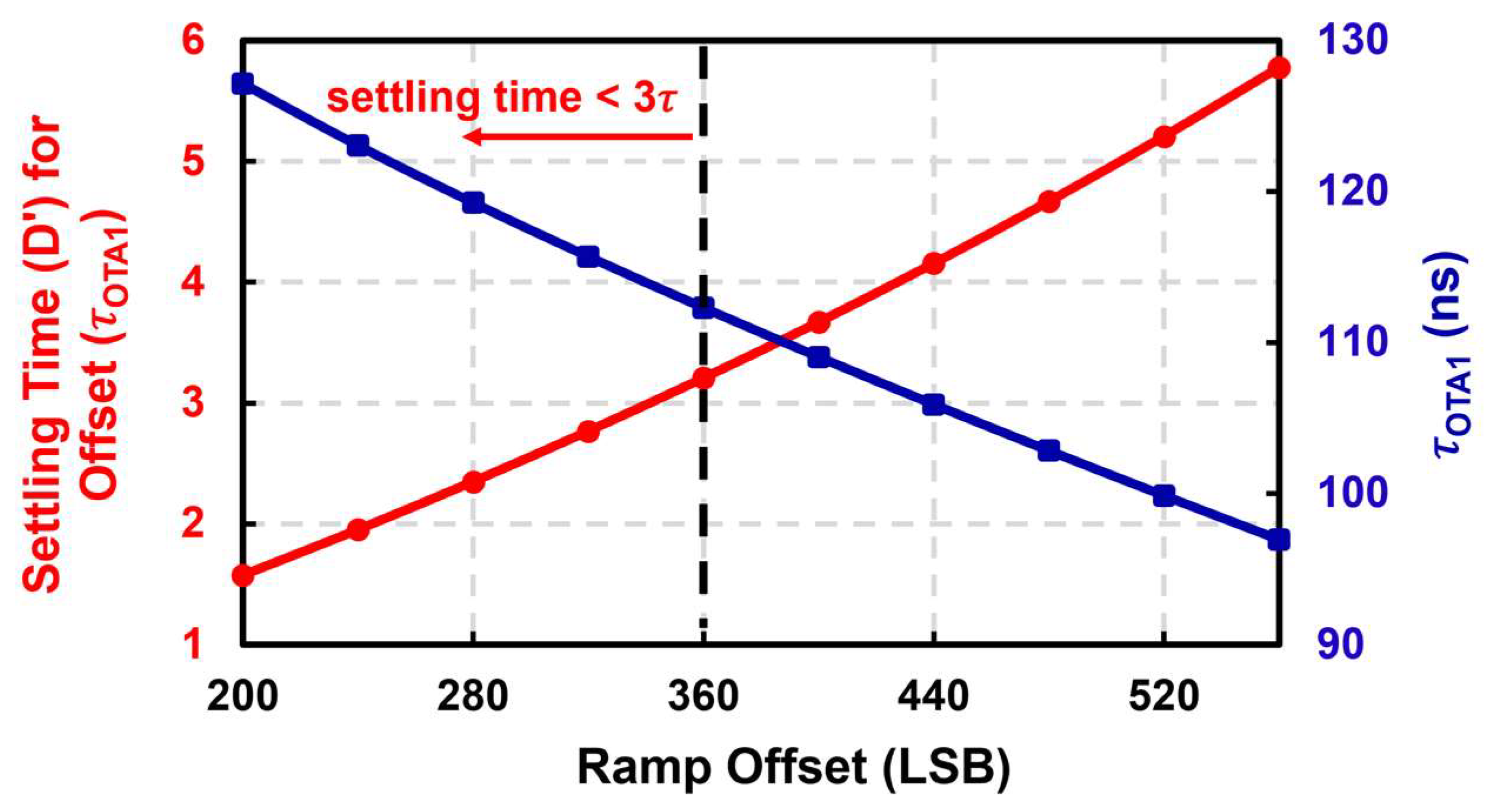

3.3. Period D: Reference Offset and Its Counting

3.4. Period E: Dark Counting

3.5. Periods F, G, and H: TG

3.6. Period I: Light Counting

3.7. Timing Optimization

4. Implementation and Experimental Results

5. Conclusions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Jun, J.; Shin, S.; Kim, M.; Kim, S. A ±0.15% RH inaccuracy humidity sensing system with ±0.44 °C (3σ) inaccuracy on-chip temperature sensor. IEEE Sens. J. 2021, 21, 2115–2123. [Google Scholar] [CrossRef]

- Tang, Z.; Pan, S.; Makinwa, K.A.A. A Sub-1 V 810 nW Capacitively-Biased BJT-Based Temperature Sensor with an Inaccuracy of ±0.15 °C (3σ) from −55 °C to 125 °C. In Proceedings of the 2023 IEEE International Solid-State Circuits Conference (ISSCC), Digest of Technical Papers, San Francisco, CA, USA, 19–23 February 2023; pp. 22–24. [Google Scholar]

- Hopf, Y.M.; Ossenkoppele, B.W.; Soozande, M.; Noothout, E.; Chang, Z.Y.; Chen, C.; Vos, H.J.; Bosch, J.G.; Verweij, M.D.; de Jong, N.; et al. A pitch-matched transceiver ASIC with shared hybrid beamforming ADC for high-frame-rate 3-D intracardiac echocardiography. IEEE J. Solid-State Circuits 2022, 57, 3228–3242. [Google Scholar] [CrossRef]

- Lee, B.; Yang, J.; Cho, J.; Kim, S. A low-power digital capacitive MEMS microphone based on a triple-sampling delta-sigma ADC with embedded gain. IEEE Access 2022, 10, 75323–75330. [Google Scholar] [CrossRef]

- Totsuka, H.; Tsuboi, T.; Muto, T.; Yoshida, D.; Matsuno, Y.; Ohmura, M.; Takahashi, H.; Sakurai, K.; Ichikawa, T.; Yuzurihara, H.; et al. An APS-H-Size 250 Mpixel CMOS Image Sensor Using Column Single-Slope ADCs with Dual-Gain Amplifiers. In Proceedings of the 2016 IEEE International Solid-State Circuits Conference (ISSCC), Digest of Technical Papers, San Francisco, CA, USA, 31 January–4 February 2016; pp. 116–118. [Google Scholar]

- Guo, M.; Chen, S.; Gao, Z.; Yang, W.; Bartkovjak, P.; Qin, Q.; Hu, X.; Zhou, D.; Uchiyama, M.; Fukuoka, S.; et al. A 3-Wafer-stacked Hybrid 15 MPixel CIS + 1 MPixel EVS with 4.6 GEvent/s Readout, in-Pixel TDC and on-Chip ISP and ESP Function. In Proceedings of the 2023 IEEE International Solid-State Circuits Conference (ISSCC), Digest of Technical Papers, San Francisco, CA, USA, 19–23 February 2023; pp. 90–92. [Google Scholar]

- Jun, J.; Seo, H.; Kwon, H.; Lee, J.; Yoon, B.; Lee, Y.; Kim, Y.; Joo, W.; Lee, J.; Koh, K. A 0.7 μm-Pitch 108 Mpixel Nonacell-Based CMOS Image Sensor with Decision-Feedback Technique. In Proceedings of the 2022 IEEE International Symposium on Circuits and Systems (ISCAS), Austin, TX, USA, 27 May–12 June 2022; pp. 283–287. [Google Scholar]

- Jun, J.; Yang, H.; Yoon, B.; Kim, Y.; Koh, K. A Low Power Digitizer with Piecewise-Linear Counting Technique for High Dynamic Range Nonacell-Based 3-D-Stacked CMOS Image Sensor. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), Monterey, CA, USA, 21–25 May 2023; pp. 1–5. [Google Scholar]

- Sakakibara, M.; Ogawa, K.; Sakai, S.; Tochigi, Y.; Honda, K.; Kikuchi, H.; Wada, T.; Kamikubo, Y.; Miura, T.; Nakamizo, M.; et al. A Back-Illuminated Global-Shutter CMOS Image Sensor with Pixel-Parallel 14b Subthreshold ADC. In Proceedings of the 2018 IEEE International Solid-State Circuits Conference-(ISSCC), Digest of Technical Papers, San Francisco, CA, USA, 11–15 February 2018; pp. 80–82. [Google Scholar]

- Kawahito, S. Column-parallel ADCs for CMOS image sensor and their FoM-based evaluations. IEICE Trans. Electrons 2018, 101, 444–456. [Google Scholar] [CrossRef]

- Funatsu, R.; Huang, S.; Yamashita, T.; Stevulak, K.; Rysinski, J.; Estrada, D.; Yan, S.; Soeno, T.; Nakamura, T.; Hayashida, T.; et al. A 133 Mpixel 60 fps CMOS Image Sensor with 32- Column Shared High-Speed Column-Parallel SAR ADCs. In Proceedings of the 2015 IEEE International Solid-State Circuits Conference-(ISSCC), Digest of Technical Papers, San Francisco, CA, USA, 22–26 February 2015; pp. 112–114. [Google Scholar]

- Sakano, Y.; Toyoshima, T.; Nakamura, R.; Asatsuma, T.; Hattori, Y.; Yamanaka, T.; Yoshikawa, R.; Kawazu, N.; Matsuura, T.; Iinuma, T.; et al. A 132 dB Single-Exposure-Dynamic-Range CMOS Image Sensor with High Temperature Tolerance. In Proceedings of the 2020 IEEE International Solid-State Circuits Conference-(ISSCC), Digest of Technical Papers, San Francisco, CA, USA, 16–20 February 2020; pp. 106–108. [Google Scholar]

- Chou, P.-S.; Chang, C.-H.; Mhala, M.M.; Liu, C.C.-M.; Chao, C.Y.-P.; Huang, C.-Y.; Tu, H.; Wu, T.; Yeh, S.-F.; Takahashi, S.; et al. A 1.1 µm-pitch 13.5 Mpixel 3D-Stacked CMOS Image Sensor Featuring 230 fps Full-High-Definition and 514 fps High-Definition Videos by Reading 2 or 3 Rows Simultaneously Using a Column-Switching Matrix. In Proceedings of the 2018 IEEE International Solid-State Circuits Conference-(ISSCC), Digest of Technical Papers, San Francisco, CA, USA, 11–15 February 2018; pp. 88–100. [Google Scholar]

- Arai, T.; Yasue, T.; Kitamura, K.; Shimamoto, H.; Kosugi, T.; Jun, S.; Aoyama, S.; Hsu, M.C.; Yamashita, Y.; Sumi, H.; et al. A 1.1 μm 33 Mpixel 240 fps 3D-Stacked CMOS Image Sensor with 3-Stage Cyclic-Based Analog-to-Digital Converters. In Proceedings of the 2016 IEEE International Solid-State Circuits Conference (ISSCC), Digest of Technical Papers, San Francisco, CA, USA, 31 January–4 February 2016; pp. 126–128. [Google Scholar]

- Okino, T.; Yamada, S.; Sakata, Y.; Kasuga, S.; Takemoto, M.; Nose, Y.; Koshida, H.; Tamaru, M.; Sugiura, Y.; Saito, S.; et al. A 1200 × 900 6 µm 450 fps Geiger-Mode Vertical Avalanche Photodiodes CMOS Image Sensor for a 250 m Time-of-Flight Ranging System Using Direct-Indirect-Mixed Fame Synthesis with Configurable-Depth-Resolution Down to 10 cm. In Proceedings of the 2020 IEEE International Solid-State Circuits Conference-(ISSCC), Digest of Technical Papers, San Francisco, CA, USA, 16–20 February 2020; pp. 96–98. [Google Scholar]

- Xu, C.; Mo, Y.; Ren, G.; Ma, W.; Wang, X.; Shi, W.; Hou, J.; Shao, K.; Wang, H.; Xiao, P.; et al. A Stacked Global-Shutter CMOS Imager with SC-Type Hybrid-GS Pixel and Self-Knee Point Calibration Single-Frame HDR and on-Chip Binarization Algorithm for Smart Vision Applications. In Proceedings of the 2019 IEEE International Solid-State Circuits Conference-(ISSCC), Digest of Technical Papers, San Francisco, CA, USA, 17–21 February 2019; pp. 94–96. [Google Scholar]

- Yoshihara, S.; Nitta, Y.; Kikuchi, M.; Koseki, K.; Ito, Y.; Inada, Y.; Kuramochi, S.; Wakabayashi, H.; Okano, M.; Kuriyama, H.; et al. A 1/1.8-inch 6.4 MPixel 60 frames/s CMOS image sensor with seamless mode change. IEEE J. Solid-State Circuits 2006, 41, 2998–3006. [Google Scholar] [CrossRef]

- Kim, H.J. 11-bit column-parallel single-slope ADC with first-step half-reference ramping scheme for high-speed CMOS image sensors. IEEE J. Solid-State Circuits 2021, 56, 2132–2141. [Google Scholar] [CrossRef]

- Lin, C.; Lai, C.; King, Y. A Four Transistor CMOS Active Pixel Sensor with High Dynamic Range Operation. In Proceedings of the 2004 IEEE Asia-Pacific Conference on Advanced System Integrated Circuits (AP-ASIC), Fukuoka, Japan, 4–5 August 2004; pp. 124–127. [Google Scholar]

- Fossum, E.R.; Hondongwa, D.B. A review of the pinned photodiode for CCD and CMOS image sensors. IEEE J. Electron Devices Soc. 2014, 2, 33–43. [Google Scholar] [CrossRef]

- Wei, J.; Li, X.; Sun, L.; Li, D. A low-power column-parallel gain-adaptive single-slope ADC for CMOS image sensors. Electronics 2020, 9, 757. [Google Scholar] [CrossRef]

| Design Parameter | Value |

|---|---|

| Full-scale range (FSRADC) | 1 V |

| Maximum analog gain | 16 V/V |

| Counter clock (1/tCCLK) | 1 GHz |

| Reset-on (TA) | 1 μs |

| ΔRGOFF | 1 V |

| 𝜏SF | 0.05 μs |

| ILOAD | 5 μA |

| ETARG,B | 5 LSB |

| ETARG,D = ETARG,H | 0.05 LSB |

| Timing margin (TC = TF) | 50 ns |

| Settling for OFFRAMP | 3τOTA1 |

| Dark counting (TE) | 200 LSB |

| TG-on (TG) | 1 μs |

| ΔTGOFF | 1 V |

| COUNTMARGIN | 256 LSB |

| Period | Time Budget |

|---|---|

| A | 1000 ns |

| B | 851 ns |

| C | 50 ns |

| D | 885 ns |

| (D’) | 360 ns |

| E | 200 ns |

| F | 50 ns |

| G | 1000 ns |

| H | 1635 ns |

| (H*) | 1275 ns |

| (H′) | 360 ns |

| I | 4328 ns |

| Sum (one-row) | 10,000 ns (=10 μs) |

| Parameter | This Work [7] | [5] | [11] | [13] | [14] | [16] |

|---|---|---|---|---|---|---|

| Pixel pitch | 0.7 μm | 1.5 μm | 2.45 μm | 1.1 μm | 1.1 μm | 2.7 μm |

| # of pixels | 108 MP | 246 MP | 133 MP | 13.5 MP | 33.8 MP | 1.38 MP |

| Frame rate | 10 fps | 5 fps | 60 fps | 34 fps | 240 fps | 120 fps |

| RN | 1.4 e−rms | 7.1 e−rms | 7.7 e−rms | 1.8 e−rms | 3.6 e−rms | 3.5 e−rms |

| HN | 0.03 e−rms | – | – | – | – | – |

| Column FPN | 66 ppm | – | – | – | – | – |

| Power Consumption | 551 mW | 1970 mW | 11,000 mW | 258 mW | 3000 mW | 205 mW |

| FoM 1 | 0.71 e−∙nJ | 11.36 e−∙nJ | 10.61 e−∙nJ | 1.01 e−∙nJ | 1.36 e−∙nJ | 4.33 e−∙nJ |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jun, J. A Comprehensive Methodology for Optimizing Read-Out Timing and Reference DAC Offset in High Frame Rate Image Sensing Systems. Sensors 2023, 23, 7048. https://doi.org/10.3390/s23167048

Jun J. A Comprehensive Methodology for Optimizing Read-Out Timing and Reference DAC Offset in High Frame Rate Image Sensing Systems. Sensors. 2023; 23(16):7048. https://doi.org/10.3390/s23167048

Chicago/Turabian StyleJun, Jaehoon. 2023. "A Comprehensive Methodology for Optimizing Read-Out Timing and Reference DAC Offset in High Frame Rate Image Sensing Systems" Sensors 23, no. 16: 7048. https://doi.org/10.3390/s23167048

APA StyleJun, J. (2023). A Comprehensive Methodology for Optimizing Read-Out Timing and Reference DAC Offset in High Frame Rate Image Sensing Systems. Sensors, 23(16), 7048. https://doi.org/10.3390/s23167048