Quantum LFSR Structure for Random Number Generation Using QCA Multilayered Shift Register for Cryptographic Purposes

Abstract

:1. Introduction

- A multilayered 2-to-1 Mux using cell interaction is proposed. Additionally, an optimized D-latch is proposed using the Mux.

- By connecting the proposed D-latch, a 4-bit SR with modularity and scalability is proposed using a multilayered structure.

- A three-input XOR gate is connected to the proposed SR to complete the 4-bit LFSR structure, and a dual-edge trigged LFSR structure is additionally proposed.

- The proposed structures and the structures of existing papers were compared, the accuracy of design and operation was checked and compared using QCADesigner [40], the latency and required area were checked, and the cost was calculated.

- Finally, the proposed LFSR structure was compared with the best existing structures by additionally calculating energy dissipation using QCADesigner-E [41].

2. Related Works

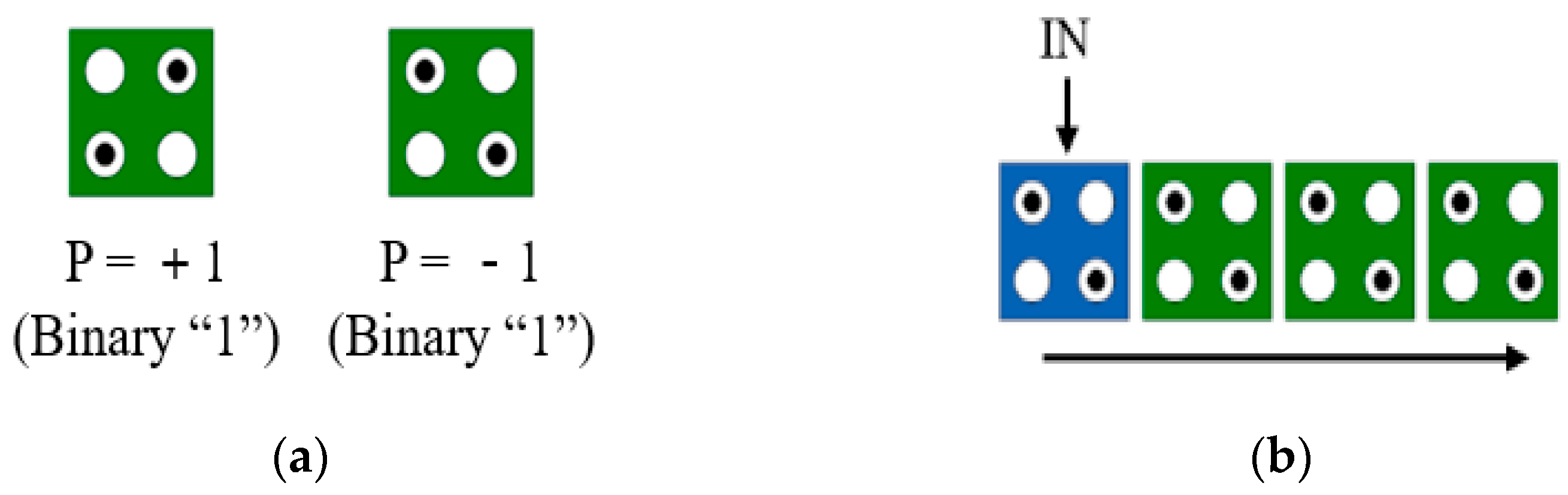

2.1. Background of QCA

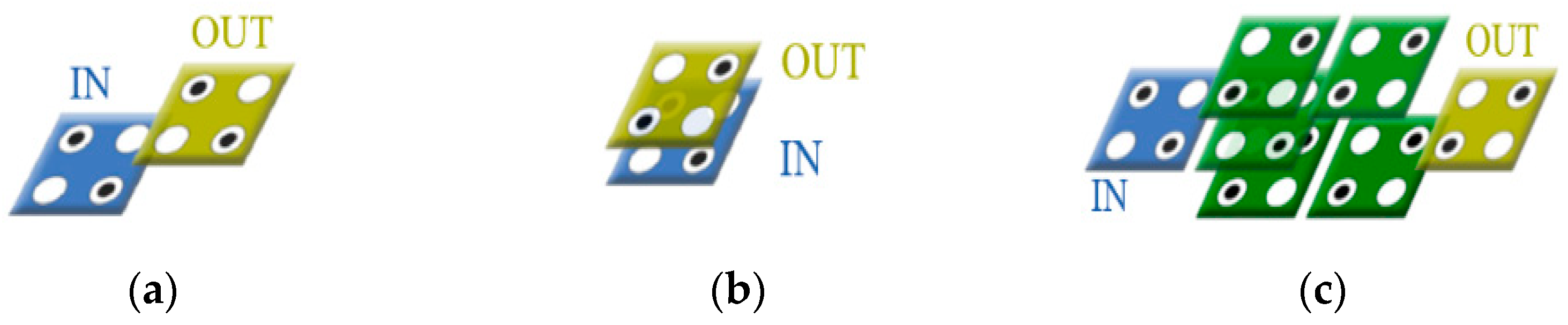

2.2. Multilayer Structure

2.3. Previous QCA Multiplexers and D-Latch

2.4. Previous QCA Shift Register and LFSR Structure

3. The Proposed Structures

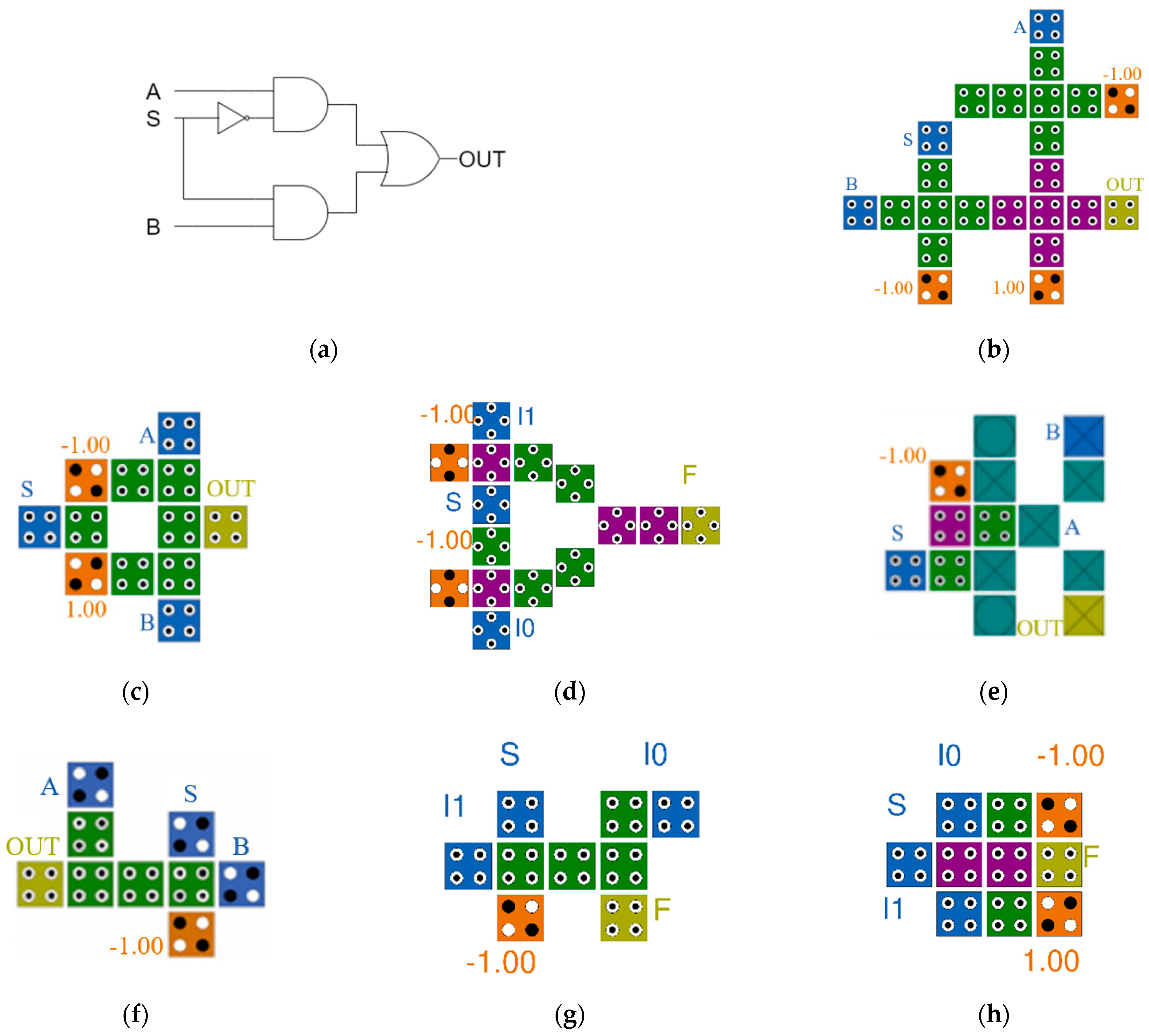

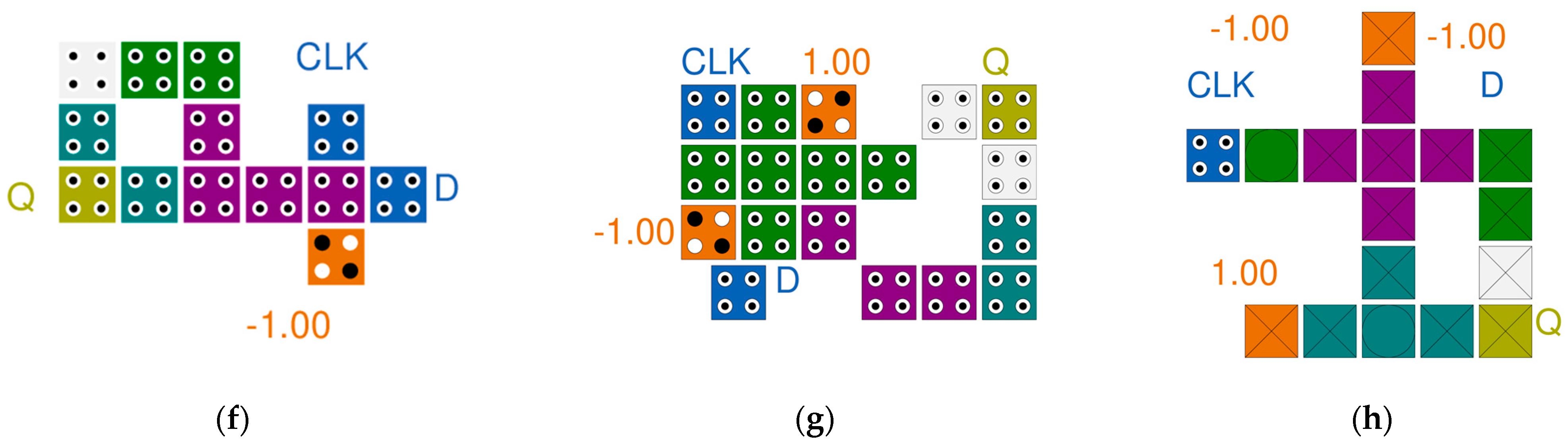

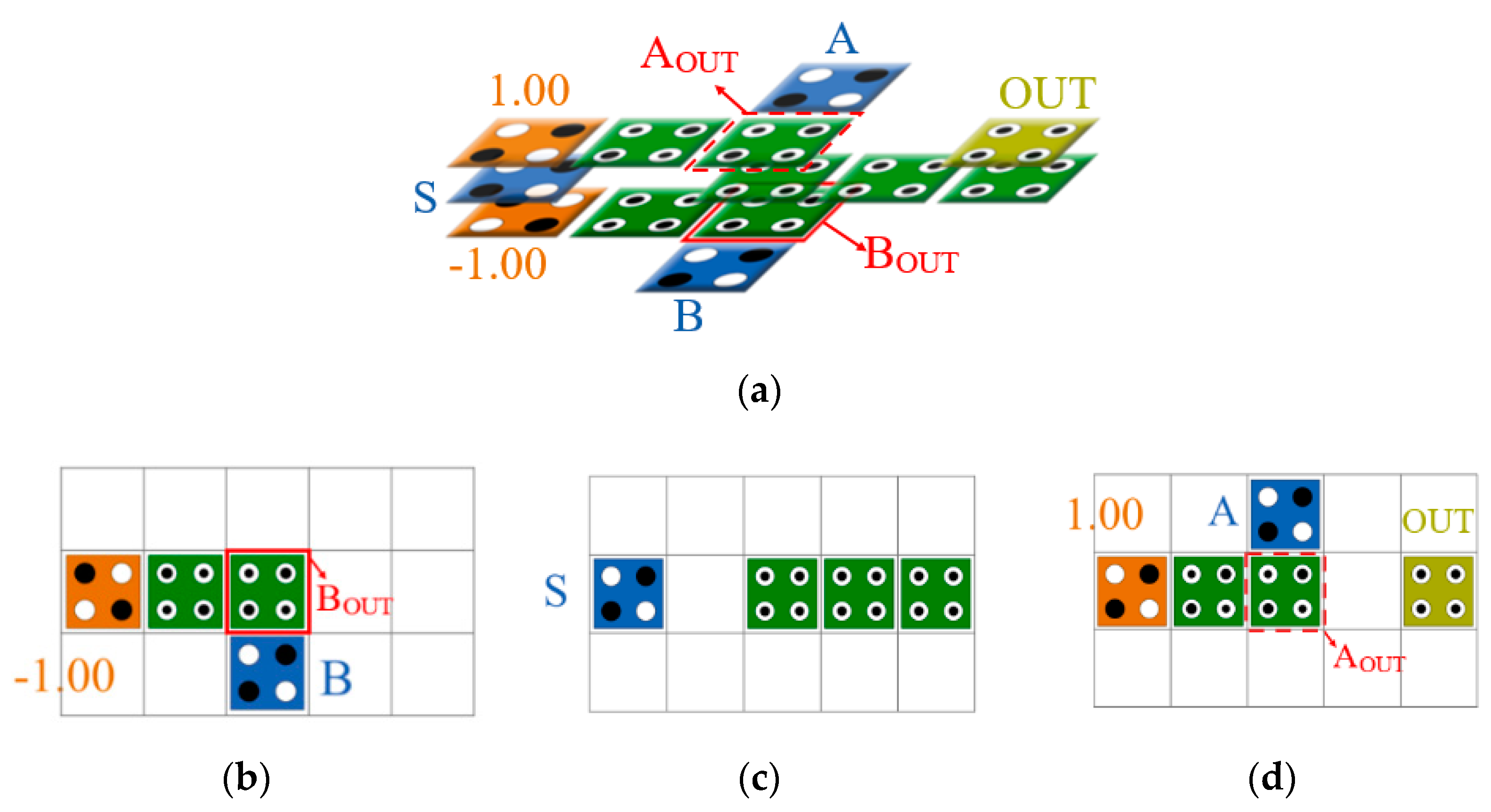

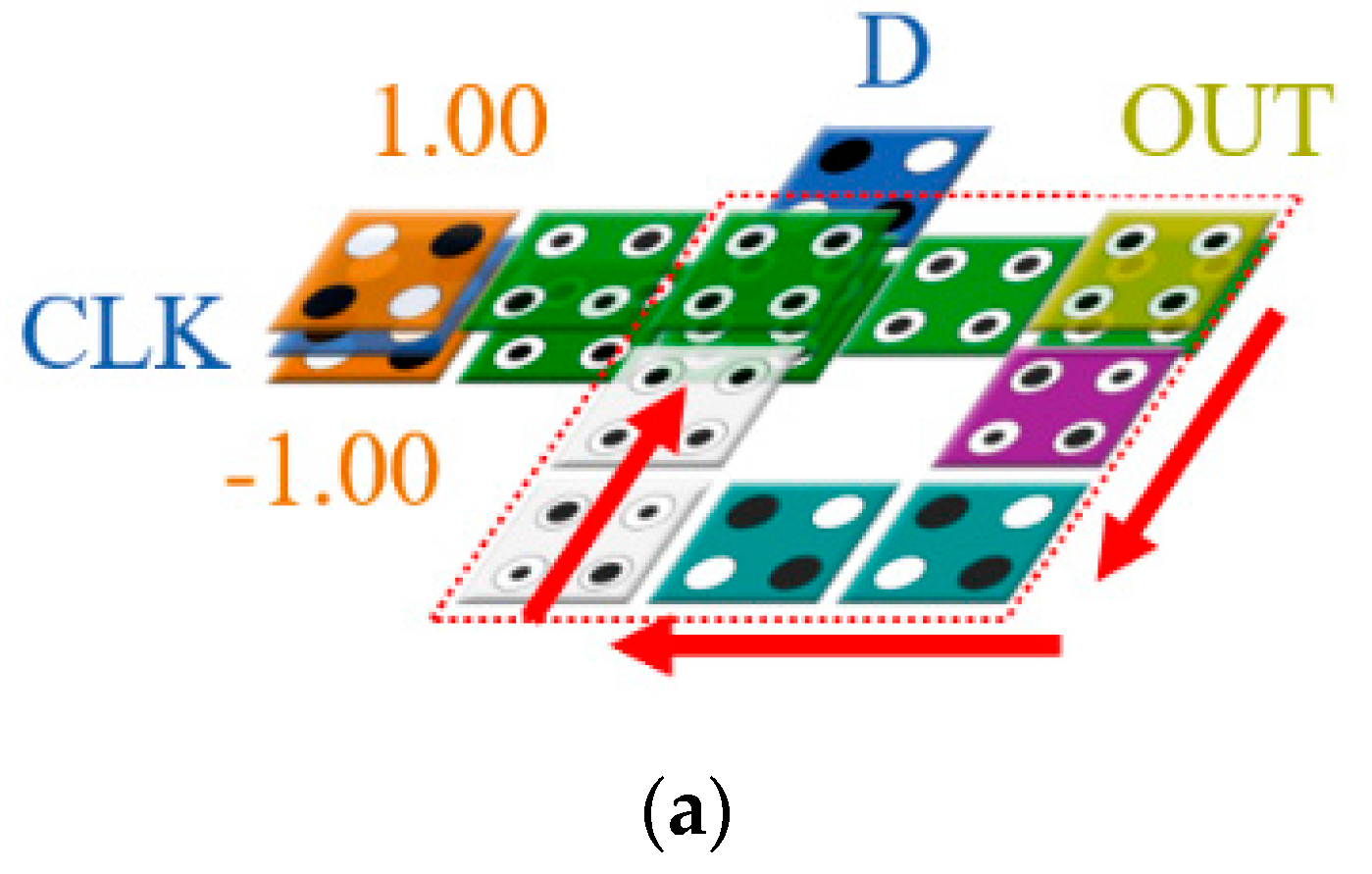

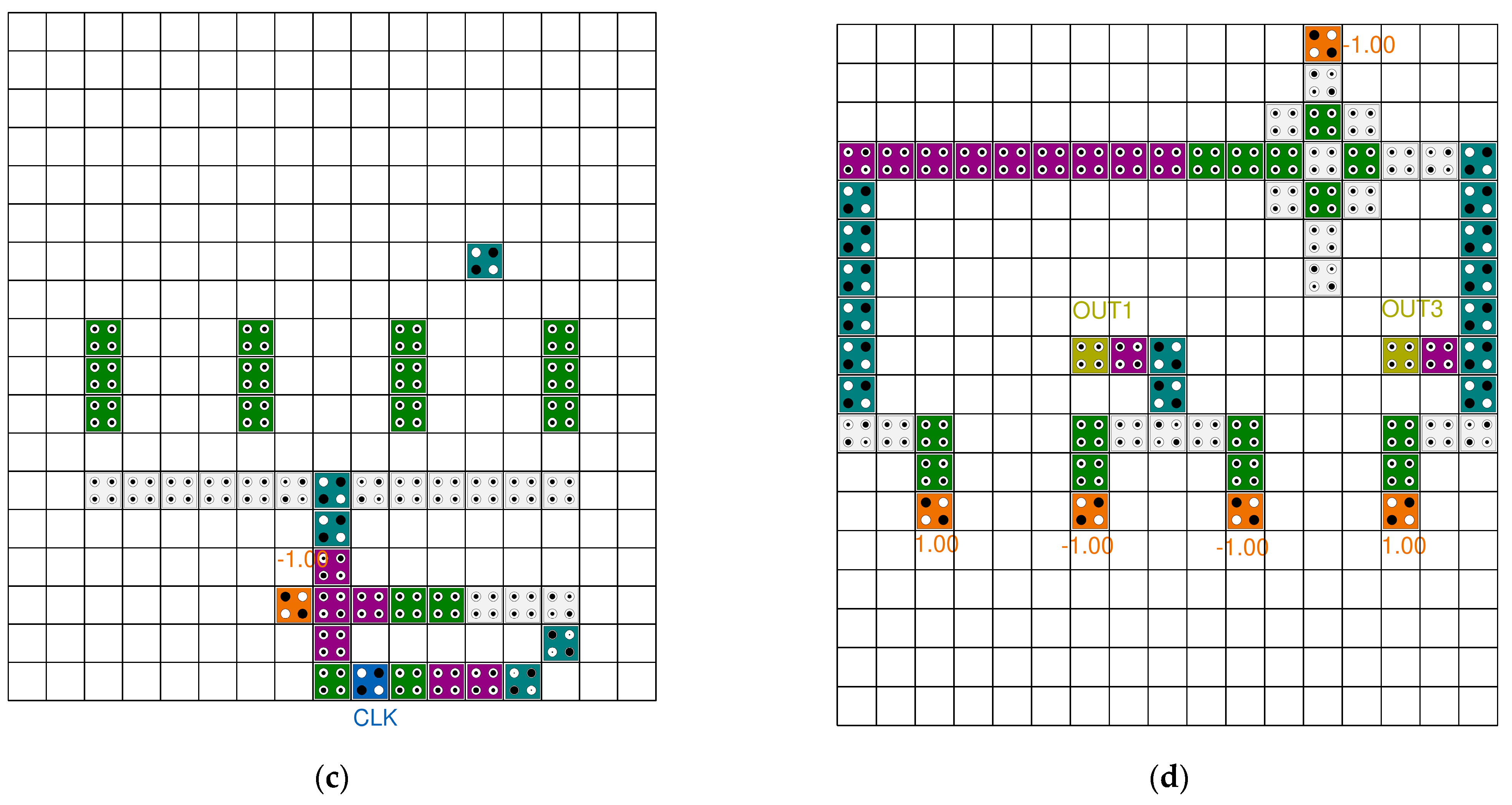

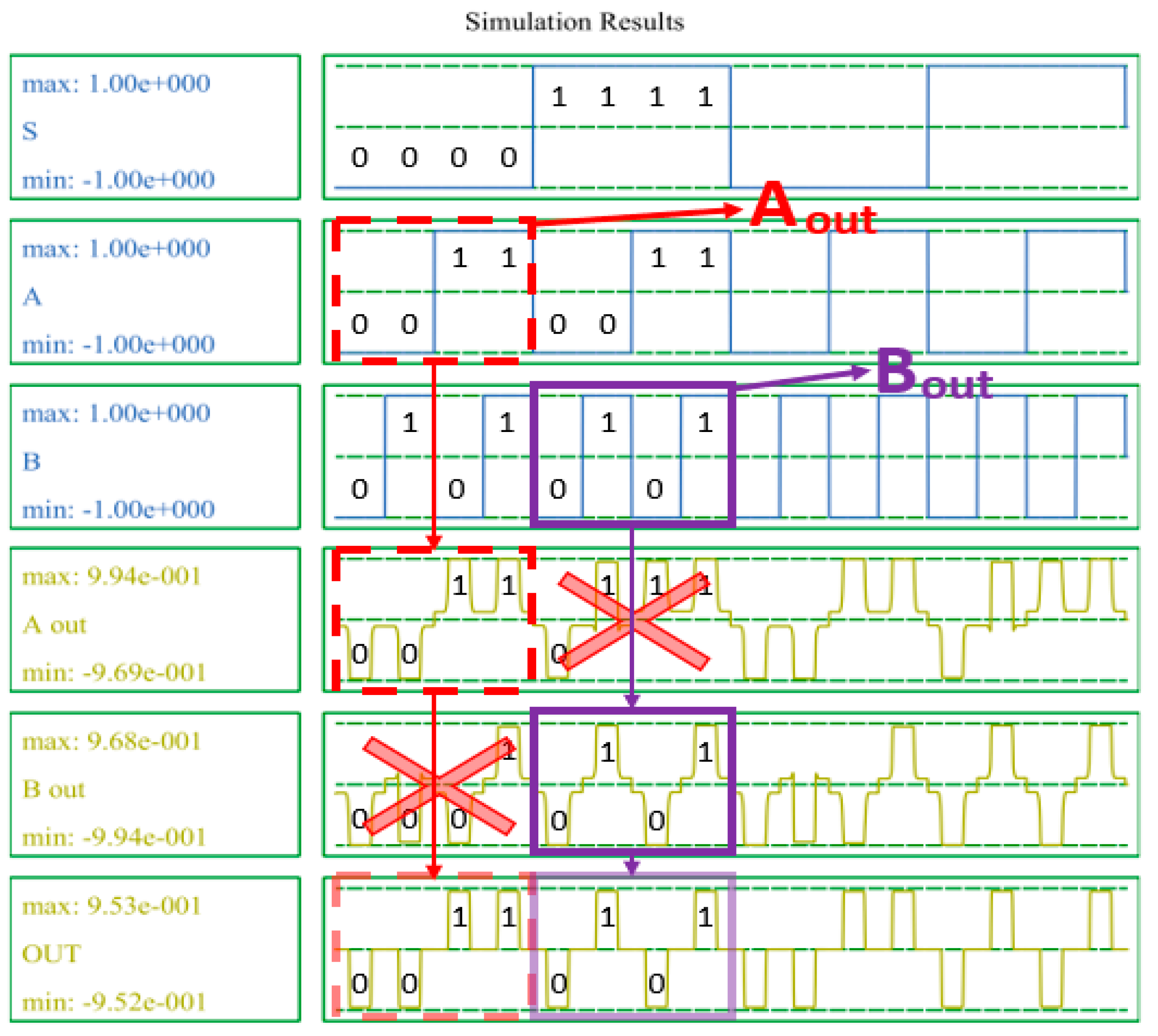

3.1. The Proposed 2-to-1 Multiplier and D-Latch

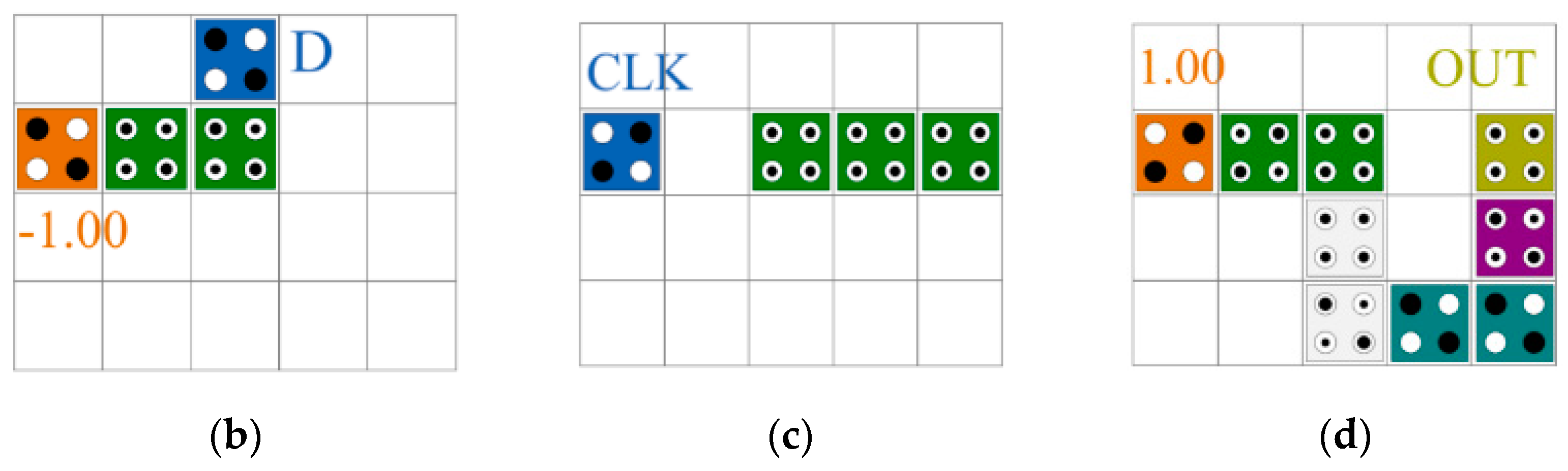

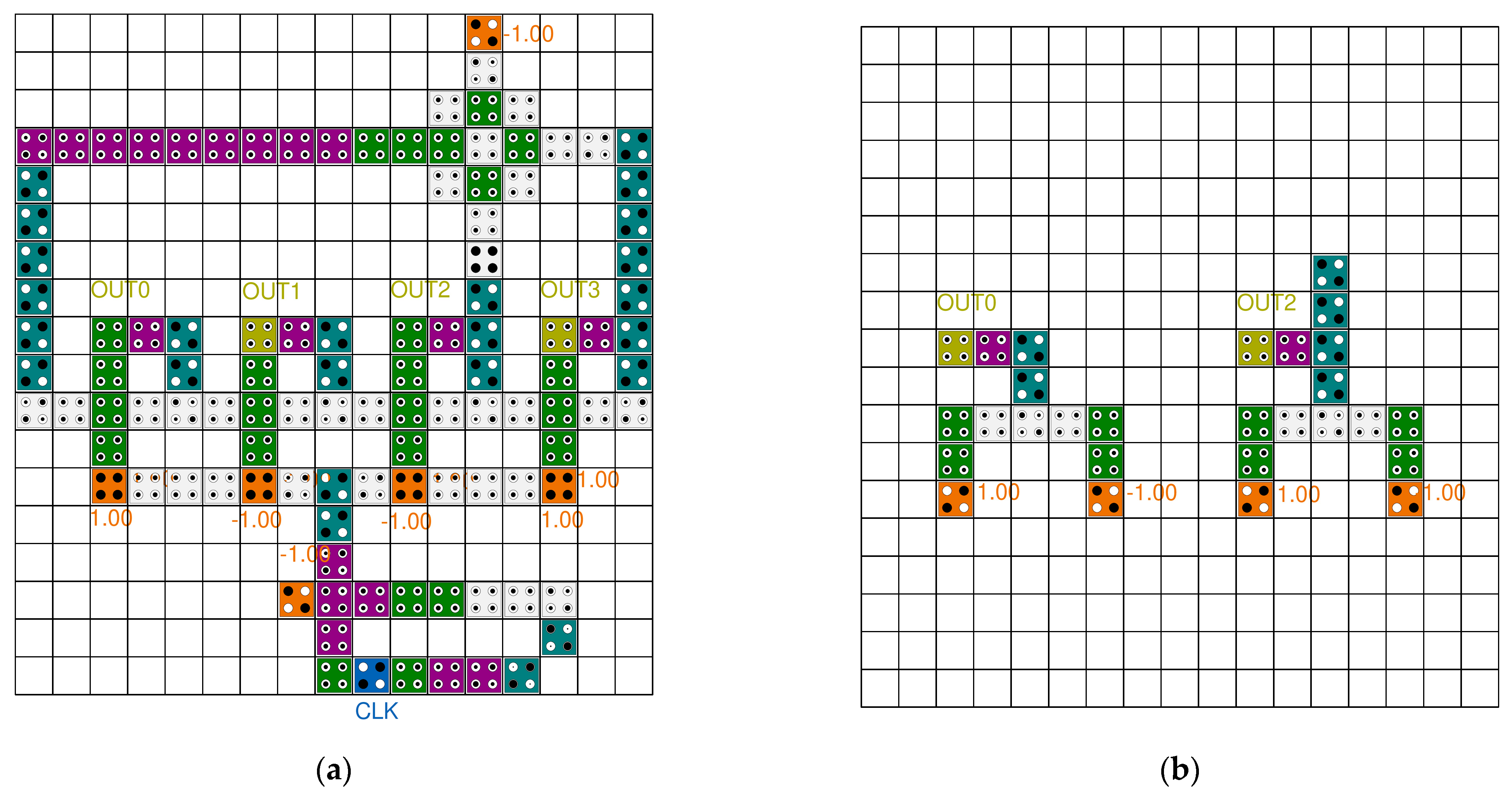

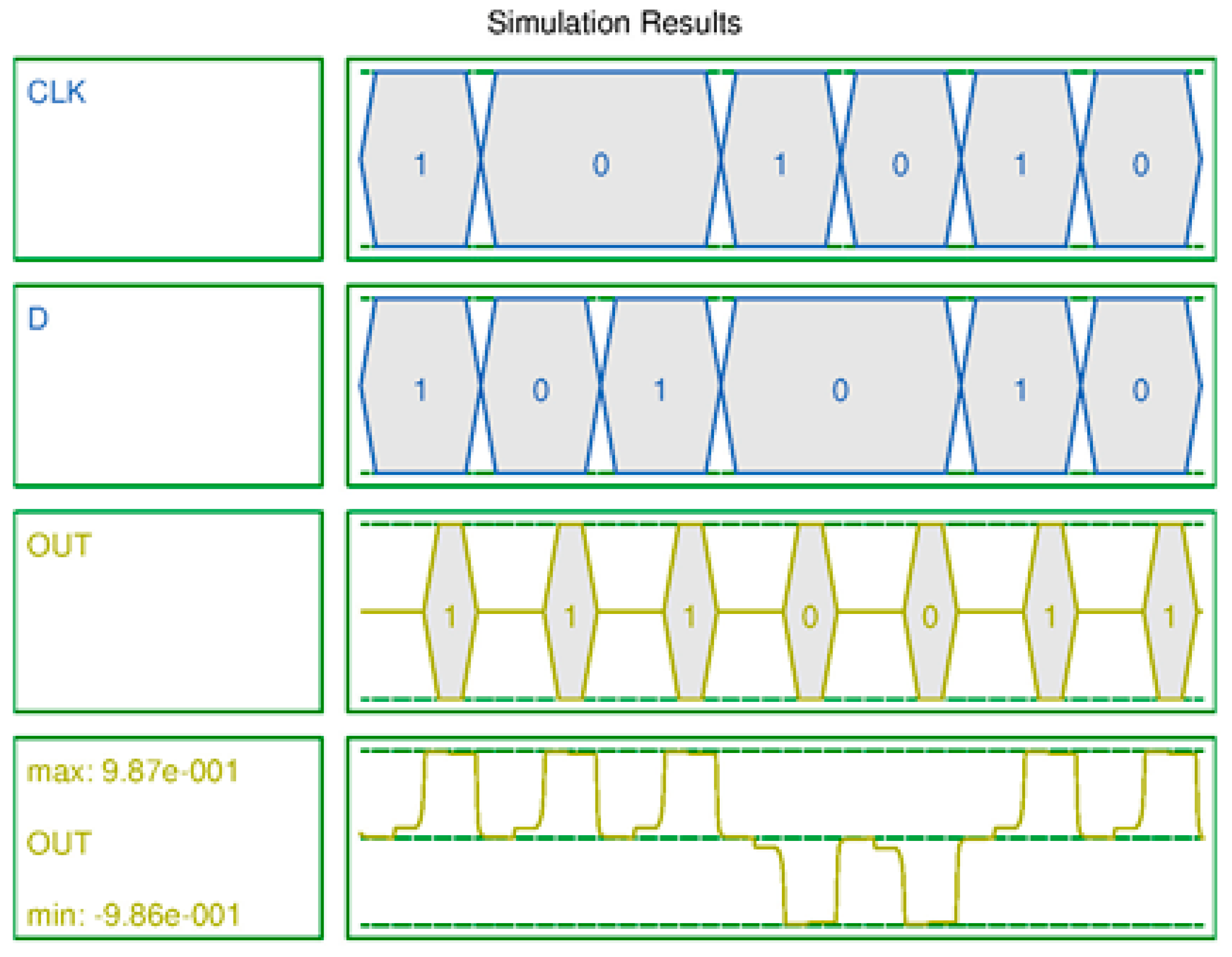

3.2. The Proposed 4-Bit SR and LFSR Structure

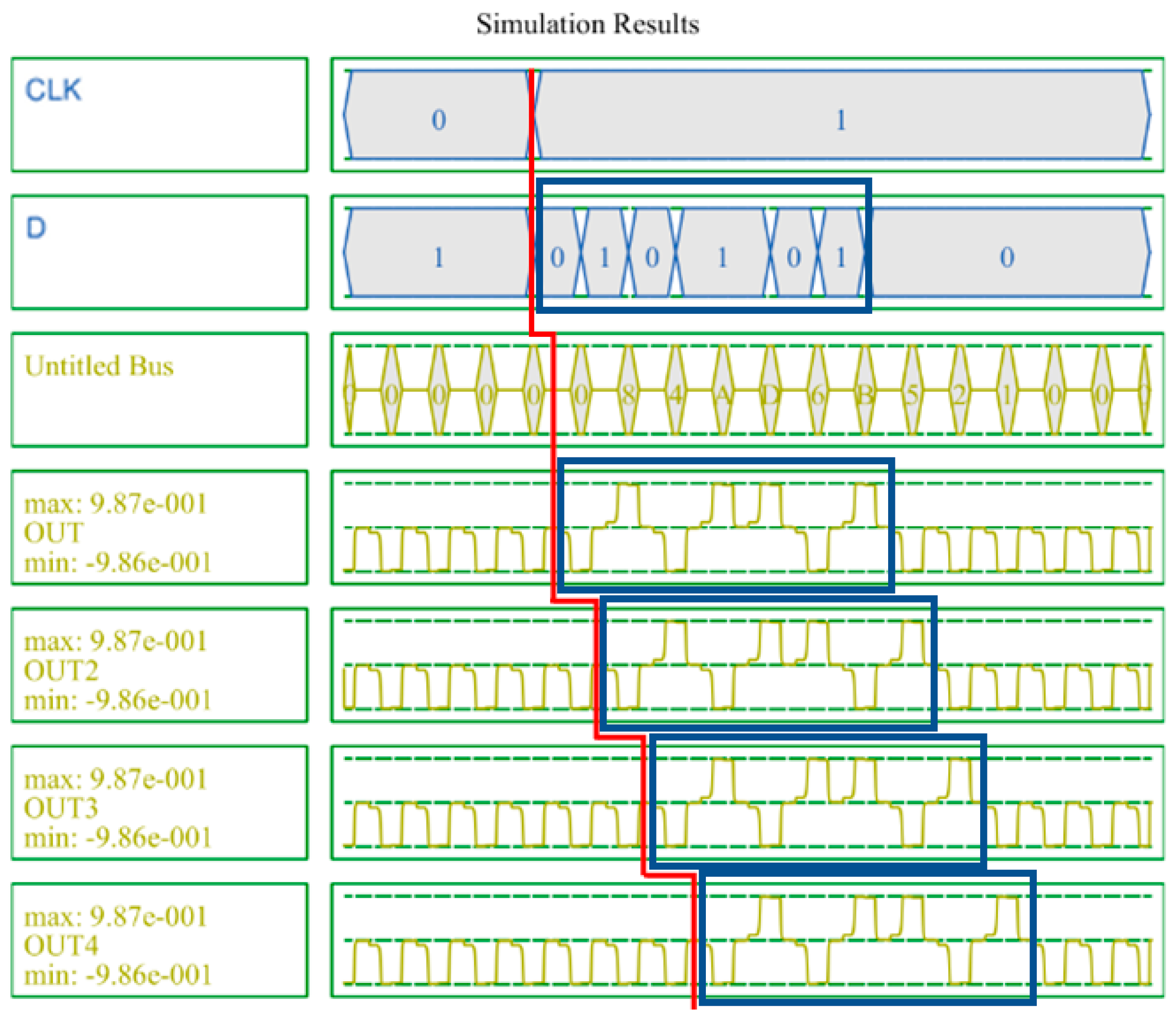

4. Simulation Results and Analyses

4.1. Structural Analysis

4.2. Performance Comparison

4.3. Energy Dissipation Analysis

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Lent, C.S.; Tougaw, P.D.; Porod, W.; Bernstein, G.H. Quantum cellular automata. Nanotechnology 1993, 4, 49–57. [Google Scholar] [CrossRef]

- Lent, C.S.; Tougaw, P.D.; Porod, W. Quantum cellular automata: The physics of computing with arrays of quantum dot molecules. In Proceedings of the Workshop on Physics and Computation, PhysComp ‘94, Dallas, TX, USA, 17–20 November 1994. [Google Scholar]

- Safoev, N.; Jeon, J.C. Design of high-performance QCA incrementer/decrementer circuit based on adder/subtractor meth-odology. Microprocess. Microsyst. 2020, 72, 102927. [Google Scholar] [CrossRef]

- Seyedi, S.; Navimpipour, N.J. Designing a three-level full-adder based on nano-scale quantum dot cellular automata. Photonic Netw. Commun. 2021, 42, 184–193. [Google Scholar] [CrossRef]

- Erniyazov, S.; Jeon, J.C. Carry save adder and carry look ahead adder using inverter chain based coplanar QCA full adder for low energy dissipation. Microelectron. Eng. 2019, 211, 37–43. [Google Scholar] [CrossRef]

- Seyedi, S.; Navimpipour, N.J. Ultra-efficient adders and even parity generators in nano scale. Comput. Electr. Eng. 2021, 96, 107548. [Google Scholar]

- Safoev, N.; Jeon, J.C. Design and Evaluation of Cell Interaction Based Vedic Multiplier Using Quantum-Dot Cellular Automata. Electronics 2020, 9, 1036. [Google Scholar] [CrossRef]

- Almatrood, A.F.; Singh, H. QCA circuit design of n-bit non-restoring binary array divider. J. Eng. 2018, 2018, 348–353. [Google Scholar] [CrossRef]

- Kim, H.I.; Jeon, J.C. Non-Restoring Array Divider Using Optimized CAS Cells Based on Quantum-Dot Cellular Automata with Minimized Latency and Power Dissipation for Quantum Computing. Nanomaterials 2022, 12, 540. [Google Scholar] [CrossRef]

- Safoev, N.; Jeon, J.C. A novel controllable inverter and adder/subtractor in quantum-dot cellular automata using cell inter-action based XOR gate. Microelectron. Eng. 2020, 222, 111197. [Google Scholar] [CrossRef]

- Jeon, J.C. Designing nanotechnology QCA–multiplexer using majority function-based NAND for quantum computing. J. Supercomput. 2021, 77, 1562–1578. [Google Scholar] [CrossRef]

- Sen, B.; Goswami, M.; Mazumdar, S.; Sikdar, B.K. Towards modular design of reliable quantum-dot cellular automata logic circuit using multiplexers. Comput. Electr. Eng. 2015, 45, 42–54. [Google Scholar] [CrossRef]

- Asfestani, M.N.; Heikalabad, S.R. A unique structure for the multiplexer in quantum-dot cellular automata to create a revolution in design of nanostructures. Phys. B Condens. Matter 2017, 512, 91–99. [Google Scholar] [CrossRef]

- Ajitha, D.; VijayaLakshmi, K.N.V.S.; BhagyaLakshmi, K.; Mehetaj, M. 2:1 MUX Implementation Using NMV-Gate: Non Majority Gate in QCA. In Emerging Trends in Electrical, Communications, and Information Technologies; Springer: Singapore, 2020; pp. 557–563. [Google Scholar]

- Mosleh, M. A novel design of multiplexer based on nano-scale quantum-dot cellular automata. Concurr. Comput. Pract. Exp. 2019, 31, e5070. [Google Scholar] [CrossRef]

- Majeed, A.H.; Alkaldy, E.; Zainal, M.S.; Navi, K.; Nor, D. Optimal design of RAM cell using novel 2:1 multiplexer in QCA technology. Circuit World 2019, 46, 147–158. [Google Scholar] [CrossRef]

- Majeed, A.H. An ultra-low complexity of 2: 1 multiplexer block in QCA technology. Indones. J. Electr. Eng. Comput. Sci. 2021, 21, 1341–1346. [Google Scholar] [CrossRef]

- Ahmadpour, S.S.; Mohammad, M.; Heikalabad, S.R. Efficient designs of quantum-dot cellular automata multiplexer and RAM with physical proof along with power analysis. J. Supercomput. 2022, 78, 1672–1695. [Google Scholar] [CrossRef]

- Seyedi, S.; Navimpipour, N.J. An efficient structure for designing a nano-scale fault-tolerant 2:1 multiplexer based on quantum-dot cellular automata. Optik 2022, 251, 168409. [Google Scholar] [CrossRef]

- Abutaleb, M.M. Robust and efficient quantum-dot cellular automata synchronous counters. Microelectron. J. 2017, 61, 6–14. [Google Scholar] [CrossRef]

- Roshan, M.G.; Gholami, M. Novel D Latches and D Flip-Flops with Set and Reset Ability in QCA Nanotechnology Using Minimum Cells and Area. Int. J. Theor. Phys. 2018, 57, 3223–3241. [Google Scholar] [CrossRef]

- Sasamal, T.N.; Singh, A.K.; Ghanekar, U. Design of QCA-Based D Flip Flop and Memory Cell Using Rotated Majority Gate, Smart Innovations in Communication and Computational Sciences. Adv. Intell. Syst. Comput. 2019, 670, 233–247. [Google Scholar]

- Jeon, J.C. Area Efficient Code Converters Based on Quantum-Dot Cellular Automata. Int. J. Civ. Eng. Technol. 2019, 10, 690–701. [Google Scholar]

- Majeed, A.H.; Alkaldy, E.; Zainal, M.S.; Nor, D. Novel Memory Structures in QCA Nano Technology. arXiv 2020, arXiv:2007.01954. [Google Scholar]

- Song, Z.; Xie, G.; Cheng, X.; Wang, L.; Zhang, Y. An Ultra Low Cost Multilayer RAM in Quantum-Dot Cellular Automata. IEEE Trans. Circuits Syst. II Express Briefs 2020, 67, 3397–3401. [Google Scholar] [CrossRef]

- Seo, D.K.; Jeon, J.C. Loop-Based QCA RAM Cell Design Using Multilayer-Based D Latch. J. Korean Inst. Inf. Technol. 2020, 18, 25–31. [Google Scholar] [CrossRef]

- Jeon, J.C. Low Complexity QCA Universal Shift Register Design Using Multiplexer and D Flip-Flop Based on Electronic Correlations. J. Supercomput. 2019, 76, 6438–6452. [Google Scholar] [CrossRef]

- Das, J.C.; De, D. Operational efficiency of novel SISO shift register under thermal randomness in quantum-dot cellular automata design. Microsyst. Technol. 2017, 23, 4155–4168. [Google Scholar] [CrossRef]

- Divshali, M.N.; Rezai, A.; Karimi, A. Towards multilayer QCA SISO shift register based on efficient D-FF circuits. Int. J. Theor. Phys. 2018, 57, 3326–3339. [Google Scholar] [CrossRef]

- Abdullah-Al-Shafi, M.; Ziaur, R. Analysis and modeling of sequential circuits in QCA nano computing: RAM and SISO register study. Solid State Electron. Lett. 2019, 1, 73–83. [Google Scholar] [CrossRef]

- Li, T.; Kornovich, R. An Optimized Design of Serial-Input-Serial-Output (SISO) and Parallel-Input-Parallel-Output (PIPO) Shift Registers Based on Quantum Dot Cellular Automata Nanotechnology. Int. J. Theor. Phys. 2019, 58, 3684–3693. [Google Scholar] [CrossRef]

- Roshan, M.G.; Gholami, M. 4-Bit serial shift register with reset ability and 4-bit LFSR in QCA technology using minimum number of cells and delay. Comput. Electr. Eng. 2019, 78, 449–462. [Google Scholar] [CrossRef]

- Fan, S.; Khamesinia, M.S. An Efficient Design of Parallel and Serial Shift Registers Based on Quantum-Dot Cellular Automata. Int. J. Theor. Phys. 2021, 60, 2400–2411. [Google Scholar] [CrossRef]

- Purkayastha, T.; De, D.; Das, K. A novel pseudo random number generator based cryptographic architecture using quantum-dot cellular automata. Microprocess. Microsyst. 2016, 45, 32–44. [Google Scholar] [CrossRef]

- Senthilnathan, S.; Kumaravel, S. Power-efficient implementation of pseudo-random number generator using quantum dot cellular automata-based D flip flop. Comput. Electr. Eng. 2020, 85, 106658. [Google Scholar] [CrossRef]

- Rezaei, A.; Saharkhiz, H. Design of low power random number generators for quantum-dot cellular automata. Int. J. Nano Dimens. 2016, 7, 308–320. [Google Scholar]

- Mohammadi, H.; Navi, K. Energy-Efficient Single-Layer QCA Logical Circuits Based on a Novel XOR Gate. J. Circuits Syst. Comput. 2018, 27, 1850216. [Google Scholar] [CrossRef]

- Kaviya, M.; Bavithra, S.; Soorya, M.; Sowndarya, S.; Senthilnathan, S. Design of Linear Feedback Shift Register in Quantum Dot Cellular Automata. Int. J. Inf. Comput. Sci. 2019, 6, 2019. [Google Scholar]

- Amirzadeh, Z.; Gholami, M. Analysis and Design of the Pseudo-Random Bit Generator in the Technology of Quantum-Dot Cellular Automata. Int. J. Theor. Phys. 2020, 59, 29–48. [Google Scholar] [CrossRef]

- Walus, K.; Dysart, T.J.; Jullien, G.A.; Budiman, R.A. QCADesigner: A rapid design and simulation tool for quantum-dot cel-lular automata. IEEE Trans. Nanotechnol. 2004, 3, 26–31. [Google Scholar] [CrossRef]

- Qcadesigner-e. Available online: https://github.com/FSillT/QCADesigner-E (accessed on 24 March 2022).

- Torres, F.S.; Wille, R.; Niemann, P.; Drechsler, R. An energy-aware model for the logic synthesis of quantum-dot cellular automata. IEEE Trans. CAD Integr. Circuits Syst. 2018, 3, 3031–3041. [Google Scholar] [CrossRef]

- Timler, J.; Lent, C.S. Power gain and dissipation in quantum-dot cellular automata. J. Appl. Phys. 2002, 91, 823–831. [Google Scholar] [CrossRef] [Green Version]

- Timler, J.; Lent, C.S. Maxwell’s demon and quantum-dot cellular automata. J. Appl. Phys. 2003, 94, 1050–1060. [Google Scholar] [CrossRef] [Green Version]

- Srivastava, S.; Asthana, A.; Bhanja, S.; Sarkar, S. QCAPro-an error power estimation tool for QCA circuit design. In Proceedings of the IEEE International Symposium Circuits System 2011, Rio de Janeiro, Brazil, 15–18 May 2011. [Google Scholar]

| Inverters | Cell Count | Area (nm2) | Signal Strength (10−1 J) | Structure |

|---|---|---|---|---|

| Figure 2a | 2 | 1444 | 5.62 | Coplanar |

| Figure 2b | 7 | 4758 | 7.75 | Coplanar |

| Figure 3b | 2 | 324 | 9.69 | Multi-layer |

| Figure 3c | 7 | 1404 | 8.42 | Multi-layer |

| S | A | B | OUT |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | |

| 1 | 0 | 1 | |

| 1 | 1 | 1 | |

| 1 | 0 | 0 | 0 |

| 0 | 1 | 1 | |

| 1 | 0 | 0 | |

| 1 | 1 | 1 |

| CLK | D | OUT |

|---|---|---|

| 0 | 0 | OUT(t − 1) |

| 1 | OUT(t − 1) | |

| 1 | 0 | 0 |

| 1 | 1 |

| Parameters | Bistable Approximation | Coherence Vector |

|---|---|---|

| Cell size | 18 nm | 18 nm |

| Dot diameter | 5 nm | 5 nm |

| Cell separation | 2 nm | 2 nm |

| Layer separation | 11.5 nm | 11.5 nm |

| Clock high | 9.8 × 10−22 J | 9.8 × 10−22 J |

| Clock low | 3.8 × 10−23 J | 3.8 × 10−23 J |

| Clock shift | 0 | 0 |

| Clock amplitude factor | 2.0 | 2.0 |

| Relative permittivity | 12.9 | 12.9 |

| Radius of effect | 65 nm | 80 nm |

| Circuit | Cell Count | Area (nm2) | Latency (Clock Cycle) | Cost (Area × Latency) | Structure |

|---|---|---|---|---|---|

| [12] | 23 | 24,964 | 0.50 | 12,482 | coplanar |

| [13] | 12 | 9604 | 0.25 | 2401 | coplanar |

| [14] | 15 | 16,284 | 0.50 | 8142 | coplanar |

| [15] | 21 | 9604 | 0.75 | 7203 | multi-layer |

| [16] | 9 | 7644 | 0.25 | 1911 | coplanar |

| [17] | 9 | 5684 | 0.25 | 1421 | coplanar |

| [18] | 10 | 4524 | 0.50 | 2262 | coplanar |

| Figure 10 | 13 | 5684 | 0.25 | 1421 | multi-layer |

| Circuit | Cell Count | Area (nm2) | Latency (Clock Cycle) | Cost (Area × Latency) | Structure |

|---|---|---|---|---|---|

| [20] | 28 | 24,964 | 0.50 | 12,482 | coplanar |

| [21] | 19 | 16,284 | 0.75 | 12,213 | coplanar |

| [22] | 23 | 21,804 | 0.75 | 16,353 | coplanar |

| [23] | 24 | 18,644 | 1.00 | 18,644 | coplanar |

| [24] | 13 | 9204 | 0.75 | 6903 | coplanar |

| [25] | 18 | 9204 | 1.00 | 9204 | coplanar |

| [26] | 27 | 13,924 | 1.00 | 13,924 | multilayer |

| Figure 11 | 17 | 7644 | 0.50 | 3822 | multilayer |

| Circuit | Cell Count | Area (nm2) | Latency (Clock Cycle) | Cost (Area × Latency) | Bits | Cost/bit | Type | Structure |

|---|---|---|---|---|---|---|---|---|

| [28] | 102 | 81,844 | 3.00 | 245,532 | 3 | 81,844 | SISO | coplanar |

| [29] | 127 | 108,564 | 3.00 | 325,692 | 3 | 108,564 | SISO | coplanar |

| [30] | 105 | 134,524 | 2.75 | 369,944 | 3 | 123,315 | SISO | coplanar |

| [31] | 120 | 28,124 | 3.00 | 84,372 | 3 | 28,124 | SISO | multilayer |

| [32] | 92 | 68,724 | 3.75 | 257,715 | 4 | 64,429 | SIPO | coplanar |

| [33] | 177 | 149,124 | 2.00 | 298,248 | 3 | 99,416 | PIPO | coplanar |

| Figure 12 | 80 | 33,124 | 0.75 | 24,843 | 4 | 6210 | SIPO | multilayer |

| Circuit | Cell Count | Area (nm2) | Latency (Clock Cycle) | Cost (Area ✕ Latency) | Bits | Cost/bit | Type | Structure |

|---|---|---|---|---|---|---|---|---|

| [36] | 440 | 958,324 | 1.25 | 1,197,905 | 5 | 239,581 | Latch | multilayer |

| [37] | 191 | 230,044 | 1.25 | 287,555 | 3 | 95,852 | Latch | coplanar |

| [38] | 472 | 918,924 | 0.75 | 689,193 | 8 | 86,149 | Latch | coplanar |

| [39] | 226 | 275,044 | 2.00 | 550,088 | 4 | 137,522 | F/F | coplanar |

| Figure 13 | 120 | 87,204 | 0.75 | 65,403 | 4 | 16,351 | Latch | multilayer |

| Figure 14 | 136 | 121,004 | 1.50 | 181,506 | 4 | 45,377 | F/F | multilayer |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kim, H.-I.; Jeon, J.-C. Quantum LFSR Structure for Random Number Generation Using QCA Multilayered Shift Register for Cryptographic Purposes. Sensors 2022, 22, 3541. https://doi.org/10.3390/s22093541

Kim H-I, Jeon J-C. Quantum LFSR Structure for Random Number Generation Using QCA Multilayered Shift Register for Cryptographic Purposes. Sensors. 2022; 22(9):3541. https://doi.org/10.3390/s22093541

Chicago/Turabian StyleKim, Hyun-Il, and Jun-Cheol Jeon. 2022. "Quantum LFSR Structure for Random Number Generation Using QCA Multilayered Shift Register for Cryptographic Purposes" Sensors 22, no. 9: 3541. https://doi.org/10.3390/s22093541

APA StyleKim, H.-I., & Jeon, J.-C. (2022). Quantum LFSR Structure for Random Number Generation Using QCA Multilayered Shift Register for Cryptographic Purposes. Sensors, 22(9), 3541. https://doi.org/10.3390/s22093541