A Hybrid Bipolar Active Charge Balancing Technique with Adaptive Electrode Tissue Interface (ETI) Impedance Variations for Facial Paralysis Patients †

Abstract

:1. Introduction

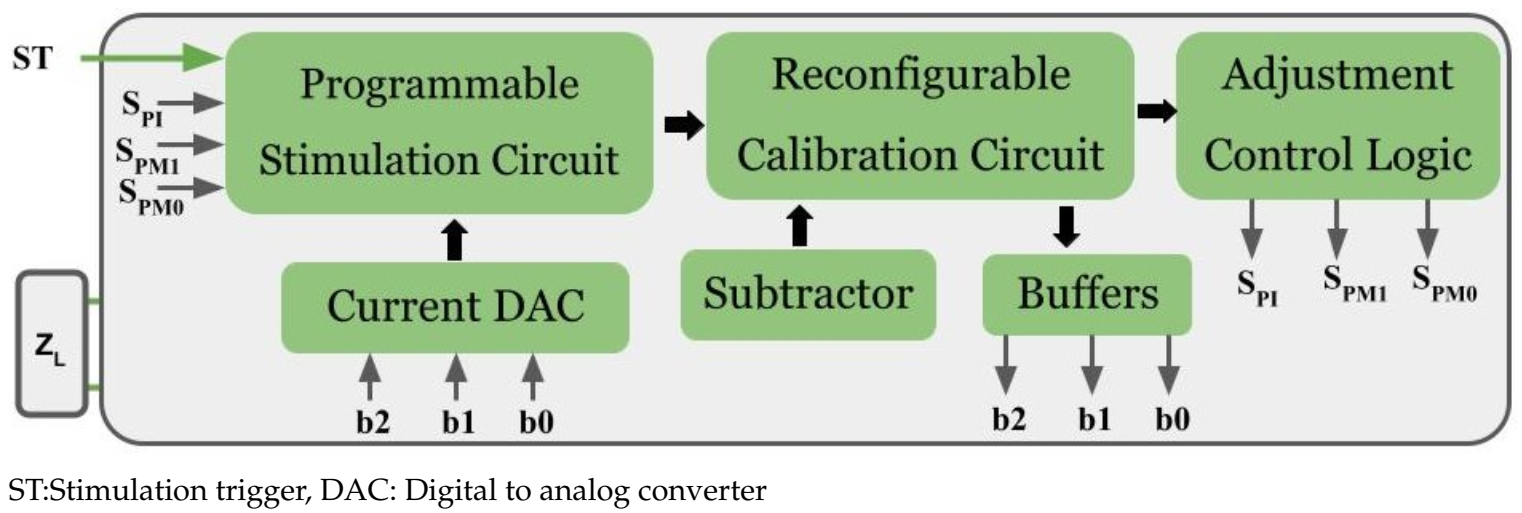

2. Proposed Architecture

- Phase-1:Before stimulation, ETI impedance is calculated and adjusts the stimulation current (in IMM mode). Different patients require different stimulation current to excite the eyelid muscles.

- Phase-2: Adjusted stimulation current applied in the form of a biphasic waveform (in stimulation mode).

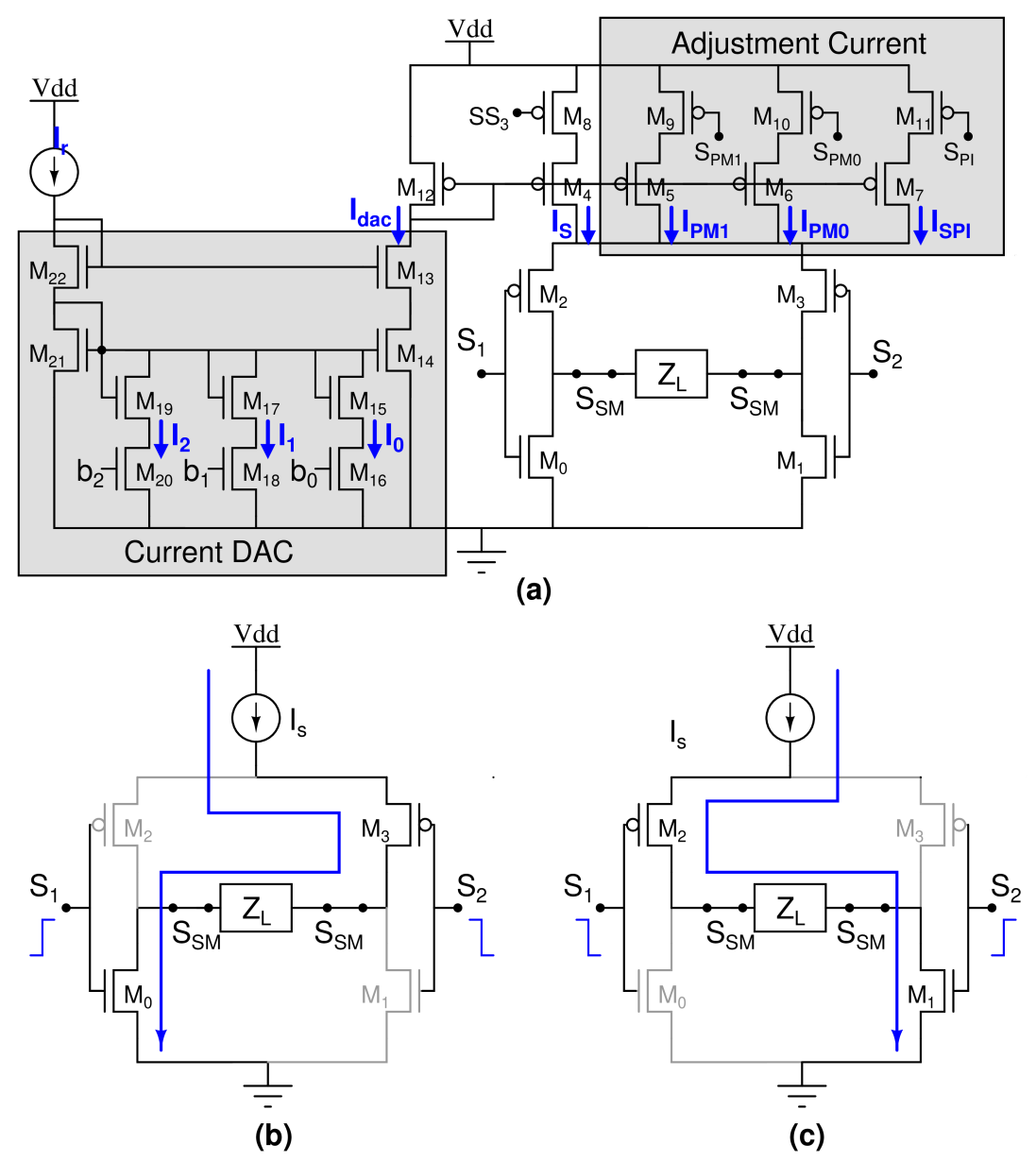

- Phase-3: After stimulation, residual voltage is calculated and nullified/reduced to a safe level (in HCBM mode). If the residual voltage is greater than 100 mV, it leads to tissue damage. Therefore, it is necessary to maintain the residual voltage within safety limits (<100 mV).

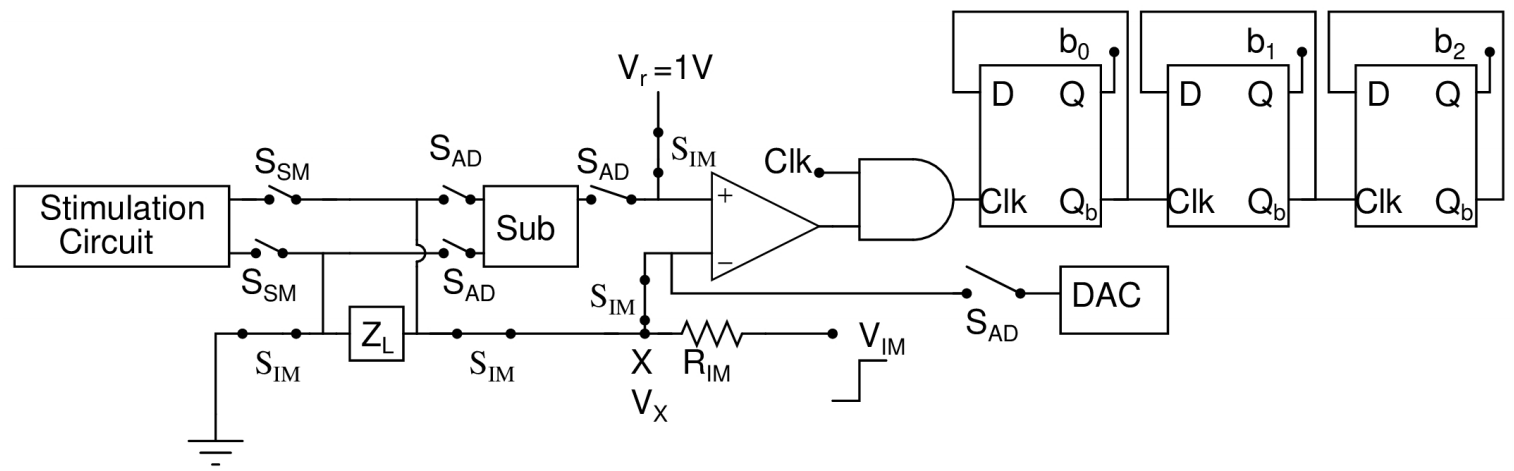

3. Impedance Measuring Mode (IMM)

4. Calculation of ETI Impedance in IMM Mode

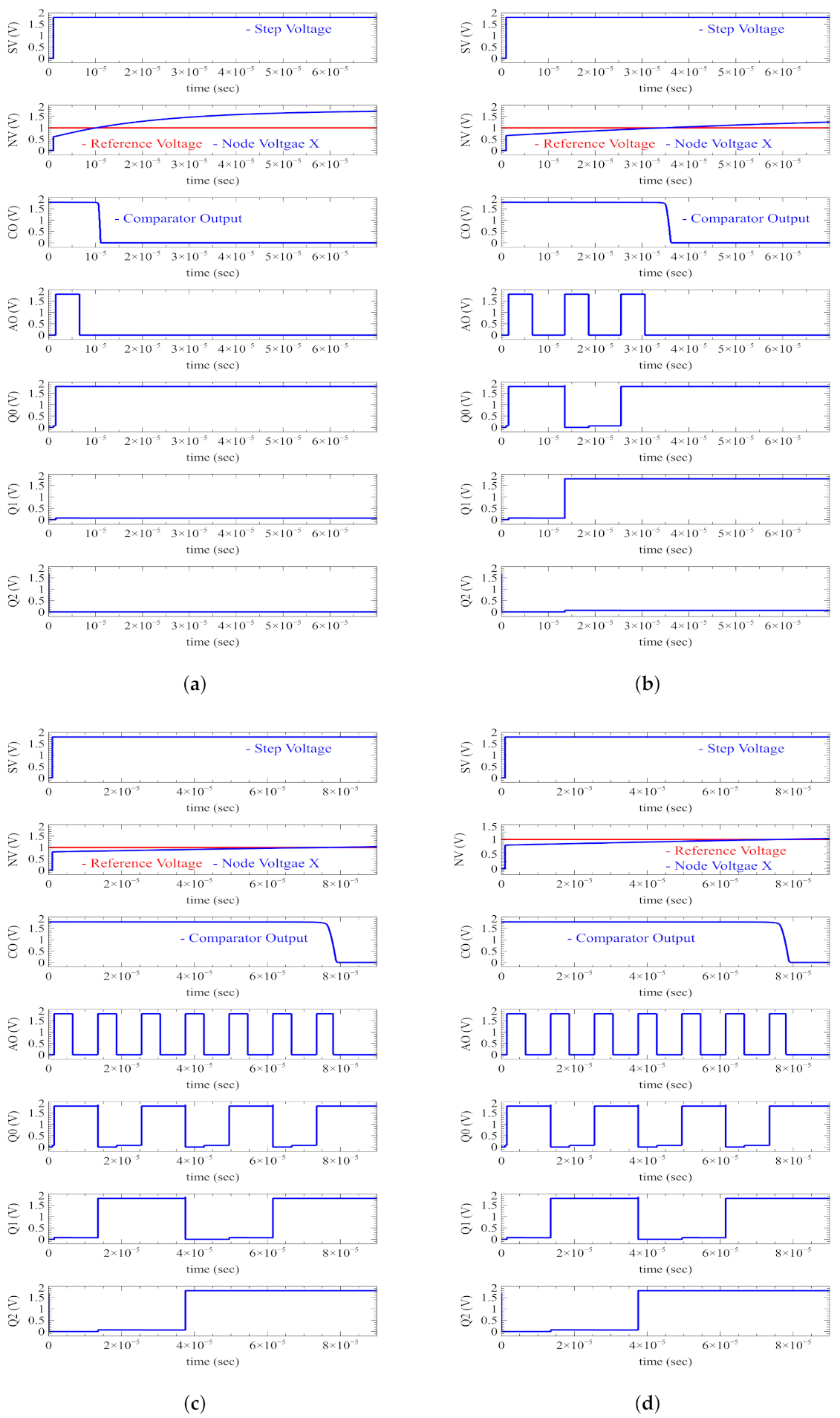

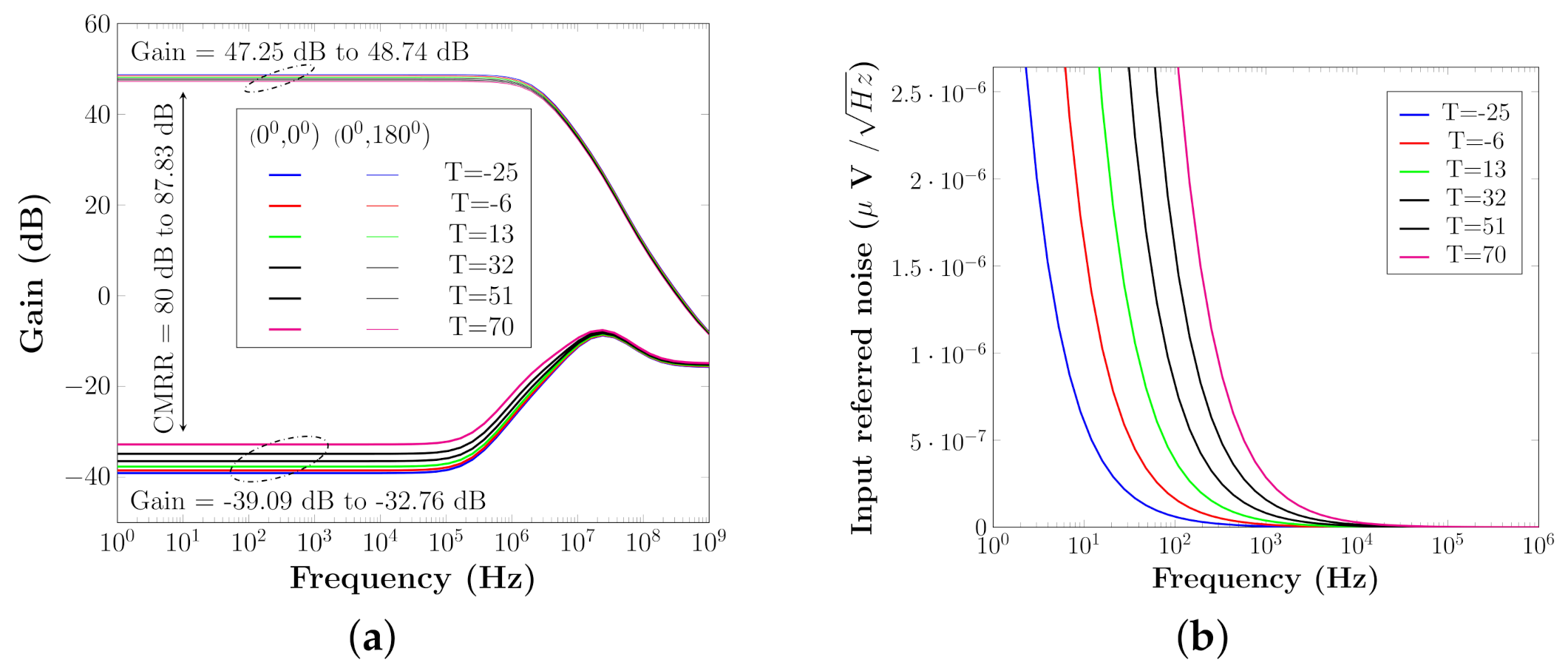

- The ETI impedance is assumed as the resistor () series with capacitor ().

- The capacitor () is uncharged, i.e., the initial load voltage, , is 0.

- The clock pulse is applied to an input of the AND gate.

5. Estimation of Stimulation Current in IMM Mode

6. Stimulation Mode (SM)

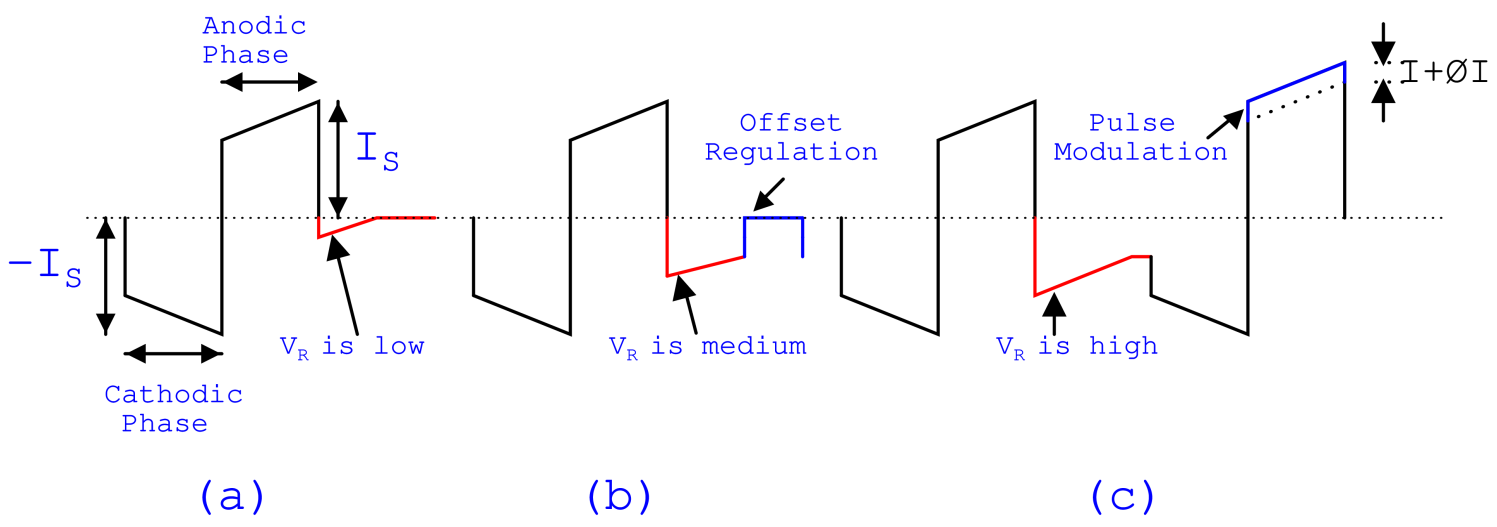

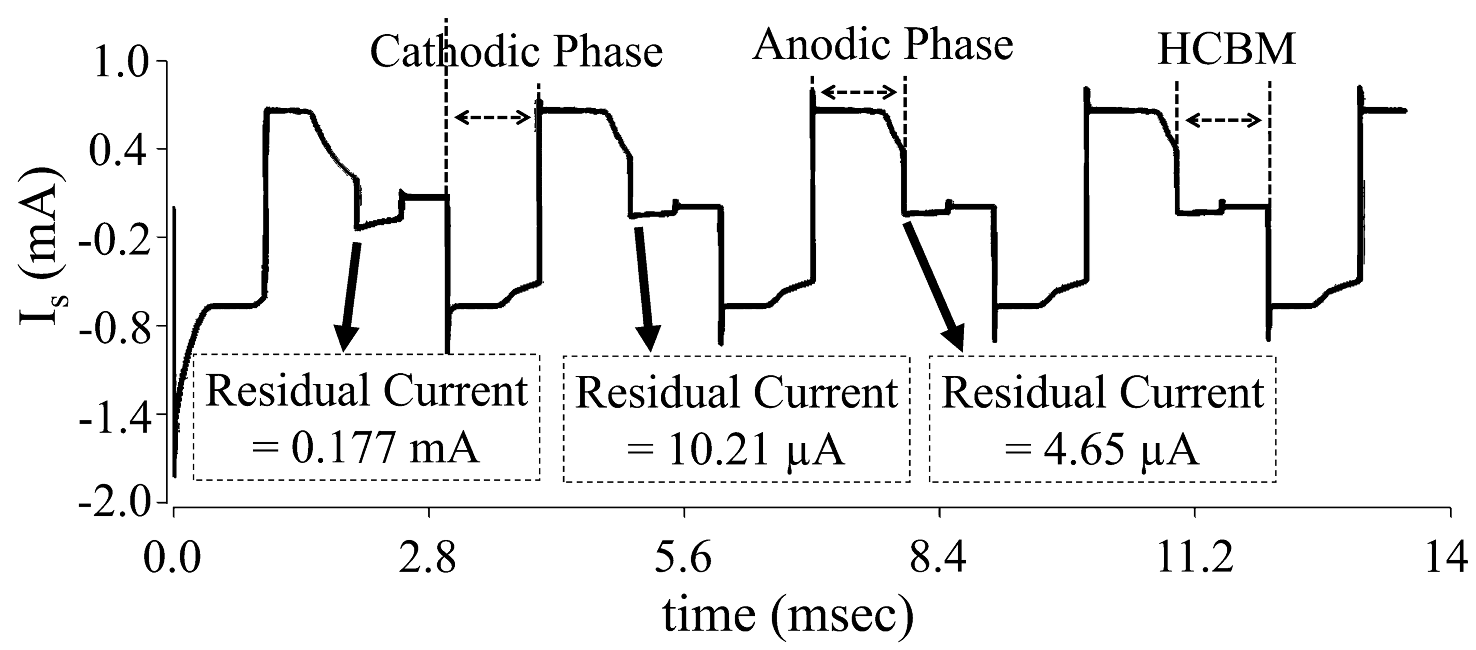

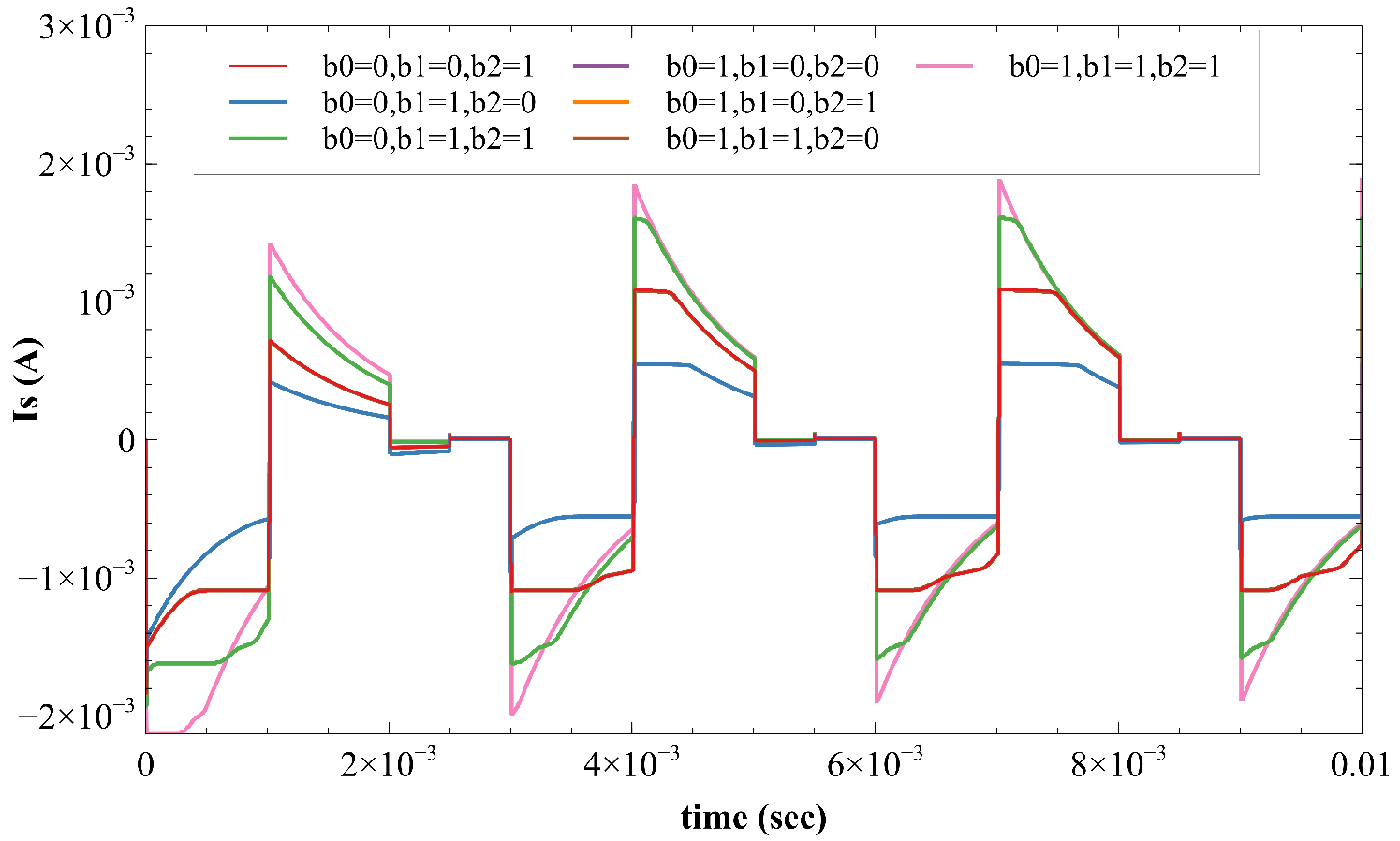

7. Hybrid Charge Balancing Mode

- Case 1—Pulse modulation: In this case, the circuit can adjust a maximum current of 175 µA when SPM1 and SPM0 are turned ON.

- Case 2—Offset regulation: In this case, the circuit can adjust a maximum current of 75 µA when the SPI switch is turned ON.

- Case 3—Electrode shorting: In this case, the circuit will not provide any current adjustment. It can only provide a discharge path for the electrode.

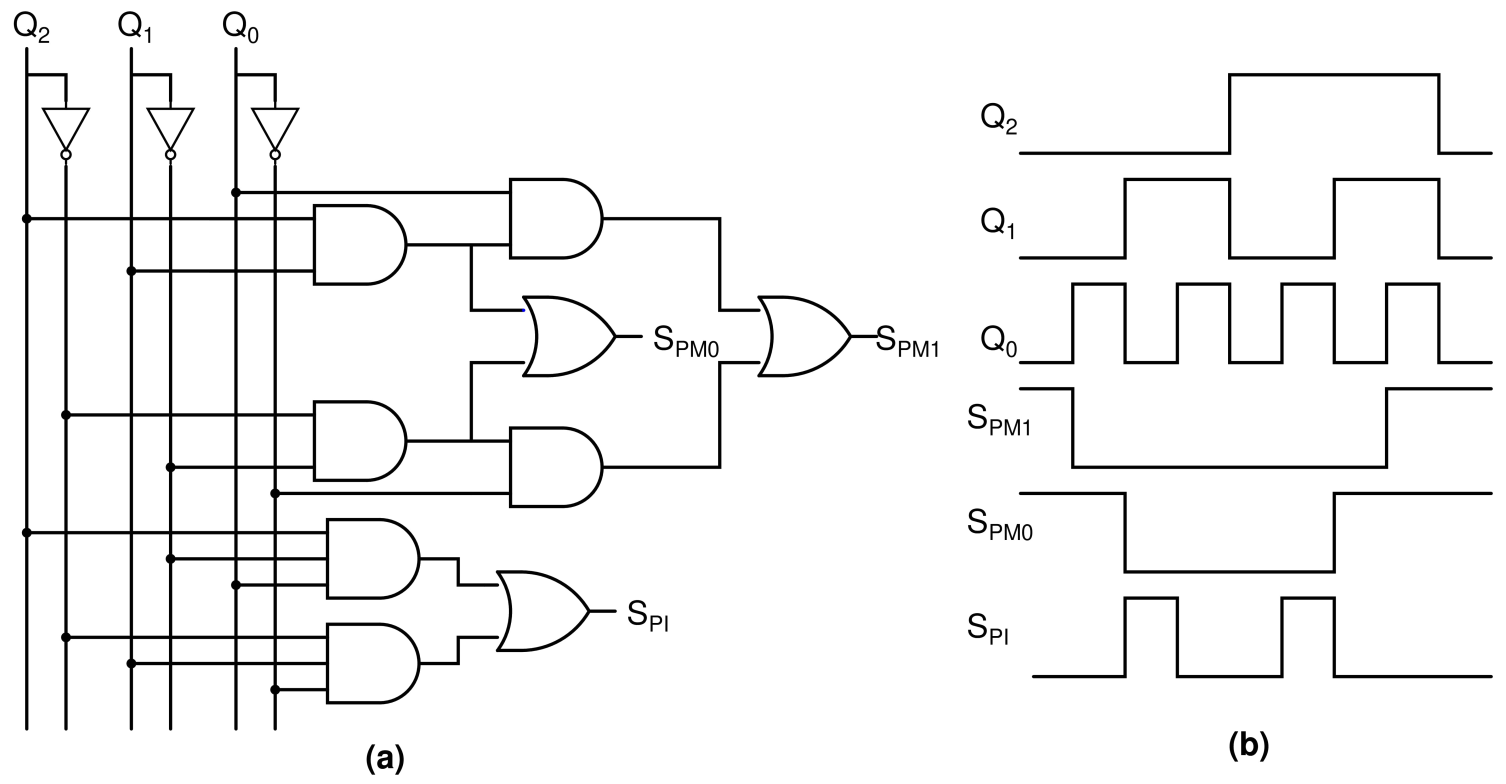

8. Adjustment Control Unit

9. Results

10. Conclusions

11. Patents

- Ganesh Lakshamana Kumar Moganti, V. N. Siva Praneeth, and Siva Rama Krishna Vanjari, “A Hybrid Charge Balancing Technique with Adaptive ETI Impedance Variations for Facial Paralysis Patients”, in Official Journal of The Patent Office, Indian Patent Office, filed and published on 10 September 2021.

- Ganesh Lakshamana Kumar Moganti, V. N. Siva Praneeth, and Siva Rama Krishna Vanjari “An Implantable Bipolar Active Charge Balancing Circuit with Six Adjustment Current levels for Facial Paralysis Patients”, in Official Journal of The Patent Office, Indian Patent Office, filed and published on 23 July 2021.

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

Abbreviations

| ETI | Electrode Tissue Interface |

| FES | Functional Electrical Stimulation |

| IMM | Impedance Measurement Mode |

| HCBM | Hybrid Charge Balancing Mode |

| SM | Stimulation Mode |

| DAC | Digital to Analog Converter |

| RVM | Residual Voltage Measure |

| BPM | Bipolar Modulation |

| ES | Electrode Shorting |

| ACM | Anodic Current Modulation |

| OR | Offset Regulation |

| DBC | DC Blocking Capacitor |

| PA | Pre-amplifier |

References

- Grosheva, M.; Beutner, D.; Volk, G.; Wittekindt, C.; Guntinas-Lichius, O. Die idiopathische fazialisparese. HNO 2010, 58, 419–425. [Google Scholar] [CrossRef] [PubMed]

- Myers, E.N.; de Diego, J.I.; Prim, M.P.; Madero, R.; Gavilaan, J. Seasonal patterns of idiopathic facial paralysis: A 16-year study. Otolaryngol.-Head Neck Surg. 1999, 120, 269–271. [Google Scholar] [CrossRef]

- Bleicher, J.N.; Hamiel, S.; Gengler, J.S.; Antimarino, J. A survey of facial paralysis: Etiology and incidence. Ear Nose Throat J. 1996, 75, 355–358. [Google Scholar] [CrossRef] [PubMed]

- Katusic, S.K.; Beard, C.M.; Wiederholt, W.; Bergstralh, E.J.; Kurland, L.T. Incidence, clinical features, and prognosis in bell’s palsy, rochester, minnesota, 1968–1982. Ann. Neurol. Off. J. Am. Neurol. Assoc. Child Neurol. 1986, 20, 622–627. [Google Scholar] [CrossRef] [PubMed]

- Peitersen, E. Bell’s palsy: The spontaneous course of 2,500 peripheral facial nerve palsies of different etiologies. Acta Oto-Laryngol. 2002, 122, 4–30. [Google Scholar] [CrossRef]

- Bylund, N.; Jensson, D.; Enghag, S.; Berg, T.; Marsk, E.; Hultcrantz, M.; Hadziosmanovic, N.; Rodriguez-Lorenzo, A.; Jonsson, L. Synkinesis in bell’s palsy in a randomised controlled trial. Clin. Otolaryngol. 2017, 42, 673–680. [Google Scholar] [CrossRef] [PubMed]

- Cockerham, K.; Aro, S.; Liu, W.; Pantchenko, O.; Olmos, A.; Oehlberg, M.; Sivaprakasam, M.; Crow, L. Application of mems technology andengineering in medicine: A new paradigm for facial muscle reanimation. Expert Rev. Med. Devices 2008, 5, 371–381. [Google Scholar] [CrossRef] [PubMed]

- Cunningham, S.; Teller, D. Facial nerve paralysis: Ocular management. In Grand Rounds Presentation of UTMB; UTMB Health: Galveston, TX, USA, 2006. [Google Scholar]

- May, M. Gold weight and wire spring implants as alternatives to tars-orrhaphy. Arch. Otolaryngol.-Head Neck Surg. 1987, 113, 656–660. [Google Scholar] [CrossRef] [PubMed]

- Abell, K.M.; Baker, R.S.; Cowen, D.E.; Porter, J.D. Efficacy of goldweight implants in facial nerve palsy: Quantitative alterations in blinking. Vis. Res. 1998, 38, 3019–3023. [Google Scholar] [CrossRef] [Green Version]

- McNeill, J.I.; Oh, Y. An improved palpebral spring for the manage-ment of paralytic lagophthalmos. Ophthalmology 1991, 98, 715–719. [Google Scholar] [CrossRef]

- Jiang, D.; Demosthenous, A. A multichannel high-frequency power-isolated neural stimulator with crosstalk reduction. IEEE Trans. Biomed. Circuits Syst. 2018, 12, 940–953. [Google Scholar] [CrossRef] [PubMed]

- Hageman, K.N.; Kalayjian, Z.K.; Tejada, F.; Chiang, B.; Rahman, M.A.; Fridman, G.Y.; Dai, C.; Pouliquen, P.O.; Georgiou, J.; della Santina, C.C.; et al. A cmos neural interface for a multi channel vestibular prosthesis. IEEE Trans. Biomed. Circuits Syst. 2015, 10, 269–279. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- van Dongen, M.N.; Serdijn, W.A. A power-efficient multi-channel neural stimulator using high-frequency pulsed excitation from an unfiltered dynamic supply. IEEE Trans. Biomed. Circuits Syst. 2015, 10, 61–71. [Google Scholar] [CrossRef] [PubMed]

- Son, J.-Y.; Cha, H.-K. An implantable neural stimulator ic withanodic current pulse modulation based active charge balancing. IEEE Access 2020, 8, 136449–136458. [Google Scholar] [CrossRef]

- Moganti, G.L.K.; Praneeth, V.S.; Vanjari, S.R.K. An Implantable Bipolar Active Charge Balancing Circuit with Six Adjustment Current levels for Facial Paralysis Patients. In Proceedings of the 11th IEEE International Conference on Intelligent Data Acquisition and Advanced Computing Systems, Krakow, Poland, 22–25 September 2021; Volume 2, pp. 1004–1009. [Google Scholar]

- Dommel, N.; Wong, Y.; Lehmann, T.; Dodds, C.; Lovell, N.; Suaning, G. A CMOS retinal neurostimulator capable of focussed, simultaneous stimulation. J. Neural Eng. 2009, 6, 035006. [Google Scholar] [CrossRef] [PubMed]

- Lee, H.-M.; Park, H.; Ghovanloo, M. A power-efficient wireless system with adaptive supply control for deep brain stimulation. IEEE J. Solid-State Circuits 2013, 48, 2203–2216. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Sooksood, K.; Noorsal, E. A Highly Compliant Current Driver for Electrical Stimulator with Compliance Monitor and Digital Controlled Offset Regulation Charge Balancing. In Proceedings of the 8th IEEE International Electrical Engineering Congress (iEECON), Chiang Mai, Thailand, 4–6 March 2020; pp. 1–4. [Google Scholar]

- Luo, Z.; Ker, M.-D. A high-voltage-tolerant and precise chargebalanced neuro-stimulator in low voltage CMOS process. IEEE Trans. Biomed. Circuits Syst. 2016, 10, 1087–1099. [Google Scholar] [CrossRef] [PubMed]

| Technique | ||||||

|---|---|---|---|---|---|---|

| 0 | 0 | 0 | ON | ON | OFF | Anodic pulse modulation |

| 0 | 0 | 1 | OFF | ON | OFF | Anodic pulse modulation |

| 0 | 1 | 0 | OFF | OFF | ON | Offset regulation |

| 0 | 1 | 1 | OFF | OFF | OFF | Electrode shorting |

| 1 | 0 | 0 | OFF | OFF | OFF | Electrode shorting |

| 1 | 0 | 1 | OFF | OFF | ON | Offset regulation |

| 1 | 1 | 0 | OFF | ON | OFF | Cathodic pulse modulation |

| 1 | 1 | 1 | ON | ON | OFF | Cathodic pulse modulation |

| This Work | IEEE Access 2020 [15] | IEECON 2020 [19] | TBioCAS 2018 [12] | TBioCAS 2016 [20] | TBioCAS 2015 [14] | TBioCAS 2015 [13] | |

|---|---|---|---|---|---|---|---|

| Technology | 0.18 m | 0.18 m | 0.35 m | 0.6 m | 0.18 m | 0.18 m | 0.18 m |

| Stimulation Current | 0.8 mA–1.4 mA | 1 | 4 A–1 mA | 0.095 | upto 3 mA | 10 mA | 1.45 mA |

| Current resolution | 3-bit | 5-bit | 5-bit | 8-bit | 15-bit | 6-bit | 9-bit |

| Voltage | 1.8 V | 12.3 V | 20V | 12 V | 12 V | 20 V | 12 V |

| Technique | RVM + BPM | ACM + ES | OR | ES | ES | OR | DBC |

| Charge Balance | Bipolar | Mono polar | - | - | Bipolar | Mono polar | - |

| ETI variations | Yes | No | No | No | No | No | No |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Moganti, G.L.K.; Siva Praneeth, V.N.; Vanjari, S.R.K. A Hybrid Bipolar Active Charge Balancing Technique with Adaptive Electrode Tissue Interface (ETI) Impedance Variations for Facial Paralysis Patients. Sensors 2022, 22, 1756. https://doi.org/10.3390/s22051756

Moganti GLK, Siva Praneeth VN, Vanjari SRK. A Hybrid Bipolar Active Charge Balancing Technique with Adaptive Electrode Tissue Interface (ETI) Impedance Variations for Facial Paralysis Patients. Sensors. 2022; 22(5):1756. https://doi.org/10.3390/s22051756

Chicago/Turabian StyleMoganti, Ganesh Lakshmana Kumar, V. N. Siva Praneeth, and Siva Rama Krishna Vanjari. 2022. "A Hybrid Bipolar Active Charge Balancing Technique with Adaptive Electrode Tissue Interface (ETI) Impedance Variations for Facial Paralysis Patients" Sensors 22, no. 5: 1756. https://doi.org/10.3390/s22051756

APA StyleMoganti, G. L. K., Siva Praneeth, V. N., & Vanjari, S. R. K. (2022). A Hybrid Bipolar Active Charge Balancing Technique with Adaptive Electrode Tissue Interface (ETI) Impedance Variations for Facial Paralysis Patients. Sensors, 22(5), 1756. https://doi.org/10.3390/s22051756